XUP-P3R PCle FPGA Board

# UltraScale+ PCIe board with Quad QSFP and 512 GBytes DDR4

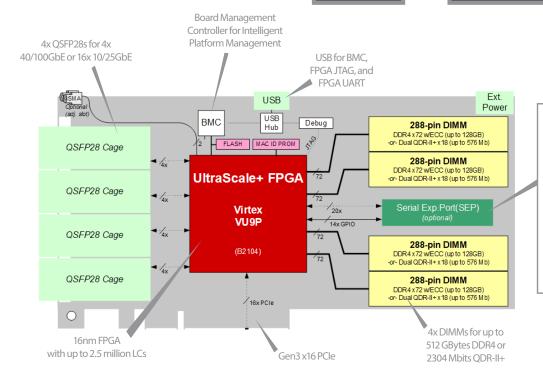

BittWare's XUP-P3R is a 3/4-length PCle x16 card based on the Xilinx Virtex UltraScale+ FPGA. The UltraScale+ devices deliver high-performance, high-bandwidth, and reduced latency for systems demanding massive data flow and packet processing. The board offers extensive memory configurations supporting up to 512 GBytes of memory, sophisticated clocking and timing options, and four front panel QSFP cages, each supporting up to 100 Gbps (4x25) - including 100GbE.

The XUP-P3R also incorporates a Board Management Controller (BMC) for advanced system monitoring, which greatly simplifies platform integration and management. All of these features combine to make the XUP-P3R ideal for a wide range of data center applications, including network processing and security, acceleration, storage, broadcast, and SigInt.

#### Tool Flow Flexibility for Softwareor Hardware-Based Development

- · SDAccel support for software-orientated customers

- · Abstration for faster development

- · Compiler, debugger, and profiler with with support for standard OpenCL APIs

- · Add optimized HDL IP cores to OpenCL designs as libraries

- · Traditional VHDL/Verilog support for hardware-orientated customers

- · Hand-code for ultimate performance

- High-Level Synthesis (HLS) available for rapid development

- FPGA card designed to support standard Xilinx IP cores for UltraScale+

key features

**4x 100GbE** via 4 QSFP28 Up to **512 GBytes** DDR4

Up to VU9P: **2.5 million LCs** FPGA by Xilinx

#### **Serial Expansion Interface**

Optimize the XUP-P3R for your application with expansion:

- · Board-to-board interconnect

- Connect to accessory boards for customization options such as x16 PCle or 4x 100G

- · Includes GPIO

Inquire about customized Molex connectors/cables as required for your application.

### **Additional Services**

Take advantage of BittWare's range of design, integration, and support options

#### **Customization**

Additional specification options or accessory boards to meet your exact needs.

#### **Server Integration**

Available pre-integrated in our <u>TeraBox servers</u> in a range of configurations.

#### **Application Optimization**

Ask about our services to help you port, optimize, and benchmark your application.

#### **Service and Support**

BittWare Developer Site provides online documentation and issue tracking.

#### **Board Specifications**

| •                           |                                                                                                                                                                                                     |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA                        | Virtex UltraScale+ VU9P Core speed grade - 2 Contact BittWare for additional FPGA options                                                                                                           |

| External memory             | <ul> <li>4 DIMM sites, each supporting*:</li> <li>Up to 128 GBytes DDR4 x72 with ECC</li> <li>Up to 576 Mbits dual QDR-II+ x18 (2 independent 288 Mbit banks)</li> </ul>                            |

| Host interface              | x16 Gen3 interface direct to FPGA                                                                                                                                                                   |

| USB header                  | Micro USB: (USB 2.0) for debug and programming<br>FPGA and Flash                                                                                                                                    |

| Serial expansion port (SEP) | Expansion interface to FPGA via 20x GTY transceivers (optional; requires second slot)     14x GPIO signals to the FPGA                                                                              |

| QSFP cages                  | <ul> <li>4 QSFP28 (zQSFP) cages on front panel connected directly to FPGA via 16 transceivers</li> <li>Each supports 100GbE, 40GbE, 4x 25GbE, or 4x 10GbE and can be combined for 400GbE</li> </ul> |

| On-board Flash              | Flash memory for booting FPGA                                                                                                                                                                       |

<sup>\*</sup> DIMM sites 1/2 and sites 3/4 must have the same memory type, or be empty.

| Board<br>Management<br>Controller | <ul> <li>Voltage, current, temperature monitoring</li> <li>Power sequencing and reset</li> <li>Field upgrades</li> <li>FPGA configuration and control</li> <li>Clock configuration</li> <li>I²C bus access</li> <li>USB 2.0</li> <li>Voltage overrides</li> </ul> |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cooling                           | <ul> <li>Standard: double-width active fan and heatsink</li> <li>Optional: double-width passive heatsink</li> <li>Optional: double-width advanced passive cooling with heatpipes</li> </ul>                                                                       |

| Electrical                        | <ul> <li>On-board power derived from 12V PCle slot &amp; an<br/>AUX connector (6-pin)</li> <li>Power dissipation is application dependent</li> </ul>                                                                                                              |

| Environmental                     | Operating temperature 5°C to 35°C                                                                                                                                                                                                                                 |

| Size                              | <ul> <li>¾-length, standard-height PCle dual-slot card</li> <li>9.4 x 4.37 inches</li> </ul>                                                                                                                                                                      |

#### **Development Tools**

| FPGA development           | • | FPGA Examples - example Vivado projects                                                                                                                                                                                       |

|----------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application<br>development | • | BittWorks II Toolkit - host, command, and debug tools for BittWare hardware     Xilinx Vivado® Design Suite     OpenCL - Xilinx SDAccel Development Environment, SDAccel Platform Release and pre-built examples for XIIP-P3R |

#### To learn more, visit www.BittWare.com

Rev 2019.12.19 | December 2019

© BittWare 2019

UltraScale, Virtex, and Vivado are registered trademarks of Xilinx Corp. All other products are the trademarks or registered trademarks of their respective holders.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Molex:

XUPP3R-0001 XUPP3R-0060 XUPP3R-0003 XUPP3R-0049 XUPP3R-0057 XUPP3R-0068