# VSC8501-03

# 10/100/1000BASE-T PHY with Synchronous Ethernet and RGMII/GMII/MII MAC Interface

#### **OVERVIEW**

The VSC8501-03 device is designed for space-constrained 10/100/1000BASE-T applications. It features integrated, line-side termination to conserve board space, to lower EMI, and to improve system performance. Additionally, integrated RGMII timing compensation eliminates the need for on-board delay lines.

The VSC8501-03 device includes Microsemi's EcoEthernet™ v2.0 technology that supports IEEE 802.3az Energy Efficient Ethernet (EEE) and power saving features to reduce power based on link state and cable reach. The device optimizes power consumption in all link operating speeds and features Wake-on-LAN (WOL) power management using magic packets.

The VSC8501-03 device also includes fast link failure indication for high availability networks. Fast link failure indication identifies the onset of a link failure in less than 1 ms typical to go beyond the IEEE 802.3 standard requirement of 750 ms ±10 ms (link master).

Synchronous Ethernet and Ring Resiliency™ are supported. The VSC8501-03 device includes recovered clock output for Synchronous Ethernet applications. Programmable clock squelch control is included to inhibit undesirable clocks from propagating and to help prevent timing loops. Ring Resiliency allows a PHY port to switch between master and slave timing references with no link drop in 1000BASE-T mode.

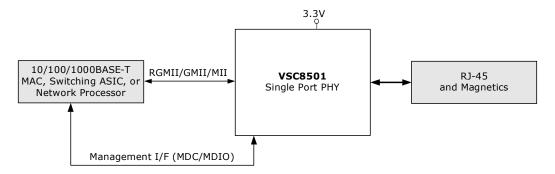

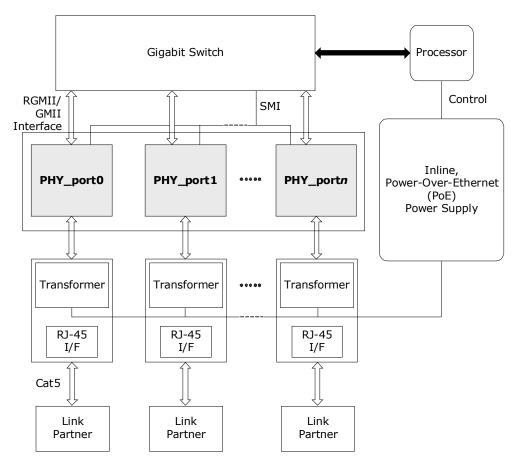

The following illustration shows a high-level, general view of a typical VSC8501-03 application.

#### Copper Transceiver Application Diagram

## **Key Features**

This section lists the main features and benefits of the VSC8501-03 device.

#### SUPERIOR PHY AND INTERFACE TECHNOLOGY

- Integrated 10/100/1000BASE-T Ethernet copper transceiver (IEEE 802.3ab compliant) with VeriPHY® cable diagnostics

- Patented line driver with low EMI voltage mode architecture and integrated line-side termination resistors

- · Wake-on-LAN using magic packets

- · HP Auto-MDIX and manual MDI/MDIX support

- Jumbo frame support up to 16 kilobytes with programmable synchronization FIFOs

#### SYNCHRONOUS ETHERNET SUPPORT

Recovered clock output with programmable clock squelch control and fast link failure indication (<1 ms typical) for ITU-T G.8261/Y.1361 compliant Synchronous Ethernet (SyncE) applications

- · 1000BASE-T Ring Resiliency feature to switch between master and slave timing without dropping link

- · Clock output squelch to inhibit clocks during auto-negotiation and no link status

#### BEST IN CLASS POWER CONSUMPTION

- EcoEthernet™ v2.0 green energy efficiency with ActiPHY™, PerfectReach™, and IEEE 802.3az Energy Efficient Ethernet (EEE)

- · Fully optimized power consumption for all link speeds

- · Clause 45 registers to support Energy Efficient Ethernet and IEEE 802.3bf

## **KEY SPECIFICATIONS**

- Compliant with IEEE 802.3 (10BASE-T, 100BASE-TX, and 1000BASE-T) specifications

- · Supports GMII

- Supports RGMII version 1.3 and 2.5V and 3.3V CMOS for RGMII version 2.0

- · Supports IEEE 1149.1 JTAG boundary scan

- Devices support operating temperatures of -40 °C ambient to 125 °C junction or 0 °C ambient to 125 °C junction

- · Optionally reports if a link partner is requesting inline Power over Ethernet (PoE or PoE+)

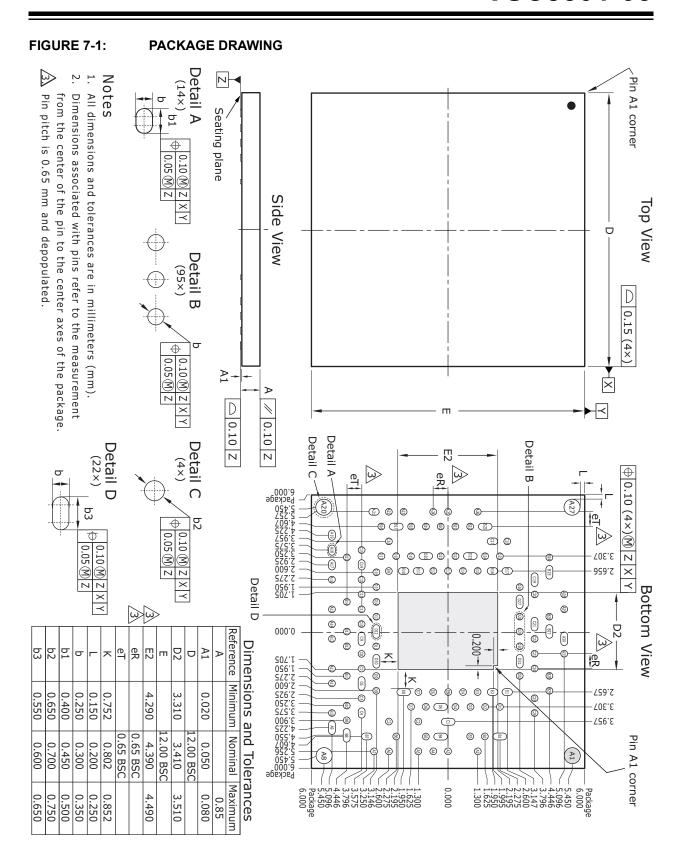

- Available in 12 mm × 12 mm, 135-pin plastic multi-row QFN package

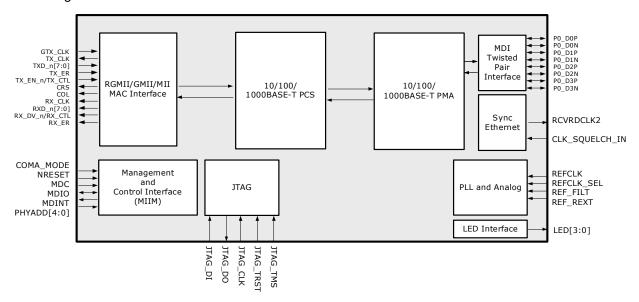

## **Block Diagram**

The following illustration shows the primary functional blocks of the VSC8501-03 device.

#### **Block Diagram**

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Contents**

| Ove | rview                                                                          | 1    |

|-----|--------------------------------------------------------------------------------|------|

| 1.0 | Pin Descriptions                                                               | 5    |

|     | 1.1 Pin Identifications                                                        | 5    |

|     | 1.2 Pin Diagram                                                                | 5    |

|     | 1.3 Pins by Function                                                           |      |

| 2.0 | Ordering Information                                                           | . 11 |

| 3.0 | Functional Descriptions                                                        |      |

|     | 3.1 Wake-On-LAN and SecureOn                                                   | 12   |

|     | 3.2 Operating Modes                                                            | 12   |

|     | 3.3 MAC Interface                                                              | . 12 |

|     | 3.4 PHY Addressing                                                             |      |

|     | 3.5 Cat5 Twisted Pair Media Interface                                          | . 14 |

|     | 3.6 Reference Clock                                                            |      |

|     | 3.7 Ethernet Inline-Powered Devices                                            |      |

|     | 3.8 IEEE 802.3af Power Over Ethernet Support                                   | 17   |

|     | 3.9 ActiPHY Power Management                                                   |      |

|     | 3.10Media Recovered Clock Output                                               | 19   |

|     | 3.11Serial Management Interface                                                | 19   |

|     | 3.12LED Interface                                                              | 21   |

|     | 3.13Fast Link Failure Indication                                               | 24   |

|     | 3.14Testing Features                                                           | . 24 |

|     | 3.15Configuration                                                              | . 28 |

| 4.0 | Registers                                                                      | . 29 |

|     | 4.1 Register and Bit Conventions                                               | 29   |

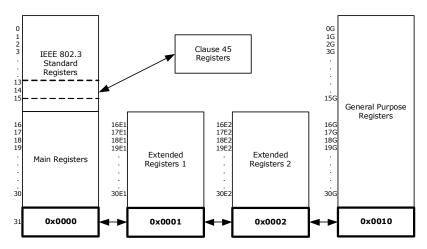

|     | 4.2 IEEE 802.3 and Main Registers                                              | . 30 |

|     | 4.3 Extended Page 1 Registers                                                  | . 44 |

|     | 4.4 Extended Page 2 Registers                                                  | . 48 |

|     | 4.5 General Purpose Registers                                                  | . 53 |

|     | 4.6 Clause 45 Registers to Support Energy Efficient Ethernet and 802.3bf       | . 57 |

| 5.0 | Design Considerations                                                          | 61   |

|     | 5.1 Rx clock duty cycle performance in MII mode                                | . 61 |

|     | 5.2 10BASE-T signal amplitude                                                  | . 61 |

|     | 5.3 TX_CLK is on in GMII 1000BASE-T mode                                       | . 61 |

|     | 5.4 Data is driven on RXD[7:4] in RGMII 1000BASE-T mode                        | . 61 |

|     | 5.5 Rx clock duty cycle performance in RGMII mode at 10 Mbps                   | . 61 |

|     | 5.6 Anomalous PCS error indications in Energy Efficient Ethernet mode          | . 61 |

|     | 5.7 RGMII interface may not generate even count of preamble nibbles at 10 Mbps |      |

|     | 5.8 MAC interface RX_CLK synchronization                                       | . 61 |

|     | 5.9 Link status LED remains on while COMA_MODE pin is asserted high            | . 62 |

|     | 5.10LED pulse stretch enable turns off LED pins                                | 62   |

|     | 5.11Long link up times while in forced 100BASE-TX mode                         | . 62 |

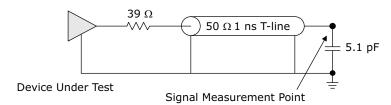

| 6.0 | Electrical Specifications                                                      | . 63 |

|     | 6.1 DC Characteristics                                                         | . 63 |

|     | 6.2 AC Characteristics                                                         | . 66 |

|     | 6.3 Operating Conditions                                                       | . 74 |

|     | 6.4 Stress Ratings                                                             | 74   |

| 7.0 | Package Information                                                            | . 76 |

|     | 7.1 Package Drawing                                                            | 76   |

|     | 7.2 Thermal Specifications                                                     |      |

|     | 7.3 Moisture Sensitivity                                                       | 78   |

| App | endix A: Revision History                                                      |      |

|     | Microchip WebSite                                                              |      |

|     | tomer Change Notification Service                                              |      |

| Cus | tomer Support                                                                  | . 80 |

## 1.0 PIN DESCRIPTIONS

The VSC8501-03 device has 135 pins, which are described in this section.

The pin information is also provided as an attached Microsoft Excel file so that you can copy it electronically. In Acrobat, double-click the attachment icon.

## 1.1 Pin Identifications

This section contains the pin descriptions for the VSC8501-03 device. The following table provides notations for definitions of the various pin types.

TABLE 1-1: PIN TYPE SYMBOL DEFINITIONS

| Symbol | Pin Type            | Description                                          |

|--------|---------------------|------------------------------------------------------|

| ADIFF  | Analog differential | Analog differential signal pair.                     |

| ļ      | Input               | Input without on-chip pull-up or pull-down resistor. |

| I/O    | Bidirectional       | Bidirectional input or output signal.                |

| NC     | No connect          | No connect pins must be left floating.               |

| 0      | Output              | Output signal.                                       |

| OD     | Open drain          | Open drain output.                                   |

| PD     | Pull-down           | On-chip pull-down resistor to VSS.                   |

| PU     | Pull-up             | On-chip pull-up resistor.                            |

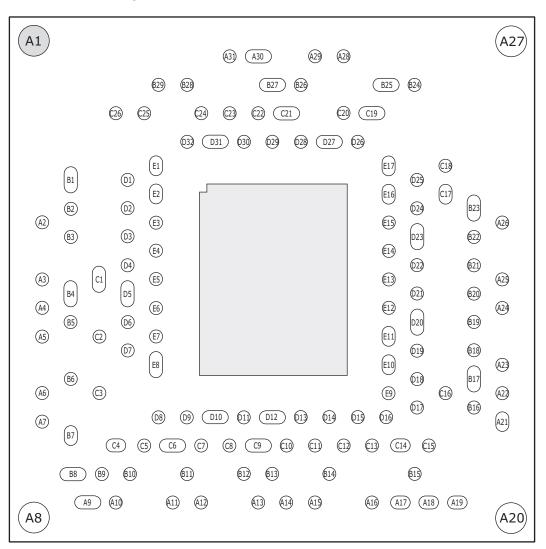

## 1.2 Pin Diagram

The following illustration shows the pin diagram for the VSC8501-03 device, as seen looking through the package from the top of it. Note that the exposed pad connects to the package ground.

FIGURE 1-1: PIN DIAGRAM

## 1.3 Pins by Function

This section contains the functional pin descriptions for the VSC8501-03 device.

## 1.3.1 COPPER PHY MEDIA

The following table lists the copper PHY media pins.

TABLE 1-2: COPPER PHY MEDIA PINS

| Name   | Pin | Type  | I/O Domain | Description                     |

|--------|-----|-------|------------|---------------------------------|

| P0_D0N | B26 | ADIFF | VDD25A     | Tx/Rx channel A negative signal |

| P0_D0P | B27 | ADIFF | VDD25A     | Tx/Rx channel A positive signal |

| P0_D1N | A28 | ADIFF | VDD25A     | Tx/Rx channel B negative signal |

| P0_D1P | A29 | ADIFF | VDD25A     | Tx/Rx channel B positive signal |

| P0_D2N | C19 | ADIFF | VDD25A     | Tx/Rx channel C negative signal |

| P0_D2P | C20 | ADIFF | VDD25A     | Tx/Rx channel C positive signal |

| P0_D3N | B24 | ADIFF | VDD25A     | Tx/Rx channel D negative signal |

| P0_D3P | B25 | ADIFF | VDD25A     | Tx/Rx channel D positive signal |

## 1.3.2 JTAG

The following table lists the JTAG test pins.

TABLE 1-3: JTAG PINS

| Name      | Pin | Туре  | I/O Domain | Description                                                                                             |

|-----------|-----|-------|------------|---------------------------------------------------------------------------------------------------------|

| JTAG_CLK  | B4  | I, PU | VDDIO      | JTAG clock                                                                                              |

| JTAG_DI   | A3  | I, PU | VDDIO      | JTAG test serial data input                                                                             |

| JTAG_DO   | C1  | 0     | VDDIO      | JTAG test serial data output                                                                            |

| JTAG_TMS  | E5  | I, PU | VDDIO      | JTAG test mode select                                                                                   |

| JTAG_TRST | D4  | I, PU | VDDIO      | JTAG reset Important When JTAG is not in use, this pin must be tied to ground with a pull-down resistor |

## 1.3.3 MISCELLANEOUS

The following table lists the miscellaneous pins.

TABLE 1-4: MISCELLANEOUS PINS

| Name            | Pin                                                                                                                                                                                               | Туре | Description                                                                                          |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------|

| LED[0:3]_PHY0   | E13, B21, A25, B20                                                                                                                                                                                | 0    | LED direct-drive outputs. All LEDs pins are active-low. A serial LED stream can also be implemented. |

| NC_[1:4]        | A1, A8, A20, A27                                                                                                                                                                                  | NC   | No connect.                                                                                          |

| REF_FILT        | C21                                                                                                                                                                                               | Α    | Reference filter connects to an external 1 $\mu F$ capacitor to analog ground.                       |

| REF_REXT        | C22                                                                                                                                                                                               | Α    | Reference external connects to an external 2 $k\Omega$ (1%) resistor to analog ground.               |

| RESERVED_[0:37] | C26, C25, B29, B28,<br>C24, C23, A31, A30,<br>C10, A13, B13, B12,<br>A12, C8, D12, A11,<br>A10, B10, D11, C6,<br>A9, C5, B11, C7, B9,<br>B8, C4, D9, B7, D8,<br>A7, A6, E8, B6, E6,<br>C2, A5, B5 |      | Reserved. Leave unconnected.                                                                         |

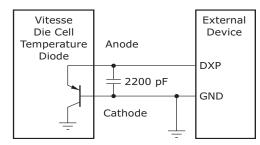

| THERMDA         | B2                                                                                                                                                                                                | Α    | Thermal diode anode.                                                                                 |

| THERMDC_VSS     | D3                                                                                                                                                                                                | A    | Thermal diode cathode connected to device ground. Temperature sensor must be chosen accordingly.     |

## 1.3.4 PHY CONFIGURATION

The following table lists the PHY configuration pins.

TABLE 1-5: PHY CONFIGURATION PINS

| Name           | Pin | Type  | I/O<br>Domain | Description                               |

|----------------|-----|-------|---------------|-------------------------------------------|

| CLK_SQUELCH_IN | A2  | I, PD | VDDIO         | Input control to squelch recovered clock. |

TABLE 1-5: PHY CONFIGURATION PINS (CONTINUED)

| Name                       | Pin | Туре    | I/O<br>Domain | Description                                                                                                                                                                                                                                                                                                        |

|----------------------------|-----|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMA_MODE                  | B22 | I/O, PU | VDDIO         | When this pin is asserted high, the PHY is held in a powered down state. When de-asserted low, the PHY is powered up and resume normal operation. This signal is also used to synchronize the operation of multiple chips on the same PCB to provide visual synchronization for LEDs driven by separate chips. (1) |

| FASTLINK_FAIL/PHY-<br>ADD0 | A4  | 0       | VDDIO         | Fast link failure indication signal. This pin is not active when NRESET is asserted. When disabled, the pin is held low. Also functions as device SMI address bit 0 that is latched when NRESET is deasserted.                                                                                                     |

| NRESET                     | E14 | I, PD   | VDDIO         | Device reset. Active low input that powers down the device and sets all register bits to their default state.                                                                                                                                                                                                      |

| PHYADD1                    | A26 | I/O, PD | VDDIO         | Device Address bit 1. <sup>(2)</sup>                                                                                                                                                                                                                                                                               |

| RCVRDCLK2/PHYADD2          | B23 | I/O, PD | VDDIO         | Clock output, can be enabled or disabled. Output a clock based on the selected active media. This pin is not active when NRESET is asserted. When disabled, the pin is held low. Also functions as device SMI address bit 2 that is latched when NRESET is deasserted. (2)                                         |

| PHYADD3                    | D23 | I, PD   | VDDIO         | Device SMI address bits 3. <sup>(2)</sup>                                                                                                                                                                                                                                                                          |

| PHYADD4                    | C17 | I, PD   | VDDIO         | Device SMI address bits 4. <sup>(2)</sup>                                                                                                                                                                                                                                                                          |

| REFCLK                     | В3  | 1       | VDDIO         | Reference clock.                                                                                                                                                                                                                                                                                                   |

| REFCLK_SEL                 | E4  | I, PU   | VDDIO         | Reference clock frequency select signal.                                                                                                                                                                                                                                                                           |

<sup>1.</sup> For more information, see Section 3.15.1 "Initialization". For information about a typical bring-up example, see Section 3.15 "Configuration".

#### 1.3.5 POWER SUPPLY AND GROUND

The following table lists the power supply pins and associated functional pins. All power supply pins must be connected to their respective voltage input, even if certain functions are not used for a specific application. No power supply sequencing is required. However, clock and power must be stable before releasing Reset.

TABLE 1-6: POWER SUPPLY AND GROUND PINS

| Name     | Pin                | Description                                                       |

|----------|--------------------|-------------------------------------------------------------------|

| VDD1     | D6, D7, D18, D20   | 1.0V digital core power supply                                    |

| VDD1A    | D26, D28, D30, D32 | 1.0V analog power requiring additional PCB power supply filtering |

| VDD25A   | D27, D29, D31      | 2.5V analog power requiring additional PCB power supply filtering |

| VDDIO    | D5, D21, D22       | 2.5V or 3.3V general I/O power supply                             |

| VDDMAC0  | C12, E10, E11      | 2.5V or 3.3V RGMII/GMII/MII MAC power supply                      |

| VDDMAC1  | C3, C9, D10        | 2.5V or 3.3V RGMII/GMII/MII MAC power supply <sup>1</sup>         |

| VDDMDIO  | D13                | 1.2V, 2.5V, or 3.3V power for SMI pins                            |

| RESERVED | E2, E16            | Reserved signal, connect to device V <sub>SS</sub>                |

| VSS_CASE | Exposed pad, E7    | Common device ground                                              |

<sup>1.</sup> This pin shall be connected to the same external supply rail as VDDMAC0. It is a required supply input for the single-port as well as the dual-port device.

<sup>2.</sup> When pulled high to 3.3V VDDIO, the pull-up must be composed of a 2.4 k $\Omega$  from VDDIO to PHYADD, and 10 k $\Omega$  from PHYADD to VSS.

## 1.3.6 REGULATOR

The following table lists the regulator pins.

TABLE 1-7: REGULATOR PINS

| Name      | Pin | Туре | I/O Domain | Description                        |

|-----------|-----|------|------------|------------------------------------|

| RESERVED  | D24 | Α    | VDDREG_33  | Reserved signal, leave unconnected |

| RESERVED  | B1  | Α    | VDDREG_33  | Reserved signal, leave unconnected |

| RESERVED  | E15 | А    | VDDREG_33  | Reserved signal, leave unconnected |

| RESERVED  | E3  | Α    | VDDREG_33  | Reserved signal, leave unconnected |

| RESERVED  | D25 | Α    | VDDREG_33  | Reserved signal, leave unconnected |

| RESERVED  | D1  | А    | VDDREG_33  | Reserved signal, leave unconnected |

| REG_EN_10 | C18 | Α    | VDDREG_33  | Connect to device V <sub>SS</sub>  |

| REG_EN_25 | D2  | Α    | VDDREG_33  | Connect to device V <sub>SS</sub>  |

| RESERVED  | E17 | А    | VDDREG_33  | Reserved signal, leave unconnected |

| RESERVED  | E1  | Α    | VDDREG_33  | Reserved signal, leave unconnected |

## 1.3.7 RGMII/GMII/MII INTERFACE

The following table lists the RGMII/GMII/MII interface pins.

TABLE 1-8: RGMII/GMII/MII INTERFACE PINS

| Name             | Pin                | Туре  | I/O<br>Domain | Description                                                               |

|------------------|--------------------|-------|---------------|---------------------------------------------------------------------------|

| COL_0            | E9                 | 0     | VDDMAC0       | GMII/MII collision output                                                 |

| CRS_0            | C15                | 0     | VDDMAC0       | GMII/MII carrier sense output                                             |

| GTX_CLK_0/TXC_0  | B16                | I, PD | VDDMAC0       | GMII/RGMII transmit clock input                                           |

| RX_CLK_0         | D16                | 0     | VDDMAC0       | GMII/MII receive clock output                                             |

| RX_DV_0/RX_CTL_0 | D15                | 0     | VDDMAC0       | GMII/MII receive data valid output/RGMII receive control output           |

| RX_ER_0          | C14                | 0     | VDDMAC0       | GMII/MII receive data error output                                        |

| RXD[0:3]_0       | A19, B15, A18, D14 | 0     | VDDMAC0       | RGMII/GMII/MII data output                                                |

| RXD[4:7]_0       | C13, A17, A16, B14 | 0     | VDDMAC0       | GMII data output                                                          |

| TX_CLK_0         | D17                | 0     | VDDMAC0       | MII transmit clock output                                                 |

| TX_EN_0/TX_CTL_0 | C16                | I, PD | VDDMAC0       | GMII/MII transmit data enable input/<br>RGMII transmit data control input |

| TX_ER_0          | A21                | I, PD | VDDMAC0       | GMII/MII transmit data error input                                        |

| TXD[0:3]_0       | A22, B17, D19, A23 | I     | VDDMAC0       | RGMII/GMII/MII data input                                                 |

| TXD[4:7]_0       | B18, B19, E12, A24 | I     | VDDMAC0       | GMII data input                                                           |

## 1.3.8 SERIAL MANAGEMENT INTERFACE

The following table lists the serial management interface (SMI) pins. The SMI pins are referenced to VDD25 and can be set to a 2.5 V power supply.

TABLE 1-9: SMI PINS

| Name  | Pin | Туре  | I/O<br>Domain | Description                                                                                                                   |

|-------|-----|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------|

| MDC   | C11 | I     | VDDMDIO       | Management data clock. A 0 MHz to 12.5 MHz reference input is used to clock serial MDIO data into and out of the PHY.         |

| MDINT | A14 | O, OD | VDDMDIO       | Management interrupt signal. These pins can be tied together in a wired-OR configuration with only a single pull-up resistor. |

## VSC8501-03

## TABLE 1-9: SMI PINS (CONTINUED)

| Name | Pin | Туре | I/O<br>Domain | Description                                                                                                                                                                                                                                      |

|------|-----|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDIO | A15 | I/O  | VDDMDIO       | Management data input/output pin. Serial data is written or read from this pin bidirectionally between the PHY and station manager, synchronously on the positive edge of MDC. One external pull-up resistor is required at the station manager. |

## 2.0 ORDERING INFORMATION

The VSC8501-03 device is offered with two operating temperature ranges. The range for VSC8501 is 0 °C ambient to 125 °C junction. The range for VSC8501-03 is –40 °C ambient to 125 °C junction.

The VSC8501-03XML package is a lead-free (Pb-free), 135-pin, multi-row plastic quad flat no-lead (QFN) package with an exposed pad, 12 mm × 12 mm body size, 0.65 mm pin pitch, and 0.85 mm maximum height.

Lead-free products from Microchip comply with the temperatures and profiles defined in the joint IPC and JEDEC standard IPC/JEDEC J-STD-020. For more information, see the IPC and JEDEC standard.

The following table lists the ordering information for the VSC8501-03 device.

TABLE 2-1: ORDERING INFORMATION

| Part Order Number | Description                                                                                                                                                                                                    |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VSC8501XML-03     | Lead-free, 135-pin, multi-row plastic QFN package with an exposed pad, 12 mm × 12 mm body size, 0.65 mm pin pitch, and 0.85 mm maximum height. The operating temperature is –40 °C ambient to 125 °C junction. |  |

## 3.0 FUNCTIONAL DESCRIPTIONS

This section describes the functional aspects of the VSC8501-03 device, including available configurations, operational features, and testing functionality. It also defines the device setup parameters that configure the device for a particular application.

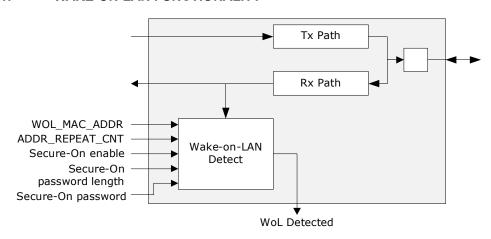

#### 3.1 Wake-On-LAN and SecureOn

The VSC8501-03 device supports Wake-on-LAN, an Ethernet networking standard to awaken hosts by using a "magic packet" that is decoded to ascertain the source, and then assert an interrupt pin or an LED. The VSC8501-03 device also supports SecureOn to secure Wake-on-LAN against unauthorized access. The following illustration shows an overview of the Wake-on-LAN functionality.

FIGURE 3-1: WAKE-ON-LAN FUNCTIONALITY

Wake-on-LAN detection is available in 10BASE-T, 100BASE-TX, and 1000BASE-T modes. It is enabled by setting the interrupt mask register (25.6) and its status is read in the interrupt status register (26.6). Wake-on-LAN and SecureOn are configured for each port using register 27E2. The MAC address for each port is saved in its local register space (21E2, 22E2, and 23E2).

## 3.2 Operating Modes

The following table lists the operating modes of the VSC8501-03 device.

TABLE 3-1: OPERATING MODES

| Operating Mode | Supported Media   |  |

|----------------|-------------------|--|

| RGMII-Cat5     | 10/100/1000BASE-T |  |

| GMII-Cat5      | 10/100/1000BASE-T |  |

#### 3.3 MAC Interface

The VSC8501-03 device supports RGMII versions 1.3 and 2.0 and GMII/MII MAC interfaces at 2.5 V and 3.3 V operating voltages.

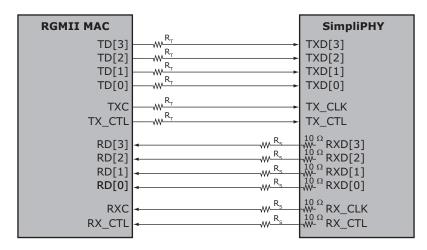

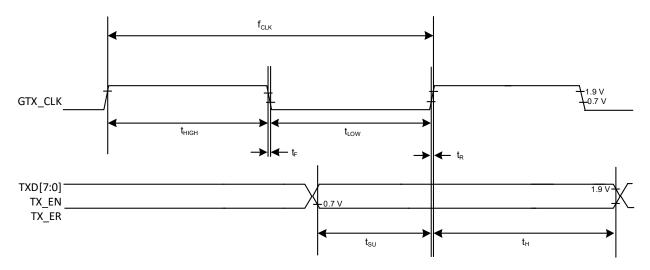

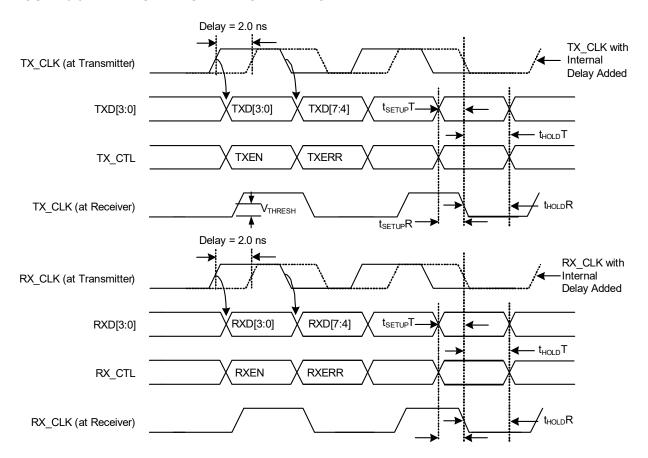

## 3.3.1 RGMII MAC INTERFACE MODE

The VSC8501-03 device supports RGMII versions 1.3 and 2.0 (2.5 V). The RGMII interface supports all three speeds (10 Mbps, 100 Mbps, and 1000 Mbps) and is used as an interface to an RGMII-compatible MAC.

FIGURE 3-2: RGMII MAC INTERFACE

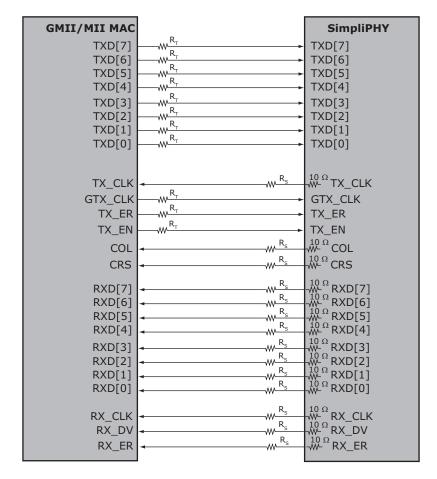

#### 3.3.2 GMII/MII INTERFACE MODE

The GMII/MII interface supports all three speeds (10 Mbps, 100 Mbps, and 1000 Mbps), and is used as an interface to a GMII/MII-compatible MAC.

FIGURE 3-3: GMII/MII MAC INTERFACE

### 3.4 PHY Addressing

The VSC8501-03 device includes five external PHY address pins, PHYADD[4:0], to allow control of multiple PHY devices on a system board sharing a common management bus.

#### 3.5 Cat5 Twisted Pair Media Interface

The twisted pair interface is compliant with IEEE 802.3-2008 and the IEEE 802.3az-2010 standard for Energy Efficient Ethernet.

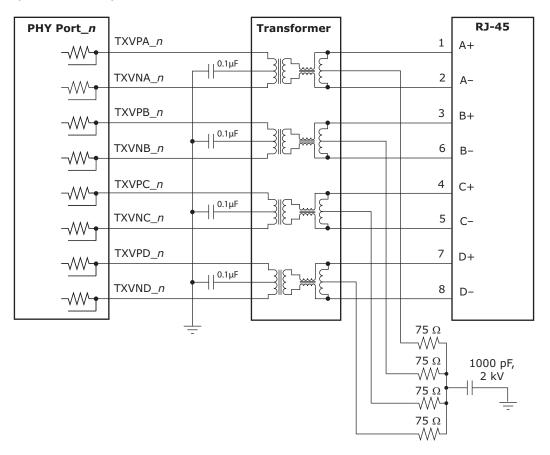

#### 3.5.1 VOLTAGE MODE LINE DRIVER

The VSC8501-03 device uses a patented voltage mode line driver that allows it to fully integrate the series termination resistors, which are required to connect the PHY's Cat5 interface to an external 1:1 transformer. Also, the interface does not require the user to place an external voltage on the center tap of the magnetic. The following illustration shows the connections.

FIGURE 3-4: CAT5 MEDIA INTERFACE

#### 3.5.2 CAT5 AUTO-NEGOTIATION AND PARALLEL DETECTION

The VSC8501-03 device supports twisted pair auto-negotiation, as defined by IEEE 802.3-2008 Clause 28 and IEEE 802.3az-2010. The auto-negotiation process evaluates the advertised capabilities of the local PHY and its link partner to determine the best possible operating mode. In particular, auto-negotiation can determine speed, duplex configuration, and master or slave operating modes for 1000BASE-TX. Auto-negotiation also enables a connected MAC to communicate with its link partner MAC through the VSC8501-03 device using optional next pages to set attributes that may not otherwise be defined by the IEEE standard.

If the Category 5 (Cat5) link partner does not support auto-negotiation, the VSC8501-03 device automatically uses parallel detection to select the appropriate link speed.

Auto-negotiation is disabled by clearing register 0, bit 12. When auto-negotiation is disabled, the state of register bits 0.6, 0.13, and 0.8 determine the device operating speed and duplex mode.

**Note:** While 10BASE-T and 100BASE-TX do not require auto-negotiation, IEEE 802.3-2008 Clause 40 has defined 1000BASE-T to require auto-negotiation.

#### 3.5.3 AUTOMATIC CROSSOVER AND POLARITY DETECTION

For trouble-free configuration and management of Ethernet links, the VSC8501-03 device includes a robust automatic crossover detection feature for all three speeds on the twisted pair interface (10BASE-T, 100BASE-T, and 1000BASE T). Known as HP Auto-MDIX, the function is fully compliant with Clause 40 of IEEE 802.3-2008.

Additionally, the device detects and corrects polarity errors on all MDI pairs — a useful capability that exceeds the requirements of the standard.

Both HP Auto-MDIX detection and polarity correction are enabled in the device by default. Default settings can be changed using device register bits 18.5:4. Status bits for each of these functions are located in register 28.

**Note:** The VSC8501-03 device can be configured to perform HP Auto-MDIX, even when auto-negotiation is disabled and the link is forced into 10/100 speeds. To enable this feature, set register 18.7 to 0. To use the feature, also set register 0.12 to 0.

The HP Auto-MDIX algorithm successfully detects, corrects, and operates with any of the MDI wiring pair combinations listed in the following table, which shows that twisted pair A (of four twisted pairs A, B, C, and D) is connected to the RJ45 connector 1,2 in normal MDI mode.

TABLE 3-2: SUPPORTED MDI PAIR COMBINATIONS

| RJ45 Connections |      | ons  |      |                                             |  |

|------------------|------|------|------|---------------------------------------------|--|

| 1, 2             | 3, 6 | 4, 5 | 7, 8 | Mode                                        |  |

| Α                | В    | С    | D    | Normal MDI                                  |  |

| В                | Α    | D    | С    | Normal MDI-X                                |  |

| Α                | В    | D    | С    | Normal MDI with pair swap on C and D pair   |  |

| В                | Α    | С    | D    | Normal MDI-X with pair swap on C and D pair |  |

## 3.5.4 MANUAL MDI/MDIX SETTING

As an alternative to HP Auto-MDIX detection, the PHY can be forced to be MDI or MDI-X using register 19E1, bits 3:2. Setting these bits to 10 forces MDI and setting 11 forces MDI-X. Leaving the bits 00 enables the HP Auto-MDIX setting to be based on register 18, bits 7 and 5.

#### 3.5.5 LINK SPEED DOWNSHIFT

For operation in cabling environments that are incompatible with 1000BASE-T, the VSC8501-03 device provides an automatic link speed downshift option. When enabled, the device automatically changes its 1000BASE-T auto-negotiation advertisement to the next slower speed after a set number of failed attempts at 1000BASE-T. No reset is required to get out of this state when a subsequent link partner with 1000BASE-T support is connected. This feature is useful in setting up in networks using older cable installations that include only pairs A and B, and not pairs C and D.

To configure and monitor link speed downshifting, set register 20E1, bits 4:1. For more information, see Table 4-35.

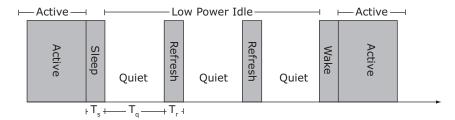

#### 3.5.6 ENERGY EFFICIENT ETHERNET

The VSC8501-03 device supports the IEEE 802.3az-2010 Energy Efficient Ethernet standard to provide a method for reducing power consumption on an Ethernet link during times of low utilization. It uses low power idles (LPI) to achieve this objective.

#### FIGURE 3-5: LOW POWER IDLE OPERATION

Using LPI, the usage model for the link is to transmit data as fast as possible and then return to a low power idle state. Energy is saved on the link by cycling between active and low power idle states. During LPI, power is reduced by turning off unused circuits and using this method, energy use scales with bandwidth utilization. The VSC8501-03 device uses LPI to optimize power dissipation in 100BASE-TX and 1000BASE-T modes of operation.

In addition, the IEEE 802.3az-2010 standard defines a 10BASE-Te mode that reduces transmit signal amplitude from 5 V peak-to-peak to approximately 3.3 V peak-to-peak. This mode reduces power consumption in 10 Mbps link speed and fully interoperates with legacy 10BASE-T compliant PHYs over 100 m Cat5 cable or better.

To configure the VSC8501-03 device in 10BASE-Te mode, set register 17E2.15 to 1 for each port. Additional energy efficient Ethernet features are controlled through Clause 45 registers. For more information, see Section 4.6, "Clause 45 Registers to Support Energy Efficient Ethernet and 802.3bf".

#### 3.5.7 RING RESILIENCY

Ring resiliency changes the timing reference between the master and slave PHYs without altering the master/slave configuration in 1000BASE-T mode. The master PHY transmitter sends data based on the local clock and initiates timing recovery in the receiver. The slave PHY instructs nodes to switch the local timing reference to the recovered clock from other PHYs in the box, freezes timing recovery, and locks clock frequency for the transmitter. The master PHY makes a smooth transition to transmission from local clock to recovered clock after timing lock is achieved.

Ring resiliency can be used in synchronous Ethernet systems because the local clocks in each node are synchronized to a grandmaster clock.

**Note:** For ring resiliency to successfully exchange master/slave timing over 1000BASE-T, the link partner must also support ring resiliency.

## 3.6 Reference Clock

The device reference clock supports a single-ended, CMOS logic level drive clock signal with both 25 MHz and 125 MHz frequency.

The REFCLK\_SEL pin configures the reference clock frequency. The following table shows the functionality and associated reference clock frequency.

TABLE 3-3: REFCLK FREQUENCY SELECTION

| REFCLK_SEL | Frequency |  |

|------------|-----------|--|

| 0          | 125 MHz   |  |

| 1          | 25 MHz    |  |

### 3.7 Ethernet Inline-Powered Devices

The VSC8501-03 device can detect legacy inline-powered devices in Ethernet network applications. Inline-powered detection capability is useful in systems that enable IP phones and other devices (such as wireless access points) to receive power directly from their Ethernet cable, similar to office digital phones receiving power from a private branch exchange (PBX) office switch over telephone cabling. This type of setup eliminates the need for an external power supply and enables the inline-powered device to remain active during a power outage, assuming that the Ethernet switch is connected to an uninterrupted power supply, battery, back-up power generator, or other uninterruptable power source.

For more information about legacy inline-powered device detection, visit the Cisco Web site at <a href="https://www.cisco.com">www.cisco.com</a>. The following illustration shows an example of an inline-powered Ethernet switch application.

FIGURE 3-6: INLINE-POWERED ETHERNET SWITCH DIAGRAM

The following procedure describes the process that an Ethernet switch must perform to process inline-power requests made by a link partner that is, in turn, capable of receiving inline-power:

- Enable the inline-powered device detection mode on each VSC8501-03 PHY using its serial management interface. Set register bit 23E1.10 to 1.

- Ensure that the auto-negotiation enable bit (register 0.12) is also set to 1. In the application, the device sends a special fast link pulse signal to the link partner. Reading register bit 23E1.9:8 returns 00 during the search for devices that require power over Ethernet (PoE).

- 3. The VSC8501-03 PHY monitors its inputs for the fast link pulse signal looped back by the link partner. A link partner capable of receiving PoE loops back the fast link pulses when the link partner is in a powered down state. This is reported when register bit 23E1.9:8 reads back 01. It can also be verified as an inline-power detection interrupt by reading register bit 26.9, which should be a 1, and which is subsequently cleared and the interrupt de-asserted after the read. When a link partner device does not loop back the fast link pulse after a specific time, register bit 23E1.9:8 automatically resets to 10.

- 4. If the VSC8501-03 PHY reports that the link partner requires PoE, the Ethernet switch must enable inline-power on this port, independent of the PHY.

- 5. The PHY automatically disables inline-powered device detection when the register bits 23E1.9:8 automatically reset to 10, and then automatically changes to its normal auto-negotiation process. A link is then autonegotiated and established when the link status bit is set (register bit 1.2 is set to 1).

- 6. In the event of a link failure (indicated when register bit 1.2 reads 0), it is recommended that the inline-power be disabled to the inline-powered device independent of the PHY. The VSC8501-03 PHY disables its normal autonegotiation process and re-enables its inline-powered device detection mode.

## 3.8 IEEE 802.3af Power Over Ethernet Support

The VSC8501-03 device is compatible with designs that are intended for use in systems that supply power to data terminal equipment (DTE) by means of the MDI or twisted pair cable, as described in IEEE 802.3af Clause 33.

### 3.9 ActiPHY Power Management

In addition to the IEEE-specified power-down control bit (device register bit 0.11), the VSC8501-03 device also includes an ActiPHY power management mode for each PHY. This mode enables support for power-sensitive applications. It utilizes a signal-detect function that monitors the media interface for the presence of a link to determine when to automatically power-down the PHY. The PHY wakes up at a programmable interval and attempts to wake up the link partner PHY by sending a burst of fast link pulse over copper media.

The ActiPHY power management mode is enabled on a per-port basis during normal operation at any time by setting register bit 28.6 to 1.

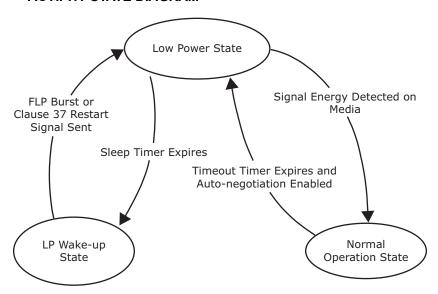

The following operating states are possible when ActiPHY mode is enabled:

- · Low power state

- · Link partner wake-up state

- · Normal operating state (link-up state)

The VSC8501-03 device switches between the low power state and link partner wake-up state at a programmable rate (the default is two seconds) until signal energy has been detected on the media interface pins. When signal energy is detected, the PHY enters the normal operating state. If the PHY is in its normal operating state and the link fails, the PHY returns to the low power state after the expiration of the link status time-out timer. After reset, the PHY enters the low power state.

When auto-negotiation is enabled in the PHY, the ActiPHY state machine operates as described.

When auto-negotiation is disabled and the link is forced to use 10BASE-T or 100BASE-TX modes while the PHY is in its low power state, the PHY continues to transition between the low power and link partner wake-up states until signal energy is detected on the media pins. At that time, the PHY transitions to the normal operating state and stays in that state even when the link is dropped. When auto-negotiation is disabled while the PHY is in the normal operation state, the PHY stays in that state when the link is dropped and does not transition back to the low power state.

The following illustration shows the relationship between ActiPHY states and timers.

FIGURE 3-7: ACTIPHY STATE DIAGRAM

#### 3.9.1 LOW POWER STATE

In the low power state, all major digital blocks are powered down. However, the SMI interface (MDC, MDIO, and MDINT) functionality is provided.

In this state, the PHY monitors the media interface pins for signal energy. The PHY comes out of low power state and transitions to the normal operating state when signal energy is detected on the media. This happens when the PHY is connected to one of the following:

- · Auto-negotiation-capable link partner

- Another PHY in enhanced ActiPHY link partner wake-up state

In the absence of signal energy on the media pins, the PHY periodically transitions from low-power state to link partner wake-up state, based on the programmable sleep timer (register bits 20E1.14:13). The actual sleep time duration is randomized from –80 ms to 60 ms to avoid two linked PHYs in ActiPHY mode entering a lock-up state during operation.

#### 3.9.2 LINK PARTNER WAKE-UP STATE

In the link partner wake-up state, the PHY attempts to wake up the link partner. Up to three complete fast link pulse bursts are sent on alternating pairs A and B of the Cat5 media for a duration based on the wake-up timer, which is set using register bits 20E1.12:11.

In this state, SMI interface (MDC, MDIO, and MDINT) functionality is provided.

After sending signal energy on the relevant media, the PHY returns to the low power state.

#### 3.9.3 NORMAL OPERATING STATE

In the normal operating state, the PHY establishes a link with a link partner. When the media is unplugged or the link partner is powered down, the PHY waits for the duration of the programmable link status time-out timer, which is set using register bit 28.7 and bit 28.2. It then enters the low power state.

#### 3.10 Media Recovered Clock Output

For Synchronous Ethernet applications, the VSC8501 includes a recovered clock output pin, RCVRDCLK2, controlled by register 24G. The recovered clock pin is synchronized to the clock of the active media link.

To enable recovered clock output, set register 24G bit 15 to 1. By default, the recovered clock output pins are disabled and held low, including when NRESET is asserted. Register 24G also controls the PHY port for clock output, the clock source, the clock frequency (either 25 MHz, 31.25 MHz, or 125 MHz), and squelch conditions.

**Note:** When EEE is enabled on a link, the use of the recovered clock output is not recommended due to long holdovers occurring during EEE quiet/refresh cycles.

## 3.10.1 CLOCK OUTPUT SQUELCH

Under certain conditions, the PHY outputs a clock based on the REFCLK pin, such as when there is no link present or during auto-negotiation. To prevent an undesirable clock from appearing on the recovered clock pins, the VSC8501 device squelches, or inhibits, the clock output based on any of the following criteria:

- No link is detected (the link status register 1, bit 2 = 0).

- The link is found to be unstable using the fast link failure detection feature. The FASTLINK-FAIL pin is asserted high when enabled.

- The active link is in 10BASE-T or in 1000BASE-T master mode. These modes produce unreliable recovered clock sources.

- · CLK SQUELCH IN is enabled to squelch the clock.

Use register 24G, bits 5:4 to configure the clock squelch criteria. This register can also disable the squelch feature. The CLK\_SQUELCH\_IN pin controls the squelching of the clock. The recovered clock output is squelched when the CLK\_SQUELCH\_IN pin is high. This pin should not be left floating.

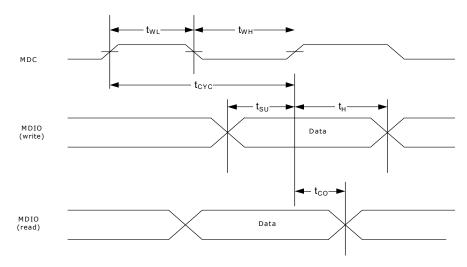

## 3.11 Serial Management Interface

The VSC8501-03 device includes an IEEE 802.3-compliant serial management interface (SMI) that is affected by use of its MDC and MDIO pins. The SMI provides access to device control and status registers. The register set that controls the SMI consists of 32 16-bit registers, including all required IEEE-specified registers. Also, there are additional pages of registers accessible using device register 31.

Energy efficient Ethernet control registers are available through the SMI using Clause 45 registers and Clause 22 register access in registers 13 through 14. For more information, see Table 4-14 and Table 4-52.

The SMI is a synchronous serial interface with input data to the VSC8501-03 device on the MDIO pin that is clocked on the rising edge of the MDC pin. The output data is sent on the MDIO pin on the rising edge of the MDC signal. The interface can be clocked at a rate from 0 MHz to 12.5 MHz, depending on the total load on MDIO. An external  $2-k\Omega$  pull-up resistor is required on the MDIO pin.

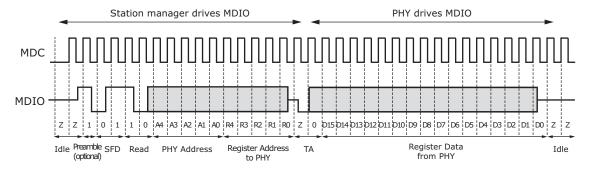

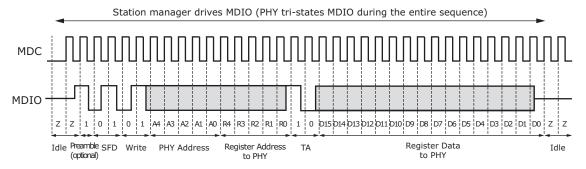

#### 3.11.1 SMI FRAMES

Data is transferred over the SMI using 32-bit frames with an optional, arbitrary-length preamble. Before the first frame can be sent, at least two clock pulses on MDC must be provided with the MDIO signal at logic one to initialize the SMI state machine. The following illustrations show the SMI frame format for read and write operations.

#### FIGURE 3-8: SMI READ FRAME

#### FIGURE 3-9: SMI WRITE FRAME

The following list defines the terms used in the SMI read and write timing diagrams.

- Idle During idle, the MDIO node goes to a high-impedance state. This allows an external pull-up resistor to pull the MDIO node up to a logical 1 state. Because the idle mode does not contain any transitions on MDIO, the number of bits is undefined during idle.

- **Preamble** By default, preambles are not expected or required. The preamble is a string of ones. If it exists, the preamble must be at least 1 bit; otherwise, it can be of an arbitrary length.

- Start of Frame Delimiter (SFD) A pattern of 01 indicates the start of frame. If the pattern is not 01, all following bits are ignored until the next preamble pattern is detected.

- Read or Write Opcode A pattern of 10 indicates a read. A 01 pattern indicates a write. If the bits are not either 01 or 10, all following bits are ignored until the next preamble pattern is detected.

- **PHY Address** The particular VSC8501-03 device responds to a message frame only when the received PHY address matches its physical address. The physical address is 5 bits long (4:0).

- Register Address The next five bits are the register address.

- **Turnaround** The two bits used to avoid signal contention when a read operation is performed on the MDIO are called the turnaround (TA) bits. During read operations, the VSC8501-03 device drives the second TA bit, a logical 0.

- **Data** The 16-bits read from or written to the device are considered the data or data stream. When data is read from a PHY, it is valid at the output from one rising edge of MDC to the next rising edge of MDC. When data is written to the PHY, it must be valid around the rising edge of MDC.

- Idle The sequence is repeated.

#### 3.11.2 SMI INTERRUPT

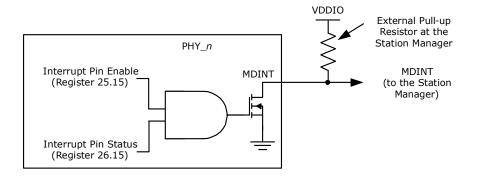

The SMI includes an output interrupt signal, MDINT, for signaling the station manager when certain events occur in the VSC8501-03 device.

When a PHY generates an interrupt, the MDINT pin is asserted by driving low if the interrupt pin enable bit (MII register 25.15) is set. The MDINT pin is configured for open-drain (active-low) operation. Tie the pin to a pull-up resistor to VDDMDIO. The following illustration shows the configuration.

FIGURE 3-10: MDINT CONFIGURED AS AN OPEN-DRAIN (ACTIVE-LOW) PIN

#### 3.12 LED Interface

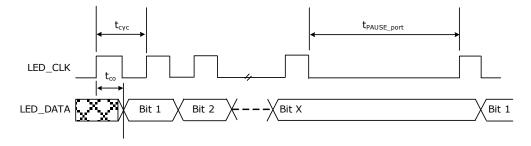

The LED interface supports the following configurations: direct drive, basic serial LED mode, and enhanced serial LED mode. The polarity of the LED outputs is programmable and can be changed using register 17E2, bits 13:10. The default polarity is active low.

Direct drive mode provides four LED signals per port, LED0 through LED3. The mode and function of each LED signal can be configured independently. When serial LED mode is enabled, the direct drive pins not used by the serial LED interface remain available.

In basic serial LED mode, all signals that can be displayed on LEDs are sent as LED\_Data and LED\_CLK for external processing.

In enhanced serial LED mode, up to four LED signals per port can be sent as LED\_Data, LED\_CLK, LED\_LD, and LED Pulse. The following sections provide detailed information about the various LED modes.

The following table shows the bit 9 settings for register 14G that are used to control the LED behavior for all the LEDs in the VSC8501-03 device.

TABLE 3-4: LED DRIVE STATE

| Setting                       | Active | Not Active |

|-------------------------------|--------|------------|

| 14G.9 = 1 (default)           | Ground | Tristate   |

| 14G.9 = 0 (alternate setting) | Ground | $V_{DD}$   |

#### 3.12.1 LED MODES

Each LED pin can be configured to display different status information that can be selected by setting the LED mode in register 29. The default LED state is active low and can be changed by modifying the value in register 17E2, bits 13:10. The blink/pulse stretch is dependent on the LED behavior setting in register 30.

The following table provides a summary of the LED modes and functions. The modes listed are equivalent to the setting used in register 29 to configure each LED pin.

TABLE 3-5: LED MODE AND FUNCTION SUMMARY

| Mode | Function Name     | LED State and Description                                                                                                                                                                         |

|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Link/Activity     | 1: No link in any speed on any media interface. 0: Valid link at any speed on any media interface. Blink or pulse-stretch = Valid link at any speed on any media interface with activity present. |

| 1    | Link1000/Activity | 1: No link in 1000BASE-T. 0: Valid 1000BASE-T. Blink or pulse-stretch = Valid 1000BASE-T link with activity present.                                                                              |

TABLE 3-5: LED MODE AND FUNCTION SUMMARY (CONTINUED)

| Mode | Function Name                         | LED State and Description                                                                                                                                                                           |

|------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | Link100/Activity                      | 1: No link in 100BASE-TX. 0: Valid 100BASE-TX. Blink or pulse-stretch = Valid 100BASE-TX link with activity present.                                                                                |

| 3    | Link10/Activity                       | 1: No link in 10BASE-T. 0: Valid 10BASE-T link. Blink or pulse-stretch = Valid 10BASE-T link with activity present.                                                                                 |

| 4    | Link100/1000/Activity                 | 1: No link in 100BASE-TX or 1000BASE-T. 0: Valid 100BASE-TX or 1000BASE-T link. Blink or pulse-stretch = Valid 100BASE-TX or 1000BASE-T link with activity present.                                 |

| 5    | Link10/1000/Activity                  | 1: No link in 10BASE-T or 1000BASE-T. 0: Valid 10BASE-T or 1000BASE-T link. Blink or pulse-stretch = Valid 10BASE-T or 1000BASE-T link with activity present.                                       |

| 6    | Link10/100/Activity                   | 1: No link in 10BASE-T or 100BASE-TX. 0: Valid 10BASE-T or 100BASE-TX link. Blink or pulse-stretch = Valid 10BASE-T or 100BASE-TX link with activity present.                                       |

| 7    | Reserved                              | Reserved.                                                                                                                                                                                           |

| 8    | Duplex/Collision                      | 1: Link established in half-duplex mode, or no link established. 0: Link established in full-duplex mode. Blink or pulse-stretch = Link established in half-duplex mode but collisions are present. |

| 9    | Collision                             | 1: No collision detected. Blink or pulse-stretch = Collision detected.                                                                                                                              |

| 10   | Activity                              | 1: No activity present.  Blink or pulse-stretch = Activity present (becomes TX activity present when register bit 30.14 is set to 1).                                                               |

| 11   | Reserved                              | Reserved.                                                                                                                                                                                           |

| 12   | Autonegotiation Fault                 | No auto-negotiation fault present.     Auto-negotiation fault occurred.                                                                                                                             |

| 13   | Serial Mode                           | Serial stream. See Section 3.12.2, "Basic Serial LED Mode". Only relevant on PHY port 0. Reserved in others.                                                                                        |

| 14   | Force LED Off                         | 1: De-asserts the LED <sup>(1)</sup> .                                                                                                                                                              |

| 15   | Force LED On                          | 0: Asserts the LED <sup>(1)</sup> .                                                                                                                                                                 |

|      | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                               |

<sup>1.</sup> Setting this mode suppresses LED blinking after reset.

#### 3.12.2 BASIC SERIAL LED MODE

The VSC8501-03 device can be configured so that access to all its LED signals is available through two pins. This option is enabled by setting LED0 to serial LED mode in register 29, bits 3:0 to 0xD. When serial LED mode is enabled, the LED0 pin becomes the serial data pin, and the LED1 pin becomes the serial clock pin. All other LED pins can still be configured normally. The serial LED mode clocks the LED status bits on the rising edge of the serial clock.

The LED behavior settings can also be used in serial LED mode. To configure LED behavior, set device register 30.

The following table shows the serial output bitstream of each LED signal.

TABLE 3-6: LED SERIAL BITSTREAM ORDER

| Output        | PHY0 |

|---------------|------|

| Link/activity | 1    |

TABLE 3-6: LED SERIAL BITSTREAM ORDER (CONTINUED)

| Output                | PHY0 |

|-----------------------|------|

| Link1000/activity     | 2    |

| Link100/activity      | 3    |

| Link10/activity       | 4    |

| Reserved              | 5    |

| Duplex/collision      | 6    |

| Collision             | 7    |

| Activity              | 8    |

| Reserved              | 9    |

| Tx activity           | 10   |

| Rx activity           | 11   |

| Autonegotiation fault | 12   |

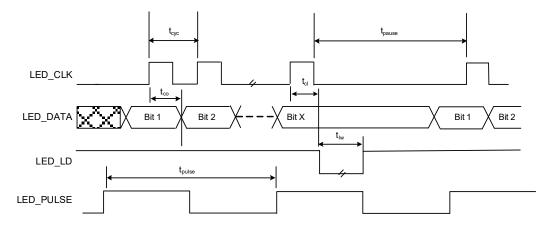

#### 3.12.3 ENHANCED SERIAL LED MODE

The VSC8501-03 device can be configured to output up to four LED signals on a serial stream that can be de-serialized externally to drive LEDs on the system board. In enhanced serial LED mode, the LED output pins serve the following functions:

LED0: LED\_DATALED1: LED\_CLKLED2: LED\_LDLED3: LED PULSE

The serial LED\_DATA is shifted out on the falling edge of LED\_CLK and is latched in the external serial-to-parallel converter on the rising edge of LED\_CLK. The falling edge of LED\_LD signal can be used to shift the data from the shift register in the converter to the parallel output drive register. When a separate parallel output drive register is not used in the external serial-to-parallel converter, the LEDs will blink at a high frequency as the data bits are being shifted through, which may be undesirable. LED pin functionality is controlled by setting register 25G, bits 7:1.

The LED\_PULSE signal provides a 5 kHz pulse stream whose duty cycle can be modulated to turn on/off LEDs at a high rate. This signal can be tied to the output enable signal of the serial-to-parallel converter to provide the LED dimming functionality to save energy. The LED\_PULSE duty cycle is controlled by setting register 25G, bits 15:8.

#### 3.12.4 EXTENDED LED MODES

In addition to the LED modes in register 29, there are also additional LED modes that are enabled on the LED0 pin whenever the corresponding register 19E1, bits 15 to 12 are set to 1. Each of these bits enables an extended mode shown in the following table. For example, LED0 = mode 17 means that register 19E1 bit 12 = 1 and register 29 bits 3 to 0 = 0001.

The following table provides a summary of the extended LED modes and functions.

TABLE 3-7: EXTENDED LED MODE AND FUNCTION SUMMARY

| Mode  | Function Name  | LED State and Description                                 |

|-------|----------------|-----------------------------------------------------------|

| 16-19 | Reserved       | Reserved                                                  |

| 20    | Force LED Off  | 1: De-asserts the LED.                                    |

| 21    | Force LED On   | 0: Asserts the LED. LED pulsing is disabled in this mode. |

| 22    | Fast Link Fail | Enable fast link fail on the LED pin     Disable          |

## 3.12.5 LED BEHAVIOR

Several LED behaviors can be programmed into the VSC8501-03 device. Use the settings in register 30 and 19E1 to program LED behavior, which includes the following:

#### 3.12.5.1 LED Combine

Enables an LED to display the status for a combination of primary and secondary modes. This can be enabled or disabled for each LED pin. For example, a copper link running in 1000BASE-T mode and activity present can be displayed with one LED by configuring an LED pin to Link1000/Activity mode. The LED asserts when linked to a 1000BASE-T partner and also blinks or performs pulse-stretch when activity is either transmitted by the PHY or received by the Link Partner. When disabled, the combine feature only provides status of the selected primary function. In this example, only Link1000 asserts the LED, and the secondary mode, activity, does not display when the combine feature is disabled.

#### 3.12.5.2 LED Blink or Pulse-Stretch

This behavior is used for activity and collision indication. This can be uniquely configured for each LED pin. Activity and collision events can occur randomly and intermittently throughout the link-up period. Blink is a 50% duty cycle oscillation of asserting and de-asserting an LED pin. Pulse-stretch guarantees that an LED is asserted and de-asserted for a specific period of time when activity is either present or not present. These rates can also be configured using a register setting.

#### 3.12.5.3 Rate of LED Blink or Pulse-Stretch

This behavior controls the LED blink rate or pulse-stretch length when blink/pulse-stretch is enabled on an LED pin. The blink rate, which alternates between a high and low voltage level at a 50% duty cycle, can be set to 2.5 Hz, 5 Hz, 10 Hz, or 20 Hz. For pulse-stretch, the rate can be set to 50 ms, 100 ms, 200 ms, or 400 ms.

## 3.12.5.4 LED Pulsing Enable

To provide additional power savings, the LEDs (when asserted) can be pulsed at 5 kHz, 20% duty cycle.

#### 3.12.5.5 LED Blink After Reset

The LEDs will blink for one second after COMA\_MODE is de-asserted (as described in Section 3.15, "Configuration") or a software reset is applied.

This feature can be enabled by setting register 19E1, bit 11 = 1.

#### 3.13 Fast Link Failure Indication

To aid Synchronous Ethernet applications, the VSC8501-03 device can indicate the onset of a link failure in less than 1 ms (<3 ms, worst case). In comparison, the IEEE 802.3 standard establishes a delay of up to 750 ms before indicating that a 1000BASE-T link is no longer present. A fast link failure indication is critical to support ports used in a synchronization timing link application. Fast link failure is supported for each PHY port through the FASTLINK-FAIL pin. Fast link failure is supported through the MDINT (active low) pin only in 1000BASE-T and 100BASE-TX modes. It is not supported through the MDINT pin and interrupt status register 26, bit 7 in 10BASE-T mode.

**Note:** For all links except 1000BASE-T, the fast link failure indication matches the link status register (address 1, bit 2). For 1000BASE-T links, the link failure is based on a circuit that analyzes the integrity of the link, and will assert at the indication of failure. The MDINT pin is not reset until register 26 is cleared.

**Note:** A system can later confirm the fast link down indication for system management purposes by actively polling the link status bit to determine if a link has failed.

Note: FLF indication should not be used when EEE is enabled on a link.

## 3.14 Testing Features

The VSC8501-03 device includes several testing features designed to facilitate performing system-level debugging and in-system production testing. This section describes the available features.

## 3.14.1 ETHERNET PACKET GENERATOR

The Ethernet packet generator (EPG) can be used at each of the 10/100/1000BASE-T speed settings for copper Cat5 media to isolate problems between the MAC and the VSC8501-03 device, or between a locally connected PHY and its remote link partner. Enabling the EPG feature disables all MAC interface transmit pins and selects the EPG as the source for all data transmitted onto the twisted pair interface. This feature is not used when the SerDes media is set to pass-through mode.

**Important** The EPG is intended for use with laboratory or in-system testing equipment only. Do not use the EPG testing feature when the VSC8501-03 device is connected to a live network.

To enable the EPG feature, set the device register bit 29E1.15 to 1.

When the EPG is enabled, packet loss occurs during transmission of packets from the MAC to the PHY. However, the PHY receive output pins to the MAC are still active when the EPG is enabled. When it is necessary to disable the MAC receive pins as well, set the register bit 0.10 to 1.

When the device register bit 29E1.14 is set to 1, the PHY begins transmitting Ethernet packets based on the settings in registers 29E1 and 30E1. These registers set:

- · Source and destination addresses for each packet

- · Packet size

- · Interpacket gap

- · FCS state

- · Transmit duration

- · Payload pattern

When register bit 29E1.13 is set to 0, register bit 29E1.14 is cleared automatically after 30,000,000 packets are transmitted.

#### 3.14.2 FAR-END LOOPBACK

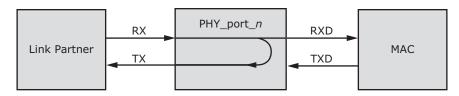

The far-end loopback testing feature is enabled by setting register bit 23.3 to 1. When enabled, it forces incoming data from a link partner on the current media interface into the MAC interface of the PHY where it is retransmitted back to the link partner on the media interface as shown in the following illustration. In addition, the incoming data also appears on the receive data pins of the MAC interface. Data present on the transmit data pins of the MAC interface is ignored when using this testing feature.

## FIGURE 3-11: FAR-END LOOPBACK DIAGRAM

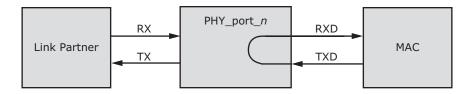

#### 3.14.3 NEAR-END LOOPBACK

When the near-end loopback testing feature is enabled, transmitted data (TXD) is looped back in the PCS block onto the receive data signals (RXD), as shown in the following illustration. When using this testing feature, no data is transmitted over the network. To enable near-end loopback, set the device register bit 0.14 to 1.

## FIGURE 3-12: NEAR-END LOOPBACK DIAGRAM

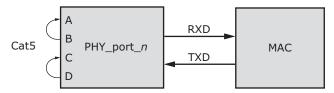

## 3.14.4 CONNECTOR LOOPBACK

The connector loopback testing feature allows the twisted pair interface to be looped back externally. When using this feature, the PHY must be connected to a loopback connector or a loopback cable. Connect pair A to pair B, and pair C to pair D, as shown in the following illustration. The connector loopback feature functions at all available interface speeds.

FIGURE 3-13: CONNECTOR LOOPBACK DIAGRAM

When using the connector loopback testing feature, the device auto-negotiation, speed, and duplex configuration is set using device registers 0, 4, and 9.

For 1000BASE-T connector loopback, additional writes are required in the following order:

- 1. Enable the 1000BASE-T connector loopback. Set register bit 24.0 to 1.

- 2. Disable pair swap correction. Set register bit 18.5 to 1.

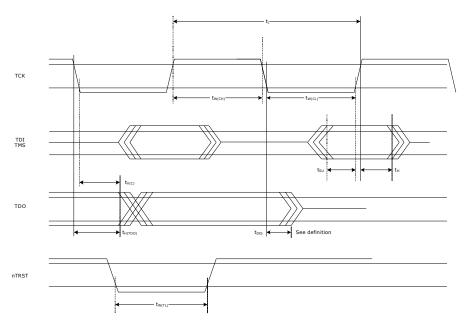

#### 3.14.5 JTAG BOUNDARY SCAN

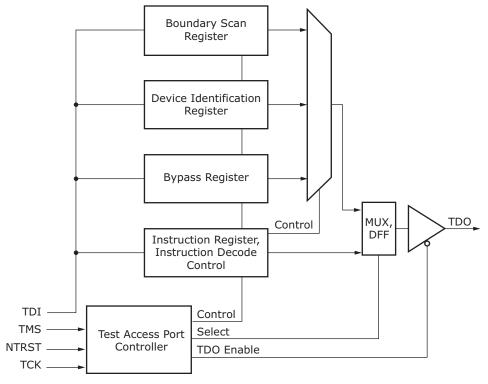

The VSC8501-03 device supports the test access port (TAP) and boundary scan architecture described in IEEE 1149.1. The device includes an IEEE 1149.1-compliant test interface, referred to as a JTAG TAP interface.

The JTAG boundary scan logic on the VSC8501-03 device, accessed using its TAP interface, consists of a boundary scan register and other logic control blocks. The TAP controller includes all IEEE-required signals (TMS, TCK, TDI, and TDO), in addition to the optional asynchronous reset signal TRST. The following illustration shows the TAP and boundary scan architecture.

**Important** When JTAG is not in use, the TRST pin must be tied to ground with a pull-down resistor for normal operation.

FIGURE 3-14: TEST ACCESS PORT AND BOUNDARY SCAN ARCHITECTURE

After a TAP reset, the device identification register is serially connected between TDI and TDO by default. The TAP instruction register is loaded from a shift register when a new instruction is shifted in, or, if there is no new instruction in the shift register, a default value of 6'b100000 (IDCODE) is loaded. Using this method, there is always a valid code in the instruction register, and the problem of toggling instruction bits during a shift is avoided. Unused codes are mapped to the BYPASS instruction.

## 3.14.5.1 JTAG Instruction Codes

The following table shows the supported JTAG instruction codes.

TABLE 3-8: JTAG INSTRUCTION CODES

| Instruction Code | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYPASS           | The bypass register contains a single shift-register stage and is used to provide a minimum-length serial path (one TCK clock period) between TDI and TDO to bypass the device when no test operation is required.                                                                                                                                                                                           |

| CLAMP            | Allows the state of the signals driven from the component pins to be determined from the boundary scan register while the bypass register is selected as the serial path between TDI and TDO. While the CLAMP instruction is selected, the signals driven from the component pins do not change.                                                                                                             |

| EXTEST           | Allows tests of the off-chip circuitry and board-level interconnections by sampling input pins and loading data onto output pins. Outputs are driven by the contents of the boundary scan cells, which have to be updated with valid values, with the PRELOAD instruction, prior to the EXTEST instruction.                                                                                                  |

| HIGHZ            | Places the component in a state in which all of its system logic outputs are placed in a high-impedance state. In this state, an incircuit test system can drive signals onto the connections normally driven by a component output without incurring a risk of damage to the component. This makes it possible to use a board where not all of the components are compatible with the IEEE 1149.1 standard. |

| IDCODE           | Provides the version number (bits 31:28), device family ID (bits 27:12), and the manufacturer identity (bits 11:1) to be serially read from the device.                                                                                                                                                                                                                                                      |

| SAMPLE/PRELOAD   | Allows a snapshot of inputs and outputs during normal system operation to be taken and examined. It also allows data values to be loaded into the boundary scan cells prior to the selection of other boundary scan test instructions.                                                                                                                                                                       |

| USERCODE         | Provides the version number (bits 31:28), part number (bits 27:12), and the manufacturer identity (bits 11:1) to be serially read from the device.                                                                                                                                                                                                                                                           |

The following tables provide information about the IDCODE and USERCODE binary values stored in the device JTAG registers .

TABLE 3-9: JTAG INSTRUCTION CODE IEEE COMPLIANCE

| Description  | Device Version | Family ID           | Manufactur ing Identity | LSB |

|--------------|----------------|---------------------|-------------------------|-----|

| Bit field    | 31–28          | 27–12               | 11–1                    | 0   |

| Binary value | 0000           | 1000 0101 0000 0010 | 000 0111<br>0100        | 1   |

TABLE 3-10: USERCODE JTAG DEVICE IDENTIFICATION REGISTER DESCRIPTIONS

| Description  | Device Version | Model Number        | Manufacturing Identity | LSB |

|--------------|----------------|---------------------|------------------------|-----|

| Bit field    | 31–28          | 27–12               | 11–1                   | 0   |

| Binary value | 0000           | 1000 0101 0000 0001 | 000 0111 0100          | 1   |

The following table provides information about the location and IEEE compliance of the JTAG instruction codes used in the VSC8501-03 device. Instructions not explicitly listed in the table are reserved. For more information about these IEEE specifications, visit the IEEE Web site at www.IEEE.org.

TABLE 3-11: JTAG INSTRUCTION CODE IEEE COMPLIANCE