**TJA1101B** 100BASE-T1 PHY for automotive Ethernet

Rev. 1 — 1 March 2021

Product data sheet

## **1** General description

The TJA1101B is a 100BASE-T1-compliant Ethernet PHY optimized for automotive use cases such as gateways, IP camera links, radar modules, driver assistance systems and back-bone networks. The device provides 100 Mbit/s transmit and receive capability over a single unshielded twisted-pair cable, supporting a cable length of up to at least 15 m. The TJA1101B has been designed for automotive robustness and ISO 26262, ASIL-A compliance, while minimizing power consumption and system costs.

Being ASIL-A compliant, adequate safety features have been implemented to ensure that ASIL requirements are met at system level. Additional documentation, including a safety manual, is available on request.

The TJA1101B supports OPEN Alliance TC-10-compliant sleep and wake-up request forwarding, with an always-on power domain connected directly to the battery supply without the need for a dedicated voltage regulator.

# 2 Features and benefits

## 2.1 General

- 100BASE-T1 PHY

- MII- and RMII-compliant interfaces

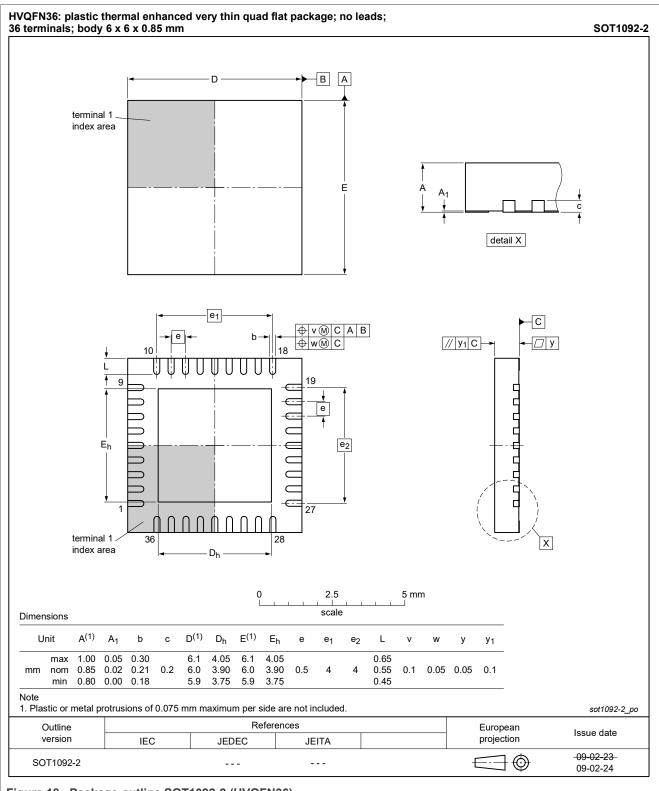

- Compact 36-pin HVQFN package (6 × 6 mm) for PCB space-constrained applications

- ISO 26262, ASIL-A compliant

## 2.2 Optimized for automotive use cases

- Transmitter optimized for capacitive coupling to unshielded twisted-pair cable

- Adaptive receive equalizer optimized for automotive cable length of up to at least 15 m

- Enhanced integrated PAM-3 pulse shaping for low RF emissions

- EMC-optimized output driver strength for MII and RMII

- MDI pins meet class IV conducted emission limit as per OPEN Alliance EMC Specification 2.0

- MDI pins protected against ESD to ±6 kV HBM and ±8 kV IEC61000-4-2

- MDI pins protected against transients in automotive environment

- MDI pins do not need external filtering or ESD protection

- Automotive-grade temperature range from -40 °C to +125 °C

- Automotive product qualification in accordance with AEC-Q100

- Host-configurable MDI polarity

- Automated polarity detection and correction

## 2.3 Low-power mode

- OPEN Alliance TC-10-compliant sleep and wake-up forwarding

Robust remote wake-up detection via bus lines

- Wake-up forwarding at PHY level (supporting global system wake-up)

- Inhibit output for voltage regulator control

- Dedicated PHY enable/disable input pin to minimize power consumption

- Local wake-up pin

- Wake-up via SMI-access

## 2.4 Diagnosis

- Signal Quality Indicator for real-time monitoring of link stability and transmitted data quality

- Diagnosis of cable errors (shorts and opens)

- Gap-free supply undervoltage detection with fail-silent behavior

- · Internal, external and remote loopback modes

## 2.5 Miscellaneous

- Reverse MII mode for back-to-back connection of two PHYs

- On-chip regulators to provide 3.3 V single-supply operation

- Supports optional 1.8 V external supply for digital core

- On-chip termination resistors for the differential cable pair

- Jumbo frame support up to 16 kB

## 3 Ordering information

## Table 1. Ordering information

| Type number | Package |                                                                                                                |           |

|-------------|---------|----------------------------------------------------------------------------------------------------------------|-----------|

|             | Name    | Description                                                                                                    | Version   |

| TJA1101BHN  | HVQFN36 | plastic thermal enhanced very thin quad flat package; no leads; 36 terminals; body $6 \times 6 \times 0.85$ mm | SOT1092-2 |

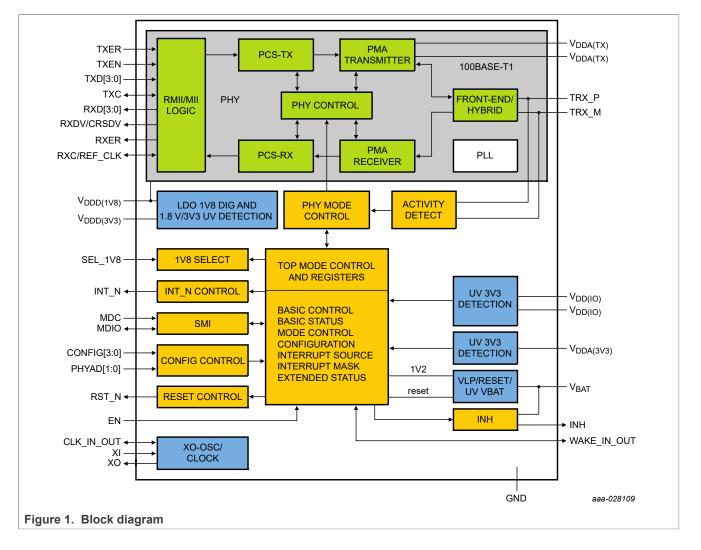

## 4 Block diagram

A block diagram of the TJA1101B is shown in <u>Figure 1</u>. The 100BASE-T1 section contains the functional blocks specified in the 100BASE-T1 standard that make up the Physical Coding Sublayer (PCS) and the Physical Medium Attachment (PMA) layer for both the transmit and receive signal paths. The MII/RMII interface (including the Serial Management Interface (SMI)) conforms to IEEE 802.3 clause 22.

Additional blocks are defined for mode control, register configuration, interrupt control, system configuration, reset control, local wake-up, remote wake-up, undervoltage detection and configuration control. A number of power-supply-related functional blocks are defined: an internal 1.8 V regulator for the digital core, a Very Low Power (VLP) supply for Sleep mode, the reset circuit, supply monitoring and inhibit control.

The clock signals needed for the operation of the PHY are generated in the PLL block, derived from an external crystal or an oscillator input signal.

Pin strapping allows a number of default PHY settings (e.g. Master or Slave configuration) to be hardware-configured at power-up.

## 5 **Pinning information**

## 5.1 Pinning

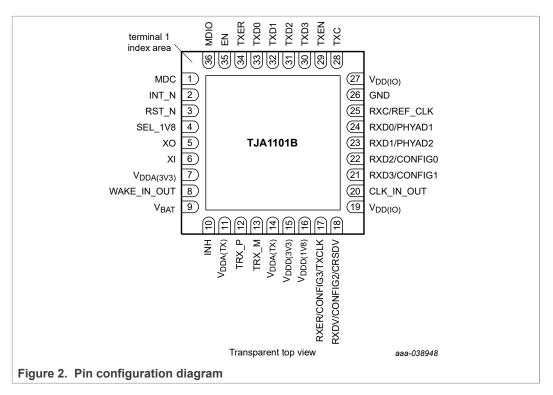

The pin configuration of the TJA1101B is shown in <u>Figure 2</u>. Since 100BASE-T1 allows for full-duplex bidirectional communication, the standard MII signals COL and CRS are not needed.

#### Table 2. Pin description

| Symbol                | Pin | Type <sup>[1]</sup> | Description                                                                                 |  |

|-----------------------|-----|---------------------|---------------------------------------------------------------------------------------------|--|

| MDC                   | 1   | I                   | SMI clock input (weak pull-down)                                                            |  |

| INT_N                 | 2   | 0                   | interrupt output (active-LOW, open-drain output, level-based)                               |  |

| RST_N                 | 3   | I                   | reset input (active-LOW, weak pull-up)                                                      |  |

| SEL_1V8               | 4   | I                   | 1.8 V LDO mode selection (external or internal; weak pull-down)                             |  |

| XO                    | 5   | AO                  | crystal feedback - used in all MII/RMII and Reverse MII modes when a 25 MHz crystal is used |  |

| XI                    | 6   | AI                  | crystal input - used in all MII/RMII and Reverse MII modes when a 25 MHz crystal is used    |  |

| V <sub>DDA(3V3)</sub> | 7   | Р                   | 3.3 V analog supply voltage                                                                 |  |

| WAKE_IN_OUT           | 8   | AIO                 | local/forwarding wake-up input/output (configurable)                                        |  |

| V <sub>BAT</sub>      | 9   | Р                   | battery supply voltage                                                                      |  |

| INH                   | 10  | AO                  | inhibit output for voltage regulator control (V <sub>BAT</sub> -related, active-HIGH)       |  |

TJA1101B Product data sheet © NXP B.V. 2021. All rights reserved.

## 100BASE-T1 PHY for automotive Ethernet

| Symbol                              | Pin | Type <sup>[1]</sup> | Description                                                                                                         |

|-------------------------------------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA(TX)</sub> <sup>[2]</sup> | 11  | Р                   | 3.3 V analog supply voltage for the transmitter                                                                     |

| TRX_P                               | 12  | AIO                 | + terminal for transmit/receive signal                                                                              |

| TRX_M                               | 13  | AIO                 | - terminal for transmit/receive signal                                                                              |

| V <sub>DDA(TX)</sub> <sup>[2]</sup> | 14  | Р                   | 3.3 V analog supply voltage for the transmitter                                                                     |

| V <sub>DDD(3V3)</sub>               | 15  | Р                   | 3.3 V digital supply voltage                                                                                        |

| V <sub>DDD(1V8)</sub>               | 16  | Р                   | 1.8 V digital supply voltage (internally or externally generated; needs to be filtered if generated internally)     |

| RXER                                | 17  | 0                   | MII/RMII receive error output                                                                                       |

| CONFIG3                             | 17  | I                   | pin strapping configuration input 3                                                                                 |

| TXCLK                               | 17  | 0                   | transmit clock output in test mode and during slave jitter test                                                     |

| RXDV                                | 18  | 0                   | MII receive data valid output                                                                                       |

| CONFIG2                             | 18  | I                   | pin strapping configuration input 2                                                                                 |

| CRSDV                               | 18  | 0                   | RMII mode: carrier sense/receive data valid output                                                                  |

| V <sub>DD(IO)</sub> <sup>[3]</sup>  | 19  | Р                   | 3.3 V I/O supply voltage                                                                                            |

| CLK_IN_OUT                          | 20  | Ю                   | 25 MHz reference clock input/output (configurable)                                                                  |

| RXD3                                | 21  | 0                   | MII mode: receive data output, bit 3 of RXD[3:0] nibble                                                             |

| CONFIG1                             | 21  | I                   | pin strapping configuration input 1                                                                                 |

| RXD2                                | 22  | 0                   | MII mode: receive data output, bit 2 of RXD[3:0] nibble                                                             |

| CONFIG0                             | 22  | I                   | pin strapping configuration input 0                                                                                 |

| RXD1                                | 23  | 0                   | MII mode: receive data output, bit 1 of RXD[3:0] nibble<br>RMII mode: receive data output, bit 1 of RXD[1:0] nibble |

| PHYAD2                              | 23  | 1                   | pin strapping configuration input for bit 2 of the PHY address used for the SMI address/Cipher scrambler            |

| RXD0                                | 24  | 0                   | MII mode: receive data output, bit 0 of RXD[3:0] nibble<br>RMII mode: receive data output, bit 0 of RXD[1:0] nibble |

| PHYAD1                              | 24  | 1                   | pin strapping configuration input for bit 1 of the PHY address used for the SMI address/Cipher scrambler            |

| RXC                                 | 25  | 0                   | MII mode: external 25 MHz receive clock output                                                                      |

|                                     |     | I                   | MII reverse mode: 25 MHz receive clock input                                                                        |

| REF_CLK                             | 25  | I                   | RMII mode: interface reference clock input (50 MHz external oscillator)                                             |

|                                     |     | 0                   | RMII mode: interface reference clock output (25 MHz crystal at PHY or 25 MHz clock at input of pin CLK_IN_OUT)      |

| GND <sup>[4]</sup>                  | 26  | G                   | ground reference                                                                                                    |

| V <sub>DD(IO)</sub> <sup>[3]</sup>  | 27  | Р                   | 3.3 V I/O supply voltage                                                                                            |

| ТХС                                 | 28  | 0                   | MII mode: 25 MHz transmit clock output                                                                              |

|                                     |     | I                   | MII reverse mode: external 25 MHz transmit clock input                                                              |

| TXEN                                | 29  | I                   | MII/RMII mode: transmit enable input (active-HIGH; weak pull-down)                                                  |

| TXD3                                | 30  | 1                   | MII mode: transmit data input, bit 3 of TXD[3:0] nibble (weak pull-down)                                            |

## Table 2. Pin description...continued

TJA1101B Product data sheet

## **100BASE-T1 PHY for automotive Ethernet**

| Symbol | Pin | Type <sup>[1]</sup> | Description                                                                                                                                           |

|--------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXD2   | 31  | 1                   | MII mode: transmit data input, bit 2 of TXD[3:0] nibble (weak pull-down)                                                                              |

| TXD1   | 32  | I                   | MII mode: transmit data input, bit 1 of TXD[3:0] nibble (weak pull-down)<br>RMII mode: transmit data input, bit 1 of TXD[1:0] nibble (weak pull-down) |

| TXD0   | 33  | I                   | MII mode: transmit data input, bit 0 of TXD[3:0] nibble (weak pull-down)<br>RMII mode: transmit data input, bit 0 of TXD[1:0] nibble (weak pull-down) |

| TXER   | 34  | I                   | MII/RMII: transmit error input (weak pull-down)                                                                                                       |

| EN     | 35  | 1                   | PHY enable input (active-HIGH; weak pull-down)                                                                                                        |

| MDIO   | 36  | IO                  | SMI data I/O (weak pull-up)                                                                                                                           |

#### Table 2. Pin description...continued

[1]

[2] [3]

AlO: analog input/output; AO: analog output; AI: analog input; I: digital input (V<sub>DD(IO)</sub> related); O: digital output (V<sub>DD(IO)</sub> related); IO: digital input/output (V<sub>DD(IO)</sub> related); P: power supply; G: ground. V<sub>DDA(TX)</sub> pins are connected internally and should be connected together on the PCB (pins 11 and 14). V<sub>DD(IO)</sub> pins are connected internally and should be connected together on the PCB (pins 19 and 27). HVQFN36 package die supply ground is connected to both the GND pin and the exposed center pad. The GND pin must be soldered to board ground. For enhanced thermal and electrical performance, it is also recommended to connect the exposed center pad to board ground. [4]

## 6 Functional description

## 6.1 System configuration

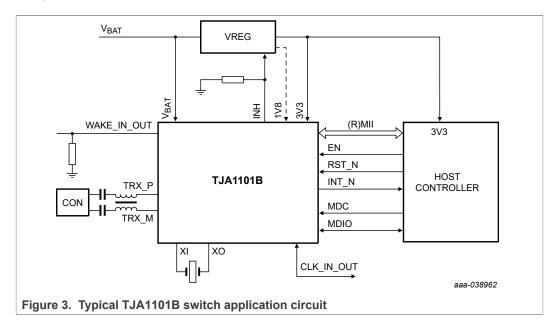

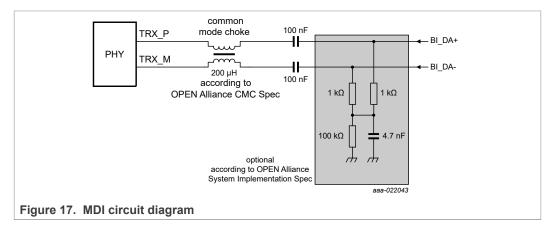

The TJA1101B contains a 100BASE-T1 compliant Ethernet PHY, with 100 Mbit/s transmit and receive capability over a single unshielded twisted-pair cable. The TJA1101B supports a cable length of up to at least 15 m, with a bit error rate of 1E-10 or less. It is optimized for capacitive signal coupling to the twisted-pair lines. A common-mode choke is typically inserted into the signal path to comply with automotive EMC requirements.

The TJA1101B is designed to provide a cost-optimized system solution for automotive Ethernet links. It communicates with the Media Access Control (MAC) unit via the MII or RMII interface.

The TJA1101B can operate with a crystal or an external clock. The clock can be forwarded to other PHYs (see Figure 3). The clocking and power supply schemes are independent of each other.

The TJA1101B can be powered via a single 3.3 V supply. An internal LDO generates the required 1.8 V supply, requiring only the addition of a decoupling capacitor.

When the TJA1101B is used in a switch application with several PHY ports, it may be more efficient to use an external SMPS to provide the 1.8 V supply. In this configuration, the internal LDO is switched off to allow an external supply to be used.

The state of SEL\_1V8 is captured and copied to bit LDO\_MODE (see <u>Table 11</u>) when the device is powered up. A bit value of 0 enables the internal 1.8 V LDO. If LDO\_MODE = 1, the internal LDO is disabled and  $V_{DDD(1V8)}$  must be supplied externally. The value of LDO\_MODE can be changed after power-up via register access.

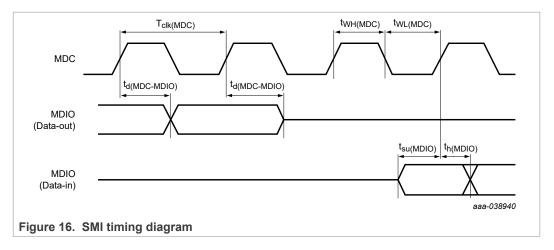

Control and status information is exchanged with the host controller via the SMI interface. The INH output can be used to switch off the external regulator when all ports are in Sleep mode.

TJA1101B Product data sheet

## 6.2 MII and RMII

The TJA1101B supports a number of MII modes that can be selected via pin strapping or the SMI. The following modes are supported:

- MII

- RMII (25 MHz XTAL or external 50 MHz via REF\_CLK)

- Reverse MII (connected externally)

Refer to the SMI register description (Section 6.11) for further configuration options. The strength of the (R)MII output driver signals can be limited in all modes (via bit MII\_DRIVER; see Table 21) to optimize EMC behavior.

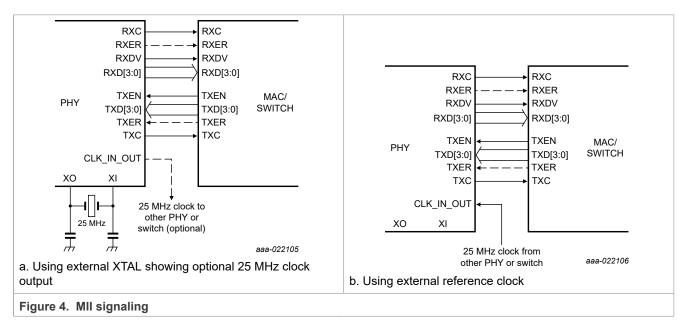

## 6.2.1 MII

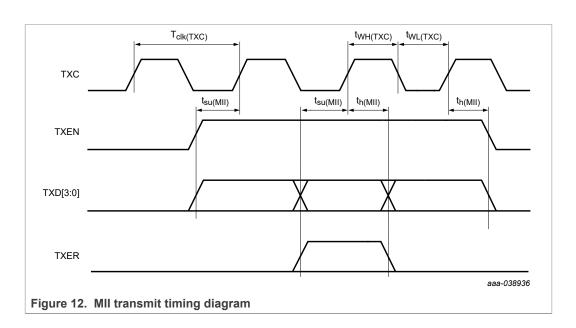

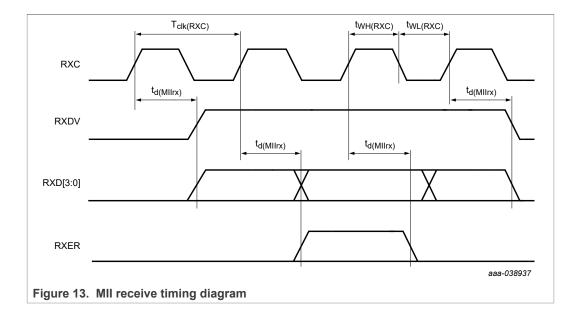

The connections between the PHY and the MAC are shown in more detail in Figure 4. Data is exchanged via 4-bit wide data nibbles on TXD[3:0] and RXD[3:0]. Transmit and receive data is synchronized with the transmit (TXC) and receive (RXC) clocks. Both clock signals are provided by the PHY and are typically derived from an external clock or crystal running at a nominal frequency of 25 MHz (±100 ppm). Normal data transmission is initiated with a HIGH level on TXEN, while a HIGH level on RXDV indicates normal data reception.

MII encoding is described in <u>Table 3</u> and <u>Table 4</u>.

#### Table 3. MII encoding of TXD[3:0], TXEN and TXER

| TXEN | TXER | TXD[3:0]          | Indication                 |

|------|------|-------------------|----------------------------|

| 0    | 0    | 0000 through 1111 | normal interframe          |

| 0    | 1    | 0000 through 1111 | reserved                   |

| 1    | 0    | 0000 through 1111 | normal data transmission   |

| 1    | 1    | 0000 through 1111 | transmit error propagation |

| RXDV | RXER | RXD[3:0]                                     | Indication               |

|------|------|----------------------------------------------|--------------------------|

| 0    | 0    | 0000 through 1111                            | normal interframe        |

| 0    | 1    | 0000                                         | normal interframe        |

| 0    | 1    | 0001 through 1101                            | reserved                 |

| 0    | 1    | 1110                                         | false carrier indication |

| 0    | 1    | 1111                                         | reserved                 |

| 1    | 0    | 0000 through 1111                            | normal data transmission |

| 1    | 1    | 0000 through 1111 data reception with errors |                          |

Table 4. Mll encoding of RXD[3:0], RXDV and RXER

#### 6.2.2 RMII

#### 6.2.2.1 Signaling and encoding

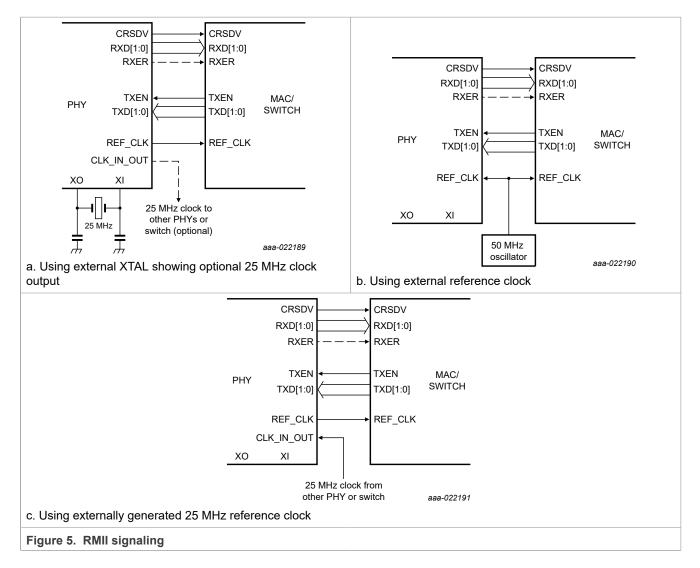

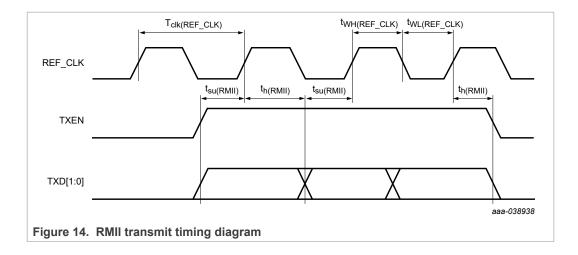

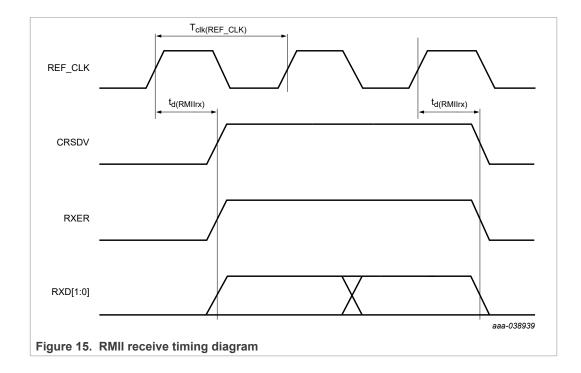

RMII data is exchanged via 2-bit wide data nibbles on TXD[1:0] and RXD[1:0], as illustrated in <u>Figure 5</u>. To achieve the same data rate as MII, the interface is clocked at a nominal frequency of 50 MHz. A single clock signal, REF\_CLK, is provided for both transmitted and received data. This clock signal is provided by the PHY and is typically derived from an external 25 MHz (±100 ppm) crystal (see <u>Figure 5</u> (a)). Alternatively, a 50 MHz clock signal (±50 ppm) generated by an external oscillator can be connected to pin REF\_CLK (see <u>Figure 5</u> (b)). A third option is to connect a 25 MHz (±100 ppm) clock signal generated by another PHY or switch to pin CLK\_IN\_OUT (see <u>Figure 5</u> (c)).

RMII encoding is described in <u>Table 5</u> and <u>Table 6</u>.

#### Table 5. RMII encoding of TXD[1:0], TXEN

| TXEN | TXD[1:0]      | Indication               |

|------|---------------|--------------------------|

| 0    | 00 through 11 | normal interframe        |

| 1    | 00 through 11 | normal data transmission |

| Table 6. RMII e | ncoding of I | RXD[1:0], CRSDV and RXER |            |

|-----------------|--------------|--------------------------|------------|

| CRSDV           | RXER         | RXD[1:0]                 | Indication |

| CRSDV | RXER | RXD[1:0]      | Indication                 |

|-------|------|---------------|----------------------------|

| 0     | 0    | 00 through 11 | normal interframe          |

| 0     | 1    | 00            | normal interframe          |

| 0     | 1    | 01 through 11 | reserved                   |

| 1     | 0    | 00 through 11 | normal data transmission   |

| 1     | 1    | 00 through 11 | data reception with errors |

TJA1101B Product data sheet

## **NXP Semiconductors**

#### **100BASE-T1 PHY for automotive Ethernet**

#### 6.2.3 Reverse MII

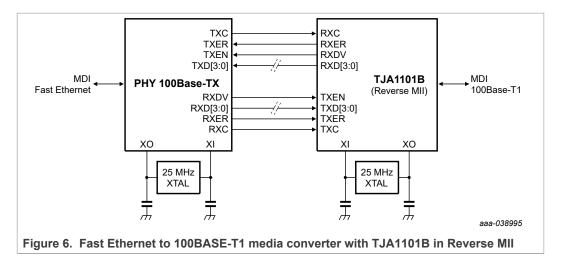

In Reverse MII mode, two PHYs are connected back-to-back via the MII interface to realize a repeater function on the physical layer (see <u>Figure 6</u>). The MII signals are cross-connected: RX output signals from one PHY are connected to the TX inputs on the other PHY. The TXC and RXC clock signals become inputs on the PHY connected in Reverse MII mode. Reverse MII mode is selected by setting bits MII\_MODE = 11

Since the MII interface is a standard solution, two PHYs could be used to implement two different physical layers to realize, for example, a conversion from Fast Ethernet to 100BASE-T1 and vice versa. Another use case for such a repeater could be to double the link length to 30 m.

### **100BASE-T1 PHY for automotive Ethernet**

## 6.3 System controller

## 6.3.1 Operating modes

#### 6.3.1.1 Power-off mode

The TJA1101B remains in Power-off mode as long as the voltage on pin  $V_{BAT}$  is below the power-on reset threshold. The analog blocks are disabled and the digital blocks are in a passive reset state in this mode.

#### 6.3.1.2 Standby mode

At power-on, when the voltage on pin V<sub>BAT</sub> rises above the under-voltage recovery threshold (V<sub>uvr(VBAT)</sub>), the TJA1101B enters Standby mode and switches on the INH control output (pin INH HIGH). This control signal may be used to activate the supply to the microcontroller in the ECU. Once the 3.3 V supply voltage is available, the internal 1.8 V regulator is activated (if selected) and the PHY is configured according to the pin strapping implemented on the CONFIGn and PHYADn pins. No SMI access takes place during the power-on settling time (t<sub>s(pon)</sub>).

From an operating point of view, Standby mode corresponds to the IEEE 802.3 Powerdown mode, where the transmit and receive functions (in the PHY) are disabled. Standby mode also acts as a fail-silent mode. The TJA1101B switches to Standby mode when an undervoltage condition is detected on  $V_{DDA(3V3)}$ ,  $V_{DDD(3V3)}$ ,  $V_{DDD(1V8)}$  or  $V_{DD(IO)}$ .

#### 6.3.1.3 Normal mode

To establish a communication link, the TJA1101B must be switched to Normal mode, either autonomously (AUTO\_OP = 1; see <u>Table 30</u>) or via an SMI command from the host (AUTO\_OP = 0).

When the TJA1101B is configured for autonomous operation, the PHY enters Normal mode automatically and activates the link on power-on. When the TJA1101B is host-controlled, the PHY must be enabled via the SMI.

When the PHY is enabled and enters Normal mode, the internal PLL starts running and the transmit and receive functions (both PCS and PMA) are enabled. After a period of stabilization,  $t_{init(PHY)}$ , the PHY is ready to set up a link.

If link control is enabled (LINK\_CONTROL = 1; see <u>Table 20</u>), a PHY configured as Master initiates the training sequence by transmitting an idle pattern. The receiver of a PHY configured as Slave will attempt to synchronize with the idle pattern. Once the descrambler is synchronized (SCR\_LOCKED = 1), the slave PHY itself starts sending an idle pattern using the recovered clock signal.

The link is established (LINK\_STATUS = 1) when the TJA1101B PHY and the remote PHY indicate that their local receiver status is OK.

#### 6.3.1.4 Disable mode

When the Ethernet interface is not in use or must be disabled for fail-safe reasons, the PHY can be switched off by pulling pin EN LOW. The PHY is switched off completely in Disable mode, minimizing power consumption. The configuration register settings are maintained. EN must be forced HIGH to exit Disable mode and activate the PHY.

#### 6.3.1.5 Sleep mode

If the network manager decides to withdraw a node from the network because it is no longer needed, the PHY can be switched to Sleep mode (powering down the entire ECU).

In Sleep mode, the transmit and receive functions are switched off and no signal is driven onto the twisted-pair lines. Transmit requests from the MII interface are ignored and the MII output pins are in a high-ohmic state. The only valid SMI operations in Sleep mode are reading the POWER\_MODE status bits in the Extended control register and issuing a Standby mode command (POWER\_MODE = 1100; see <u>Table 20</u>).

Releasing the INH output (INH LOW) allows the ECU to switch off its main power supply unit. Typically, the entire ECU is powered-down. The TJA1101B is kept partly alive by the permanent battery supply and can still react to activity on the Ethernet lines. Once valid Ethernet idle pulses longer than  $t_{det(PHY)}$  are detected on the lines (with REMWUPHY = 1), the TJA1101B wakes up in Standby mode and switches on the main power unit via the INH control signal. The TJA1101B PHY enters Normal mode via autonomous operation once the supply voltages are stable within their operating ranges, or can be switched to Normal mode via an SMI command if host-controlled. The communication link to the partner can then be re-established.

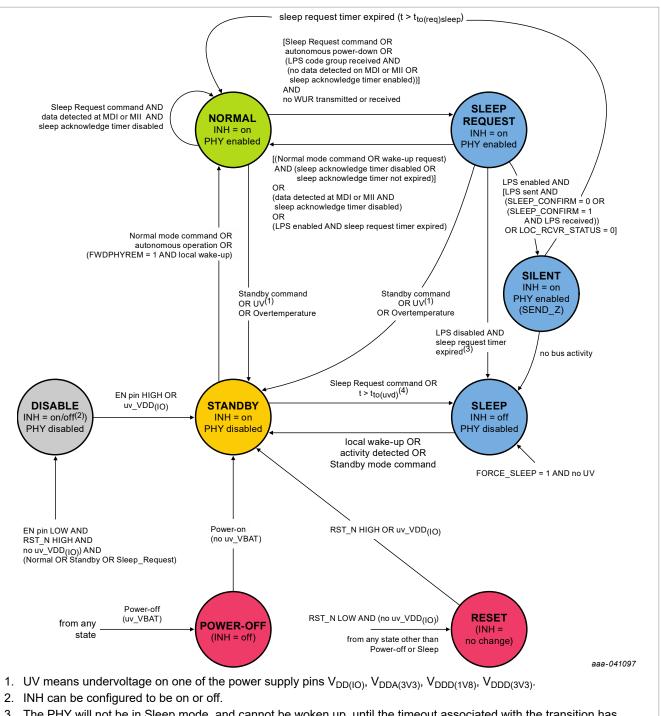

Sleep mode can be entered from Normal mode via the intermediate Sleep Request mode as well as from Standby mode, as shown in <u>Figure 7</u>. Note that the configuration register settings are maintained in Sleep mode.

If CLK\_IN\_OUT is used to provide the clock for other devices (e.g. other PHYs), the clock signal can be configured to remain active (CLK\_HOLD = 1) along with INH even when the PHY is in Sleep mode or disabled. When CLK\_HOLD = 1, the device enters Sleep mode automatically but remains active until a FORCE\_SLEEP SMI command is received. Note that this command forces the PHY to Sleep mode immediately (if it was not already in Sleep mode).

#### 6.3.1.6 Sleep Request mode

Sleep Request mode is an intermediate state used to initiate a transition to Sleep mode. In Sleep Request mode, the PHY transmits scrambler code with an encoded LPS command to inform the link partner about the request to enter Sleep mode.

The PHY sleep request timer ( $t_{to(req)sleep}$ ; see <u>Table 37</u>) starts when the TJA1101B enters Sleep Request mode. This timer determines the maximum length of time the PHY

remains in Sleep Request mode. The PHY switches to Sleep mode (via an intermediate step through Silent mode) on receiving LPS confirmation of the sleep request from the Link partner. If the timer expires before confirmation is received from the link partner, the PHY returns to Normal mode. This process is valid when LPS\_ACTIVE = 1 and SLEEP\_CONFIRM = 1.

If bit SLEEP\_ACK is not set when the PHY enters Sleep Request mode, it switches back to Normal mode if data is detected on MII or MDI (see <u>Table 21</u>). The DATA\_DET\_WU flag in the General status register is set and a WAKEUP interrupt is generated (if REMWUPHY = 1).

If SLEEP\_ACK is set when the PHY enters Sleep Request mode, the PHY sleep acknowledge timer ( $t_{to(ack)sleep}$ ; see <u>Table 37</u>) is started. While the timer is running, the PHY switches back to Normal mode in response to a host command or wake-up request. When the timer expires, LPS transmission begins to initiate a transition to Sleep mode. Data detected at MII or MDI is ignored.

INH is released when the PHY is in Sleep mode.

#### 6.3.1.7 Silent mode

Silent mode is an intermediate state between Sleep Request mode and Sleep mode. It is provided to allow time to switch off the transmitter after a sleep request has been accepted before entering Sleep mode. The TJA1101B switches to Sleep mode once the channel goes silent.

If the channel remains active for longer than  $t_{to(req)sleep}$ , the PHY returns to Normal mode and a SLEEP\_ABORT interrupt is generated.

#### 6.3.1.8 Reset mode

The TJA1101B switches to Reset mode from any mode except Power-off when pin RST\_N is held LOW for at least  $t_{det(rst)(max)}$ , provided the voltage on  $V_{DD(IO)}$  is above the undervoltage threshold.

When RST\_N goes HIGH again, or an undervoltage is detected on  $V_{DD(IO)}$ , the TJA1101B switches to Standby mode. All register bits are reset to their default values in Reset mode and the state of the pin strapping pins is captured.

## 6.3.2 Status of functional blocks in TJA1101B operating modes

<u>Table 7</u> presents an overview of the status of TJA1101B functional blocks in each operating mode.

|                    |                       |                           | oporating mode        | <u> </u>           | 1          |

|--------------------|-----------------------|---------------------------|-----------------------|--------------------|------------|

| Functional block   | Normal                | Standby                   | Sleep Request         | Sleep              | Disable    |

| MII                | on                    | high-ohmic <sup>[1]</sup> | on                    | high-ohmic         | high-ohmic |

| PMA/PCS-TX         | on                    | off                       | on                    | off                | off        |

| PMA/PCS-RX         | on                    | off                       | on                    | off                | off        |

| SMI                | on                    | on                        | on                    | on <sup>[2]</sup>  | off        |

| Activity detection | off                   | on                        | off                   | on                 | off        |

| Crystal oscillator | on/off <sup>[3]</sup> | off                       | on/off <sup>[3]</sup> | off <sup>[4]</sup> | off        |

| LDO_1V8            | on/off <sup>[5]</sup> | on/off <sup>[5]</sup>     | on/off <sup>[5]</sup> | off                | off        |

Table 7. Status of functional blocks in TJA1101B operating modes

13 / 58

### **100BASE-T1 PHY for automotive Ethernet**

Table 7. Status of functional blocks in TJA1101B operating modes...continued

| Functional block | Normal                | Standby               | Sleep Request         | Sleep                 | Disable               |

|------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| RST_N input      | on                    | on                    | on                    | off                   | on                    |

| EN input         | on                    | on                    | on                    | off                   | on                    |

| WAKE_IN_OUT      | on/off <sup>[6]</sup> | on/off <sup>[6]</sup> | on/off <sup>[6]</sup> | on/off <sup>[6]</sup> | off                   |

| INT_N output     | on                    | on                    | on                    | high-ohmic            | high-ohmic            |

| INH output       | on                    | on                    | on                    | off                   | on/off <sup>[7]</sup> |

| Temp detection   | on                    | on                    | on                    | off                   | off                   |

Outputs RXD[3:0], RXER and RXDV are LOW in Standby mode; the other MII pins are configured as inputs via internal 100 kΩ pull-down resistors. [1]

[2] Limited access to SMI registers in Sleep mode to allow mode control/wake-up via SMI.  $V_{DD(IO)}$  must be available. Configurable; depends on bits CLK\_MODE in the Common configuration register. The crystal will be off in Sleep mode unless bit CLK\_HOLD = 1 and bits CLK\_MODE = 00 or 01.

[3] [4] [5] Configurable; V<sub>DDD(1V8)</sub> can be supplied internally (bit LDO\_MODE in the Common configuration register LOW) or externally (bit LDO\_MODE HIGH).

Configurable. [6]

The behavior of the INH output in Disable mode is configurable and depends on bit CONFIG\_INH in the Common [7] configuration register.

## 6.4 Mode transitions

A mode transition diagram for the TJA1101B is shown in <u>Figure 7</u>. Abbreviations used in the mode transition diagram are defined in <u>Table 8</u>.

The following events, listed in order of priority, trigger mode transitions:

- Power on/off

- Undervoltage on V<sub>DD(IO)</sub>

- RST\_N input

- EN input

- Overtemperature or Undervoltage on V<sub>DDA(3V3)</sub>, V<sub>DDD(3V3)</sub>, V<sub>DDD(1V8)</sub>

- SMI command and wake-up (local, remote or forwarding)

#### Table 8. State diagram legend

| Transition              | Abbreviation                                | Description                                                                                                                                                                                                                 |  |

|-------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Silent to Normal        | sleep request timer expired                 | t > t <sub>to(req)sleep</sub>                                                                                                                                                                                               |  |

| Normal to Sleep Request | Sleep Request command                       | POWER_MODE = 1011                                                                                                                                                                                                           |  |

|                         | autonomous power-down                       | no frame transmission or reception for longer than $t_{to(pd)autn}$ AND AUTO_PWD = 1                                                                                                                                        |  |

|                         | LPS code group received                     | $\label{eq:linear_loss} \begin{array}{l} \mbox{LPS}_WUR\_DIS = 0 \ (\mbox{LPS}_WUR enabled) \ \mbox{AND} \\ \mbox{LPS}_RECEIVED = 1 \ \mbox{AND} \ t > t_{to(req)sleep} \ \mbox{AND} \\ \mbox{LPS}\_ACTIVE = 1 \end{array}$ |  |

|                         | no data detected on MDI or MII              | pcs_rx_dv = FALSE AND TXEN = LOW                                                                                                                                                                                            |  |

|                         | sleep acknowledge timer enabled             | SLEEP_ACK = 1                                                                                                                                                                                                               |  |

| Sleep Request to Normal | Normal mode command                         | POWER_MODE = 0011                                                                                                                                                                                                           |  |

|                         | wake-up request                             | (FWDPHYREM = 1 and WAKEUP = 1) OR WUR symbols received at the bus pins                                                                                                                                                      |  |

|                         | sleep acknowledge timer disabled            | SLEEP_ACK = 0                                                                                                                                                                                                               |  |

|                         | sleep acknowledge time-out time not expired | $t < t_{to(ack)sleep}$                                                                                                                                                                                                      |  |

|                         | data detected on MDI or MII                 | pcs_rx_dv = TRUE OR TXEN = HIGH                                                                                                                                                                                             |  |

|                         | LPS enabled                                 | LPS_WUR_DIS = 0                                                                                                                                                                                                             |  |

|                         | sleep request timer expired                 | $t > t_{to(req)sleep}$                                                                                                                                                                                                      |  |

| Normal to Normal        | data detected on MDI or MII                 | pcs_rx_dv = TRUE OR TXEN = HIGH                                                                                                                                                                                             |  |

|                         | sleep acknowledge timer disabled            | SLEEP_ACK = 0                                                                                                                                                                                                               |  |

| Sleep Request to Sleep  | LPS disabled                                | LPS_WUR_DIS = 1                                                                                                                                                                                                             |  |

|                         | sleep request timer expired                 | $t > t_{to(req)sleep}$                                                                                                                                                                                                      |  |

| Sleep Request to Silent | LPS enabled                                 | LPS_WUR_DIS = 0                                                                                                                                                                                                             |  |

| Standby to Normal       | autonomous operation                        | see <u>Section 6.6</u>                                                                                                                                                                                                      |  |

|                         |                                             |                                                                                                                                                                                                                             |  |

## **NXP Semiconductors**

# **TJA1101B**

## 100BASE-T1 PHY for automotive Ethernet

- The PHY will not be in Sleep mode, and cannot be woken up, until the timeout associated with the transition has expired (after t<sub>to(req)sleep</sub>).

- At power-on, after a transition from Power-off to Standby mode, undervoltage detection timeout is enabled once all supply voltages are available. When an undervoltage is detected, the TJA1101B switches to Sleep mode after t<sub>to(uvd)</sub>.

Figure 7. Mode transition diagram

#### **100BASE-T1 PHY for automotive Ethernet**

## 6.5 Sleep and wake-up forwarding concept

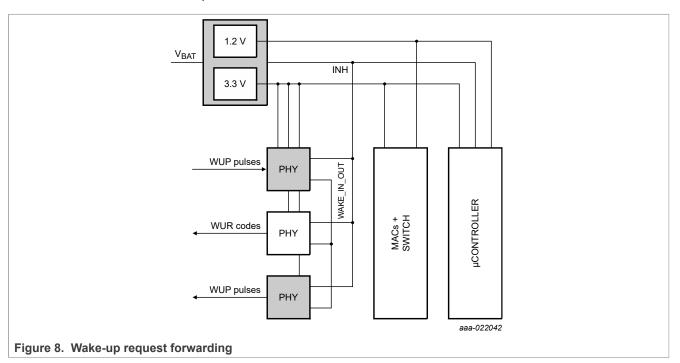

The sleep and wake-up forwarding concept of the TJA1101B is compliant with the OPEN Alliance Sleep/Wake-up specification. The TJA1101B features a wake-up request forwarding function that enables fast wake-up forwarding without the need for a switch, MAC or  $\mu$ C action. The wake-up forwarding principle is illustrated in Figure 8. The wake-up request can be forwarded via non-active (gray PHYs in the figure) or active links (white PHY). In the case of a non-active link, a wake-up pulse (WUP; duration t<sub>w(wake)</sub>) is transmitted, to be detected as activity at the link partner. For an active link, wake up request (WUR) scrambler code groups are sent.

The wake-up behavior of the PHY can be configured. This arrangement allows WAKE\_IN\_OUT to be used as a local wake-up or to have a mixed system with only some ports forwarding wake-up requests. The following configuration options are available and are selected via the SMI Configuration register 1 (Table 21):

REMWUPHY determines whether the PHY reacts to a remote wake-up request. FWDPHYREM determines whether the PHY forwards a wake-up request (via WAKE\_IN\_OUT) to its MDI. A WUP or WUR is sent, depending on the link status. LOCWUPHY determines whether the PHY should be woken up in response to a local wake-up event (forwarded via WAKE\_IN\_OUT)

FWDPHYLOC determines whether a wake-up event should be forwarded to other ports (i.e. should the WAKE\_IN\_OUT signal be activated).

The WAKE\_IN\_OUT signal features a programmable timeout to enable it to support a number of wake-up concepts (e.g. wake-up line). It reacts on a rising edge.

The wake-up detection time,  $t_{det(wake)}$  (see <u>Table 37</u>) on pin WAKE\_IN\_OUT is determined by register bit settings LOC\_WU\_TIM (see <u>Table 30</u>). The wake-up pulse duration ( $t_p$ ; see <u>Table 37</u>) is also determined by LOC\_WU\_TIM.

## 6.6 Autonomous operation

When the TJA1101B is configured for autonomous operation (either via pin strapping, see <u>Section 6.10</u>, or via bit AUTO\_OP in the Common configuration register, <u>Table 30</u>), it can operate and establish a link without further interaction with a host controller. On power-on or wake-up from Sleep mode, the TJA1101B goes directly to Normal mode once all supply voltages are available and the link-up process starts automatically. Host configuration (e.g. for link or mode control) will not be possible until the device is switched from autonomous to managed operation by resetting bit AUTO\_OP.

## 6.7 Autonomous power-down

If autonomous power-down is enabled for the PHY (AUTO\_PWD = 1), it goes to Sleep Request mode automatically if no Ethernet frames have been received at the MDI and (R)MII within the timeout time,  $t_{to(pd)autn}$ .

## 6.8 Test modes

Five test modes are supported. Only test modes 1, 2, 4 and 5 are included in the 100BASE-T1 specification [1]. The test modes can be selected individually via an SMI command in Normal mode while link control is disabled. Pin RXER is used as a reference clock output for test modes 1 to 4 (the nominal RXER function is disabled when test modes are active). No load should be connected when the reference clock is being measured.

#### 6.8.1 Test mode 1

Test mode 1 is used to test transmitter droop. In Test mode 1, the PHY transmits '+1' symbols for 600 ns followed by '-1' symbols for a further 600 ns. This sequence is repeated continuously.

## 6.8.2 Test mode 2

Test mode 2 is used to test transmitter timing jitter in Master mode. In Test mode 2, the PHY transmits the data symbol sequence  $\{+1, -1\}$  repeatedly. The transmission of the symbols is synchronized with the local external oscillator.

#### 6.8.3 Test mode 3

Test mode 3 is used to test transmitter timing jitter in Slave mode. In Test mode 3, the PHY transmits the data symbol sequence  $\{+1, -1\}$  repeatedly. The transmission of the symbols is synchronized with the local external oscillator.

#### 6.8.4 Test mode 4

Test mode 4 is used to test transmitter distortion. In Test mode 4, the PHY transmits the sequence of symbols generated by the scrambler polynomial gs1 = 1 + x9 + x11.

The bit sequence x0n, x1n is derived from the scrambler according to the following equations:

x0n = Scrn[0]

x1n = Scrn[1] XOR Scrn[1]

This stream of 3-bit nibbles is mapped to a stream of ternary symbols according to Table 9.

| Table 9. | Symbol | mapping | in | test | mode 4 |  |

|----------|--------|---------|----|------|--------|--|

| Table J. | Oymbol | mapping |    | ισσι | moue + |  |

| x1n | x0n | PAM-3 transmit symbol |

|-----|-----|-----------------------|

| 0   | 0   | 0                     |

| 0   | 1   | +1                    |

| 1   | 0   | 0                     |

| 1   | 1   | -1                    |

#### 6.8.5 Test mode 5

Test mode 5 is used to test the transmit PSD mask. In Test mode 5, the PHY transmits a random sequence of PAM-3 symbols.

#### 6.8.6 Slave jitter test

To enable the Slave jitter test in Normal mode, bit SLAVE\_JITTER\_TEST must be set to 1 before link control is enabled (LINK\_CONTROL = 1; see <u>Table 20</u>). During this test, the transmitter reference clock is fed to pin TXCLK.

## 6.9 Error diagnosis

#### 6.9.1 Undervoltage detection

The TJA1101B continuously monitors the status of the supply voltages. Once a supply voltage drops below the specified minimum operating threshold, the TJA1101B enters the fail-silent Standby mode and communication is halted. If an undervoltage is detected on  $V_{BAT}$ , the TJA1101B switches to Power-off mode.

At power-on, after a transition from Power-off to Standby mode, undervoltage detection timeout is enabled once all supply voltages are available. The timeout timer is started when an undervoltage is detected. If the undervoltage is still active when the timer expires (after  $t_{to(uvd)}$ ), the TJA1101B switches from Standby mode to Sleep mode.

The microcontroller can determine the source of the interruption by reading the contents of the External status register (Table 28). The under-voltage detection/recovery range is positioned immediately next to the operating range, without a gap. Since parameters are specified down to the minimum value of the under-voltage detection threshold, it is guaranteed that the behavior of the TJA1101B is fully specified and defined for all possible voltage condition on the supply pins.

## 6.9.2 Cabling errors

The TJA1101B can detect open and short circuits between the twisted-pair bus lines when neither of the link partners is transmitting (link control disabled). It may make sense to run the diagnostic before establishing the Ethernet link. When bit CABLE\_TEST in the Extended Control register (Table 20) is set to 1, test pulses are transmitted onto the transmission medium with a repetition rate of 666.6 kHz. The TJA1101B evaluates the reflected signals and uses impedance mismatch data along the channel to determine the quality of the link. The results of the cable test are available in the External status register

(Table 28) within  $t_{to(cbl\_tst)}$ . The tests performed and associated results are summarized in Table 10.

Table 10. Cable tests and results

The cable bus lines are designated BI\_DA+ and BI\_DA-, in alignment with 100BASE-T1 [1].

| BI_DA+                                    | BI_DA-                                    | Result                  |

|-------------------------------------------|-------------------------------------------|-------------------------|

| open                                      | open                                      | open detected           |

| + shorted to -                            | - shorted to +                            | short detected          |

| shorted to V <sub>DD</sub>                | open                                      | open detected           |

| open                                      | shorted to V <sub>DD</sub>                | open detected           |

| shorted to V <sub>DD</sub>                | shorted to V <sub>DD</sub>                | short detected          |

| shorted to GND                            | open                                      | open detected           |

| open                                      | shorted to GND                            | open detected           |

| shorted to GND                            | shorted to GND                            | short detected          |

| connected to active link partner (master) | connected to active link partner (master) | short and open detected |

## 6.9.3 Link stability

The Signal Quality Indicator (SQI) is the parameter used to estimate link stability. The PMA receive function monitors the SQI. Once the value falls below a configurable threshold (SQI\_FAILLIMIT), the link status is set to FAIL and communication is interrupted. The TJA1101B allows for adjusting the sensitivity of the PMA receive function by configuring this threshold. The microcontroller can always check the current value of the SQI via the SMI, allowing it to track a possible degradation in link stability.

#### 6.9.4 Link-fail counter

High losses and/or a noisy channel may cause the link to shut down when reception is no longer reliable. In such cases, the PHY generates a LINK\_STATUS\_FAIL interrupt. Retraining of the link begins automatically provided link control is enabled (LINK\_CONTROL = 1).

Bits LOC\_RCVR\_COUNTER and REM\_RCVR\_COUNTER in the Link-fail counter register (Table 29) are incremented after every link fail event. Both counters are reset when this register is read.

#### 6.9.5 Jabber detection

The Jabber detection function prevents the PHY being locked in the DATA state of the PCS Receive state diagram when the End-of-Stream Delimiters, ESD1 and ESD2, are not detected.

The maximum time the PHY can reside in the DATA state is limited to  $t_{to(PCS-RX)}$  (rcv\_max\_timer in the IEEE specification [1]). After this time, the PCS-RX state machine is reset, triggering a transition to PHY Idle state.

#### 6.9.6 Polarity detection

A polarity error occurs when the two signal wires in the twisted pair cable are swapped. According to the IEEE specification [1], the polarity is always observed to be correct by the Master PHY; only the Slave is allowed to correct the polarity. When the TJA1101B is in Slave configuration, it can detect if the ternary symbols sent from the Master PHY are received with the wrong polarity and will correct this error internally and set the POLARITY\_DETECT bit in the External status register (<u>Table 28</u>). Irrespective of the Master or Slave mode, the host can overwrite and swap the default MDI polarity by setting MDI\_POL in Configuration Register 3 (<u>Table 31</u>).

#### 6.9.7 Interleave detection

A 100BASE-T1 PHY can send two different interleave sequences of ternary symbols (TAn, TBn) or (TBn, TAn). The receivers in the TJA1101B are able to de-interleave both sequences. The order of the ternary symbols detected by the receiver is indicated by the INTERLEAVE\_DETECT bit in the External status register (<u>Table 28</u>).

#### 6.9.8 Loopback modes

The TJA1101B supports three loopback modes:

- Internal loopback (PCS loopback in accordance with IEEE 802.3bw)

- External loopback

- Remote loopback

To run the PHY in loopback mode, the LOOPBACK control bit in the Basic control register should be set before enabling link control.

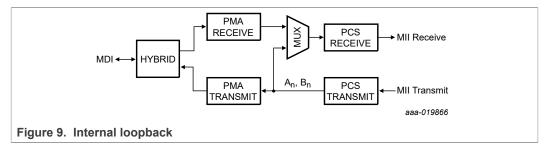

#### 6.9.8.1 Internal loopback

In Internal loopback mode, the PCS receive function gets the ternary symbols  $A_n$  and  $B_n$  directly from the PCS transmit function as shown in Figure 9. This action allows the MAC to compare packets sent through the MII transmit function with packets received from the MII receive function and, therefore, to validate the functionality of the 100BASE-T1 PCS function.

#### 6.9.8.2 External loopback

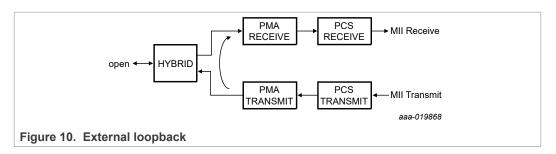

In External loopback mode, the PMA receive function receives signals directly from the PMA transmit function as shown in <u>Figure 10</u>. This external loopback test allows the MAC to compare packets sent through the MII transmit function with packets received from the MII receive function and, therefore, to validate the functionality of the 100BASE-T1 PCS and PMA functions.

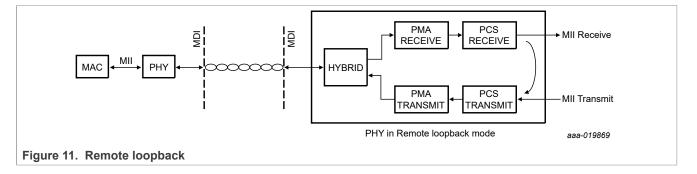

#### 6.9.8.3 Remote loopback

In Remote loopback mode, the packet received by the link partner at the MDI is passed through the PMA receive and PCS receive functions and forwarded to the PCS transmit function, which in turn sends it back to the link partner from where it came. The PCS receive data is made available at the MII. Remote loopback allows the MAC to compare the packets sent to the MDI with the packets received back from the MDI and, therefore, to validate the functionality of the physical channel, including both 100BASE-T1 PHYs.

## 6.10 Hardware configuration

A number of pins are provided to allow default values for a number of features to be hardware-configured, without microcontroller interaction. The pull-up/down behavior of these pins is sensed at power-up and after a reset. A pull-up behavior is coded as logic 1, while a pull-down behavior is coded as logic 0. The results are stored in the corresponding SMI registers. All pre-configuration settings (except for the PHY addresses) can be overwritten via SMI commands.

Pin strapping at pins 23 (PHYAD2) and 24 (PHYAD1) determines bits 2 and 1, respectively, of the PHY address used for the SMI address/Cipher scrambler. The PHY address cannot be changed once the PHY has been configured. Besides the address configured via pin strapping, the TJA1101B can always be accessed via address 0.

Table 11 gives an overview of the functions to be configured via hardware pins.

| Symbol       | Pin          | Value | Description                           |

|--------------|--------------|-------|---------------------------------------|

| MASTER_SLAVE | 22 (CONFIG0) | 0     | PHY configured as Slave               |

|              |              | 1     | PHY configured as Master              |

| AUTO_OP      | 21 (CONFIG1) | 0     | managed operation                     |

|              |              | 1     | autonomous operation                  |

| MII_MODE     | 17 (CONFIG3) | 00    | Normal MII mode                       |

|              | 18 (CONFIG2) | 01    | RMII mode (50 MHz input on REF_CLK)   |

|              |              | 10    | RMII mode (50 MHz output on REF_CLK)  |

|              |              | 11    | Reverse MII mode                      |

| PHYAD[2:1]   | 23 (PHYAD2)  | -     | bit 2 of PHY address used for the SMI |

|              | 24 (PHYAD1)  | -     | bit 1 of PHY address used for the SMI |

| LDO_MODE     | 4 (SEL_1V8)  | 0     | internal 1.8 V LDO enabled            |

|              |              | 1     | external 1.8 V supply                 |

| Table 11  | Pin | stranning | configuration |

|-----------|-----|-----------|---------------|

| Table II. | ГШ  | Suapping  | connyuration  |

## 6.11 SMI registers

### 6.11.1 Register mapping overview

| Register index (dec) | Register name                 | Group        |

|----------------------|-------------------------------|--------------|

| 0                    | Basic control register        | Basic        |

| 1                    | Basic status register         | Basic        |

| 2                    | PHY identification register 1 | Extended     |

| 3                    | PHY identification register 2 | Extended     |

| 15                   | Extended status register      | Extended     |

| 16                   | PHY identification register 3 | NXP specific |

| 17                   | Extended control register     | NXP specific |

| 18                   | Configuration register 1      | NXP specific |

| 19                   | Configuration register 2      | NXP specific |

| 20                   | Symbol error counter register | NXP specific |

| 21                   | Interrupt source register     | NXP specific |

| 22                   | Interrupt enable register     | NXP specific |

| 23                   | Communication status register | NXP specific |

| 24                   | General status register       | NXP specific |

| 25                   | External status register      | NXP specific |

| 26                   | Link-fail counter register    | NXP specific |

| 27                   | Common configuration register | NXP specific |

| 28                   | Configuration register 3      | NXP specific |

# Table 12. SMI register mapping

#### Table 13. Register notation

| Notation | Description                             |

|----------|-----------------------------------------|

| R/W      | Read/write                              |

| R        | Read only                               |

| LH       | Latched HIGH; must be read out to reset |

| LL       | Latched LOW; must be read out to reset  |

| SC       | Self-clearing                           |

| PS       | Pin strapping                           |

## 6.11.2 TJA1101B registers

| Bit | Symbol                  | Access    | Value            | Description                                                                                                                                                                          |

|-----|-------------------------|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | RESET                   | R/W       |                  | software reset control:                                                                                                                                                              |

|     |                         | SC        | 0 <sup>[1]</sup> | normal operation                                                                                                                                                                     |

|     |                         |           | 1                | PHY reset                                                                                                                                                                            |

| 14  | LOOPBACK <sup>[2]</sup> | R/W       |                  | loopback control:                                                                                                                                                                    |

|     |                         |           | 0 <sup>[1]</sup> | normal operation                                                                                                                                                                     |

|     |                         | 1         | 1                | loopback mode                                                                                                                                                                        |

| 13  | SPEED_SELECT (LSB)      | R/W       | [3]              | speed select (LSB):                                                                                                                                                                  |

|     |                         |           | 0                | 10 Mbit/s if SPEED_SELECT (MSB) = 0<br>1000 Mbit/s if SPEED_SELECT (MSB) = 1                                                                                                         |

|     |                         |           | 1 <sup>[1]</sup> | 100 Mbit/s if SPEED_SELECT (MSB) = 0<br>reserved if SPEED_SELECT (MSB) = 1                                                                                                           |

| 12  | AUTONEG_EN              | R/W<br>SC | 0 <sup>[1]</sup> | Auto negotiation not supported; always 0; a write access is ignored.                                                                                                                 |

| 11  | POWER_DOWN              | R/W       |                  | Standby power down enable:                                                                                                                                                           |

|     |                         |           | 0 <sup>[1]</sup> | normal operation (clearing this bit automatically triggers<br>a transition to Normal mode, provided control bits<br>POWER_MODE are set to 0011 Normal mode, see<br><u>Table 20</u> ) |

|     |                         |           | 1                | power down and switch to Standby mode (provided<br>ISOLATE = 0; ignored if ISOLATE = 1 and<br>CONTROL_ERR interrupt generated)                                                       |

| 10  | ISOLATE                 | R/W       |                  | PHY isolation:                                                                                                                                                                       |

|     |                         |           | 0 <sup>[1]</sup> | normal operation                                                                                                                                                                     |

|     |                         |           | 1                | isolate PHY from MII/RMII (provided POWER_DOWN = 0; ignored if POWER_DOWN = 1 and CONTROL_ERR interrupt generated)                                                                   |

| 9   | RE_AUTONEG              | R/W<br>SC | 0 <sup>[1]</sup> | Auto negotiation not supported; always 0; a write access is ignored.                                                                                                                 |

| 8   | DUPLEX_MODE             | R/W       | 1 <sup>[1]</sup> | only full duplex supported; always 1; a write access is ignored.                                                                                                                     |

| 7   | COLLISION_TEST          | R/W       | 0 <sup>[1]</sup> | COL signal test not supported; always 0; a write access is ignored.                                                                                                                  |

| 6   | SPEED_SELECT (MSB)      | R/W       | [3]              | speed select (MSB):                                                                                                                                                                  |

|     |                         |           | 0 <sup>[1]</sup> | 10 Mbit/s if SPEED_SELECT (LSB) = 0<br>100 Mbit/s if SPEED_SELECT (LSB) = 1                                                                                                          |

|     |                         |           | 1                | 1000 Mbit/s if SPEED_SELECT (LSB) = 0<br>reserved if SPEED_SELECT (LSB) = 1                                                                                                          |

| 5   | UNIDIRECT_EN            | R/W       |                  | unidirectional enable when bit 12 (AUTONEG_EN) = 0 and bit 8 (DUPLEX_MODE) = 1:                                                                                                      |

#### Table 14. Basic control register (register 0)

TJA1101B Product data sheet

|--|

| Bit | Symbol   | Access | Value                | Description                                                                                                  |  |  |

|-----|----------|--------|----------------------|--------------------------------------------------------------------------------------------------------------|--|--|

|     |          |        | 0 <sup>[1]</sup>     | enable transmit from MII only when the PHY has determined that a valid link has been established             |  |  |

|     |          |        | 1                    | enable transmit from MII regardless of whether the PHY has determined that a valid link has been established |  |  |

| 4:0 | reserved | R/W    | 00000 <sup>[1]</sup> | always write 00000; ignore on read                                                                           |  |  |

Default value. [1]

The loopback mode is selected via bits LOOPBACK\_MODE in the Extended control register (<u>Table 20</u>). Speed Select: 00: 10 Mbit/s; 01: 100 Mbit/s; 10: 1000 Mbit/s; 11: reserved; a write access value other than 01 is ignored. [2] [3]

| Bit | Symbol                  | Access | Value               | Description                                                                                                       |

|-----|-------------------------|--------|---------------------|-------------------------------------------------------------------------------------------------------------------|

| 15  | 100BASE-T4              | R      | 0 <sup>[1]</sup>    | PHY not able to perform 100BASE-T4                                                                                |

|     |                         |        | 1                   | PHY able to perform 100BASE-T4                                                                                    |

| 14  | 100BASE-X_FD            | R      | 0 <sup>[1]</sup>    | PHY not able to perform 100BASE-X full-duplex                                                                     |

|     |                         |        | 1                   | PHY able to perform 100BASE-X full-duplex                                                                         |

| 13  | 100BASE-X_HD            | R      | 0 <sup>[1]</sup>    | PHY not able to perform 100BASE-X half-duplex                                                                     |

|     |                         |        | 1                   | PHY able to perform 100BASE-X half-duplex                                                                         |

| 12  | 10Mbps_FD               | R      | 0 <sup>[1]</sup>    | PHY not able to perform 10 Mbit/s full-duplex                                                                     |

|     |                         |        | 1                   | PHY able to perform 10 Mbit/s full-duplex                                                                         |

| 11  | 10Mbps_HD               | R      | 0 <sup>[1]</sup>    | PHY not able to perform 10 Mbit/s half-duplex                                                                     |

|     |                         |        | 1                   | PHY able to perform 10 Mbit/s half-duplex                                                                         |

| 10  | 100BASE-T2_FD           | R      | 0 <sup>[1]</sup>    | PHY not able to perform 100BASE-T2 full-duplex                                                                    |

|     |                         |        | 1                   | PHY able to perform 100BASE-T2 full-duplex                                                                        |

| 9   | 100BASE-T2_HD           | R      | 0 <sup>[1]</sup>    | PHY not able to perform 100BASE-T2 half-duplex                                                                    |

|     |                         |        | 1                   | PHY able to perform 100BASE-T2 half-duplex                                                                        |

| 8   | 8 EXTENDED_STATUS       | R      | 0                   | no extended status information in register 15h                                                                    |

|     |                         |        | 1 <sup>[1]</sup>    | extended status information in register 15h                                                                       |

| 7   | UNIDIRECT_ ABILITY      | R      | 0                   | PHY able to transmit from MII only when the PHY has determined that a valid link has been established             |

|     |                         |        | 1 <sup>[1]</sup>    | PHY able to transmit from MII regardless of whether the PHY has determined that a valid link has been established |

| 6   | MF_PREAMBLE_SUPPRESSION | R      | 0                   | PHY will not accept management frames with preamble suppressed                                                    |

|     |                         |        | 1 <sup>[1]</sup>    | PHY will accept management frames with preamble suppressed                                                        |

| 5   | AUTONEG_COMPLETE        | R      | 0                   | Autonegotiation process not completed                                                                             |

|     |                         |        | 1 <sup>[1]</sup>    | Autonegotiation process completed                                                                                 |

| 4   | REMOTE_FAULT            | R      | 0 <sup>[1][2]</sup> | no remote fault condition detected                                                                                |

|     |                         | LH     | 1                   | remote fault condition detected                                                                                   |

#### Table 15. Basic status register (register 1)

### **100BASE-T1 PHY for automotive Ethernet**

| Bit    | Symbol              | Access | Value                  | Description                             |

|--------|---------------------|--------|------------------------|-----------------------------------------|

| 3 AUTC | AUTONEG_ABILITY     | R      | 0 <sup>[1]</sup>       | PHY not able to perform Autonegotiation |

|        |                     |        | 1                      | PHY able to perform Autonegotiation     |

| 2      | 2 LINK_STATUS       | R      | 0 <sup>[1][2][3]</sup> | link is down                            |

|        | LL                  | 1      | link is up             |                                         |

| 1      | JABBER_DETECT       | R      | 0 <sup>[1][2]</sup>    | no jabber condition detected            |

|        |                     | LH     | 1                      | jabber condition detected               |

| 0      | EXTENDED_CAPABILITY | R      | 0                      | basic register set capabilities only    |

|        |                     |        | 1 <sup>[1]</sup>       | extended register capabilities          |

#### Table 15. Basic status register (register 1)...continued

[1] [2] [3]

Default value. Reset to default value when link control is disabled (LINK\_CONTROL = 0). According to IEEE 802.3; LINK\_STATUS = 1 when LOC\_RCVR\_STATUS = 1.

#### Table 16. PHY identification register 1 (register 2)

| Bit  | Symbol | Access | Value                | Description                                                          |

|------|--------|--------|----------------------|----------------------------------------------------------------------|

| 15:0 | PHY_ID | R      | 0180h <sup>[1]</sup> | bits 3 to 18 of the Organizationally Unique Identifier $(OUI)^{[2]}$ |

Default value. OUI = 00.60.37h. [1]

[2]

#### Table 17. PHY identification register 2 (register 3)

| Bit   | Symbol      | Access | Value                 | Description                             |

|-------|-------------|--------|-----------------------|-----------------------------------------|

| 15:10 | PHY_ID      | R      | 110111 <sup>[1]</sup> | bits 19 to 24 of the OUI <sup>[2]</sup> |

| 9:4   | TYPE_NO     | R      | 010000                | six-bit manufacturer's type number      |

| 3:0   | REVISION_NO | R      | 0010 <sup>[1]</sup>   | four-bit manufacturer's revision number |

Default value. OUI = 00.60.37h. [1]

[2]

#### Table 18. PHY identification register 3 (Register 16)

| Bit  | Symbol     | Access | Value              | Description                                   |

|------|------------|--------|--------------------|-----------------------------------------------|

| 15:8 | reserved   | R      | -                  |                                               |

| 7:0  | VERSION_NO | R      | xxh <sup>[1]</sup> | 8-bit manufacturer's firmware revision number |

[1] Default value.

#### Table 19. Extended status register (register 15)

| Bit | Symbol        | Access | Value            | Description                                    |

|-----|---------------|--------|------------------|------------------------------------------------|

| 15  | 1000BASE-X_FD | R      | 0 <sup>[1]</sup> | PHY not able to perform 1000BASE-X full-duplex |

|     |               |        | 1                | PHY able to perform 1000BASE-X full-duplex     |

TJA1101B Product data sheet

## 100BASE-T1 PHY for automotive Ethernet

| Bit  | Symbol            | Access | Value               | Description                                    |

|------|-------------------|--------|---------------------|------------------------------------------------|

| 14   | 4 1000BASE-X_HD F | R      | 0 <sup>[1]</sup>    | PHY not able to perform 1000BASE-X half-duplex |

|      |                   |        | 1                   | PHY able to perform 1000BASE-X half-duplex     |

| 13   | 1000BASE-T_FD     | R      | 0 <sup>[1]</sup>    | PHY not able to perform 1000BASE-T full-duplex |

|      |                   |        | 1                   | PHY able to perform 1000BASE-T full-duplex     |

| 12   | 1000BASE-T_HD     | R      | 0 <sup>[1]</sup>    | PHY not able to perform 1000BASE-T half-duplex |

|      |                   |        | 1                   | PHY able to perform 1000BASE-T half-duplex     |

| 11:8 | reserved          | R      | 0000 <sup>[1]</sup> | always 0000; ignore on read                    |

| 7    | 100BASE-T1        | R      | 0                   | PHY not able to 1-pair 100BASE-T1 100 Mbit/s   |

|      |                   |        | 1 <sup>[1]</sup>    | PHY able to 1-pair 100BASE-T1 100 Mbit/s       |

| 6    | 1000BASE-RTPGE    | R      | 0 <sup>[1]</sup>    | PHY not able to support RTPGE                  |

|      |                   |        | 1                   | PHY supports RTPGE                             |

| 5:0  | reserved          | R      | -                   | ignore on read                                 |

|      |                   |        | -                   | PHY supports RTPGE                             |

#### Table 19. Extended status register (register 15)...continued

[1] Default value.

#### Table 20. Extended control register (register 17)

| Bit   | Symbol                           | Access    | Value               | Description                            |

|-------|----------------------------------|-----------|---------------------|----------------------------------------|

| 15    | LINK_CONTROL                     | R/W       | [1]                 | link control enable:                   |

|       |                                  |           | 0                   | link control disabled                  |

|       |                                  |           | 1                   | link control enabled                   |

| 14:11 | POWER_MODE                       | R/W       | [2]                 | operating mode select:                 |

|       |                                  |           | 0000 <sup>[3]</sup> | no change                              |

|       |                                  |           | 0011                | Normal mode (command)                  |

|       |                                  |           | 1001                | Silent mode (read only)                |

|       |                                  |           | 1010                | Sleep mode (read only)                 |

|       |                                  |           | 1011                | Sleep Request mode (command)           |