## **FS5600**

# Automotive buck regulator and controller with voltage monitors and watchdog timer

Rev. 2 — 1 June 2021

Product data sheet

## 1 General Description

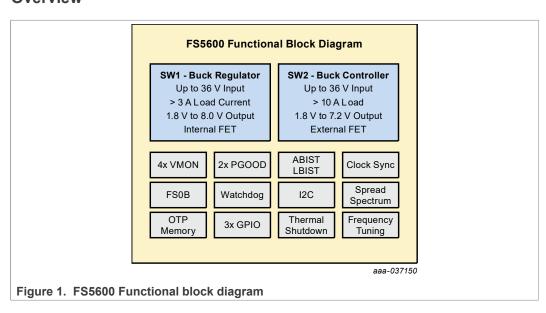

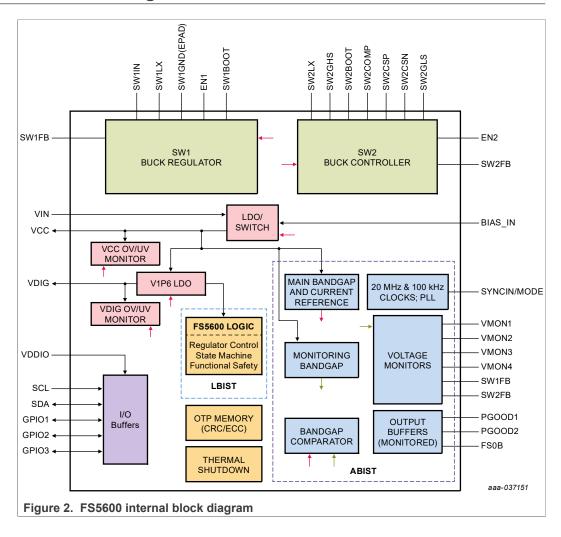

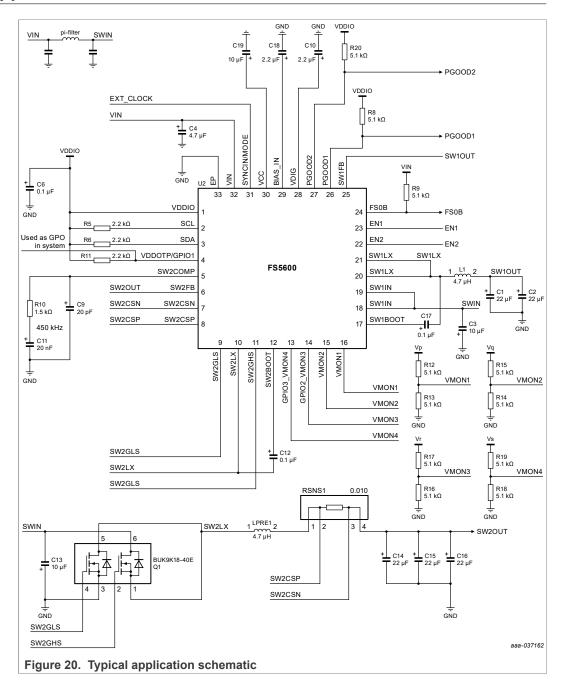

The FS5600 integrates a battery connected DC-DC controller with external FETs and a battery connected DC-DC converter with internal FETs. In addition, it offers functional safety features such as independent voltage monitors, windowed watchdog timer, I/O monitoring via ERRMON and FCCU and built-in self-test.

Automotive buck regulator and controller with voltage monitors and watchdog timer

#### 2 Features and Benefits

- 2 x High-Voltage Buck Converters:

- Buck Controller External FETs 900 mA gate drive current

- Buck Regulator Internal FETs 3 A+ load capability

- ±2 % Output Accuracy

- 250 kHz to 3 MHz switching frequency

- High-efficiency PFM mode

- · Safety Features:

- Available in Enhanced ASIL B, ASIL B, and QM variations

- 2 internal and up to 4 high-accuracy external voltage monitors

- Windowed Watchdog Timer

- ERRMON and FCCU monitoring

- 2 x PGOOD and 1 x FS0B outputs

- ABIST and LBIST for latest failure check

- GPIOs for seamless operation with PF PMICs

- Rated from –40 °C to 150 °C T<sub>J</sub>

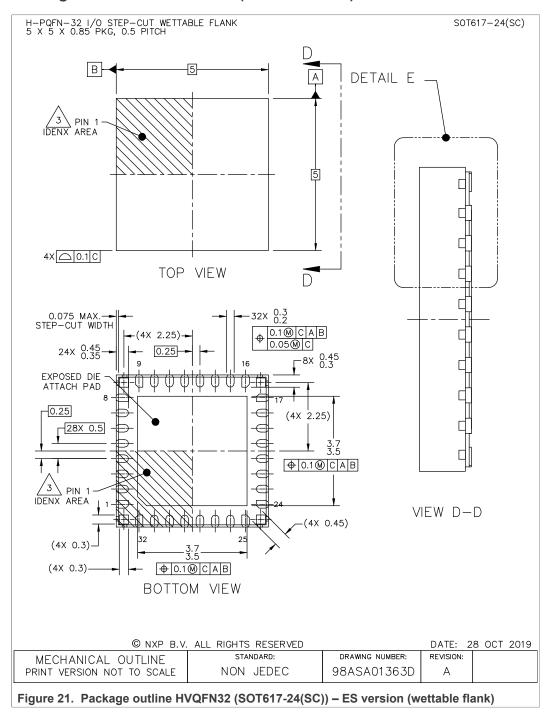

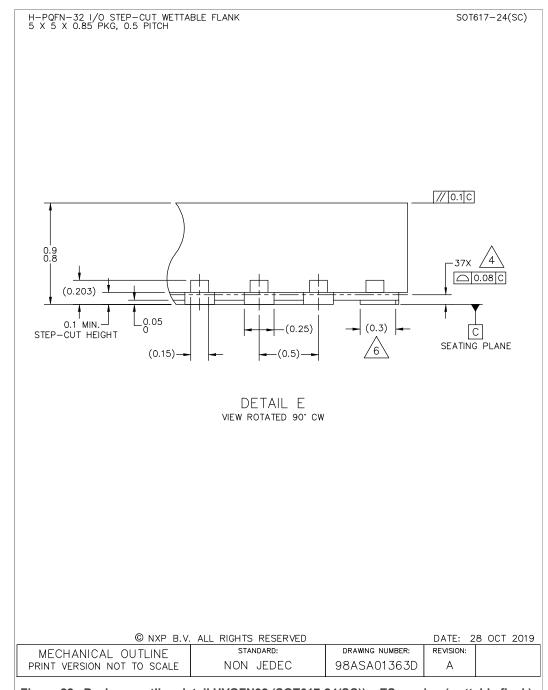

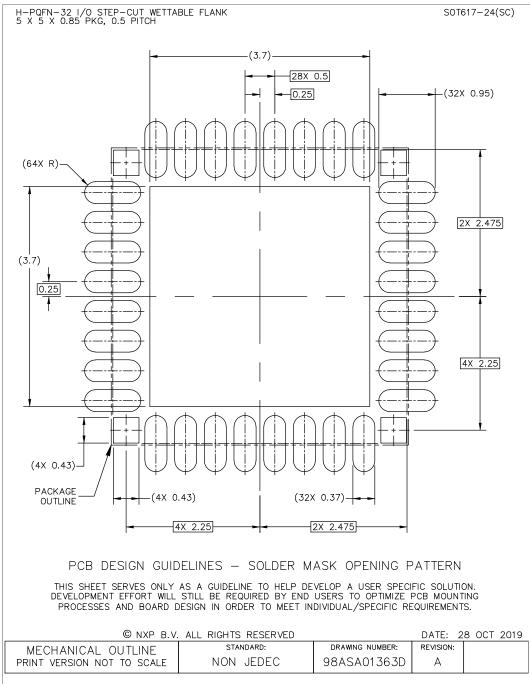

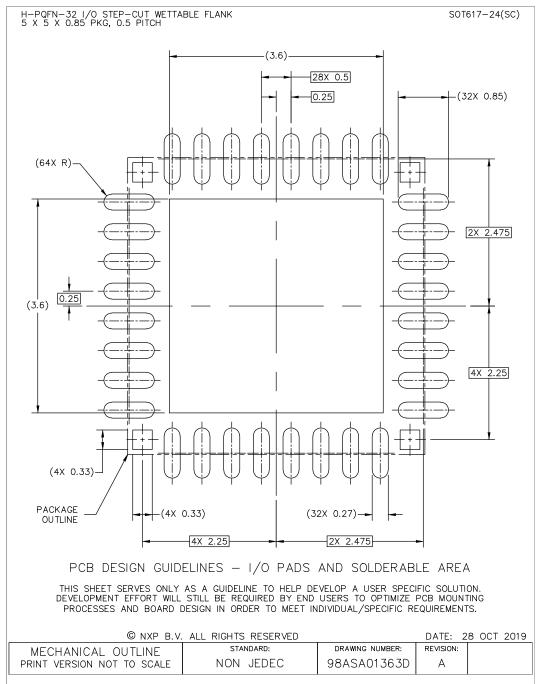

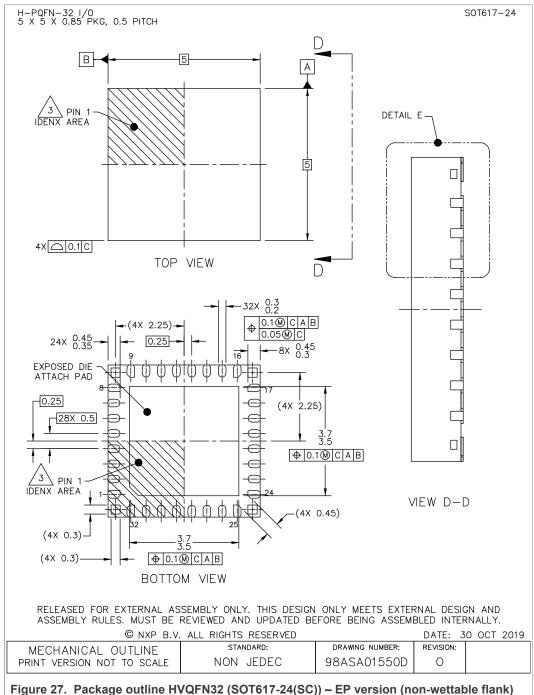

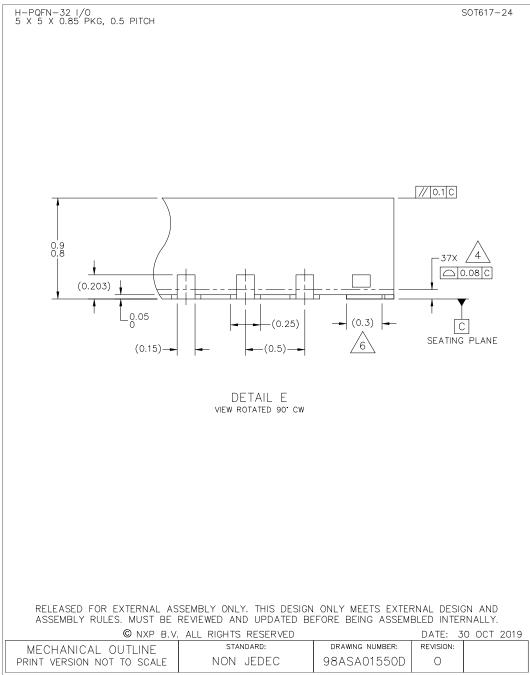

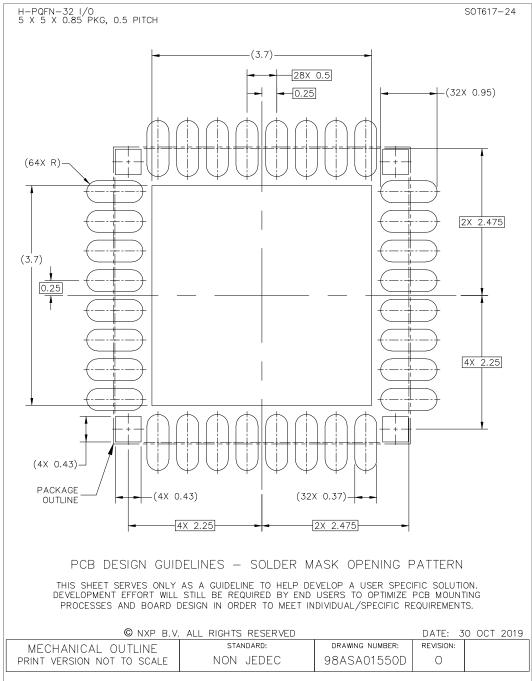

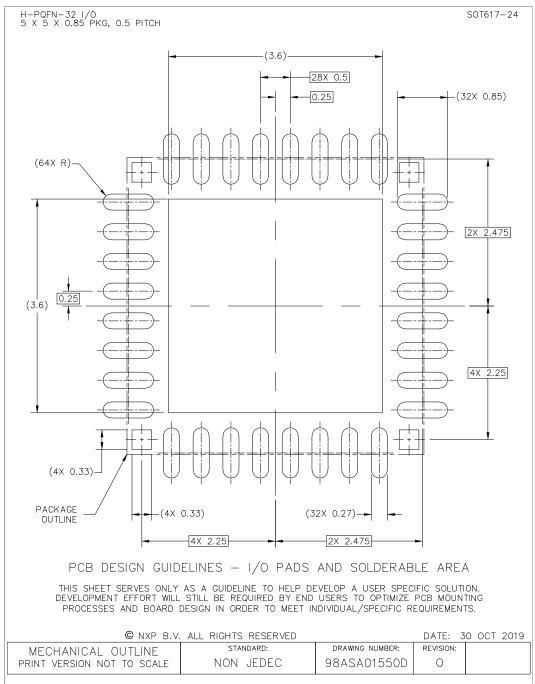

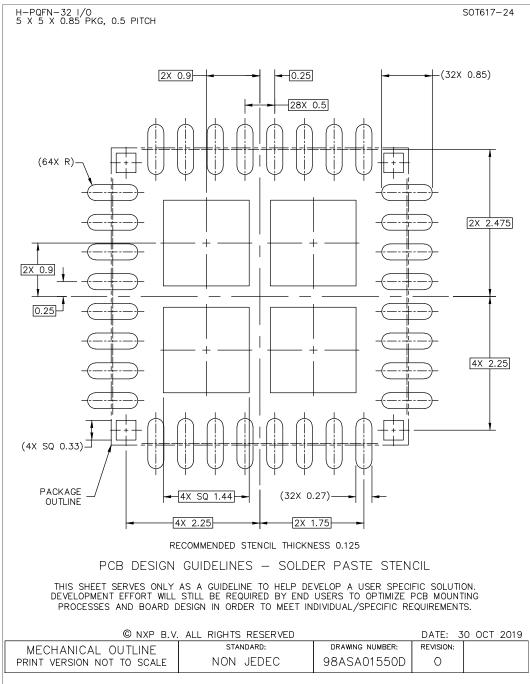

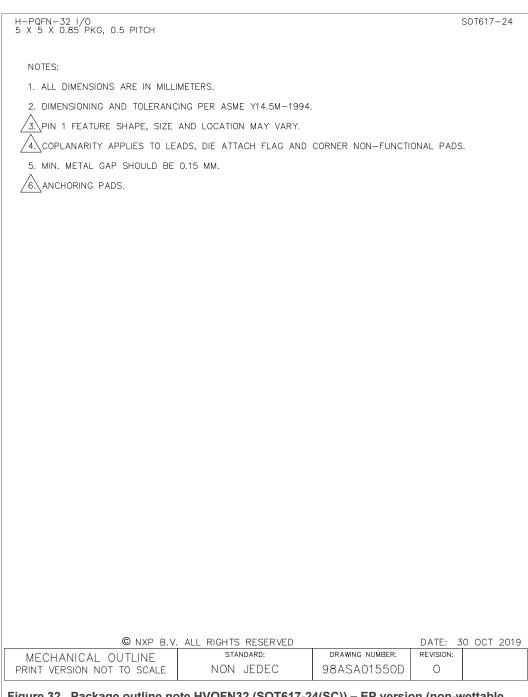

- 32-Ld 5 mm x 5 mm QFN

- AEC-Q100 Grade-1 Qualified

#### 2.1 Overview

Automotive buck regulator and controller with voltage monitors and watchdog timer

## 3 Applications

QM to ASIL D automotive applications such as:

- Infotainment / Cluster / Driver Awareness

- Telematics

- V2X

- Radar

- Vision

- ADAS

- · Sensor fusion

Additional safety mechanisms may be needed for ASIL D compliance in the system level. FS5600 is developed to meet ASIL B requirements.

Automotive buck regulator and controller with voltage monitors and watchdog timer

## 4 Ordering Information

The FS5600 is offered in QM, ASIL B, and Enhanced ASIL B versions. The Enhanced ASIL B version features a Challenger Watchdog and Logic BIST (LBIST) which may be used to achieve ASIL D functional safety at the system level. Additional safety mechanisms may be needed at the system level for ASIL D compliance.

Table 1. Device options

| Feature                             | QM Version | ASIL B Version | Enhanced ASIL B<br>Version |

|-------------------------------------|------------|----------------|----------------------------|

| SW1 – Integrated FET buck converter | Yes        | Yes            | Yes                        |

| SW2 – External FET buck controller  | Yes        | Yes            | Yes                        |

| GPOs for system sequence control    | Yes        | Yes            | Yes                        |

| PGOOD1 and PGOOD2 output            | Yes        | Yes            | Yes                        |

| Windowed Watchdog Timer             | No         | Yes (Simple)   | Yes (Challenger)           |

| 4 External Voltage Monitors (VMON)  | No         | Yes            | Yes                        |

| ERRMON Monitoring (muxed with VMON) | No         | Yes            | Yes                        |

| FCCU Monitoring (muxed with VMON)   | No         | Yes            | Yes                        |

| FS0B output                         | No         | Yes            | Yes                        |

| ABIST                               | No         | Yes            | Yes                        |

| LBIST                               | No         | No             | Yes                        |

| I <sup>2</sup> C CRC                | No         | Yes            | Yes                        |

Table 2. Ordering information

| Part number    | Target<br>market | Safety<br>grade    | OTP ID                                             | SW1              | SW2              | Package drawing |

|----------------|------------------|--------------------|----------------------------------------------------|------------------|------------------|-----------------|

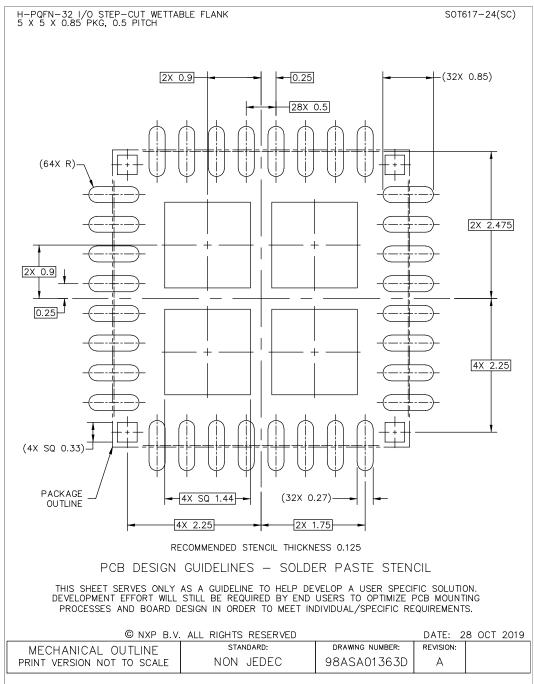

| MFS5600AMMA0ES | Automotive       | QM                 | A0 – Non-programmed                                | _                | _                | SOT617-24(SC)   |

| MFS5600AMBA0ES | Automotive       | ASIL B             | A0 – Non-programmed                                | _                | _                | SOT617-24(SC)   |

| MFS5600AMEA0ES | Automotive       | Enhanced<br>ASIL B | A0 – Non-programmed                                | _                | _                | SOT617-24(SC)   |

| MFS5600AVMA0EP | Industrial       | QM                 | A0 – Non-programmed                                | _                | _                | SOT617-24       |

| MFS5600AMMA7ES | Automotive       | QM                 | https://www.nxp.com/<br>MFS5600A7ES-OTP-<br>Report | 5.0 V<br>450 kHz | 3.3 V<br>450 kHz | SOT617-24(SC)   |

| MFS5600AMMA8ES | Automotive       | QM                 | https://www.nxp.com/<br>MFS5600A8ES-OTP-<br>Report | 3.3 V<br>450 kHz | 5.0 V<br>450 kHz | SOT617-24(SC)   |

Automotive buck regulator and controller with voltage monitors and watchdog timer

## 5 FS5600 Internal Block Diagram

Automotive buck regulator and controller with voltage monitors and watchdog timer

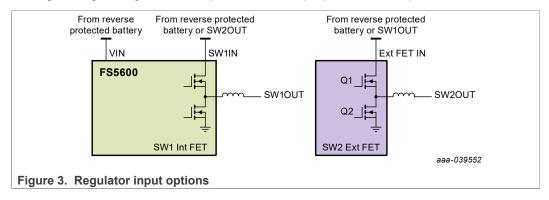

## 6 Regulator Input Configurations

Input to SW1 and SW2 may be applied directly from a reverse protected automotive battery, or from the output of the other regulator as shown below. Ensure that Enable for the regulator goes high after its input is stable for proper soft-start operation.

Automotive buck regulator and controller with voltage monitors and watchdog timer

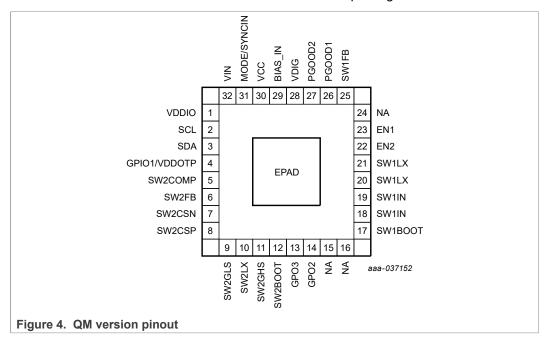

## 7 Pinout and Pin Description

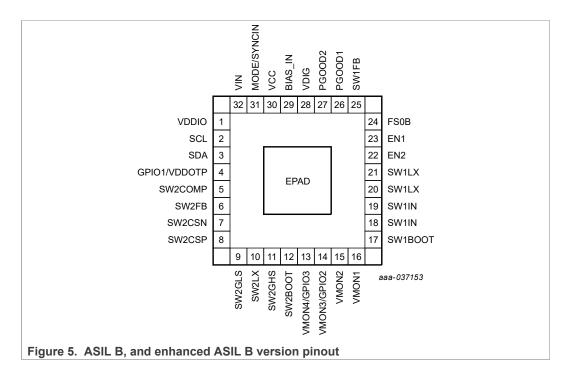

The FS5600 is offered in a 32-Ld 5 mm x 5 mm WF-QFN package.

## Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 3. Pin description

| Pin<br>number | Pin name                                | Description                                                                                                                                            | Absolute<br>maximum<br>voltage rating | Connection if not used |

|---------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------|

| 1             | VDDIO                                   | $I^2C$ I/O driver supply. Connect to 1.8 V or 3.3 V on the board. Bypass with 0.1 $\mu F$ capacitor.                                                   | –0.3 V to 5.5 V                       | Connect to VCC         |

| 2             | SCL                                     | I <sup>2</sup> C clock line. Pullup to VDDIO on board.                                                                                                 | –0.3 V to 5.5 V                       | Connect to ground      |

| 3             | SDA                                     | I <sup>2</sup> C data line. Pullup to VDDIO on board.                                                                                                  | –0.3 V to 5.5 V                       | Connect to ground      |

| 4             | GPIO1/VDDOTP                            | General-purpose input/output pin. Used as VDDOTP during development.                                                                                   | –0.3 V to 10 V                        | Connect to ground      |

| 5             | SW2COMP                                 | SW2 compensation pin. Connect to external compensation network.                                                                                        | –0.3 V to 5.5 V                       | Connect to ground      |

| 6             | SW2FB                                   | SW2 output voltage feedback. Use external or internal resistor divider for SW2 outputs ≤ 5.5 V. Use external resistor divider for SW2 outputs > 5.5 V. | -0.3 V to 7.5 V                       | Connect to ground      |

| 7             | SW2CSN                                  | SW2 current sense feedback (-ve). Route differentially with SW2CSP to sense circuitry.                                                                 | –0.3 V to 7.5 V                       | Connect to ground      |

| 8             | SW2CSP                                  | SW2 current sense feedback (+ve). Route differentially with SW2CSN to sense circuitry.                                                                 | –0.3 V to 7.5 V                       | Connect to ground      |

| 9             | SW2GLS                                  | SW2 low side MOSFET gate output. Connect to gate of external low side MOSFET.                                                                          | –0.3 V to 5.5 V                       | Leave floating         |

| 10            | SW2LX                                   | SW2 switching node. High side gate drive return path. Route parallel to SW2GHS trace on the board.                                                     | -0.3 V to 40 V                        | Leave floating         |

| 11            | SW2GHS                                  | SW2 high side MOSFET gate output. Connect to gate of external high side MOSFET.                                                                        | -0.3 V to<br>(SW2BOOT +<br>0.3 V)     | Leave floating         |

| 12            | SW2BOOT                                 | SW2 bootstrap pin. Connect bootstrap capacitor between SW2BOOT and SW2LX.                                                                              | -0.3 V to V <sub>SW2LX</sub><br>+ 6 V | Leave floating         |

| 13            | VMON4/GPIO3<br>(GPO3 for QM<br>version) | General-purpose input/output pin. Also selectable as voltage monitoring input via OTP. Only general-purpose output (GPO3) available in QM version.     | –0.3 V to 5.5 V                       | Connect to ground      |

| 14            | VMON3/GPIO2<br>(GPO2 for QM<br>version) | General-purpose input/output pin. Also selectable as voltage monitoring input via OTP. Only general-purpose output (GPO2) available in QM version.     | –0.3 V to 5.5 V                       | Connect to ground      |

| 15            | VMON2<br>(NA for QM<br>version)         | Voltage Monitor 2 input. Not available in QM version. Connect to ground for QM version.                                                                | –0.3 V to 5.5 V                       | Connect to ground      |

| 16            | VMON1<br>(NA for QM<br>version)         | Voltage Monitor 1 input. Not available in QM version. Connect to ground for QM version.                                                                | -0.3 V to 10 V                        | Connect to ground      |

| 17            | SW1BOOT                                 | SW1 bootstrap pin. Connect bootstrap capacitor between SW1BOOT and SW1LX.                                                                              | -0.3 V to V <sub>SW1LX</sub><br>+ 6 V | Leave floating         |

| 18, 19        | SW1IN                                   | SW1 input voltage. Bypass with at least 10 µF capacitor for both pins together.                                                                        | -0.3 V to 40 V                        | Connect to VIN         |

| 20, 21        | SW1LX                                   | SW1 switching node. Connect to inductor.                                                                                                               | -0.3 V to 40 V                        | Leave floating         |

## Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 3. Pin description...continued

| Pin<br>number | Pin name                       | Description                                                                                                                                            | Absolute maximum voltage rating | Connection if not used |

|---------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|

| 22            | EN2                            | SW2 enable input pin.                                                                                                                                  | –0.3 V to 40 V                  | Connect to ground      |

| 23            | EN1                            | SW1 enable input pin.                                                                                                                                  | –0.3 V to 40 V                  | Connect to ground      |

| 24            | FS0B<br>(NA for QM<br>version) | Fail-Safe Output pin. Open drain. Connect to ground for QM version.                                                                                    | -0.3 V to 40 V                  | Connect to ground      |

| 25            | SW1FB                          | SW1 output voltage feedback. Use external or internal resistor divider for SW1 outputs ≤ 5.5 V. Use external resistor divider for SW1 outputs > 5.5 V. | –0.3 V to 7 V                   | Connect to ground      |

| 26            | PGOOD1                         | PGOOD1 output from monitoring of selected voltage monitors. Open-drain.                                                                                | –0.3 V to 5.5 V                 | Connect to ground      |

| 27            | PGOOD2                         | PGOOD2 output from monitoring of selected voltage monitors. Open-drain.                                                                                | –0.3 V to 5.5 V                 | Connect to ground      |

| 28            | VDIG                           | Output of internal regulator for powering logic.<br>Bypass with 2.2 µF capacitor. No external loading<br>permitted.                                    | -0.3 V to 2.0 V                 | N/A                    |

| 29            | BIAS_IN                        | Input pin for external bias supply. Bypass with 1 $\mu$ F capacitor. Connect to external bias supply < 5.5 V.                                          | –0.3 V to 5.5 V                 | Connect to ground      |

| 30            | vcc                            | VCC regulator/switch output. Bypass with 10 μF capacitor. No external loading permitted. Nominally regulated at 4.7 V in the absence of BIAS_IN.       | –0.3 V to 5.5 V                 | N/A                    |

| 31            | MODE/SYNCIN                    | Selectable via OTP to be used for external clock synchronization or to select between PFM and PWM modes of operation.                                  | –0.3 V to 5.5 V                 | Connect to ground      |

| 32            | VIN                            | Input to internal circuitry. Connect to battery input.                                                                                                 | -0.3 V to 40 V                  | N/A                    |

| _             | EPAD                           | Connect to ground with sufficient number of thermal vias.                                                                                              | _                               | N/A                    |

Automotive buck regulator and controller with voltage monitors and watchdog timer

## **ESD Ratings**

#### Table 4. ESD ratings

| Symbol           | Rating                                                                                                           | Min   | Unit |

|------------------|------------------------------------------------------------------------------------------------------------------|-------|------|

|                  | Human Body Model – all pins <sup>[1][2]</sup>                                                                    | ±2000 |      |

| V <sub>ESD</sub> | Charge Device Model – All pins <sup>[3][2]</sup>                                                                 | ±500  | V    |

| 1 E3D            | GUN discharged contact test – 2 k $\Omega$ /150 pF; 2 k $\Omega$ /300 pF; 300 $\Omega$ /150 pF – Global pins [4] | ±8000 | •    |

- ESD testing is performed in accordance with the Human Body Model (HBM) (CZAP = 100 pF, RZAP = 1500  $\Omega$ ), and the Charge Device Model (CDM), Robotic (CZAP = 4.0 pF) In accordance with AEC-Q-100 Rev H [1]

- ESD testing is performed in accordance with the Human Body Model (HBM) (CZAP = 100 pF, RZAP = 1500  $\Omega$ ), and the Charge Device Model (CDM), Robotic (CZAP = 4.0 pF [3]

- In accordance with IEC61000-4-2 and ISO10605.2008

#### Caution

This device is sensitive to mechanical shock, improper handling can cause permanent damage to the part.

#### Caution

This is an ESD sensitive device, improper handling can cause permanent damage to the part.

Automotive buck regulator and controller with voltage monitors and watchdog timer

### 9 Thermal Characteristics

Table 5. Temperature range

| Symbol            | Description (Rating)                             | Min | Max | Unit |

|-------------------|--------------------------------------------------|-----|-----|------|

| T <sub>A</sub>    | Ambient Operating Temperature Range (Automotive) | -40 | 125 | °C   |

| T <sub>A</sub>    | Ambient Operating Temperature Range (Industrial) | -40 | 105 | °C   |

| T <sub>J</sub>    | Operating Junction Temperature Range             | -40 | 150 | °C   |

| T <sub>PPRT</sub> | Peak package reflow temperature                  | _   | 260 | °C   |

| T <sub>ST</sub>   | Storage Temperature Range                        | -55 | 150 | °C   |

Table 6. QFN32 thermal resistance and package dissipation ratings

| Rating                                                                       | <b>Board Type</b> | Symbol          | Value | Unit |

|------------------------------------------------------------------------------|-------------------|-----------------|-------|------|

| Junction to Ambient Thermal Resistance <sup>[1]</sup>                        | JESD51-9, 2s2p    | $R_{\theta JA}$ | 36.3  | °C/W |

| Junction-to-Top of Package Thermal Characterization Parameter <sup>[1]</sup> | JESD51-9, 2s2p    | $\Psi_{JT}$     | 4.5   | °C/W |

| Junction to Ambient Thermal Resistance <sup>[1]</sup>                        | Customized, 2s4p  | $R_{\theta JA}$ | 31.7  | °C/W |

| Junction-to-Top of Package Thermal Characterization Parameter <sup>[1]</sup> | Customized, 2s4p  | $\Psi_{ m JT}$  | 4.4   | °C/W |

| Junction to Ambient Thermal Resistance <sup>[1]</sup>                        | Customized, 2s6p  | $R_{\theta JA}$ | 29.4  | °C/W |

| Junction-to-Top of Package Thermal Characterization Parameter <sup>[1]</sup> | Customized, 2s6p  | $\Psi_{JT}$     | 4.4   | °C/W |

<sup>[1]</sup> Determined in accordance to JEDEC JESD51-2A natural convection environment. Thermal resistance data in this report is solely for a thermal performance comparison of one package to another in a standardized specified environment. It is not meant to predict the performance of a package in an application-specific environment. Normal practice assumes uniform heating on the die. When higher power density occurs in localized areas, there are significant hot spots on the die.

Automotive buck regulator and controller with voltage monitors and watchdog timer

## 10 Device Level Electrical Parameters

All parameters are specified at  $T_A$  = -40 °C to 125 °C,  $V_{IN}$  = 14 V, ENx = 12 V, VCC = 5.0 V, No Load on regulators, Fsw = 450 kHz, typical external component values, unless otherwise noted. Typical values are specified at 25 °C, unless otherwise noted.

Table 7. Device level electrical parameters

| Parameter                                                                                                                                             | Symbol | Min | Тур         | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|-----|------|

| VIN Rising Threshold<br>(minimum VIN for FS5600 to turn on)                                                                                           | VIN_r  | _   | _           | 5.7 | V    |

| VIN and SW1/2IN recommended operating voltage (after crossing VIN_r).  BIAS_IN = 5 V powers VCC                                                       | VIN    | 2.7 | _           | 36  | V    |

| VIN and SW1/2IN recommended operating voltage (after crossing VIN_r).  BIAS_IN = 0 V.                                                                 | VIN    | 4.4 | _           | 36  | V    |

| Quiescent Current (non-switching), SW1 & SW2 in PFM. BIAS_IN connected to 5 V. ULPM Mode. Current measured at VIN Current measured at BIAS_IN         | Iq1    | _   | 16<br>140   | _   | μΑ   |

| Quiescent Current (non-switching), SW1 in PFM. SW2 disabled. BIAS_IN connected to 5 V. ULPM Mode. Current measured at VIN Current measured at BIAS_IN | lq2    | _   | 12.5<br>105 | _   | μΑ   |

| Quiescent Current (non-switching), SW2 in PFM. SW1 disabled. BIAS_IN connected to 5 V. ULPM Mode. Current measured at VIN Current measured at BIAS_IN | Iq3    | _   | 10<br>100   | _   | μΑ   |

| Shutdown Mode quiescent current                                                                                                                       | lq4    | _   | 7.5         | _   | μΑ   |

Automotive buck regulator and controller with voltage monitors and watchdog timer

## 11 SW1: 36 V Integrated FET DC-DC Converter

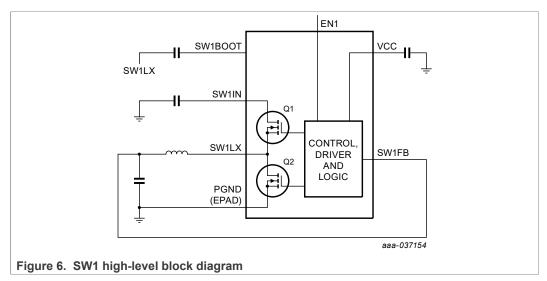

SW1 is a 3 A integrated FET DC DC converter. Load currents of up to 3.5 A may be drawn without entering current limit. The <u>Figure 6</u> shows a high-level block diagram of SW1.

SW1IN pins provide input power to the MOSFETs and VCC provides the voltage needed to drive the MOSFET gates. EN1 controls the enable of the SW1 regulator.

#### 11.1 SW1 electrical specifications

All parameters are specified at  $T_j$  = -40 °C to 150 °C,  $V_{SW1IN}$  = 6 V to 18 V, Vout = 5 V, typical external component values, unless otherwise noted. Typical parameters are specified at  $V_{SW1IN}$  = 12 V,  $T_j$  = 25 °C unless otherwise noted.

Table 8. SW1 electrical specifications

| Parameter                                                                                                                                                   | Symbol                | Min  | Typical                    | Max                         | Units |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|----------------------------|-----------------------------|-------|

| Output Voltage Accuracy (PWM mode, SW1IN = 6 V to 18 V, 0 A <= ISW <= Rated A, minimum 2 V headroom, Vout = 1.8 V to 5.5 V using internal resistor divider) | V <sub>SW1ACC</sub>   | -2   | _                          | 2                           | %     |

| Output Voltage Accuracy in Dropout:<br>(PWM mode, SW1IN = 6 V to (Vout+2 V), 0 A <=ISW <= Rated A, 25C, Vout <= 5 V, 450 kHz)                               | V <sub>SW1ACCDO</sub> | -3   | _                          | 3                           | %     |

| Output Voltage Accuracy<br>(Internal resistor divider, PFM mode, Load = 10 mA)                                                                              | V <sub>SW1ACC</sub>   | -3   | _                          | 3                           | %     |

| Reference accuracy when using external resistor divider                                                                                                     | V <sub>SW1ACC</sub>   | 0.99 | 1                          | 1.01                        | V     |

| Rated load current (PWM mode)                                                                                                                               | V <sub>SW1LOAD</sub>  | 3    | _                          | _                           | Α     |

| Soft-start time (all output voltages) (Measured from 0 % to 90 % of Vout) OTP_SW1_SS = 00 OTP_SW1_SS = 01 OTP_SW1_SS = 10 OTP_SW1_SS = 11                   | t <sub>ss</sub>       | _    | 337<br>675<br>1350<br>2700 | 500<br>1000<br>2000<br>4000 | us    |

FS5600

#### Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 8. SW1 electrical specifications...continued

| SW1 <sub>FSW</sub>    | 250                                                            |                                                                                                                             |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                                                                |                                                                                                                             | 3000                                                                                                                                                                          | kHz                                                                                                                                                                                                                                                                                                                                         |

|                       |                                                                |                                                                                                                             |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                             |

|                       | 1.5                                                            | 2.5                                                                                                                         | 3.5                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                             |

| SW1 <sub>ILIM</sub>   | 3                                                              | 4.1                                                                                                                         | 5.2                                                                                                                                                                           | Α                                                                                                                                                                                                                                                                                                                                           |

|                       | 3.8                                                            | 4.9                                                                                                                         | 6.5                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                             |

|                       | 5                                                              | 6.5                                                                                                                         | 8                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                             |

| HSR <sub>DS(ON)</sub> | _                                                              | 105                                                                                                                         | _                                                                                                                                                                             | mΩ                                                                                                                                                                                                                                                                                                                                          |

| LSR <sub>DS(ON)</sub> | _                                                              | 46                                                                                                                          | _                                                                                                                                                                             | mΩ                                                                                                                                                                                                                                                                                                                                          |

| EN1 <sub>RTH</sub>    | 1.4                                                            | _                                                                                                                           | _                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                           |

| EN1 <sub>FTH</sub>    | _                                                              | _                                                                                                                           | 0.95                                                                                                                                                                          | V                                                                                                                                                                                                                                                                                                                                           |

| _                     | 5                                                              | _                                                                                                                           | 15                                                                                                                                                                            | %                                                                                                                                                                                                                                                                                                                                           |

| _                     | -15                                                            | _                                                                                                                           | -5                                                                                                                                                                            | %                                                                                                                                                                                                                                                                                                                                           |

| _                     | _                                                              | 5                                                                                                                           | _                                                                                                                                                                             | mV                                                                                                                                                                                                                                                                                                                                          |

| _                     | _                                                              | 40                                                                                                                          | _                                                                                                                                                                             | us                                                                                                                                                                                                                                                                                                                                          |

|                       | HSR <sub>DS(ON)</sub> LSR <sub>DS(ON)</sub> EN1 <sub>RTH</sub> | SW1 <sub>ILIM</sub> 3 3.8 5 5 HSR <sub>DS(ON)</sub> — LSR <sub>DS(ON)</sub> — EN1 <sub>RTH</sub> 1.4 EN1 <sub>FTH</sub> — 5 | SW1 <sub>ILIM</sub> 3  4.1  3.8  4.9  5  6.5   HSR <sub>DS(ON)</sub> —  105  LSR <sub>DS(ON)</sub> —  46  EN1 <sub>RTH</sub> 1.4  —  EN1 <sub>FTH</sub> —  5  —  —  -15  —  5 | SW1 <sub>ILIM</sub> 3     4.1     5.2       3.8     4.9     6.5       5     6.5     8       HSR <sub>DS(ON)</sub> —     105     —       LSR <sub>DS(ON)</sub> —     46     —       EN1 <sub>RTH</sub> 1.4     —     —       EN1 <sub>FTH</sub> —     0.95       —     5     —     15       —     -15     —     -5       —     -     5     — |

#### 11.2 SW1 external component selection

<u>Table 9</u> provides the recommended external components for the SW1 regulator.

Table 9. SW1 external component selection

| Components          | Switching frequency < 1 MHz    | Switching frequency > 1 MHz    |

|---------------------|--------------------------------|--------------------------------|

| Inductor            | 6.8 µH                         | 1.5 µH                         |

| Output Capacitor    | 2 x 22 μF to 5 x 22 μF X5R/X7R | 2 x 22 µF to 5 x 22 µF X5R/X7R |

| Bootstrap Capacitor | 0.1 μF                         | 0.1 μF                         |

| Input Capacitor     | 2 x 10 μF X5R/X7R              | 1 x 10 μF X5R/X7R              |

See <u>Section 14.4</u> for switching frequency selection.

#### 11.3 SW1 operation

SW1 is a peak current mode controlled regulator with internal current sense. It integrates low Rds(on) N-FETs for high efficiency and low solution cost.

#### 11.3.1 Output voltage selection

Output voltage of SW1 may be set via OTP using the OTP\_SW1\_VOLT[7:0] bits.

OTP\_SW1\_VOLT[7] = 0b0 sets the output voltage using an internal resistor divider via OTP. Connect the SW1FB pin directly to the output voltage in this case.

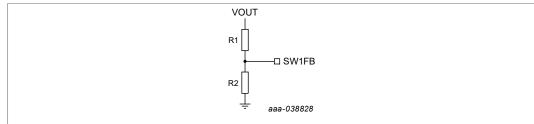

OTP\_SW1\_VOLT[7] = 0b1 allows using an external resistor divider to set the output voltage. In this case, connect the SW1FB pin to the output voltage via a resistor divider. The gain of the resistor divider sets the output voltage as shown in Figure 7. Set R1 = 10 k $\Omega$  and calculate R2 such that VOUT × [R2 / (R1 + R2)] = 1 V. Ensure

Automotive buck regulator and controller with voltage monitors and watchdog timer

that OTP\_SW1\_VOLT[7:0] is set to the appropriate value from <u>Table 10</u> as the slope compensation is calculated internally based on the output voltage.

Figure 7. SW1 output voltage setting using an external resistor divider

Table 10. OTP\_SW1\_VOLT[7:0] selection

| OTP_SW1_VOLT[7:0] | Vout Setting (V) |

|-------------------|------------------|

| 00010000          | 1.8              |

| 00010001          | 1.85             |

| 00010010          | 1.9              |

| 00010011          | 1.95             |

| 00010100          | 2                |

| 00010101          | 2.05             |

| 00010110          | 2.1              |

| 00010111          | 2.15             |

| 00011000          | 2.2              |

| 00011001          | 2.25             |

| 00011010          | 2.3              |

| 00011011          | 2.35             |

| 00011100          | 2.4              |

| 00011101          | 2.45             |

| 00011110          | 2.5              |

| 00011111          | 2.55             |

| 00100000          | 2.6              |

| 00100001          | 2.65             |

| 00100010          | 2.7              |

| 00100011          | 2.75             |

| 00100100          | 2.8              |

| 00100101          | 2.85             |

| 00100110          | 2.9              |

| 00100111          | 2.95             |

| 00101000          | 3                |

| 00101001          | 3.05             |

| 00101010          | 3.1              |

| 00101011          | 3.15             |

Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 10. OTP\_SW1\_VOLT[7:0] selection...continued

| OTP_SW1_VOLT[7:0] Selectioncom | Vout Setting (V) |

|--------------------------------|------------------|

| 00101100                       | 3.2              |

| 00101101                       | 3.25             |

| 00101110                       | 3.3              |

| 00101111                       | 3.35             |

| 00110000                       | 3.4              |

| 00110001                       | 3.45             |

| 00110010                       | 3.5              |

| 00110011                       | 3.55             |

| 00110100                       | 3.6              |

| 00110101                       | 3.65             |

| 00110110                       | 3.7              |

| 00110111                       | 3.75             |

| 00111000                       | 3.8              |

| 00111001                       | 3.85             |

| 00111010                       | 3.9              |

| 00111011                       | 3.95             |

| 00111100                       | 4                |

| 00111101                       | 4.05             |

| 00111110                       | 4.1              |

| 00111111                       | 4.15             |

| 01000000                       | 4.2              |

| 01000001                       | 4.25             |

| 01000010                       | 4.3              |

| 01000011                       | 4.35             |

| 01000100                       | 4.4              |

| 01000101                       | 4.45             |

| 01000110                       | 4.5              |

| 01000111                       | 4.55             |

| 01001000                       | 4.6              |

| 01001001                       | 4.65             |

| 01001010                       | 4.7              |

| 01001011                       | 4.75             |

| 01001100                       | 4.8              |

| 04004404                       | 4 OF             |

| 01001101                       | 4.85             |

| 01001101                       | 4.9              |

Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 10. OTP\_SW1\_VOLT[7:0] selection...continued

| Table 10. OTP_SW1_VOLT[7:0] selectionconti | Vout Setting (V)                              |

|--------------------------------------------|-----------------------------------------------|

| 01010000                                   | 5                                             |

| 01010001                                   | 5.05                                          |

| 01010010                                   | 5.1                                           |

| 01010011                                   | 5.15                                          |

| 01010100                                   | 5.2                                           |

| 01010101                                   | 5.25                                          |

| 01010110                                   | 5.3                                           |

| 01010111                                   | 5.35                                          |

| 01011000                                   | 5.4                                           |

| 01011001                                   | 5.45                                          |

| 01011010                                   | 5.5                                           |

| 01011011                                   | 5.55                                          |

| 01011100                                   | 5.6                                           |

| 01011101                                   | 5.65                                          |

| 01011110                                   | 5.7                                           |

| 01011111                                   | 5.75                                          |

| 01100000                                   | 5.8                                           |

| 01100001                                   | 5.85                                          |

| 01100010                                   | 5.9                                           |

| 01100011                                   | 5.95                                          |

| 01100100                                   | 6                                             |

| 01100101                                   | 6.05                                          |

| 01100110                                   | 6.1                                           |

| 01100111                                   | 6.15                                          |

| 01101000                                   | 6.2                                           |

| 01101001                                   | 6.25                                          |

| 01101010                                   | 6.3                                           |

| 01101011 to 01111111                       | Reserved. Do not use.                         |

| 10010xxx                                   | 1.8 V - 2.15 V with external resistor divider |

| 10011xxx                                   | 2.2 V - 2.55 V with external resistor divider |

| 10100xxx                                   | 2.6 V - 2.95 V with external resistor divider |

| 10101xxx                                   | 3 V - 3.35 V with external resistor divider   |

| 10110xxx                                   | 3.4 V - 3.75 V with external resistor divider |

| 10111xxx                                   | 3.8 V - 4.15 V with external resistor divider |

| 11000xxx                                   | 4.2 V - 4.55 V with external resistor divider |

| 11001xxx                                   | 4.6 V - 4.95 V with external resistor divider |

Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 10. OTP\_SW1\_VOLT[7:0] selection...continued

| OTP_SW1_VOLT[7:0] | Vout Setting (V)                              |

|-------------------|-----------------------------------------------|

| 11010xxx          | 5 V - 5.35 V with external resistor divider   |

| 11011xxx          | 5.4 V5.75 with external resistor divider      |

| 11100xxx          | 5.8 V - 6.15 V with external resistor divider |

| 11101xxx          | 6.2 V - 6.55 V with external resistor divider |

| 11110xxx          | 6.6 V - 6.95 V with external resistor divider |

| 11111xxx          | 7 V - 8 V with external resistor divider      |

#### 11.3.2 PFM and pulse skipping operation

At high VIN/VOUT ratio with high switching frequency, the controller may start to skip pulses to maintain regulation. The minimum on-time of high side FET is programmable via the OTP\_SW1\_MIN\_TON[1:0] bits. OTP\_SW1\_MIN\_TON[1:0] = 0b01 is the recommended default value that is optimal for most applications.

Table 11. OTP\_SW1\_MIN\_TON[1:0] selection

| OTP_SW1_MIN_TON[1:0] | SW1 minimum on-time (ns) |  |  |

|----------------------|--------------------------|--|--|

| 00                   | 40                       |  |  |

| 01                   | 60 (recommended)         |  |  |

| 10                   | 80                       |  |  |

| 11                   | 100                      |  |  |

In addition, the controller starts to switch at half of the selected frequency when the VIN/VOUT ratio is above 6. This allows reduced ripple operation compared to pulse-skipping.

#### 11.3.3 PFM operation

When the OTP\_MODE\_SYNCINB bit = 0, the MODE/SYNCIN pin is configured as a SYNCIN input. In this case, switching mode of SW1 can be selected using the SW1\_MODE[1:0] bits. Default value of SW1\_MODE[1:0] is loaded from OTP\_SW1\_MODE[1:0].

Table 12. SW1\_MODE[1:0] selection.

| OTP_SW1_MODE[1:0]<br>SW1_MODE[1:0] | SW1 operating mode    |

|------------------------------------|-----------------------|

| 00                                 | PFM                   |

| 01                                 | Reserved. Do not use. |

| 10                                 | Reserved. Do not use. |

| 11                                 | PWM                   |

When the OTP\_MODE\_SYNCINB bit = 1, the MODE/SYNCIN pin is configured as a MODE input that can be used to select the operating mode of SW1 between PWM (MODE = 0) and PFM (MODE = 1). Do not use the SW1\_MODE[1:0] to change the operating mode to avoid conflicts between the pin and the register bits.

Automotive buck regulator and controller with voltage monitors and watchdog timer

On-time of the pulses in PFM mode is configurable using the OTP\_SW1\_PFM\_TON[1:0] bits. OTP\_SW1\_PFM\_TON[1:0] = 0b10 offers a good compromise between quiescent current and the output ripple for most applications.

Table 13. OTP\_SW1\_PFM\_TON[1:0] selection

| OTP_SW1_PFM_TON[1:0] | SW1 PFM on-time (ns) |

|----------------------|----------------------|

| 00                   | 160                  |

| 01                   | 320                  |

| 10                   | 640                  |

| 11                   | 800                  |

#### 11.3.4 Soft-start

Startup of SW1 is internally controlled to eliminate overshoot and control the inrush current. Soft-start time is programmable via OTP using the OTP\_SW1\_SS[1:0] bits. See Table 8 for values.

#### 11.3.5 Current limit protection

Cycle-by-cycle current limit is utilized to limit the total permissible output current. Output voltage returns to regulation when the overcurrent is removed. Current limit value is programmable to four different values via OTP using the OTP\_SW1\_ILIM\_SEL[1:0] bits. See <u>Table 8</u> for values.

#### 11.3.6 Compensation selection

OTP\_SW1\_SLOPECOMP[1:0], OTP\_SW1\_PWM\_R\_COMP[2:0], and OTP\_SW1\_GM\_COMP[1:0] select the loop parameters for SW1. See <u>Table 14</u> for recommended values for different operating conditions. Use interpolation for values between the ones shown in <u>Table 14</u>.

Table 14. SW1 compensation selection

| Switching frequency | Output voltage | Output capacitance | OTP_SW1_<br>SLOPECOMP[1:0] | OTP_SW1_PWM_<br>R_COMP[2:0] | OTP_SW1_GM_<br>COMP[1:0] |

|---------------------|----------------|--------------------|----------------------------|-----------------------------|--------------------------|

| 450 kHz             | 3.3 V          | 2 x 22 µF          | 10                         | 000                         | 10                       |

| 450 kHz             | 3.3 V          | 5 x 22 μF          | 10                         | 000                         | 10                       |

| 2.2 MHz             | 3.3 V          | 2 x 22 µF          | 10                         | 000                         | 10                       |

| 2.2 MHz             | 3.3 V          | 5 x 22 μF          | 10                         | 010                         | 10                       |

| 450 kHz             | 4.0 V          | 2 x 22 µF          | 10                         | 000                         | 10                       |

| 450 kHz             | 4.0 V          | 5 x 22 μF          | 10                         | 000                         | 10                       |

| 2.2 MHz             | 4.0 V          | 2 x 22 µF          | 10                         | 000                         | 10                       |

| 2.2 MHz             | 4.0 V          | 5 x 22 μF          | 10                         | 010                         | 10                       |

| 450 kHz             | 5.0 V          | 2 x 22 µF          | 10                         | 000                         | 10                       |

| 450 kHz             | 5.0 V          | 5 x 22 μF          | 10                         | 000                         | 10                       |

| 2.2 MHz             | 5.0 V          | 2 x 22 µF          | 10                         | 010                         | 10                       |

| 2.2 MHz             | 5.0 V          | 5 x 22 μF          | 10                         | 010                         | 10                       |

FS5600

#### Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 14. SW1 compensation selection...continued

| Switching frequency | Output voltage | Output capacitance | OTP_SW1_<br>SLOPECOMP[1:0] |     | OTP_SW1_GM_<br>COMP[1:0] |

|---------------------|----------------|--------------------|----------------------------|-----|--------------------------|

| 450 kHz             | 7.2 V          | 2 x 22 µF          | 10                         | 000 | 10                       |

| 450 kHz             | 7.2 V          | 5 x 22 μF          | 10                         | 000 | 10                       |

| 2.2 MHz             | 7.2 V          | 2 x 22 µF          | 10                         | 010 | 10                       |

| 2.2 MHz             | 7.2 V          | 5 x 22 μF          | 10                         | 100 | 10                       |

Table 15. OTP\_SW1\_SLOPECOMP[1:0] Value

| OTP_SW1_SLOPECOMP[1:0] | Slope compensation (mV/μs) |

|------------------------|----------------------------|

| 00                     | 45                         |

| 01                     | 67.5                       |

| 10                     | 90                         |

| 11                     | 112.5                      |

Table 16. OTP\_SW1\_GM\_COMP[1:0] Value

| OTP_SW1_GM_COMP[1:0] | Transconductance (µS) |

|----------------------|-----------------------|

| 00                   | 14                    |

| 01                   | 21                    |

| 10                   | 28                    |

| 11                   | 35                    |

Table 17. OTP SW1 PWM R COMP[2:0] Value

| OTP_SW1_PWM_R_COMP[2:0] | Compensation resistor (kΩ) |

|-------------------------|----------------------------|

| 000                     | 150                        |

| 001                     | 300                        |

| 010                     | 450                        |

| 011                     | 600                        |

| 100                     | 750                        |

| 101                     | 900                        |

| 110                     | 1050                       |

| 111                     | 1200                       |

#### 11.3.7 SW1 fault monitoring

SW1FB pin voltage is compared against an internal reference to detect undervoltage and overvoltage faults in SW1. See  $\underline{\text{Table 8}}$  for monitoring thresholds.

Automotive buck regulator and controller with voltage monitors and watchdog timer

When OTP\_SW1\_OV\_PGOOD1 = 1, an overvoltage fault on SW1 asserts PGOOD1. Similarly, when OTP\_SW1\_OV\_PGOOD2 = 1, an overvoltage fault on SW1 asserts PGOOD2.

When OTP\_SW1\_UV\_PGOOD1 = 1, an undervoltage fault on SW1 asserts PGOOD1. Similarly, when OTP\_SW1\_UV\_PGOOD2 = 1, an undervoltage fault on SW1 asserts PGOOD2.

The SW1\_UV\_I and SW1\_OV\_I bits are latched to 1 respectively if undervoltage and overvoltage faults are detected. The latch bits can be cleared by writing a 1 to them.

SW1\_UV\_RT and SW1\_OV\_RT read-only bits indicate the real-time status of the faults.

Automotive buck regulator and controller with voltage monitors and watchdog timer

#### 12 SW2: 36 V DC-DC Controller with External FETs

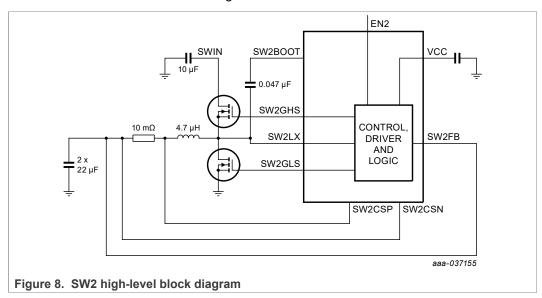

SW2 is an external FET buck controller. <u>Figure 8</u> shows a high-level block diagram of SW2. Rated load current of SW2 is dependent on the external components chosen. With careful selection of the MOSFET, inductor and current sense circuitry, load currents of up to 15 A can be drawn without entering current limit.

#### 12.1 SW2 electrical characteristics

All parameters are specified at  $T_j$  = -40 °C to 150 °C,  $V_{SW2IN}$  = 6 V to 18 V, Vout = 1.8 V to 7.2 V, typical external component values, unless otherwise noted. Typical parameters are specified at  $V_{SW2IN}$  = 12 V,  $T_i$  = 25 °C unless otherwise noted.

Table 18. SW2 electrical characteristics

| Parameter                                                                                                                                                                           | Symbol        | Min                   | Тур                    | Max                     | Unit      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|------------------------|-------------------------|-----------|

| Output Voltage Accuracy<br>(Vout = 1.8 V to 5.5 V, internal resistor divider, PWM mode, Not in<br>dropout, Vin up to 36 V)                                                          | VSW2ACC       | -3                    | _                      | 3                       | %         |

| Output Voltage Accuracy (Internal resistor divider, PFM mode, Vin = 12 V, Load = 0 A to 10 mA)                                                                                      | VSW2ACC       | -3                    | _                      | 3                       | %         |

| Reference accuracy for external resistor divider                                                                                                                                    | SW2REF        | 0.98                  | 1.00                   | 1.02                    | V         |

| Soft start Ramp Slew Rate (Measured at EA input. Multiply by Vout setting for start up time)  OTP_SW2_SS = 0  OTP_SW2_SS = 1                                                        | SW2RAMP       | _                     | 1 2                    | _                       | mV/<br>μs |

| Current Limiter-Inductor Peak Current Sense Voltage in CCM in the forward direction  OTP_SW2_ILIM[1:0] = 00  OTP_SW2_ILIM[1:0] = 01  OTP_SW2_ILIM[1:0] = 10  OTP_SW2_ILIM[1:0] = 11 | VSW2CSL<br>IM | 35<br>60<br>96<br>120 | 50<br>80<br>120<br>150 | 65<br>100<br>144<br>180 | mV        |

#### Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 18. SW2 electrical characteristics...continued

| Parameter                                                                                                                                                                                                                             | Symbol             | Min | Тур                     | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------------------------|------|------|

| Current Limiter-Inductor Peak Current Sense Voltage in CCM (Sense Resistor 10 m $\Omega$ to 20 m $\Omega$ ) in the reverse direction                                                                                                  | VSW2CSL<br>IM      | 35  | 50                      | 65   | mV   |

| PWM Switching Frequency Range (Programmable via OTP)                                                                                                                                                                                  | fsw                | 300 | _                       | 2400 | kHz  |

| Error Amplifier Transconductance (COMP = 0.9 V)                                                                                                                                                                                       | GM                 | 1   | 1.5                     | 2.3  | ms   |

| N-Channel MOSFET Gate Drivers                                                                                                                                                                                                         |                    |     |                         |      | ,    |

| High/ Low Side Driver Pull-up Resistance at Vds = 0.5 V OTP_SW2_HS_SR[3:2]/OTP_SW2_LS_SR[1:0] = 00 OTP_SW2_HS_SR[3:2]/OTP_SW2_LS_SR[1:0] = 01 OTP_SW2_HS_SR[3:2]/OTP_SW2_LS_SR[1:0] = 10 OTP_SW2_HS_SR[3:2]/OTP_SW2_LS_SR[1:0] = 11   | RSW2PUP            | _   | 11<br>5.6<br>2.8<br>1.6 | _    | Ω    |

| High/ Low Side Driver Pull-Down Resistance at Vds = 0.5 V OTP_SW2_HS_SR[1:0]/OTP_SW2_LS_SR[1:0] = 00 OTP_SW2_HS_SR[1:0]/OTP_SW2_LS_SR[1:0] = 01 OTP_SW2_HS_SR[1:0]/OTP_SW2_LS_SR[1:0] = 10 OTP_SW2_HS_SR[1:0]/OTP_SW2_LS_SR[1:0] = 11 | RSW2PDN            | _   | 6.8<br>3.4<br>1.7       | _    | Ω    |

| Discharge Resistance (at the output) during regulator disable                                                                                                                                                                         | RSW2DIS            | _   | 500                     | _    | Ω    |

| EN2 pin rising threshold                                                                                                                                                                                                              | EN2 <sub>RTH</sub> | 1.4 | _                       | _    | V    |

| EN2 pin falling threshold                                                                                                                                                                                                             | EN2 <sub>FTH</sub> | _   | _                       | 0.95 | V    |

| SW2 monitor over voltage threshold (% of nominal)                                                                                                                                                                                     | _                  | 5   | _                       | 15   | %    |

| SW2 monitor under voltage threshold (% of nominal)                                                                                                                                                                                    | _                  | -15 | _                       | -5   | %    |

| SW2 monitoring hysteresis (measured at mid-point of resistor divider)                                                                                                                                                                 | _                  | _   | 5                       | _    | mV   |

| SW2 monitoring debounce                                                                                                                                                                                                               | _                  | _   | 40                      | _    | μs   |

## 12.2 SW2 external component selection

Table 19 provides the recommended external components for the SW2 regulator.

Table 19. SW2 recommended external components

| Components          | Switching frequency < 1 MHz    | Switching frequency > 1 MHz    |

|---------------------|--------------------------------|--------------------------------|

| Inductor            | 4.7 μH                         | 1.5 µH                         |

| Output Capacitor    | 3 x 22 μF to 5 x 22 μF X5R/X7R | 3 x 22 μF to 5 x 22 μF X5R/X7R |

| Bootstrap Capacitor | 0.1 µF                         | 0.1 μF                         |

| Input Capacitor     | 2 x 10 µF X5R/X7R              | 1 x 10 μF X5R/X7R              |

Choose VDS > 40 V for 12 V automotive applications. At high current (> 8 A), each MOSFETs should be selected in a single package to limit the heat exchange between HS and LS. Dual MOSFETs in the same package are practical for low and mid current. (< 8 A).

See Table 20 for guidance on the MOSFET selection.

Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 20. MOSFET selection

| Switching frequency | Load current | High-side MOSFET                                               | Low-side MOSFET                                                |

|---------------------|--------------|----------------------------------------------------------------|----------------------------------------------------------------|

|                     | < 5 A        | Qg < 10 nC<br>Rds(on) < 40 m $\Omega$<br>Example: BUK9K18-40E  | Qg < 20 nC<br>Rds(on) < 20 m $\Omega$<br>Example: BUK9K18-40E  |

| 450 kHz             | < 8 A        | Qg < 10 nC<br>Rds(on) < 25 m $\Omega$<br>Example: NVTFS5C471NL | Qg < 20 nC<br>Rds(on) < 15 m $\Omega$<br>Example: NVTFS5C471NL |

|                     | > 8 A        | Qg < 10 nC<br>Rds(on) < 10 mΩ<br>Example: BUK9M9R5-40H         | Qg < 20 nC<br>Rds(on) < 4 mΩ<br>Example: BUK9M3R3-40H          |

| 2.2 MHz             | < 5 A        | Qg < 10 nC<br>Rds(on) < 30 m $\Omega$<br>Example: BUK9M20-40H  | Qg < 20 nC<br>Rds(on) < 20 mΩ<br>Example: BUK9M20-40H          |

See <u>Section 14.4</u> for switching frequency selection.

#### 12.2.1 Compensation network

SW2 is compensated externally using an R-C ( $R_{comp}$ - $C_{comp}$ ) network from SW2COMP to Ground. A high frequency capacitor ( $C_{hf}$ ) placed from SW2COMP to Ground can be additionally used. Refer to the table below for recommended compensation values for typical use case conditions.

Table 21. SW2 Compensation selection

| Vout(V) | Switching frequency (kHz) | Slope compensation<br>(OTP_SW2_<br>SLOPECOMP[5:0]) | R <sub>comp</sub><br>kΩ | C <sub>comp</sub><br>nF | C <sub>hf</sub><br>pF |

|---------|---------------------------|----------------------------------------------------|-------------------------|-------------------------|-----------------------|

| 3.3     | 450                       | 0x04                                               | 1.5                     | 20                      | 20                    |

| 5.0     | 450                       | 0x08                                               | 2.3                     | 20                      | 20                    |

| 3.3     | 2200                      | 0x0D                                               | 8.0                     | 20                      | Open                  |

| 5.0     | 2200                      | 0x20                                               | 22                      | 20                      | Open                  |

| 1.8     | 450                       | 0x02                                               | 0.8                     | 100                     | 150                   |

Select logical level NMOS (threshold voltage < 2.5 V). Gate drive comes from VCC (5 V).

#### 12.3 SW2 operation

SW2 is a peak current-mode controller plus driver with external current sense. The driver is built to drive low Rds(on) N-channel high and low side MOSFETs for low cost and high efficiency.

#### 12.3.1 Output voltage selection

Output voltage of SW2 may be set via OTP using the OTP SW2 VOLT[5:0] bits.

OTP\_SW2\_VOLT[5:0] = 0b111000 configures the device to use an external resistor divider to set the output voltage. Use the same equation for the external divider as for SW1.

FS5600

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 22. OTP\_SW2\_VOLT[5:0] Selection

| OTP_SW2_VOLT[5:0] Selection | SW2 voltage setting (V) |

|-----------------------------|-------------------------|

| 000000                      | 1.8                     |

| 000001                      | 1.9                     |

| 000010                      | 2                       |

| 000011                      | 2.1                     |

| 000100                      | 2.2                     |

| 000101                      | 2.3                     |

| 000110                      | 2.4                     |

| 000111                      | 2.5                     |

| 001000                      | 2.6                     |

| 001001                      | 2.7                     |

| 001010                      | 2.8                     |

| 001011                      | 2.9                     |

| 001100                      | 3                       |

| 001101                      | 3.1                     |

| 001110                      | 3.2                     |

| 001111                      | 3.3                     |

| 010000                      | 3.4                     |

| 010001                      | 3.5                     |

| 010010                      | 3.6                     |

| 010011                      | 3.7                     |

| 010100                      | 3.8                     |

| 010101                      | 3.9                     |

| 010110                      | 4                       |

| 010111                      | 4.1                     |

| 011000                      | 4.2                     |

| 011001                      | 4.3                     |

| 011010                      | 4.4                     |

| 011011                      | 4.5                     |

| 011100                      | 4.6                     |

| 011101                      | 4.7                     |

| 011110                      | 4.8                     |

| 011111                      | 4.9                     |

| 100000                      | 5                       |

| 100001                      | 5.1                     |

| 100010                      | 5.2                     |

| 100011                      | 5.3                     |

Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 22. OTP\_SW2\_VOLT[5:0] Selection...continued

| OTP_SW2_VOLT[5:0] | SW2 voltage setting (V)           |

|-------------------|-----------------------------------|

| 100100            | 5.4                               |

| 100101            | 5.5                               |

| 100110            | 5.6                               |

| 100111            | 5.7                               |

| 101000            | 5.8                               |

| 101001            | 5.9                               |

| 101010            | 6                                 |

| 101011            | 6.1                               |

| 101100            | 6.2                               |

| 101101            | 6.3                               |

| 101110            | 6.4                               |

| 101111            | 6.5                               |

| 110000            | 6.6                               |

| 110001            | 6.7                               |

| 110010            | 6.8                               |

| 110011            | 6.9                               |

| 110100            | 7                                 |

| 110101            | 7.1                               |

| 110110            | 7.2                               |

| 110111            | Reserved. Do not use.             |

| 111000            | 1 (Use External Resistor Divider) |

| 111001            | Reserved. Do not use.             |

| 111010            | Reserved. Do not use.             |

| 111011            | Reserved. Do not use.             |

| 111100            | Reserved. Do not use.             |

| 111101            | Reserved. Do not use.             |

| 111110            | Reserved. Do not use.             |

| 111111            | Reserved. Do not use.             |

|                   |                                   |

#### 12.3.2 Pulse skipping operation

At high VIN/VOUT ratio with high switching frequency, the controller may start to skip pulses to maintain regulation. The minimum on-time of high side FET is programmable via the OTP\_SW2\_TON\_MIN[1:0] bits.

Table 23. OTP\_SW2\_TON\_MIN[1:0] Selection

| OTP_SW2_TON_MIN[1:0] | SW2 minimum on-time (ns)               |

|----------------------|----------------------------------------|

| 00                   | 45 (recommended for 450 kHz operation) |

| 01                   | 65                                     |

FS5600

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Automotive buck regulator and controller with voltage monitors and watchdog timer

Table 23. OTP\_SW2\_TON\_MIN[1:0] Selection...continued

| OTP_SW2_TON_MIN[1:0] | SW2 minimum on-time (ns)               |

|----------------------|----------------------------------------|

| 10                   | 25 (recommended for 2.2 MHz operation) |

| 11                   | 45                                     |

#### 12.3.3 PFM operation

When the OTP\_MODE\_SYNCINB bit = 0, the MODE/SYNCIN pin is configured as a SYNCIN input. In this case, switching mode of SW2 can be selected using the SW2\_MODE[1:0] bits. The default value of SW2\_MODE[1:0] is loaded from OTP\_SW2\_MODE[1:0].

Table 24. SW2\_MODE[2:0] selection

| OTP_SW2_MODE[1:0]<br>SW2_MODE[1:0] | SW2 operating mode    |

|------------------------------------|-----------------------|

| 00                                 | PFM                   |

| 01                                 | Reserved. Do not use. |

| 10                                 | Reserved. Do not use. |

| 11                                 | PWM                   |

When the OTP\_MODE\_SYNCINB bit = 1, the MODE/SYNCIN pin is configured as a MODE input that can be used to select the operating mode of SW2 between PWM (MODE = 0) and PFM (MODE = 1). Do not use the SW2\_MODE[1:0] to change the operating mode to avoid conflicts between the pin and the register bits.

On-time of the pulses in PFM mode is configurable using the OTP\_SW2\_PFM\_TON[1:0] bits. OTP\_SW2\_PFM\_TON[1:0] = 0b10 offers a good compromise between quiescent current and the output ripple for most applications.

Table 25. OTP\_SW2\_PFM\_TON[1:0] Selection

| OTP_SW2_PFM_TON[1:0] | SW2 PFM on-time (ns) |

|----------------------|----------------------|

| 00                   | 120                  |

| 01                   | 210                  |

| 10                   | 300                  |

| 11                   | 550                  |

#### 12.3.4 Soft-Start

Startup of SW2 is internally controlled to eliminate overshoot and control the inrush current. Soft-start time is programmable via OTP using the OTP\_SW2\_SS bit. See <u>Table 18</u> for values.

#### 12.3.5 Current limit protection

Cycle-by-cycle current limit is utilized to limit the total permissible output current. Output voltage returns to regulation when the overcurrent is removed. Current limit value is programmable to 4 different values via OTP using the OTP\_SW2\_ILIM[1:0] bits. See Table 18 for values.

Automotive buck regulator and controller with voltage monitors and watchdog timer

#### 12.3.6 Slope compensation

Slope compensation for the controller is set via OTP using the OTP\_SW2\_SLOPECOMP[5:0] bits. See <u>Section 12.2 "SW2 external component selection"</u> for values to use based on operating conditions.

Table 26. OTP\_SW2\_SLOPECOMP[5:0] selection

| OTP_SW2_SLOPECOMP[5:0] | SW2 slope compensation (mV/µs) |

|------------------------|--------------------------------|

| 000000                 | 0                              |

| 000001                 | 10                             |

| 000010                 | 20                             |

| 000011                 | 31                             |

| 000100                 | 41                             |

| 000101                 | 51                             |

| 000110                 | 62                             |

| 000111                 | 72                             |

| 001000                 | 82                             |

| 001001                 | 92                             |

| 001010                 | 103                            |

| 001011                 | 113                            |

| 001100                 | 123                            |

| 001101                 | 134                            |

| 001110                 | 144                            |

| 001111                 | 154                            |

| 010000                 | 175                            |

| 010001                 | 195                            |

| 010010                 | 216                            |

| 010011                 | 237                            |

| 010100                 | 258                            |

| 010101                 | 279                            |