# IS2083 Bluetooth<sup>®</sup> Stereo Audio SoC Data Sheet

## Introduction

The IS2083 is a System-on-Chip (SoC) for dual mode Bluetooth stereo audio applications. It contains an on-board Bluetooth stack, audio profiles and supports 24-bit/96 kHz high-resolution (Hi-Res) audio formats to enable high-fidelity wireless audio. An integrated Digital Signal Processor (DSP) decodes (LDAC, Advanced Audio Codec (AAC), and Sub-band Codec (SBC) codecs) and executes advanced audio and voice processing (wideband speech, Acoustic Echo Cancellation (AEC), and Noise Reduction (NR)). This platform provides a Microcontroller (MCU) core for application implementation via Software Development Kit (SDK) with debug support and a GUI (Config Tool) tool for easy customization of peripheral settings and DSP functionality.

Additionally, the Audio Transceiver (AT) solution enables Bluetooth capability in non-Bluetooth Audio equipment. The AT receives audio inputs through the Aux-In or I<sup>2</sup>S pin and streams the audio to up to two Bluetooth paired sink devices.

Note: Contact your local sales representative for more information about the Software Development Kit (SDK).

The IS2083 SoC is offered in a BGA package and contains in-package Flash, and is referred to as IS2083BM.

The IS2083BM supports an Over-the-Air (OTA) firmware upgrade and controls the end-application via Bluetooth Low Energy using the Microchip Bluetooth Audio (MBA) mobile app.

## Features

- Qualified for Bluetooth v5.0 specification

- Hands-free Profile (HFP) 1.7.2, Headset Profile (HSP) 1.2, Advanced Audio Distribution Profile (A2DP) 1.3, Serial Port Profile (SPP) 1.2, Audio/Video Remote Control Profile (AVRCP) 1.6 and Phone Book Access Profile (PBAP) 1.2

- Bluetooth classic (BR/EDR) and Bluetooth Low Energy

- General Attribute Profile (GATT) and General Access Profile (GAP)

- Bluetooth Low Energy Data Length Extension (DLE) and secure connection

- Software Development Kit

- 8051 microcontroller debugging

- 24-bit program counter and Data Pointer modes

- Multi-Speaker (MSPK) solution

- Microchip's proprietary solution to connect a central speaker to one or more peripheral speakers

- With MSPK firmware, the IS2083 can provide Concert mode and Stereo mode

- Audio Transceiver (AT) solution

- With AT firmware, the IS2083 can work as either an A2DP source (where IS2083 is the transmitter) or A2DP/HFP sink (where IS2083 is a receiver)

- Audio Interfaces

- Stereo line input

- Two analog microphones

- One stereo digital microphone

- Stereo audio Digital-to-Analog Converter (DAC)

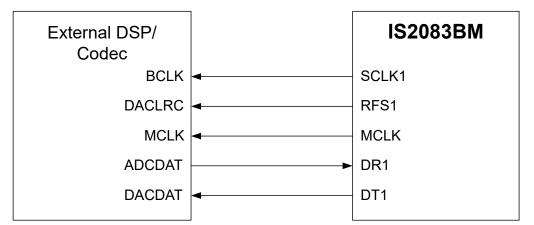

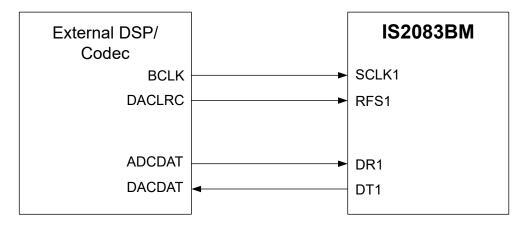

- I<sup>2</sup>S input/output

- I<sup>2</sup>S Primary clock (MCLK)/reference clock

- USB, UART and Over-the-Air (OTA) firmware upgrade

- Built-in lithium-ion and lithium polymer battery charger (up to 350 mA)

- Integrated 3V and 1.8V configurable switching regulator and Low-Dropout (LDO)

#### Radio Frequency (RF)/Analog

- Bluetooth 5.0 dual mode RF radio

- Receive sensitivity: -90 dBm (2 Mbps EDR)

- Programmable transmit output power:

- Up to +11 dBm (typical) for Basic Data Rate (BDR)

- Up to +9.5 dBm (typical) for Enhanced Data Rate (EDR)

- Integrated Medium Power Amplifier (MPA) and Low Power Amplifier (LPA)

#### **MCU Features**

- 8051 8-bit core

- 8-bit data

- 24-bit program counter (PC24) mode

- 24-bit data pointer (DPTR24) mode

- Operating speed:

- DC 48 MHz clock input

- 0.33-1 MIPS/MHz, depending on instruction

#### DSP Voice and Audio Processing

- 16/32-bit DSP core with enhanced 32-bit precision, single cycle multiplier

- Synchronous Connection-Oriented (SCO) channel operation

- Modified Sub-Band Coding (mSBC) decoder for wideband speech

- Built-in High-definition Clean Audio (HCA) algorithms for both narrowband and wideband speech processing

- · Built-in audio effect algorithms to enhance audio streaming

- 64 Kbps A-Law, µ-Law Pulse Code Modulation (PCM) or Continuous Variable Slope Delta (CVSD) modulation for SCO channel operation

- 8/16 kHz Noise Reduction (NR)

- 8/16 kHz Acoustic Echo Cancellation (AEC)

- Packet Loss Concealment (PLC) for SBC and mSBC codecs only

#### Audio Codec

- Sub-band Codec (SBC), Advanced Audio Codec (AAC) and LDAC Decoding (IS2083BM-2L2 only)

- 20-bit audio stereo DAC with SNR 95 dB

- 16-bit audio stereo ADC with SNR 90 dB

- 24-bit, I<sup>2</sup>S digital audio:

- 96 kHz output sampling frequency

- 48 kHz input sampling frequency

#### Peripherals

- Successive Approximation Register Analog-to-Digital Converter (SAR ADC) with dedicated channels:

- Battery voltage detection and adapter voltage detection

- Charger thermal protection and ambient temperature detection

- UART (with hardware flow control)

- USB (full-speed USB 1.1 interface)

- I<sup>2</sup>C<sup>™</sup> Host

- One Pulse Width Modulation (PWM) channel

- Two LED drivers

- Up to 19 General Purpose Inputs/Outputs (GPIOs)

#### 8051 MCU Debug Features

- Two-wire 8051 MCU Joint Test Action Group (JTAG) debug

- CPU registers to write Flash for software downloading

- Debug features supported

- Run/Stop control

- Single Step mode

- Software breakpoint

- Debug program

- Hardware breakpoint

- Program trace

- Access to ACC

#### **Operating Condition**

- Operating voltage: 3.2V to 4.2V

- Operating temperature: -40°C to +85°C

#### Applications

- Portable speakers

- Multiple speakers

- Headphones

- Bluetooth audio transmitter

#### Compliance

• Bluetooth Special Interest Group (SIG) QDID: 134083 (Class1) and 134099 (Class2)

# **Table of Contents**

| Introduction1 |        |                                   |     |  |  |

|---------------|--------|-----------------------------------|-----|--|--|

| Fea           | tures  |                                   | 1   |  |  |

| 1.            | Quick  | References                        | 6   |  |  |

|               | 1.1.   | Reference Documentation           | 6   |  |  |

|               | 1.2.   | Acronyms/Abbreviations            | 6   |  |  |

| 2.            | Devic  | e Overview                        | 9   |  |  |

|               | 2.1.   | IS2083BM Device Ball Diagram      | 10  |  |  |

|               | 2.2.   | IS2083BM Device Ball Description  |     |  |  |

| 3.            | Audio  | Subsystem                         | 17  |  |  |

| 0.            | 3.1.   | Digital Signal Processor          |     |  |  |

|               | 3.1.   | Codec                             |     |  |  |

|               | 3.3.   | Auxiliary Port                    |     |  |  |

|               | 3.4.   | Microphone Inputs                 |     |  |  |

|               | 3.5.   | Analog Speaker Output             |     |  |  |

|               |        |                                   |     |  |  |

| 4.            | Blueto | ooth Transceiver                  |     |  |  |

|               | 4.1.   | Transmitter                       |     |  |  |

|               | 4.2.   | Receiver                          |     |  |  |

|               | 4.3.   | Synthesizer                       |     |  |  |

|               | 4.4.   | Modulator-Demodulator             |     |  |  |

|               | 4.5.   | Adaptive Frequency Hopping        | 31  |  |  |

| 5.            | Micro  | controller                        | .32 |  |  |

|               | 5.1.   | Memory                            | 33  |  |  |

|               | 5.2.   | Clock                             | 33  |  |  |

| 6.            | Powe   | r Management Unit                 | .35 |  |  |

|               | 6.1.   | Device Operation                  |     |  |  |

|               | 6.2.   | Power Supply                      |     |  |  |

|               | 6.3.   | Adapter Input                     |     |  |  |

|               | 6.4.   | Buck1 (BK1) Switching Regulator   |     |  |  |

|               | 6.5.   | Buck2 (BK2) Switching Regulator   |     |  |  |

|               | 6.6.   | Low-Droput Regulator              |     |  |  |

|               | 6.7.   | Battery Charging                  |     |  |  |

|               | 6.8.   | SAR ADC                           | 37  |  |  |

|               | 6.9.   | LED Driver                        | 39  |  |  |

| 7.            | Applic | ation Information                 | .40 |  |  |

|               | 7.1.   | Power On/Off Sequence             |     |  |  |

|               | 7.2.   | Reset                             |     |  |  |

|               | 7.3.   | Programming and Debugging         |     |  |  |

|               | 7.4.   | General Purpose I/O Pins          |     |  |  |

|               | 7.5.   | I <sup>2</sup> S Mode Application |     |  |  |

|               | 7.6.   | Host MCU Interface                |     |  |  |

| 8.         | Electrical Specifications                 | 49 |  |  |  |

|------------|-------------------------------------------|----|--|--|--|

|            | 8.1. Timing Specifications                | 55 |  |  |  |

| 9.         | Package Information                       | 58 |  |  |  |

| 10.        | Ordering Information                      | 62 |  |  |  |

| 11.        | Document Revision History                 | 63 |  |  |  |

| The        | Microchip Website                         | 65 |  |  |  |

| Pro        | Product Change Notification Service65     |    |  |  |  |

| Cus        | Customer Support                          |    |  |  |  |

| Mic        | Microchip Devices Code Protection Feature |    |  |  |  |

| Leg        | Legal Notice                              |    |  |  |  |

| Trademarks |                                           |    |  |  |  |

| Qua        | Quality Management System                 |    |  |  |  |

| Woi        | Worldwide Sales and Service               |    |  |  |  |

## 1. Quick References

## 1.1 Reference Documentation

For further information, refer to the following:

- BM83 Bluetooth<sup>®</sup> Stereo Audio Module Data Sheet (DS70005402)

- BM83 Bluetooth<sup>®</sup> Audio Development Board User's Guide (DS50002902)

- IS2083 SDK User Guide (DS50002894)

- BM83 Host MCU Firmware Development Guide (DS50002896)

- IS2083/BM83 Bluetooth<sup>®</sup> Application Design Guide (DS00003118)

- IS2083 SDK Debugger User's Guide (DS50002892)

- IS2083 Reference Design Application Note

- IS2083/BM83 Battery Charger Application Note (AN3490)

- Serial Quad Interface (SQI) Family Reference Manual (DS60001244)

#### Notes:

- 1. For a complete list of development support tools and documents, visit:

- www.microchip.com/BM83

- www.microchip.com/IS2083

- 2. Contact your local sales representative for more information about the Software Development Kit (SDK).

## 1.2 Acronyms/Abbreviations

#### Table 1-1. Acronyms/Abbreviations

| Acronyms/Abbreviations | Description                         |  |

|------------------------|-------------------------------------|--|

| A2DP                   | Advanced Audio Distribution Profile |  |

| AAC                    | Advanced Audio Codec                |  |

| ADC                    | Analog-to-Digital Converter         |  |

| AEC                    | Acoustic Echo Cancellation          |  |

| AFH                    | Adaptive Frequency Hopping          |  |

| ANCS                   | Apple Notification Center Service   |  |

| API                    | Application Programming Interfaces  |  |

| AVRCP                  | Audio/Video Remote Control Profile  |  |

| AW                     | Audio Widening                      |  |

| BDR                    | Basic Data Rate                     |  |

| BER                    | Bit Error Rate                      |  |

| BLE                    | Bluetooth Low Energy                |  |

| BOM                    | Bill of Materials                   |  |

| BPF                    | Band Pass Filter                    |  |

| BR                     | Basic Rate                          |  |

| CVSD                   | Continuous Variable Slope Delta     |  |

| DAC                    | Digital-to-Analog Converter         |  |

| DFU                    | Device Firmware Upgrade             |  |

| DIS                    | Device Information Service          |  |

| continued              |                                            |  |  |  |

|------------------------|--------------------------------------------|--|--|--|

| Acronyms/Abbreviations | Description                                |  |  |  |

| DLE                    | Data Length Extension                      |  |  |  |

| DPSK                   | Differential Phase Shift Keying            |  |  |  |

| DQPSK                  | Differential Quadrature Phase Shift Keying |  |  |  |

| DR                     | Receive Data                               |  |  |  |

| DSP                    | Digital Signal Processor                   |  |  |  |

| DT                     | Transmit Data                              |  |  |  |

| EDR                    | Enhanced Data Rate                         |  |  |  |

| EMC                    | Electromagnetic Compatibility              |  |  |  |

| EVB                    | Evaluation Board                           |  |  |  |

| FET                    | Field Effect Transistor                    |  |  |  |

| GAP                    | General Access Profile                     |  |  |  |

| GATT                   | General Attribute Profile                  |  |  |  |

| GFSK                   | Gaussian Frequency Shift Keying            |  |  |  |

| GPIO                   | General Purpose Input Output               |  |  |  |

| GUI                    | Graphical User Interface                   |  |  |  |

| HFP                    | Hands-Free Profile                         |  |  |  |

| HPF                    | High Pass Filter                           |  |  |  |

| HSP                    | Headset Profile                            |  |  |  |

| HW                     | Hardware                                   |  |  |  |

| I <sup>2</sup> C       | Inter-Integrated Circuit                   |  |  |  |

| I <sup>2</sup> S       | Inter-IC Sound                             |  |  |  |

| IC                     | Integrated Circuit                         |  |  |  |

| ICSP™                  | In-Circuit Serial Programming <sup>™</sup> |  |  |  |

| IDE                    | Integrated Development Environment         |  |  |  |

| IF                     | Intermediate Frequency                     |  |  |  |

| IPE                    | Integrated Programming Environment         |  |  |  |

| JTAG                   | Joint Test Action Group                    |  |  |  |

| LDO                    | Low-Dropout                                |  |  |  |

| LED                    | Light Emitting Diode                       |  |  |  |

| LNA                    | Low-Noise Amplifier                        |  |  |  |

| LPA                    | Linear Power Amplifier                     |  |  |  |

| LSB                    | Least Significant Bit                      |  |  |  |

| MAC                    | Medium Access Control                      |  |  |  |

| MB DRC                 | Multi-Band Dynamic Range Compression       |  |  |  |

| MCLK                   | Primary Clock                              |  |  |  |

| MCU                    | Microcontroller                            |  |  |  |

| MEMS                   | Micro-Electro-Mechanical Systems           |  |  |  |

| MFB                    | Multi-Function Button                      |  |  |  |

| Modem                  | Modulator-demodulator                      |  |  |  |

| MPA                    | Medium Power Amplifier                     |  |  |  |

| continued              |                                             |  |  |  |

|------------------------|---------------------------------------------|--|--|--|

| Acronyms/Abbreviations | Description                                 |  |  |  |

| mSBC                   | Modified Sub-Band Coding                    |  |  |  |

| MSPK                   | Multi-Speaker                               |  |  |  |

| NR                     | Noise Reduction                             |  |  |  |

| OTA                    | Over-the-Air                                |  |  |  |

| PBAP                   | Phone Book Access Profile                   |  |  |  |

| PCB                    | Printed Circuit Board                       |  |  |  |

| PCM                    | Pulse Code Modulation                       |  |  |  |

| PDM                    | Pulse Density Modulation                    |  |  |  |

| PIM                    | Plug-In Module                              |  |  |  |

| PLC                    | Packet Loss Concealment                     |  |  |  |

| PMU                    | Power Management Unit                       |  |  |  |

| POR                    | Power-On Reset                              |  |  |  |

| PWM                    | Pulse Width Modulation                      |  |  |  |

| RF                     | Radio Frequency                             |  |  |  |

| RFS                    | Receive Frame Sync                          |  |  |  |

| RoHS                   | Restriction of Hazardous Substances         |  |  |  |

| RSSI                   | Received Signal Strength Indicator          |  |  |  |

| RX                     | Receiver                                    |  |  |  |

| SAR                    | Successive Approximation Register           |  |  |  |

| SBC                    | Sub-Band Coding                             |  |  |  |

| SCO                    | Synchronous Connection-Oriented             |  |  |  |

| SDK                    | Software Development Kit                    |  |  |  |

| SIG                    | Special Interest Group                      |  |  |  |

| SNR                    | Signal-to-Noise Ratio                       |  |  |  |

| SoC                    | System-on-Chip                              |  |  |  |

| SPP                    | Serial Port Profile                         |  |  |  |

| SW                     | Software                                    |  |  |  |

| ТХ                     | Transmitter                                 |  |  |  |

| UART                   | Universal Asynchronous Receiver-Transmitter |  |  |  |

| UI                     | User Interface                              |  |  |  |

| USB                    | Universal Serial Bus                        |  |  |  |

| VB                     | Virtual Bass Enhancement                    |  |  |  |

| VCO                    | Voltage-Controlled Oscillator               |  |  |  |

| WDT                    | Watchdog Timer                              |  |  |  |

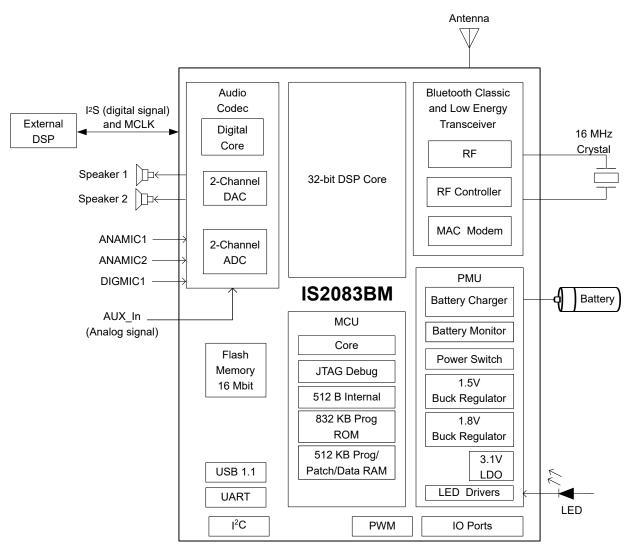

## 2. Device Overview

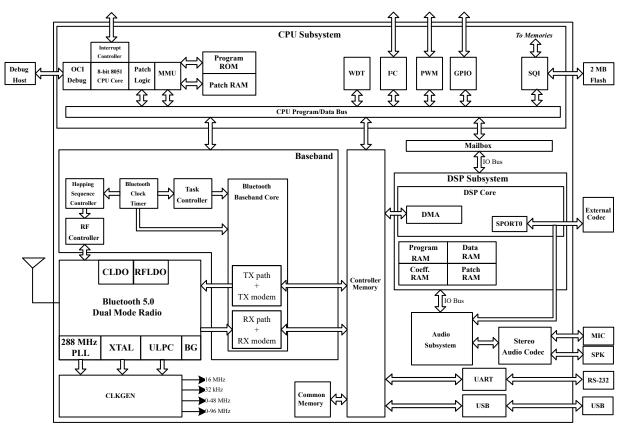

The IS2083BM uses a single-cycle 8-bit 8051 MCU core connected to the system components via an MCU system bus. The MCU system bus provides interface memory map address decode for the Read Only Memory (ROM), Static Random Access Memory (SRAM), and peripherals.

IS2083BM contains the following major blocks:

- Bluetooth Link Controller (BTLC) Bluetooth clock, task scheduler, and Bluetooth hopping

- Bluetooth modulator-demodulator (modem) TX/RX baseband and RF

- DSP audio subsystem DSP with audio codec

- Program ROM Memory

- Bluetooth DMA Common Memory Access

- Power Management Unit (PMU)

- Clock/Reset Low power logic

#### Figure 2-1. IS2083BM SoC Architecture

The IS2083BM device variants are:

- IS2083BM variant supports analog output from the internal DAC

- IS2083BM-2L2 variant supports LDAC and does not support analog output

The following table provides the features of IS2083BM SoC variants.

#### Table 2-1. IS2083BM Features

| Features                                                | IS2083BM                                                              | IS2083BM-2L2    |

|---------------------------------------------------------|-----------------------------------------------------------------------|-----------------|

| Application                                             | <ul><li>Headset/Speaker</li><li>Bluetooth Audio Transmitter</li></ul> | Headset/Speaker |

| Memory                                                  | Flash                                                                 | Flash           |

| Stereo/Concert mode                                     | Yes                                                                   | Yes             |

| Package                                                 | BGA                                                                   | BGA             |

| Pin/Ball count                                          | 82                                                                    | 82              |

| Dimensions                                              | 5.5 mm x 5.5 mm                                                       | 5.5 mm x 5.5 mm |

| Audio DAC output                                        | 2 channel                                                             | —               |

| DAC (single-ended) SNR                                  | 95 dB                                                                 | -               |

| DAC (cap-less) SNR                                      | 95 dB                                                                 | _               |

| ADC SNR at 1.8V                                         | -88 dB                                                                | -88 dB          |

| I <sup>2</sup> S audio input                            | Yes                                                                   | Yes             |

| I <sup>2</sup> S digital output                         | Yes                                                                   | Yes             |

| MCLK output                                             | Yes                                                                   | Yes             |

| Analog output                                           | Yes                                                                   | -               |

| Analog Line-In                                          | Yes                                                                   | Yes             |

| Analog microphone                                       | 2 channel                                                             | 2 channel       |

| Digital microphone                                      | 2 channel                                                             | 2 channel       |

| External audio amplifier interface                      | Yes                                                                   | Yes             |

| UART with hardware flow control                         | 1                                                                     | 1               |

| USB (Full-speed USB 1.1 interface and battery charging) | Yes                                                                   | Yes             |

| l <sup>2</sup> C                                        | 1                                                                     | 1               |

| PWM                                                     | 1 channel                                                             | 1 channel       |

| LED driver                                              | 2                                                                     | 2               |

| Battery charger (350 mA maximum)                        | Yes                                                                   | Yes             |

| ADC for battery voltage and temperature monitoring      | Yes                                                                   | Yes             |

| GPIO                                                    | Up to 19                                                              | Up to 19        |

| Multitone                                               | Yes                                                                   | Yes             |

| Integrated MPA and LPA                                  | Yes                                                                   | Yes             |

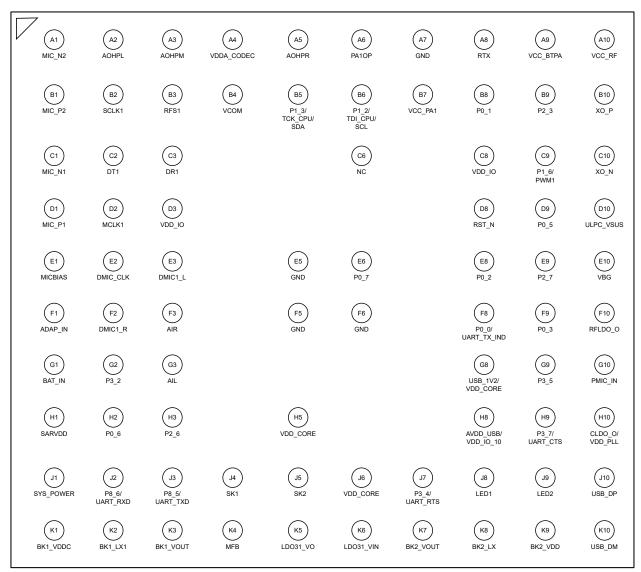

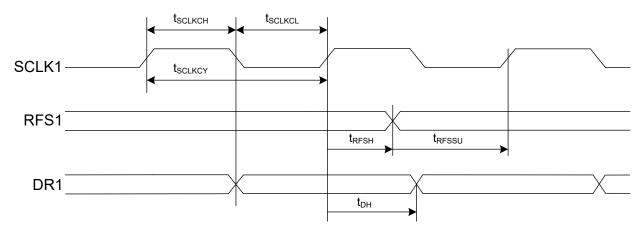

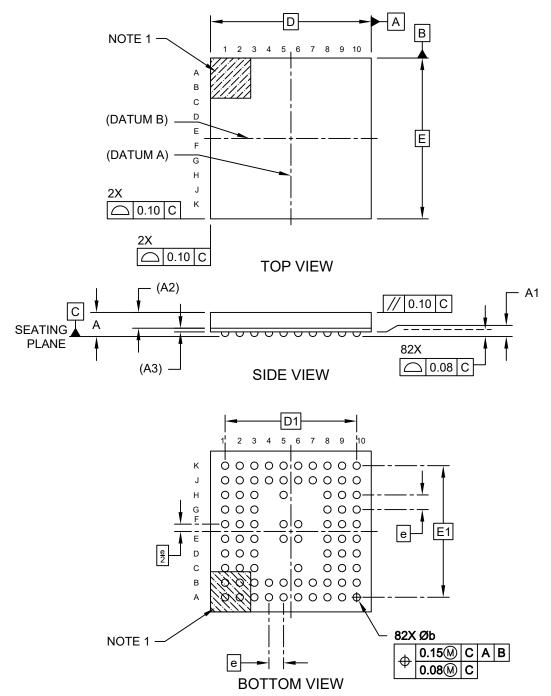

## 2.1 IS2083BM Device Ball Diagram

The following figure illustrates the ball diagram of the IS2083BM and IS2083BM-2L2.

#### Figure 2-2. IS2083BM and IS2083BM-2L2 Ball Diagram

**Note:** The IS2083BM-2L2 does not support an analog output from the internal DAC. The AOHPR, AOHPM and AOHPL are affected pins.

## 2.2 IS2083BM Device Ball Description

#### Table 2-2. IS2083BM and IS2083BM-2L2 Ball Description

| IS2083BM Ball<br>Number | IS2083BM-2L2 Ball<br>Number | Ball Name            | Ball<br>Type | Description                                  |

|-------------------------|-----------------------------|----------------------|--------------|----------------------------------------------|

| A1                      | A1                          | MIC_N2               | I            | MIC2 mono differential analog negative input |

| A2                      | —                           | AOHPL <sup>(1)</sup> | 0            | Left channel, analog headphone output        |

| A3                      |                             | AOHPM <sup>(1)</sup> | 0            | Headphone common mode output/sense input     |

| continued               |                             |                       |              |                                                                                                                                        |  |

|-------------------------|-----------------------------|-----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| IS2083BM Ball<br>Number | IS2083BM-2L2 Ball<br>Number | Ball Name             | Ball<br>Type | Description                                                                                                                            |  |

| A4                      | A4                          | VDDA_CODEC            | Ρ            | <ul> <li>Analog audio codec power supply<br/>(1.8V)</li> <li>Connect to BK2_VOUT pin</li> </ul>                                        |  |

| A5                      | —                           | AOHPR <sup>(1)</sup>  | 0            | Right channel, analog headphone output                                                                                                 |  |

| A6                      | A6                          | PA10P                 | I/O          | RF output pin for MPA                                                                                                                  |  |

| A7                      | A7                          | GND                   | Ρ            | Ground reference                                                                                                                       |  |

| A8                      | A8                          | RTX                   | I/O          | <ul> <li>RF path (transmit/receive)</li> <li>TX LPA output multiplexed with RX<br/>LNA input</li> </ul>                                |  |

| A9                      | A9                          | VCC_BTPA              | Ρ            | <ul><li>Power supply for RF power amplifier</li><li>Connect to BK1_VOUT</li></ul>                                                      |  |

| A10                     | A10                         | VCC_RF                | Ρ            | <ul> <li>RF power input (1.28V) for both<br/>synthesizer and TX/RX block</li> <li>Connect to RFLDO_O</li> </ul>                        |  |

| B1                      | B1                          | MIC_P2                | 1            | MIC2 mono differential analog positive input                                                                                           |  |

| B2                      | B2                          | SCLK1                 | I/O          | I <sup>2</sup> S interface for bit clock                                                                                               |  |

| B3                      | B3                          | RFS1                  | I/O          | I <sup>2</sup> S interface for DAC digital left/right clock                                                                            |  |

| B4                      | B4                          | VCOM                  | Ρ            | <ul> <li>Internal biasing voltage for codec</li> <li>Connect a 4.7 µF capacitor to ground</li> </ul>                                   |  |

| B5                      | B5                          | P1_3/<br>TCK_CPU/ SDA | I/O          | <ul> <li>General purpose I/O port P1_3</li> <li>CPU two-wire debug clock</li> <li>I<sup>2</sup>C SDA</li> </ul>                        |  |

| B6                      | B6                          | P1_2/ TDI_CPU/<br>SCL | I/O          | <ul> <li>General purpose I/O port P1_2</li> <li>CPU two-wire debug data</li> <li>I<sup>2</sup>C SCL</li> </ul>                         |  |

| В7                      | В7                          | VCC_PA1               | Ρ            | <ul><li>Power supply for MPA</li><li>Connect to BK1_VOUT</li></ul>                                                                     |  |

| B8                      | B8                          | P0_1                  | I/O          | <ul> <li>General purpose I/O port P0_1</li> <li>By default, this is configured as forward button (user configurable button)</li> </ul> |  |

| B9                      | B9                          | P2_3                  | I/O          | General purpose I/O port P2_3                                                                                                          |  |

| B10                     | B10                         | XO_P                  | I            | 16 MHz crystal positive input                                                                                                          |  |

| C1                      | C1                          | MIC_N1                | I            | MIC1 mono differential analog negative input                                                                                           |  |

| C2                      | C2                          | DT1                   | 0            | I <sup>2</sup> S interface: ADC digital left/right data                                                                                |  |

| C3                      | C3                          | DR1                   | I/O          | I <sup>2</sup> S interface: DAC digital left/right data                                                                                |  |

| C6                      | C6                          | NC                    | _            | Not connected                                                                                                                          |  |

| continued               |                             |            |              |                                                                                                                                                |

|-------------------------|-----------------------------|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| IS2083BM Ball<br>Number | IS2083BM-2L2 Ball<br>Number | Ball Name  | Ball<br>Type | Description                                                                                                                                    |

| C8                      | C8                          | VDD_IO     | Ρ            | <ul> <li>I/O power supply input</li> <li>Connect to ground through a 1 µF<br/>(X5R/X7R) capacitor</li> </ul>                                   |

| C9                      | C9                          | P1_6/ PWM1 | I/O          | <ul><li>General purpose I/O port P1_6</li><li>PWM1 output</li></ul>                                                                            |

| C10                     | C10                         | XO_N       | I            | 16 MHz crystal negative input                                                                                                                  |

| D1                      | D1                          | MIC_P1     | I            | MIC1 mono differential analog positive input                                                                                                   |

| D2                      | D2                          | MCLK1      | 0            | Primary clock output provided to an external I <sup>2</sup> S device/codec                                                                     |

| D3                      | D3                          | VDD_IO     | Ρ            | <ul> <li>I/O power supply input</li> <li>Connect to LDO31_VO and ground through a 1 µF (X5R/X7R) capacitor</li> </ul>                          |

| D8                      | D8                          | RST_N      | I            | System Reset pin (active-low)                                                                                                                  |

| D9                      | D9                          | P0_5       | I/O          | <ul> <li>General purpose I/O port P0_5</li> <li>By default, this is configured as volume down button (user configurable button)</li> </ul>     |

| D10                     | D10                         | ULPC_VSUS  | Ρ            | <ul> <li>1.2V ULPC output power</li> <li>Maximum loading 1 mA</li> <li>Connect to ground through a 1 µF capacitor</li> </ul>                   |

| E1                      | E1                          | MICBIAS    | Р            | Electric microphone biasing voltage                                                                                                            |

| E2                      | E2                          | DMIC_CLK   | 0            | Digital microphone clock                                                                                                                       |

| E3                      | E3                          | DMIC1_L    | I            | Digital microphone left channel                                                                                                                |

| E5                      | E5                          | GND        | Р            | Ground reference                                                                                                                               |

| E6                      | E6                          | P0_7       | I/O          | General purpose I/O port P0_7                                                                                                                  |

| E8                      | E8                          | P0_2       | I/O          | <ul> <li>General purpose I/O port P0_2</li> <li>By default, this is configured as play/<br/>pause button (user configurable button)</li> </ul> |

| E9                      | E9                          | P2_7       | I/O          | <ul> <li>General purpose I/O port P2_7</li> <li>By default, this is configured as volume up button (user configurable button)</li> </ul>       |

| E10                     | E10                         | VBG        | Ρ            | <ul> <li>Bandgap output reference for<br/>decoupling interference</li> <li>Connect to ground through a 1 µF<br/>capacitor</li> </ul>           |

| F1                      | F1                          | ADAP_IN    | Ρ            | 5V power adapter input to charge the battery in the battery powered applications                                                               |

| F2                      | F2                          | DMIC1_R    | I            | Digital microphone right channel                                                                                                               |

| F3                      | F3                          | AIR        | 1            | Right channel, single-ended analog input                                                                                                       |

| continued               |                             |                        |              |                                                                                                                                                                                                                           |

|-------------------------|-----------------------------|------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IS2083BM Ball<br>Number | IS2083BM-2L2 Ball<br>Number | Ball Name              | Ball<br>Type | Description                                                                                                                                                                                                               |

| F5                      | F5                          | GND                    | Р            | Ground reference                                                                                                                                                                                                          |

| F6                      | F6                          | GND                    | Р            | Ground reference                                                                                                                                                                                                          |

| F8                      | F8                          | P0_0/<br>UART_TX_IND   | 1/0          | <ul> <li>General purpose I/O port P0_0</li> <li>By default, this is configured as<br/>an external codec reset (Embedded<br/>mode)</li> <li>UART_TX_IND (active-high); used to<br/>wake-up host MCU (Host mode)</li> </ul> |

| F9                      | F9                          | P0_3                   | I/O          | <ul> <li>General purpose I/O port P0_3</li> <li>By default, this is configured as reverse button (user configurable button)</li> </ul>                                                                                    |

| F10                     | F10                         | RFLDO_O                | Ρ            | <ul> <li>1.28V RF LDO output for internal use<br/>only</li> <li>Connect to ground through a 1 µF<br/>capacitor</li> </ul>                                                                                                 |

| G1                      | G1                          | BAT_IN                 | Ρ            | <ul><li>Input power supply</li><li>Source can either be a battery or any other power rail on the host board</li></ul>                                                                                                     |

| G2                      | G2                          | P3_2                   | I/O          | <ul> <li>General purpose I/O port P3_2</li> <li>By default, this is configured as<br/>AUX_IN DETECT</li> </ul>                                                                                                            |

| G3                      | G3                          | AIL                    | 1            | Left channel, single-ended analog input                                                                                                                                                                                   |

| G8                      | G8                          | USB_1V2/<br>VDD_CORE   | Ρ            | <ul> <li>1.2V core power input</li> <li>Connect to ground through a 1 µF<br/>(X5R/X7R) capacitor</li> </ul>                                                                                                               |

| G9                      | G9                          | P3_5                   | I/O          | General purpose I/O port P3_5                                                                                                                                                                                             |

| G10                     | G10                         | PMIC_IN                | Ρ            | <ul><li> 1.8V power input for internal blocks</li><li> Connect to BK1_VOUT</li></ul>                                                                                                                                      |

| H1                      | H1                          | SARVDD                 | Ρ            | <ul><li>SAR ADC 1.8V input</li><li>Connect to BK2_O pin</li></ul>                                                                                                                                                         |

| H2                      | H2                          | P0_6                   | I/O          | General purpose I/O port P0_6                                                                                                                                                                                             |

| H3                      | H3                          | P2_6                   | I/O          | General purpose I/O port P2_6                                                                                                                                                                                             |

| H5                      | H5                          | VDD_CORE               | Р            | <ul><li>Core 1.2V power input</li><li>Connect to CLDO_O pin</li></ul>                                                                                                                                                     |

| H8                      | H8                          | AVDD_USB/<br>VDD_IO_10 | Ρ            | <ul> <li>USB power input</li> <li>Connect to LDO31_VO pin</li> <li>Do not connect if USB functionality is not required</li> </ul>                                                                                         |

| continued               | continued                   |                    |              |                                                                                                                                                              |  |  |

|-------------------------|-----------------------------|--------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IS2083BM Ball<br>Number | IS2083BM-2L2 Ball<br>Number | Ball Name          | Ball<br>Type | Description                                                                                                                                                  |  |  |

| H9                      | H9                          | P3_7/<br>UART_CTS  | I/O          | <ul> <li>General purpose I/O port P3_7 (this pin should not be pulled low during start-up)</li> <li>UART CTS</li> </ul>                                      |  |  |

| H10                     | H10                         | CLDO_O/<br>VDD_PLL | Ρ            | <ul> <li>1.2V core LDO output for internal use<br/>only</li> <li>Connect to ground through a 1 µF<br/>capacitor</li> </ul>                                   |  |  |

| J1                      | J1                          | SYS_POWER          | Ρ            | <ul> <li>System power output derived from the ADAP_IN or BAT_IN input</li> <li>Do not connect to any other devices</li> <li>Only for internal use</li> </ul> |  |  |

| J2                      | J2                          | P8_6/<br>UART_RXD  | I/O          | <ul><li>General purpose I/O port P8_6</li><li>UART data input</li></ul>                                                                                      |  |  |

| J3                      | J3                          | P8_5/<br>UART_TXD  | I/O          | <ul><li>General purpose I/O port P8_5</li><li>UART data output</li></ul>                                                                                     |  |  |

| J4                      | J4                          | SK1                | 1            | ADC channel 1                                                                                                                                                |  |  |

| J5                      | J5                          | SK2                | I            | ADC channel 2                                                                                                                                                |  |  |

| J6                      | J6                          | VDD_CORE           | Ρ            | <ul> <li>1.2V core input power supply</li> <li>Connect to ground through a 1 µF<br/>(X5R/X7R) capacitor</li> </ul>                                           |  |  |

| J7                      | J7                          | P3_4/<br>UART_RTS  | I/O          | <ul> <li>General purpose I/O port P3_4</li> <li>System configuration pin (Application mode or Test mode)</li> <li>UART RTS</li> </ul>                        |  |  |

| J8                      | J8                          | LED1               | 0            | LED driver 1                                                                                                                                                 |  |  |

| J9                      | J9                          | LED2               | 0            | LED driver 2                                                                                                                                                 |  |  |

| J10                     | J10                         | USB_DP             | I/O          | Differential data-plus USB                                                                                                                                   |  |  |

| К1                      | K1                          | BK1_VDDC           | Р            | <ul><li>1.5V buck VDD power input</li><li>Connect to SYS_POWER pin</li></ul>                                                                                 |  |  |

| K2                      | К2                          | BK1_LX1            | Р            | 1.5V buck regulator feedback path                                                                                                                            |  |  |

| КЗ                      | К3                          | BK1_VOUT           | Ρ            | <ul><li>1.5V buck regulator output</li><li>Do not connect to other devices</li><li>Only for internal use</li></ul>                                           |  |  |

| K4                      | K4                          | MFB                | I            | Multifunction push button and Power On key                                                                                                                   |  |  |

| К5                      | K5                          | LDO31_VO           | Ρ            | <ul><li> 3V LDO output for VDD_IO power</li><li> Do not calibrate</li></ul>                                                                                  |  |  |

| К6                      | K6                          | LDO31_VIN          | Ρ            | <ul><li>LDO input</li><li>Connect to SYS_POWER</li></ul>                                                                                                     |  |  |

| continued               | continued                   |           |              |                                                                                                                    |  |  |

|-------------------------|-----------------------------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| IS2083BM Ball<br>Number | IS2083BM-2L2 Ball<br>Number | Ball Name | Ball<br>Type | Description                                                                                                        |  |  |

| К7                      | К7                          | BK2_VOUT  | Ρ            | <ul><li>1.8V buck regulator output</li><li>Do not connect to other devices</li><li>Only for internal use</li></ul> |  |  |

| K8                      | K8                          | BK2_LX    | Р            | 1.8V buck regulator feedback path                                                                                  |  |  |

| К9                      | K9                          | BK2_VDD   | Ρ            | <ul><li>1.8V buck VDD power input</li><li>Connect to SYS_POWER pin</li></ul>                                       |  |  |

| K10                     | K10                         | USB_DM    | I/O          | Differential data-minus USB                                                                                        |  |  |

#### Notes:

- 1. The AOHPR, AOHPM and AOHPL pins are not available in the IS2083BM-2L2 variant as it does not support an analog output from the internal DAC.

- 2. The conventions used in the preceding table are indicated as follows:

- I = Input pin

- O = Output pin

- I/O = Input/Output pin

- P = Power pin

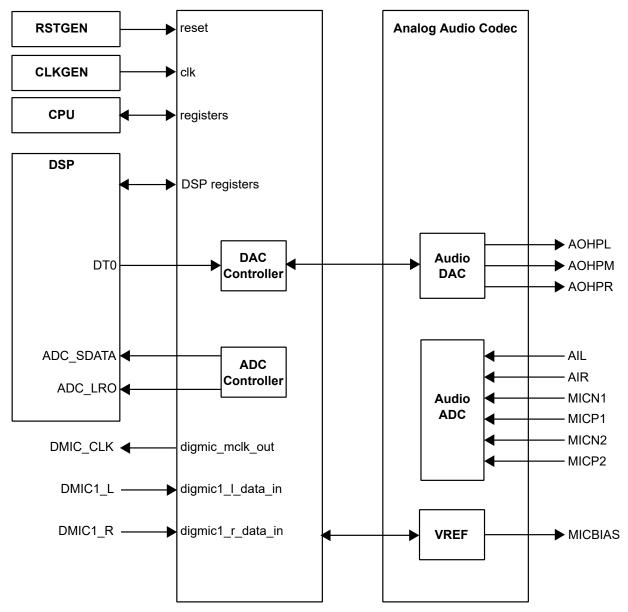

## 3. Audio Subsystem

The input and output audio have different stages and each stage can be programmed to vary the gain response characteristics. For microphones, both single-ended inputs and differential inputs are supported. To maintain a high-quality signal, a stable bias voltage source to the condenser microphone's FET is provided. The DC blocking capacitors can be used at both positive and negative sides of the input. Internally, this analog signal is converted to 16-bit, 8/16 kHz linear PCM data.

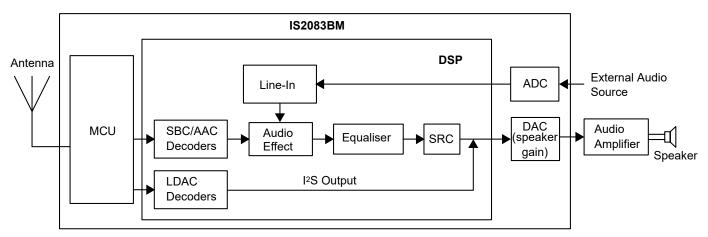

The following figure shows the audio subsystem.

#### Figure 3-1. Audio Subsystem

**Note:** The AOHPL, AOHPM, AOHPR pins are not available in the IS2083BM-2L2 variant.

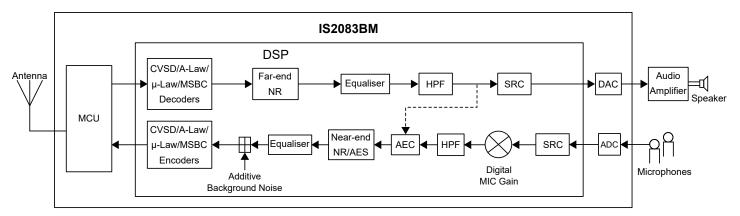

## 3.1 Digital Signal Processor

A Digital Signal Processor (DSP) is used to perform speech and audio processing. The advanced speech features, such as AES and NR are inbuilt. To reduce nonlinear distortion and to help echo cancellation, an outgoing signal level to the speaker is monitored and adjusted to avoid saturation of speaker output or microphone input. In addition, adaptive filtering is applied to track the echo path impulse in response to provide echo free and full-duplex user experience.

The embedded noise reduction algorithm helps to extract clean speech signals from the noisy inputs captured by the microphones and improves mutual understanding in communication. The advanced audio features, such as multiband dynamic range control, parametric multiband equalizer, audio widening and virtual bass are inbuilt. The audio effect algorithms improve the user's audio listening experience in terms of better-quality audio after audio signal processing.

Note: DSP parameters can be configured using the Config Tool.

The following figures illustrate the processing flow of speaker phone applications for speech and audio signal processing.

#### Figure 3-2. Speech Signal Processing

Figure 3-3. Audio Signal Processing

**Note:** LDAC is supported only in the IS2083BM-2L2 device.

The DSP core consists of three computational units (ALU, MAC, and Barrel Shifter), two data address generators, PMD-DMD bus exchanger, program sequencer, bi-directional serial ports (SPORT), DMA controller, interrupt controller, programmable I/O, on-chip program, and on-chip data memory.

The DSP memory subsystem defines the address ranges for the following addressable memory regions:

- Program space

- 96 KB of Program RAM

- 12 KB of Patch RAM

- 64 KB of Coefficient RAM

- Data space

- 96 KB of Data RAM

- I/O Space

- Memory-mapped registers

The DSP core implements a modified Harvard architecture in which data memory stores data and program memory stores both instructions and data (coefficients).

### 3.2 Codec

The built-in codec has a high signal-to-noise ratio (SNR) performance and it consists of an Analog-to-Digital Converter (ADC), a Digital-to-Analog Converter (DAC), and an additional analog circuitry.

- Interfaces

- Two mono differential or single-ended microphone inputs

- One stereo single-ended line input

- One stereo single-ended line output

- One stereo single-ended earphone output (capacitor-less connection)

- Built-in circuit

- Microphone bias (MICBIAS)

- Reference and biasing circuitry

- Optional digital High Pass Filter (HPF) on ADC path

- Silence detection

- Typically, used for Line-In inputs. For some applications, the Line-In input has high priority. After the Line-In input source is plugged in and before streaming out an audio, the Line-In noise cannot be ignored. So, the silence detection feature is used to mute this background noise.

- Anti-pop function to reduce audible glitches

- Pop reduction system

- Soft Mute mode

- Typically used when the codec analog gain is changed suddenly (for example, turning OFF the power or switching the volume dial very quickly), in which case the RCL circuits in the external audio amplifier would cause "pop" noise. The anti-pop function is used to lower or increase the gain in many small steps, 1- or 2-dB change for each step, rather than a single large gain decrease or increase.

- ADC supports 8 kHz, 16 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, and 96 kHz sampling rates.

#### 3.2.1 Audio Performance

This section provides characteristics of the internal codec in the IS2083BM device.

#### Table 3-1. Test Conditions

| Parameter (Condition)        | Value  |

|------------------------------|--------|

| FS                           | 48 kHz |

| Analog gain setting for ADC  | 0 dB   |

| Digital gain setting for ADC | 0 dB   |

| Analog gain setting for DAC  | -3 dB  |

| Digital gain setting for DAC | 0 dB   |

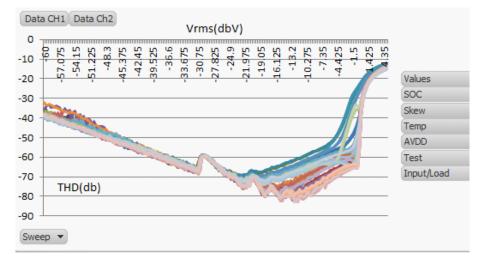

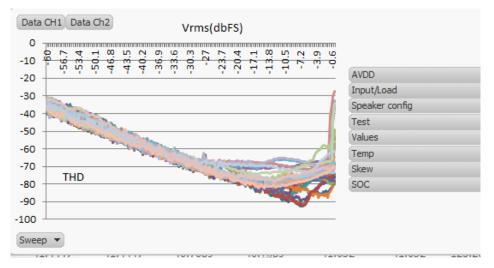

#### Figure 3-4. ADC Signal Quality – THD

Note: Analog Gain = 0 dB, Digital Gain = 0 dB, Sweep Vin= -60 dbV to 5 dbV @ 1 kHz.

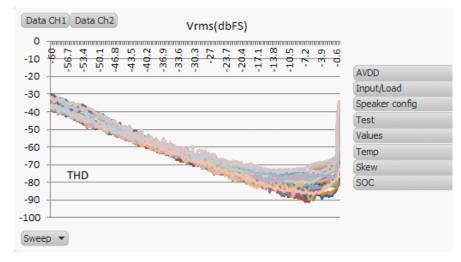

#### Figure 3-5. ADC Signal Quality – THD+N

Note: Analog Gain = 0 dB, Digital Gain = 0 dB, Sweep V<sub>in</sub>= -60 dbV to 5 dbV @ 1 kHz.

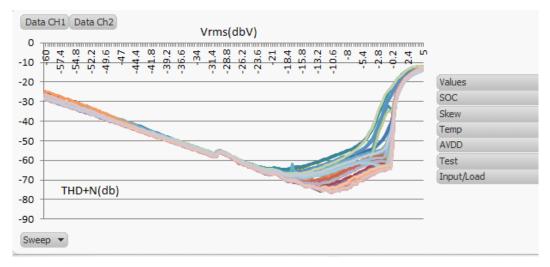

#### Figure 3-6. ADC Dynamic Range

Note: Analog Gain = 0 dB, Digital Gain = 0 dB, Sweep  $V_{in}$ = -100 dbV to 5 dbV @ 1 kHz.

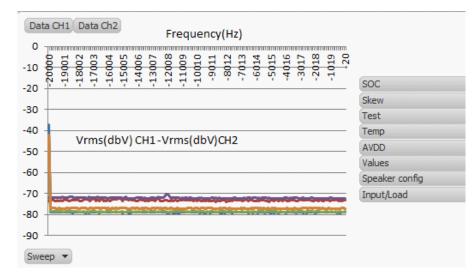

#### Figure 3-7. ADC Frequency Response

Note: Analog Gain = 0 dB, Digital Gain = 0 dB Sweep F<sub>in</sub>= 20 Hz to 20 kHz @ -3 dbV.

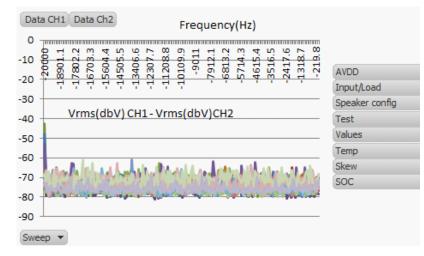

#### Figure 3-8. ADC Crosstalk – Line-In

Note: Analog Gain = 0 dB, Digital Gain = 0 dB Sweep  $F_{in}$ = 20 Hz to 20 kHz @ -3 dbV.

#### Figure 3-9. ADC Crosstalk – Mic-in

Note: Analog Gain = 0 dB, Digital Gain = 0 dB Sweep  $F_{in}$ = 20 Hz to 20 kHz @ -3 dbV.

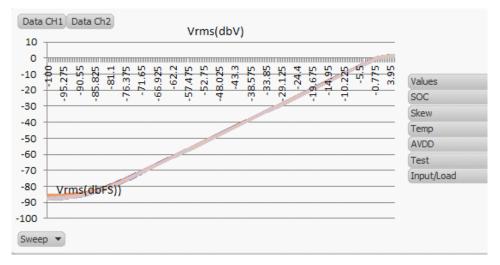

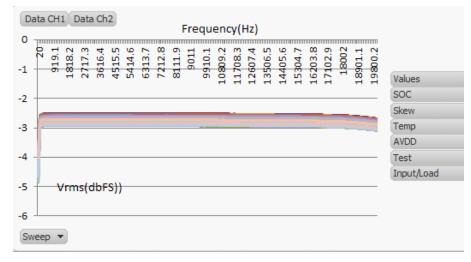

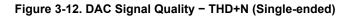

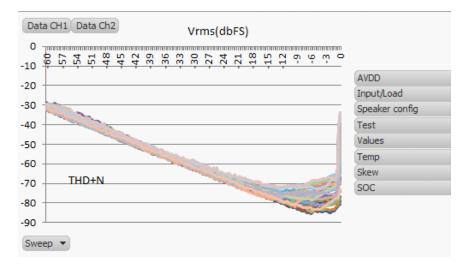

Note: Analog gain = -3 dB, digital gain = 0 dB, sweep V<sub>in</sub> = -60 dBFS to 0 dBFS @ 1 kHz.

Figure 3-11. DAC Signal Quality – THD (Capless)

Note: Analog gain = -3 dB, digital gain = 0 dB, sweep V<sub>in</sub> = -60 dBFS to 0 dBFS @ 1 kHz.

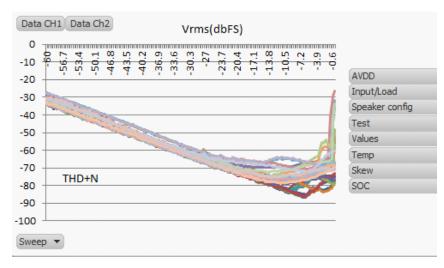

Note: Analog gain = -3 dB, digital gain = 0 dB, sweep  $V_{in}$  = -60 dBFS to 0 dbFS @ 1 kHz.

### Figure 3-13. DAC Signal Quality – THD+N (Capless)

Note: Analog gain = -3 dB, digital gain = 0 dB, sweep V<sub>in</sub> = -60 dBFS to 0 dBFS @ 1 kHz.

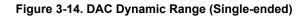

Note: Analog gain = 3 dB, digital gain = 0 dB, sweep  $V_{in}$  = -100 dBFS to 0 dBFS @ 1 kHz.

Figure 3-15. DAC Dynamic Range (Capless)

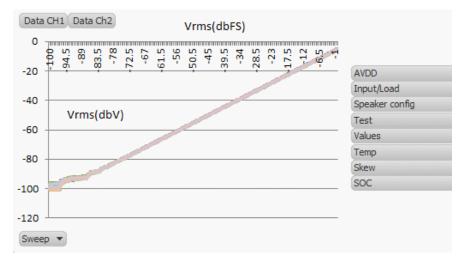

Note: Analog gain = 3 dB, digital gain = 0 dB, sweep  $V_{in}$  = -100 dBFS to 0 dBFS @ 1 kHz.

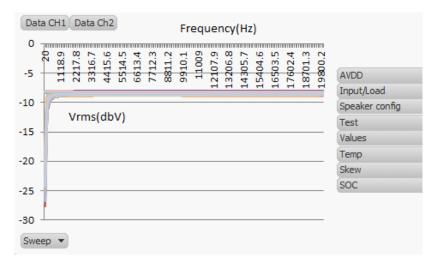

#### Figure 3-16. DAC Frequency Response (Single-ended)

Note: Analog gain = -3 dB, sweep  $f_{in}$  = 20 Hz to 20 kHz @ -3 dBFS.

#### Figure 3-17. DAC Frequency Response (Capless)

Note: Analog gain = -3 dB, sweep  $f_{in}$  = 20 Hz to 20 kHz @ -3 dBFS.

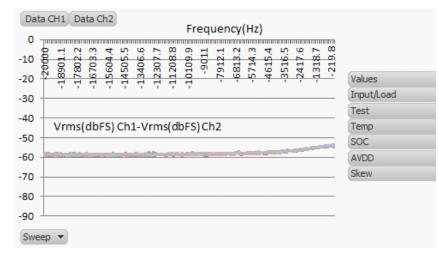

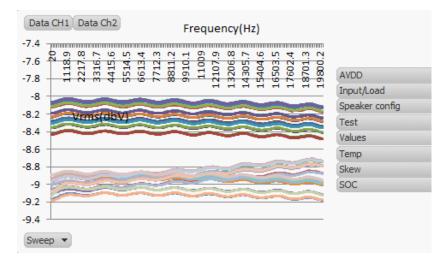

#### Figure 3-18. DAC Crosstalk (Single-ended)

**Note:** Analog gain = -3 dB, sweep  $f_{in}$  = 20 Hz to 20 kHz @ -3 dBFS.

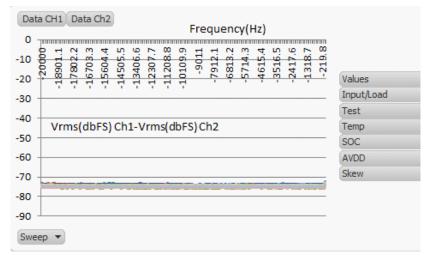

#### Figure 3-19. DAC Crosstalk (Capless)

Note: Analog gain = -3 dB, sweep f<sub>in</sub> = 20 Hz to 20 kHz @ -3 dBFS.

## 3.3 Auxiliary Port

The IS2083BM SoC supports one analog (Line-In, also called as Aux-In) signal from the external audio source. The analog (Line-In) signal can be processed by the DSP to generate different sound effects (multiband dynamic range compression and audio widening), which can be configured by using the Config Tool.

## 3.4 Microphone Inputs

The IS2083BM SoC supports:

- One digital microphone with one (mono) or two channels (stereo L and R)

- Two analog microphones (left and right)

Note: Do not use analog and digital microphones simultaneously.

The DIGMIC interfaces should only be used for PDM digital microphones (typically, MEMS microphones) up to 4 MHz of clock frequency. I<sup>2</sup>S-based digital microphones should use the external I<sup>2</sup>S port.

**Note:** To avoid saturation in the PDM Digital Microphone path, Microchip recommends to limit the PDM maximum input level to -6 dBFS.

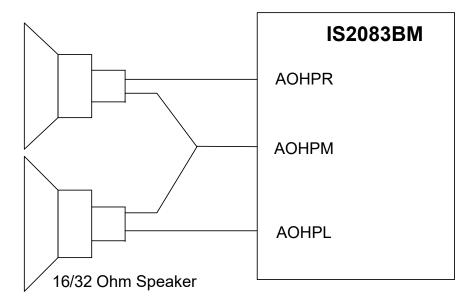

## 3.5 Analog Speaker Output

The IS2083BM SoC supports the following speaker output modes:

Capless mode – Used for headphone applications in which capacitor less (capless) output connection helps to save the Bill of Material (BoM) cost by avoiding a large DC blocking capacitor. The following figure illustrates the Capless mode analog speaker output.

#### Figure 3-20. Capless Mode Analog Speaker Output

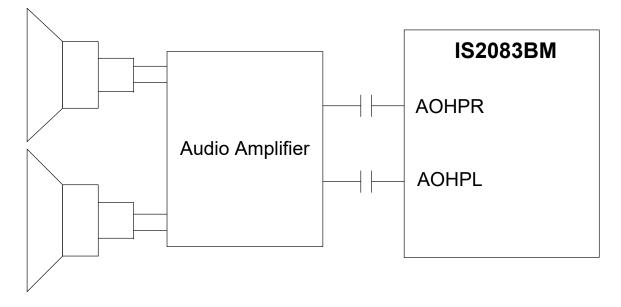

• Single-Ended mode – Used for driving an external audio amplifier where a DC blocking capacitor is required. The following figure illustrates the Single-Ended mode analog speaker output.

Figure 3-21. Single-ended Mode Analog Speaker Output

## 4. Bluetooth Transceiver

The IS2083BM SoC is designed and optimized for Bluetooth 2.4 GHz systems. It contains a complete radio frequency transmitter (TX)/receiver (RX) section. An internal synthesizer generates a stable clock for synchronizing with another device.

## 4.1 Transmitter

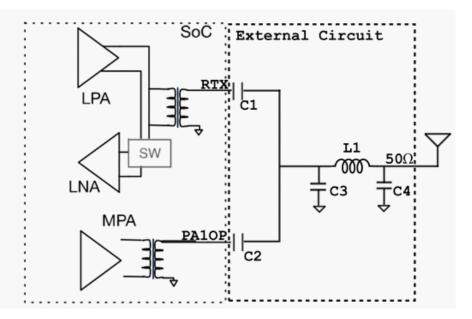

The IS2083BM has Lower Power Amplifier (LPA) and Medium Power Amplifier (MPA). The MPA supports up to +11 dBm power level for Bluetooth Class1 configuration and LPA supports up to about +1 dBm power level for Bluetooth Class2 configuration. The MPA output is connected to the PA1OP pin of the SoC. The LPA output and LNA input are multiplexed and connected to the RTX pin of the device.

The IS2083BM supports shared port configuration, in which the MPA and LPA pins are wired together as shown in the following figure. In shared port configuration, the external series capacitors on RTX, PA1OP pins and PI filter circuit implements a low BoM cost solution to combine the MPA and LPA/LNA signals. Typical value of these components are C1 = 2 pF, C2 = 3 pF, C3 = 1.3 pF/1.4 pF, L1 = 2.7 nH/2.8 nH, C4 = 3 pF (use the BM83 RF schematics as it is to achieve the desired RF performance).

Note: For more details, refer to the IS2083 Reference Design Application Note.

#### Figure 4-1. Shared Port Configuration

## 4.2 Receiver

The Low-Noise Amplifier (LNA) operates in a TR-combined mode for a single port application. It saves a pin on the package without having an external TX/RX switch.

The ADC is used to sample the analog input signal and convert it into a digital signal for demodulator analysis. A channel filter is integrated into the receiver channel before the ADC to reduce the external component count and increase the anti-interference capability.

The image rejection filter is used to reject the image frequency for the low-IF architecture, and it also intended to reduce the external Band Pass Filter (BPF) component for a super heterodyne architecture.

The Received Signal Strength Indicator (RSSI) signal feedback to the processor is used to control the RF output power to make a good trade-off for effective distance and current consumption.

## 4.3 Synthesizer

A synthesizer generates a clock for radio transceiver operation. There is a Voltage Controlled Oscillator (VCO) inside with a tunable internal LC tank that can reduce components variation. A crystal oscillator with an internal digital trimming circuit provides a stable clock for the synthesizer.

### 4.4 Modulator-Demodulator

For Bluetooth 1.2 specification and below, 1 Mbps is the standard data rate based on the Gaussian Frequency Shift Keying (GFSK) modulation scheme. This basic rate modulator-demodulator (Modem) meets Basic Data Rate (BDR) requirements of Bluetooth 2.0 with Enhanced Data Rate (EDR) specifications.

For Bluetooth 2.0 and above specifications, EDR is introduced to provide the data rates of 1/2/3 Mbps. For baseband, both BDR and EDR utilize the same 1 MHz symbol rate and 1.6 kHz slot rate. For BDR, symbol 1 represents 1-bit. However, each symbol in the payload part of the EDR packet represents 2 or 3 bits. This is achieved by using two different modulations,  $\pi/4$  DQPSK and 8 DPSK.

## 4.5 Adaptive Frequency Hopping

The IS2083BM SoC has an Adaptive Frequency Hopping (AFH) function to avoid RF interference. It has an algorithm to check the nearby interference and to choose a clear channel for transceiver Bluetooth signal.

## 5. Microcontroller

A 8051 microcontroller is built into the SoC to execute the Bluetooth protocols. It operates from 16 MHz to higher frequencies where the firmware can dynamically adjust the trade-off between the computing power and the power consumption.

#### Figure 5-1. IS2083BM SoC Block Diagram

The MCU core contains Bluetooth stack and profiles, which are hard-coded into ROM to minimize power consumption for the firmware execution and to save the external Flash cost. This core is responsible for the following system functions:

- Boot-up

- On-the-Air Device Firmware Upgrade (OTA DFU)

- Executing the Bluetooth stack and Bluetooth profiles

- · Sending the packets to DSP core for audio processing

- · Loading audio codec registers with values read the Flash

- Managing low-power modes

- Executing UART commands

- Device programming

- GPIO button control

- PWM control

- LED control

- Bluetooth role swap for multi-speakers

- Adjusting the Bluetooth clock

- External audio codec control/configuration, if needed

- USB battery charge detection and configuration of the PMU battery charger

- Configuration of PMU power regulation

- · Changing the audio subsystem clocks On-the-Fly (OTF) for different audio sampling rates

### 5.1 Memory

A synchronous single port RAM interface is used to fulfill the ROM and RAM requirements of the processor. The register bank, dedicated single port memory and Flash memory are connected to the processor bus. The processor coordinates with all link control procedures and the data movement happens using a set of pointer registers.

## 5.2 Clock

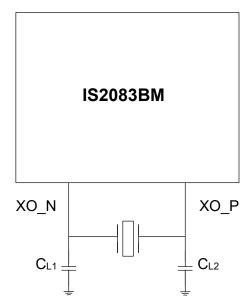

The IS2083BM SoC is composed of an integrated crystal oscillator that uses a 16 MHz  $\pm$ 10 ppm external crystal and two specified loading capacitors to provide a high-quality system reference timer source. This feature is typically used to remove the initial tolerance frequency errors, which are associated with the crystal and its equivalent loading capacitance in the mass production. Frequency trim is achieved by adjusting the crystal loading capacitance through the on-chip trim capacitors (C<sub>trim</sub>).

The crystal trimming can be done using manufacturing tools provided by Microchip. The following figure illustrates the crystal oscillator connection of the IS2083BM SoC with two capacitors.

#### Figure 5-2. Crystal Oscillator in the IS2083BM

The clock module controls switching and synchronization of clock sources. Clock sources include:

- System Phase-locked Loop (PLL)

- · Primary oscillator

- External clock oscillator

- Ultra Low-power internal RC oscillator (UPLC) with nominal frequency as 32 kHz.

The clock module provides gated clock output for 8051 and its peripheral modules, gated clock output for Bluetooth modules as well as DSP audio subsystem. The system enters low power mode by switching OFF clocks driven from the PLL and external oscillator. Only ULPC is operated to maintain Bluetooth timing.

## 6. **Power Management Unit**

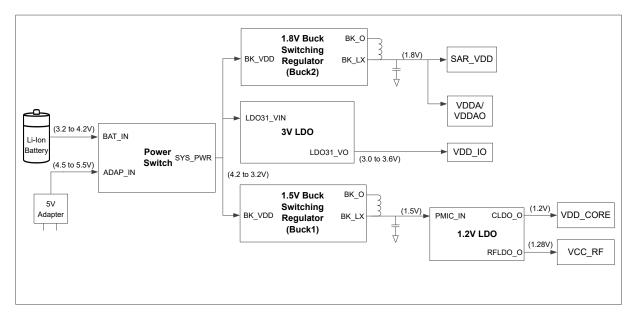

The IS2083BM SoC has an integrated Power Management Unit (PMU). The PMU includes buck switching regulator, LDO, battery charger, SAR ADC for voltage sensing, and LED drivers. The power switch is provided to switch between battery and adapter. It also provides current to the LED drivers.

## 6.1 Device Operation

The IS2083BM SoC is powered through the BAT\_IN input pin. The external 5V power adapter can be connected to the ADAP\_IN pin to charge the battery.

For normal operation, it is recommend to use the BAT\_IN pin to power the IS2083BM SoC and ADAP\_IN only for charging the battery. The following figure illustrates the connection from the BAT\_IN pin to other voltage supply pins of the IS2083BM. The IS2083BM has two buck switching regulators:

- Buck1 DC/DC regulator provides 1.5V and is used to supply power to RF and baseband.

- Buck2 DC/DC regulator provides 1.8V and is used to supply power to I/O pads and internal codec.

#### Figure 6-1. Power Tree Diagram

## 6.2 Power Supply

Typically, the PWR (MFB) pin is connected to a mechanical button on the device. When pressed, it connects the BAT\_IN pin to the power detection block of the PMU. The PMU keeps the  $V_{BAT_IN}$  connected once the PWR pin is released.

## 6.3 Adapter Input

The adapter input (ADAP\_IN) is used for charging the battery. If the total power consumed by IS2083BM SoC is less than 120 mA, ADAP\_IN pin can also be used as power supply input. If the current to be driven is more than 120 mA, it is recommended to use the BAT\_IN pin as the power supply input and the ADAP\_IN pin can be left floating.

## 6.4 Buck1 (BK1) Switching Regulator

The IS2083BM includes a built-in programmable output voltage regulator which converts the battery voltage to 1.5V to supply the RF and baseband power supply. This converter has high conversion efficiency and fast transient response.

Note: Do not connect any other devices to buck1 regulator output pin (BK1\_VOUT).

## 6.5 Buck2 (BK2) Switching Regulator

The IS2083BM includes a second build in programmable output voltage regulator which converts the battery voltage to 1.8V, to supply the PMU ADC and to optionally supply stereo audio codec and/or I/O's. This converter has a high conversion efficiency and a fast-transient response.

Note: Do not connect any other devices to buck2 regulator output pin (BK2\_VOUT).

### 6.6 Low-Droput Regulator

The built-in Low-Dropout (LDO) regulator is used to convert the battery or adapter power to 3.3V to supply the USB transceiver and to supply the I/O's.

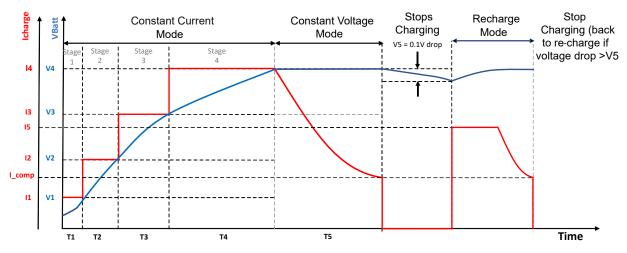

## 6.7 Battery Charging

The IS2083BM SoC has a built-in battery charger that is optimized for lithium-ion and lithium polymer batteries.

The on-chip PMU integrates the battery charger and voltage regulator. A power switch is used to switch over the power source between the battery (BAT\_IN) and an adapter (ADAP\_IN). The PMU provides the current to drive two LEDs.

The battery charger supports various modes with the features listed below:

- Charging control using current sensor

- · User-programmable current regulation

- High accuracy voltage regulation

- Constant current and constant voltage modes

- Stop charging and re-charging modes

The following figure illustrates the charging curve of a battery.

#### Figure 6-2. Battery Charging Curve

**Note:** For more details on battery charger configuration, please refer to the *IS2083/BM83 Battery Charger Application Note (AN3490).*

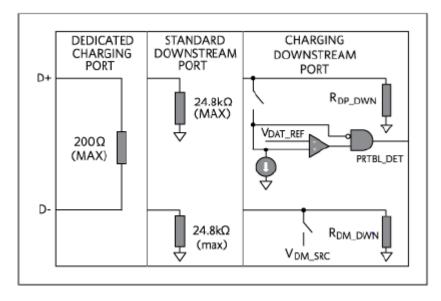

# 6.7.1 Battery Charger Detection

The IS2083BM USB transceiver includes built-in battery charger detection that is compatible with the following:

**USB BC 1.2 Standard Downstream Port (SDP):** This is the same port defined by the USB 2.0 spec and is the typical form found in desktop and laptop computers. The maximum load current is 2.5 mA when suspended, 100mA when connected and not suspended, and 500 mA (max) when connected and configured for higher power.

**USB BC 1.2 Dedicated Charger Port (DCP):** BC 1.2 describes power sources like wall warts and auto adapters that do not enumerate so that charging can occur with no digital communication at all. DCPs can supply up to 1.5A and are identified by a short between D+ to D-. This port does not support any data transfer, but is capable of supplying charge current beyond 1.5A.

Any device (such as the IS2083BM) that connects to any USB receptacle and uses that power to run itself or charge a battery, must know how much current is appropriate to draw. Attempting to draw 1A from a source capable of supplying only 500mA would not be good. An overloaded USB port will likely shut down or blow a fuse. Even with resettable protection, it will often not restart until the device is unplugged and reconnected. In ports with less rigorous protection, an overloaded port can cause the entire system to Reset. Once the USB transceiver determines the battery charger profile and port type (SDP, CDP, DCP), it interrupts the CPU, which then reads the battery charger profile and port type information out of the USB registers. It uses this information to program the PMU (via the 3-wire PMU interface) with the configuration corresponding to the battery charger profile and port type.

#### Figure 6-3. USB Battery Charger 1.2 DCP/SDP/CDP Signaling

# 6.8 SAR ADC

The IS2083BM SoC has a 10-bit Successive Approximation Register (SAR) ADC with ENOB (Effective Number of Bits) of 8-bits; used for battery voltage detection, adapter voltage detection, charger thermal protection, and ambient temperature detection. The input power of the SAR ADC is supplied by the 1.8V output of Buck2. The warning level can be programmed by using the Config Tool or the SDK.

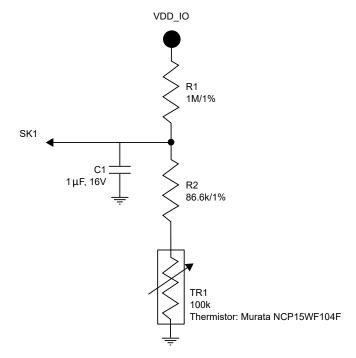

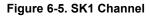

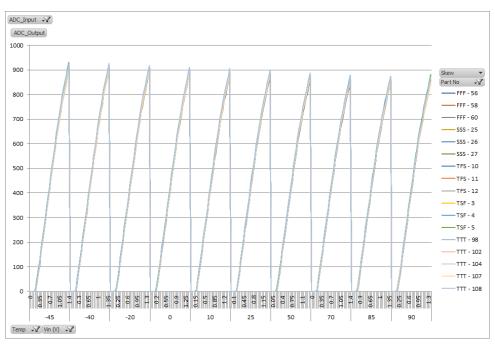

The SK1 and SK2 are the ADC channel pins. The SK1 is used for charger thermal protection. The following figure illustrates the suggested circuit and thermistor, Murata NCP15WF104F. The charger thermal protection can avoid battery charge in a restricted temperature range. The upper and lower limits for temperature values can be configured by using the Config Tool.

### Figure 6-4. Ambient Detection Circuit

**Note:** The thermistor must be placed close to the battery in the user application for accurate temperature measurements and to enable the thermal shutdown feature.

The following figures show SK1 and SK2 channel behavior.

## Figure 6-6. SK2 Channel

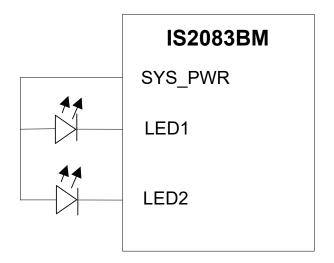

# 6.9 LED Driver

The IS2083BM has two LED drivers to control external LEDs. The LED drivers provide enough sink current (16-step control and 0.35 mA for each step) and the LED can be connected directly to the IS2083BM. The LED settings can be configured by using the Config Tool. The following figure illustrates the LED drivers in the IS2083BM.

# Figure 6-7. LED Driver

# 7. Application Information

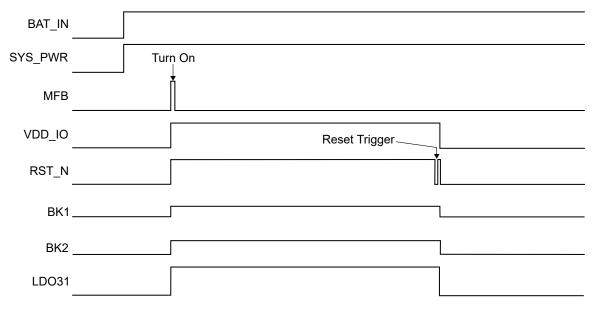

# 7.1 Power On/Off Sequence

In Embedded mode, the BM83 module utilizes the MFB button to turn on and turn off the system. For Host mode, refer to 7.6 Host MCU Interface. The following figure illustrates the system behavior (Embedded mode) upon a MFB press event to turn on and turn off the system.

Figure 7-1. Timing Sequence of Power On/Off in Embedded Mode

| BAT_IN  |                  |  |

|---------|------------------|--|

| SYS_PWR | Turn On Turn Off |  |

| MFB     |                  |  |

| VDD_IO  |                  |  |

| RST_N   |                  |  |

| BK1     |                  |  |

| BK2     |                  |  |

| LDO31   |                  |  |

The following figure illustrates the system behavior (Embedded mode) upon a MFB press event to turn on the system and then trigger a Reset event.

Figure 7-2. Timing Sequence of Power On and Reset Trigger in Embedded Mode

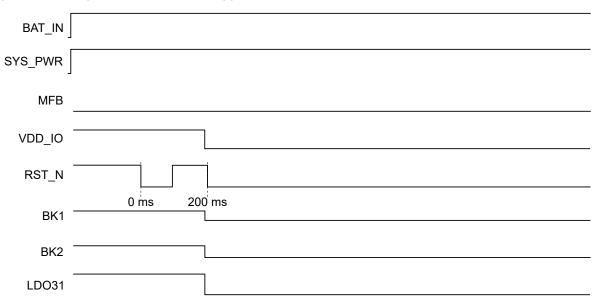

# 7.2 Reset

The Reset logic generates proper sequence to the device during Reset events. The Reset sources include external Reset, power-up Reset, and Watchdog Timer (WDT). The IS2083 SoC provides a WDT to Reset the chip. In addition, it has an integrated Power-on Reset (POR) circuit that resets all circuits to a known Power On state. This action can also be driven by an external Reset signal, which is used to control the device externally by forcing it into a POR state. The following figure illustrates the system behavior upon a RST\_N event.

**Note:** The Reset (RST\_N) is an active-low signal and can be utilized based on the application needs, otherwise, it can be left floating.

# Figure 7-3. Timing Sequence of Reset Trigger

**Note:** RST\_N pin has an internal pull-up, thus, RST\_N signal will transition to high again upon releasing the RST\_N button. This is an expected behavior of RST\_N signal.

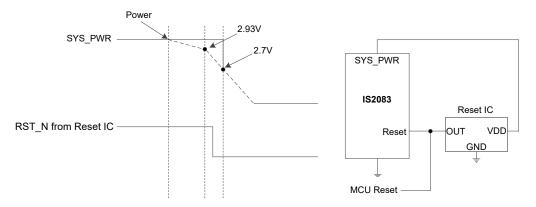

# Figure 7-4. Timing Sequence of Power Drop Protection

Timing sequence of power drop protection:

- It is recommended to use the battery to provide the power supply at BAT\_IN.

- If an external power source or a power adapter is utilized to provide power to BAT\_IN, it is recommended to use a voltage supervisor Integrated Circuit (IC).

- The Reset IC output pin, RST\_N, must be open drain type and threshold voltage as 2.93V.

- The RST\_N signal must be fully pulled low before SYS\_PWR power drop to 2.7V.

# 7.3 **Programming and Debugging**

The IS2083BM devices contain 2 MB of Flash memory, which is interfaced using the Serial Quad Interface (SQI). The following sections describe the Test mode programming and two-wire ICSP debug interface for the SDK user.

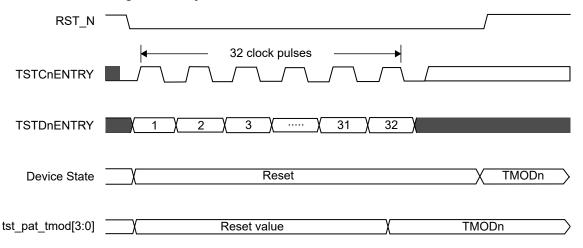

# 7.3.1 Test Mode Programming

The Test mode allows an external UART host to communicate with the device using Bluetooth vendor commands over the UART interface. Also, the host can interface with the device driver firmware to perform firmware programming using the isUpdate tool. The Test mode also supports TX/RX operations and collects/reports Bit Error Rate (BER) and other RF performance parameters. These values can, then, be used to accept/reject the device and/or calibrate the module.

Enter the Test mode by pulling the PORT3\_4 pin to low during start-up/Reset when powered by ADAP\_IN 5V supply. The pin PORT3\_4 can be used as a GPIO pin if the pin level is high during start-up/Reset. The boot code residing in the boot ROM is responsible for identifying this event, setting the CFGMODE [TEST\_MODE] bit and, then, performing a Reset of the device using the RST\_N pin.

The following table provides the configurations required to set the Test mode or Application mode.

## Table 7-1. Test Mode Configuration Settings

| Pins | Status   | Mode             |  |  |

|------|----------|------------------|--|--|

| P3_4 | Low      | Test mode        |  |  |

|      | Floating | Application mode |  |  |

To exit from the Test mode (regardless of how it is entered), the firmware can clear the Test mode bit and perform a device Reset, either by asserting RST\_N pin or by a Software Reset.

# 7.3.2 Two-Wire JTAG Debug Interface

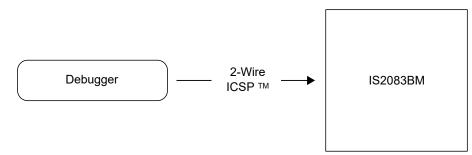

The IS2083BM devices provide a two-wire JTAG interface for SDK debugging (see the following figure). The target device must be powered, and all required signals must be connected. In addition, the interface must be enabled through a special initialization sequence (see 7.3.3 Enabling Debugging Interface).

# Figure 7-5. Two-Wire ICSP Interface

The two-wire ICSP port is used as an interface to connect a Debugger in the IS2083BM device. The following table provides the required pin connections. This interface uses the following two communication lines to transfer data to and from the IS2083BM device being programmed:

- Serial Program Clock (TCK\_CPU)

- Serial Program Data (TDI\_CPU)

These signals are described in the following two sections. Refer to the specific device data sheet for the connection of the signals to the chip pins. The following table describes the two-wire interface pins.

## Table 7-2. Two-Wire Interface Pin Description

| Pin Name                | Pin Type | Description       |

|-------------------------|----------|-------------------|

| RST_N                   | I        | Reset pin         |

| VDD_IO, ADAP_IN, BAT_IN | Р        | Power supply pins |

| GND                     | Р        | Ground pin        |

| TCK_CPU                 | 1        | Serial Clock      |

| TDI_CPU                 | I/O      | Serial Data       |

Note: For more details, refer to the IS2083 SDK Debugger User's Guide available in the SDK package.

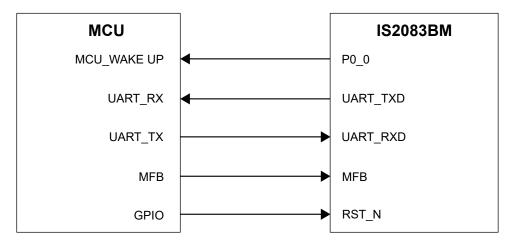

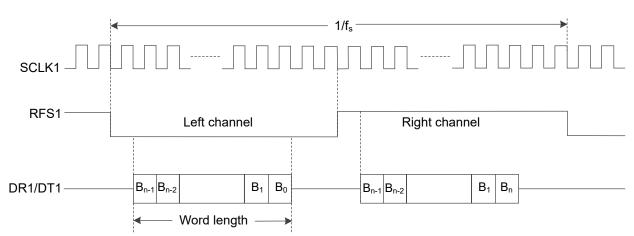

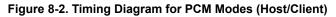

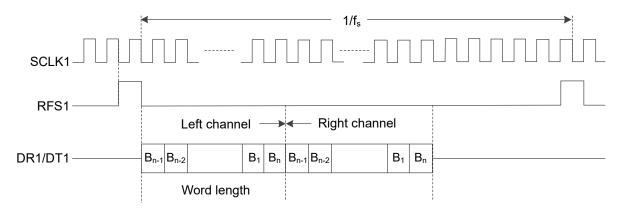

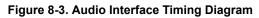

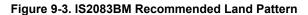

## 7.3.2.1 Serial Program Clock