# RENESAS

# EL4511

# DATASHEET

FN7009 Rev 8.00 November 12, 2010

The EL4511 sync separator IC is designed for operation in the next generation of DTV, HDTV, and projector applications, as well as broadcast equipment and other applications where video signals need to be processed.

The EL4511 accepts sync on green, separate sync, and H/V sync inputs, automatically selecting the relevant format. It is also capable of detecting and decoding tri-level syncs used with the latest HD systems. Unlike standard sync separators, the EL4511 can automatically detect the line rate and locks to it, without the use of an external  $R_{SET}$  resistor.

The EL4511 is available in a 24-pin QSOP package and operates over the full 0°C to 70°C temperature range.

## **Ordering Information**

| PART<br>NUMBER              | PACKAGE                  | TAPE &<br>REEL | PKG. DWG. # |

|-----------------------------|--------------------------|----------------|-------------|

| EL4511CU                    | 24-Pin QSOP              | -              | MDP0040     |

| EL4511CU-T7                 | 24-Pin QSOP              | 7"             | MDP0040     |

| EL4511CU-T13                | 24-Pin QSOP              | 13"            | MDP0040     |

| EL4511CUZ<br>(See Note)     | 24-Pin QSOP<br>(Pb-Free) | -              | MDP0040     |

| EL4511CUZ-T7<br>(See Note)  | 24-Pin QSOP<br>(Pb-Free) | 7"             | MDP0040     |

| EL4511CUZ-T13<br>(See Note) | 24-Pin QSOP<br>(Pb-Free) | 13"            | MDP0040     |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### Features

- · Composite, component, HDTV, and PC signal-compatible

- Tri-level & bi-level sync-compatible

- Auto sync detection

- 150kHz max line rate

- Low power

- Small package outline

- · 3.3V and 5V operation

- · Pb-Free Plus Anneal Available (RoHS Compliant)

## Applications

- · HDTV/DTV analog inputs

- Video projectors

- Computer monitors

- Set top boxes

- Security video

- · Broadcast video equipment

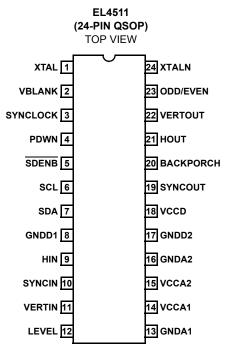

### Pinout

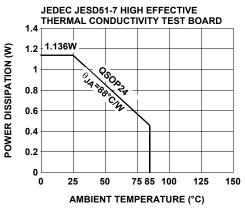

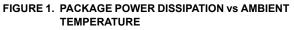

Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

### EL4511

| Supply Voltage                                           | (V <sub>S</sub> to GND) +6V      |

|----------------------------------------------------------|----------------------------------|

| Pin Voltage                                              | GND - 0.3V, V <sub>S</sub> +0.3V |

| V <sub>CCA1</sub> , V <sub>CCA2</sub> & V <sub>CCD</sub> | Must Be Same Voltage             |

| Power Dissipation                                        | See Curves                       |

Storage Temperature Range

-65°C to +150°C

Operating Junction Temperature

125°C

Ambient Operating Temperature

0°C to +70°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

**Electrical Specifications**  $V_S = V_{CCA1} = V_{CCA2} = V_{CCD} = +5V$ ,  $T_A = 25^{\circ}C$ , NTSC input signal on SYNCIN, no output loads, unless otherwise specified.

| PARAMETER                                  | DESCRIPTION                                                           | CONDITIONS                                   | MIN                   | TYP    | MAX      | UNIT           |

|--------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------|-----------------------|--------|----------|----------------|

| GENERAL                                    |                                                                       | ·                                            |                       |        |          | I.             |

| ISD                                        | Digital Supply Current                                                | (Note 1)                                     |                       | 15     | 20       | mA             |

|                                            |                                                                       | Standby PDWN = V <sub>CCD</sub> (Note 2)     |                       | 4      | 20       | μA             |

| ISA2                                       | Rate Acquisition Oscillator Supply                                    | (Note 1)                                     |                       | 3      | 20       | mA             |

|                                            | Current                                                               | Standby PDWN = V <sub>CCD</sub>              |                       | 2.5    | 20       | μA             |

| ISA1                                       | Analog Processing Supply Current                                      | (Note 1)                                     |                       | 3      | 20       | mA             |

|                                            |                                                                       | Standby PDWN = V <sub>CCD</sub> (Note 2)     |                       | 3      | 20       | μA             |

| COMPOSITE SY                               | NC INPUT AT SYNCIN                                                    |                                              |                       |        |          | r              |

| V <sub>SYNC</sub>                          | Sync Signal Amplitude                                                 | AC coupled to SYNCIN pin (Notes 1 & 3)       | 140                   |        | 600      | mV             |

| V <sub>SLICE</sub>                         | Slicing Level of Sync Signal                                          | After sync lock is attained, see description |                       | 50     |          | %              |

| HORIZONTAL A                               | ND VERTICAL INPUT AT H <sub>IN</sub> , VERT                           | IN                                           |                       |        |          | r.             |

| ${\rm H}_{\rm SLICE}, {\rm V}_{\rm SLICE}$ | Slice Level of $H_{\text{IN}}$ and $VERTIN$                           |                                              |                       | 1.4    |          | V              |

| T <sub>HINL</sub> H S                      | H Sync Width<br>(Bi-Level)                                            |                                              | 3                     |        | 12.8     | % of H<br>time |

|                                            | (Tri-Level)                                                           | Minimum Sync Width                           |                       | 1.4    |          | % of H<br>time |

| F <sub>HINH</sub>                          | H Sync Frequency                                                      |                                              | 10.75                 |        | 150      | kHz            |

| T <sub>VINL</sub>                          | V Sync Width                                                          |                                              | 2                     |        | 7        | H lines        |

| F <sub>VINH</sub>                          | V Sync Frequency                                                      |                                              | 23                    |        | 100      | Hz             |

| LOGIC OUTPUT                               | SIGNALS, H <sub>OUT</sub> , V <sub>OUT</sub> , V <sub>BLANK</sub> , B | ACKPORCH, ODD/EVEN, SYNCLOCK                 |                       |        |          | r              |

| O/P <sub>LOW</sub>                         | Logic Low State                                                       | 1.6mA, V <sub>CCD</sub> = 5V                 |                       |        | GNDD+0.4 | V              |

|                                            |                                                                       | 1.6mA, V <sub>CCD</sub> = 3.3V               |                       |        | GNDD+0.5 |                |

| O/P <sub>HI</sub>                          | Logic High State                                                      | 1.6mA, V <sub>CCD</sub> = 5V                 | V <sub>CCD</sub> -0.4 |        |          | V              |

|                                            |                                                                       | 1.6mA, V <sub>CCD</sub> = 3.3V               | V <sub>CCD</sub> -0.5 |        |          |                |

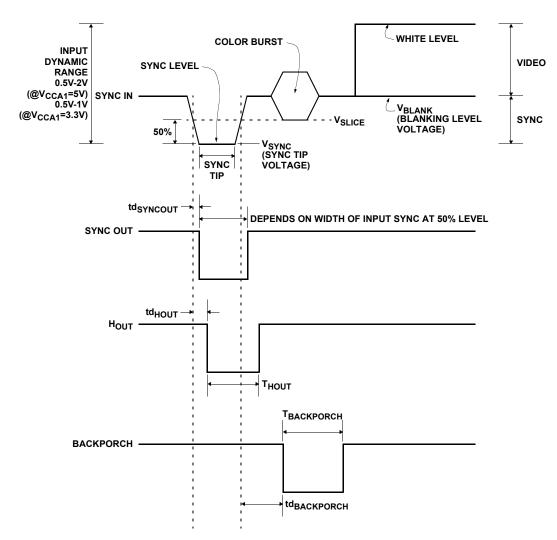

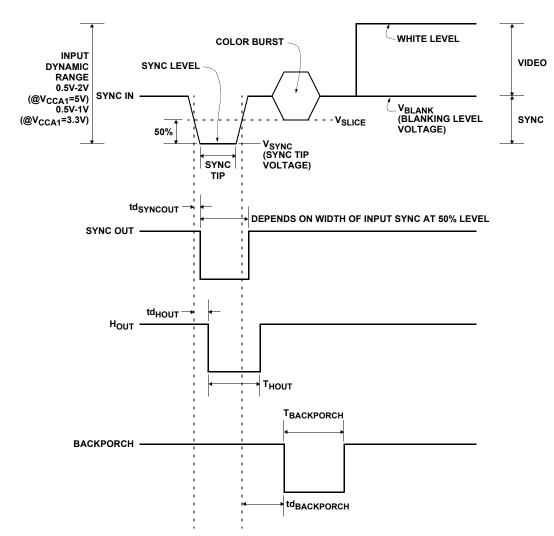

| Td <sub>HOUT</sub>                         | H <sub>OUT</sub> Timing Relative to Input                             | See timing diagrams 1, 2, 3 & 4              |                       |        |          |                |

| Td <sub>SYNCOUT</sub>                      | SYNCOUT Timing Relative to Input                                      | See timing diagrams 1, 2, 3 & 4              |                       |        |          |                |

| Td <sub>BACKPORCH</sub>                    | BACKPORCH Timing Relative to<br>Input                                 | See timing diagrams 1, 2, 3 & 4              |                       |        |          |                |

| LEVEL OUTPUT                               | DRIVER, LEVEL                                                         |                                              |                       |        |          |                |

| V <sub>LEVEL</sub>                         | 2 X Amplitude of V <sub>SYNC</sub>                                    | Refer to description of operation            | 1.9x                  | 2.15x  | 2.4x     |                |

| Z <sub>LEVEL</sub>                         | O/P Resistance of Driver Stage                                        |                                              |                       | 450    |          | Ω              |

| REFERENCE O                                | SCILLATOR                                                             |                                              |                       |        |          |                |

| F <sub>IN</sub>                            | Reference Input Frequency                                             | Refer to description of operation            |                       |        | 50       | kHz            |

| F <sub>XTAL</sub>                          | Crystal Frequency                                                     | Watch crystal (optional)                     |                       | 32.768 |          | kHz            |

# **Electrical Specifications** $V_S = V_{CCA1} = V_{CCA2} = V_{CCD} = +5V$ , $T_A = 25^{\circ}C$ , NTSC input signal on SYNCIN, no output loads, unless otherwise specified. (Continued)

| PARAMETER                                          | DESCRIPTION                    | CONDITIONS | MIN                   | TYP | MAX                  | UNIT |  |  |  |

|----------------------------------------------------|--------------------------------|------------|-----------------------|-----|----------------------|------|--|--|--|

| CONTROL INTERFACE SIGNALS PDWN, SDENB, SCL AND SDA |                                |            |                       |     |                      |      |  |  |  |

| V <sub>HIGH</sub>                                  | Input Logic High Threshold     |            |                       |     | V <sub>CCD</sub> -1V |      |  |  |  |

| V <sub>LOW</sub>                                   | Input Logic Low Threshold      |            | V <sub>GNDD</sub> +1V |     |                      |      |  |  |  |

| 0/PV <sub>HI</sub>                                 | SDA O/P Logic High State       | @ 1mA      | V <sub>CCD</sub> -0.4 |     |                      | V    |  |  |  |

| O/PV <sub>LOW</sub>                                | SDA O/P Logic Low State        | @ 1mA      |                       |     | GNDD+0.4             | V    |  |  |  |

| F <sub>SCL</sub>                                   | Serial Control Clock Frequency |            |                       | 5   |                      | MHz  |  |  |  |

| T <sub>CLS</sub>                                   | Setup Time                     |            |                       | 30  |                      | ns   |  |  |  |

| T <sub>CLH</sub>                                   | Hold Time                      |            |                       | 30  |                      | ns   |  |  |  |

| T <sub>LC</sub>                                    | Load to Clock Time             |            |                       | 30  |                      | ns   |  |  |  |

| T <sub>DC</sub>                                    | Hold to Clock Time             |            |                       | 30  |                      | ns   |  |  |  |

| T <sub>CD</sub>                                    | Clock to Data Out Time         |            |                       | 30  |                      | ns   |  |  |  |

NOTES:

1. NTSC signal; see curves for other rates.

2. XTAL pin must be low, otherwise  $70 \mu A.$

3. I/P range reduces if  $V_{\mbox{S}}$  of 3.3V - 4.5V (see Timing Diagram 1).

# **Pin Descriptions**

| PIN NUMBER | PIN NAME  | PIN TYPE     | PIN DESCRIPTION                                                                                      |

|------------|-----------|--------------|------------------------------------------------------------------------------------------------------|

| 1          | XTAL      | Input        | Crystal input (see Table 2 for details)                                                              |

| 2          | VBLANK    | Logic Output | Vertical blank output                                                                                |

| 3          | SYNCLOCK  | Logic Output | Indicates that the EL4511 has locked to the line rate and has found three consecutive "good H lines" |

| 4          | PWDN      | Logic Input  | Power-down = hi                                                                                      |

| 5          | SDENB     | Logic Input  | Serial interface enable = low                                                                        |

| 6          | SCL       | Logic Input  | Serial clock                                                                                         |

| 7          | SDA       | Logic BIDIR  | Serial data (input for chip setup, output for diagnostic information)                                |

| 8          | GNDD1     | Power        | Digital ground 1                                                                                     |

| 9          | HIN       | Input        | Horizontal sync                                                                                      |

| 10         | SYNCIN    | Input        | Video input, which may incorporate sync signal; connect to Y or G                                    |

| 11         | VERTIN    | Input        | Vertical sync input                                                                                  |

| 12         | LEVEL     | Output       | Indicates 2x amplitude of sync tip vs. back porch; referred to ground                                |

| 13         | GNDA1     | Power        | Analog ground 1                                                                                      |

| 14         | VCCA1     | Power        | Analog power supply 1                                                                                |

| 15         | VCCA2     | Power        | Analog power supply 2                                                                                |

| 16         | GNDA2     | Power        | Analog ground 2                                                                                      |

| 17         | GNDD2     | Power        | Digital ground 2                                                                                     |

| 18         | VCCD1     | Power        | Digital power supply 1                                                                               |

| 19         | SYNCOUT   | Logic Output | Composite sync output                                                                                |

| 20         | BACKPORCH | Logic Output | Back porch output                                                                                    |

| 21         | HOUT      | Logic Output | Horizontal sync output                                                                               |

| 22         | VERTOUT   | Logic Output | Vertical sync output                                                                                 |

| 23         | ODD/EVEN  | Logic Output | Odd-Even field indicator output                                                                      |

| 24         | XTALN     | Output       | Crystal output (see Table 2 for details)                                                             |

# **Typical Performance Curves**

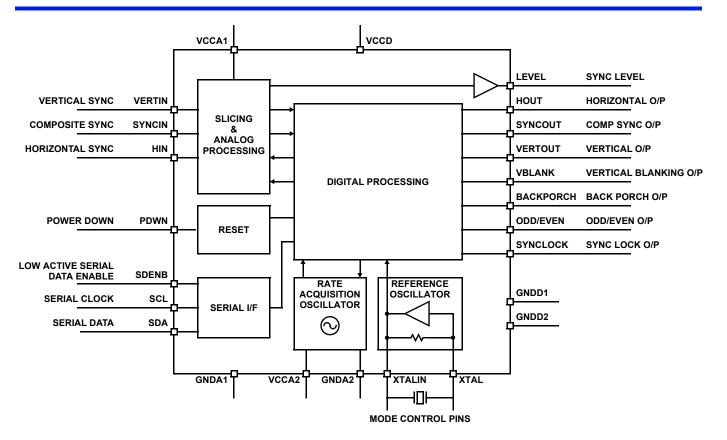

FIGURE 3. BLOCK DIAGRAM

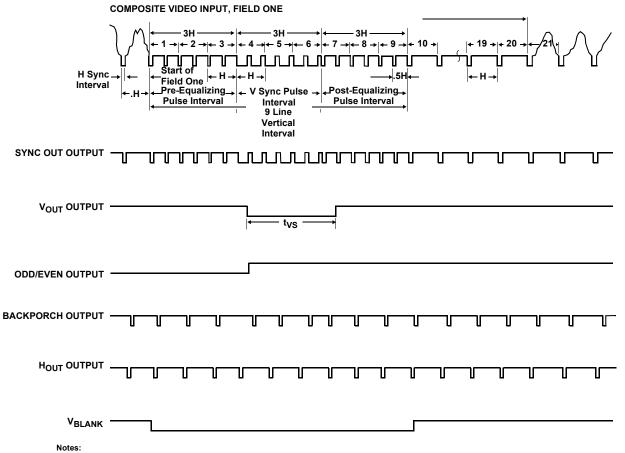

b. The composite sync output reproduces all the video input sync pulses, with a propagation delay.

c. Vertical sync leading edge is coincident with the first vertical serration pulse leading edge, with a propagation delay.

d. Odd-even output is low for even field, and high for odd field.

e. Back porch goes low for a fixed pulse width on the trailing edge of video input sync pulses. Note that for serration pulses during vertical, the back porch starts on the rising edge of the serration pulse (with propagation delay).

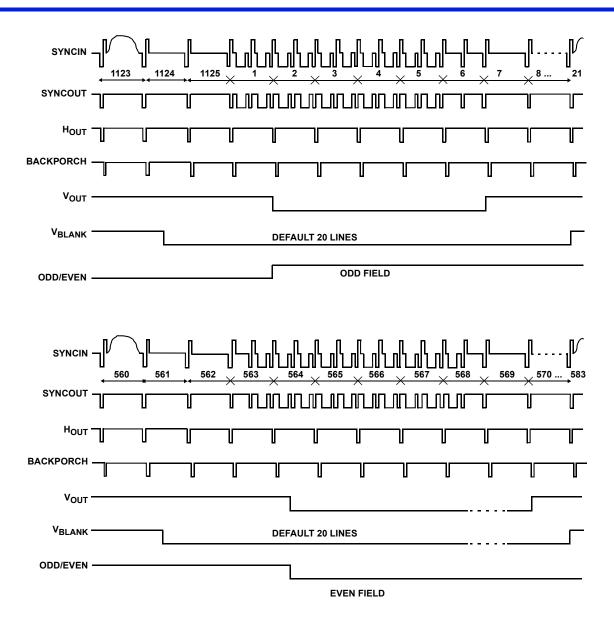

FIGURE 4. EXAMPLE OF VERTICAL INTERVAL (525)

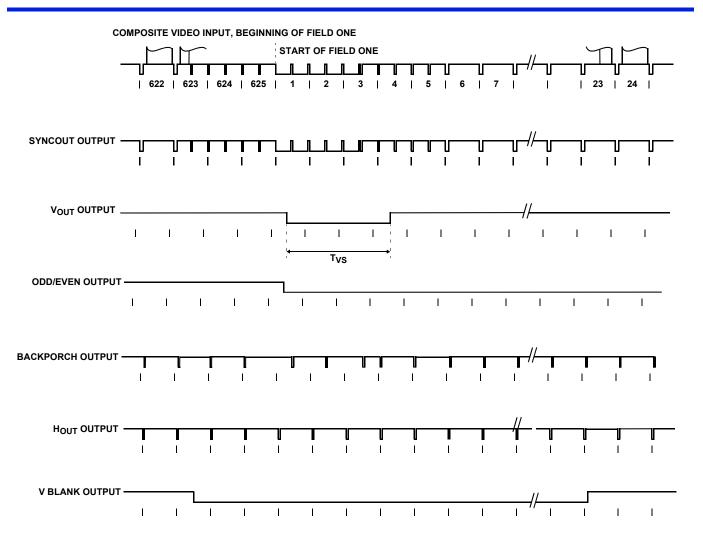

Notes: b. The composite sync output reproduces all the video input sync pulses, with a propagation delay. c. Vertical sync leading edge is coincident with the first vertical serration pulse leading edge, with a propagation delay. d. Odd-even output is low for even field, and high for odd field.

e. Back porch goes low for a fixed pulse width on the trailing edge of video input sync pulses. Note that for serration pulses during vertical, the back porch starts on the rising edge of the serration pulse (with propagation delay).

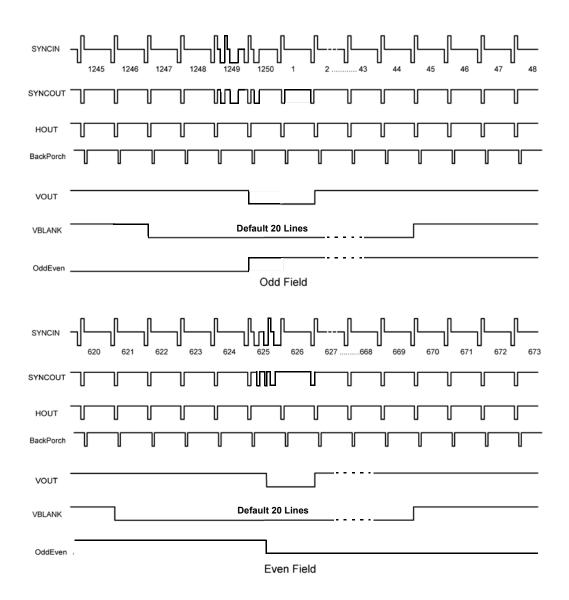

FIGURE 5. EXAMPLE OF VERTICAL INTERVAL (625)

FIGURE 6. EXAMPLE OF HDTV 1080I/30 LINE COMPOSITE VIDEO: INTERLACED, ODD & EVEN FIELD

FIGURE 7. HDTV 1080I/25 LINE COMPOSITE VIDEO: INTERLACED ODD & EVEN FIELD (1250 LINES)

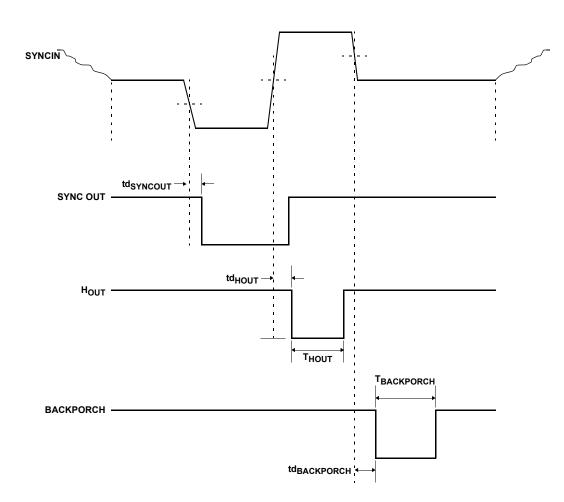

# Timing Diagram 1 - Example of Horizontal Interval 525/625 Line Composite

CONDITIONS:  $V_{CCA1} = V_{CCA2} = V_{CCD} = +5V$ ,  $T_A = 25^{\circ}C$ , NO FILTER (REGISTER 2 BIT 4 = 0)

## No Filter

| PARAMETER               | DESCRIPTION                        | CONDITIONS           | TYP<br>(Note 1) | UNIT |

|-------------------------|------------------------------------|----------------------|-----------------|------|

| td <sub>SYNCOUT</sub>   | SYNCOUT Timing Relative to Input   | See Timing Diagram 1 | 65              | ns   |

| td <sub>HOUT</sub>      | HOUT Timing Relative to Input      | See Timing Diagram 1 | 470             | ns   |

| td <sub>BACKPORCH</sub> | BACKPORCH Timing Relative to Input | See Timing Diagram 1 | 525             | ns   |

| T <sub>HOUT</sub>       | Horizontal Output Width            | See Timing Diagram 1 | 1545            | ns   |

| TBACKPORCH              | BACKPORCH (Clamp) Width            | See Timing Diagram 1 | 3345            | ns   |

NOTE:

# Timing Diagram 2 - Example of Horizontal Interval 525/625 Line Composite

CONDITIONS:  $V_{CCA1} = VC_{CA2} = V_{CCD} = +5V$ ,  $T_A = 25^{\circ}C$ , FILTER IN (REGISTER 2 BIT 4 = 1)

### Filter In

| PARAMETER               | DESCRIPTION                        | CONDITIONS           | TYP<br>(Note 1) | UNIT |

|-------------------------|------------------------------------|----------------------|-----------------|------|

| td <sub>SYNCOUT</sub>   | SYNCOUT Timing Relative to Input   | See Timing Diagram 2 | 220             | ns   |

| td <sub>HOUT</sub>      | HOUT Timing Relative to Input      | See Timing Diagram 2 | 470             | ns   |

| td <sub>BACKPORCH</sub> | BACKPORCH Timing Relative to Input | See Timing Diagram 2 | 525             | ns   |

| T <sub>HOUT</sub>       | Horizontal Output Width            | See Timing Diagram 2 | 1545            | ns   |

| TBACKPORCH              | BACKPORCH (Clamp) Width            | See Timing Diagram 2 | 3345            | ns   |

NOTE:

# Timing Diagram 3 - Example of Horizontal Interval (HDTV) (720p)

CONDITIONS:  $V_{CCA1} = V_{CCA2} = V_{CCD} = +3.3V/+5V$ ,  $T_A = 25^{\circ}C$ , NO FILTER (REGISTER 2 BIT 4 = 0)

# H Timing for HDTV, No Filter (using 720p input signal)

| PARAMETER               | DESCRIPTION                        | CONDITIONS           | TYP<br>@ 3.3V<br>(Note 1) | TYP<br>@ 5V<br>(Note 1) | UNIT |

|-------------------------|------------------------------------|----------------------|---------------------------|-------------------------|------|

| td <sub>SYNCOUT</sub>   | SYNCOUT Timing Relative to Input   | See Timing Diagram 3 | 56                        | 50                      | ns   |

| td <sub>HOUT</sub>      | HOUT Timing Relative to Input      | See Timing Diagram 3 | 48                        | 36                      | ns   |

| td <sub>BACKPORCH</sub> | BACKPORCH Timing Relative to Input | See Timing Diagram 3 | 150                       | 140                     | ns   |

| T <sub>HOUT</sub>       | Horizontal Output Width            | See Timing Diagram 3 | 275                       | 275                     | ns   |

| T <sub>BACKPORCH</sub>  | BACKPORCH (Clamp) Width            | See Timing Diagram 3 | 300                       | 300                     | ns   |

NOTE:

# Timing Diagram 4 - Example of Horizontal Interval (HDTV)

SYNCIN SYNC OUT SYNC OUT HOUT HO

#### CONDITIONS: $V_{CCA1} = V_{CCA2} = V_{CCD} = +3.3V/+5V$ , $T_A = 25^{\circ}C$ , FILTER (REGISTER 2 BIT 4 = 1)

# H Timing for HDTV, With Filter (using 720p input)

| PARAMETER               | DESCRIPTION                        | CONDITIONS           | TYP<br>@ 3.3V<br>(Note 1) | TYP<br>@ 5V<br>(Note 1) | UNIT |

|-------------------------|------------------------------------|----------------------|---------------------------|-------------------------|------|

| td <sub>SYNCOUT</sub>   | SYNCOUT Timing Relative to Input   | See Timing Diagram 4 | 120                       | 110                     | ns   |

| td <sub>HOUT</sub>      | HOUT Timing Relative to Input      | See Timing Diagram 4 | 112                       | 100                     | ns   |

| td <sub>BACKPORCH</sub> | BACKPORCH Timing Relative to Input | See Timing Diagram 4 | 155                       | 140                     | ns   |

| T <sub>HOUT</sub>       | Horizontal Output Width            | See Timing Diagram 4 | 300                       | 300                     | ns   |

| T <sub>BACKPORCH</sub>  | BACKPORCH (Clamp) Width            | See Timing Diagram 4 | 300                       | 300                     | ns   |

NOTE:

**Operation Summarized Table** Default register settings. All with no external analog filter. No Mode setting. 525/625

| OPERATING<br>STANDARD                           | DEFAULT     | PINS 1 &<br>24 XTAL,<br>XTALN | DIGITAL<br>FILTER<br>ENABLED | SYNC<br>LOCK | V<br>BLANK | O/E                   | V <sub>OUT</sub> | H <sub>OUT</sub> | BACK<br>PORCH | SYNC<br>OUT | COMMENTS                                                               |

|-------------------------------------------------|-------------|-------------------------------|------------------------------|--------------|------------|-----------------------|------------------|------------------|---------------|-------------|------------------------------------------------------------------------|

| SDTV (Clean signals)                            |             |                               |                              |              |            |                       |                  |                  |               |             |                                                                        |

| 525 NTSC                                        | Yes         | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct          | Correct       | Correct     |                                                                        |

| 625 PAL                                         | Yes         | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct          | Correct       | Correct     |                                                                        |

| 625 SECAM                                       | Yes         | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct          | Correct       | Correct     |                                                                        |

| SDTV (VHS tape signals)                         |             |                               |                              | 1            |            | L                     |                  |                  | I             | I           |                                                                        |

| 525 NTSC                                        | Yes         | 00                            | default                      |              | Correct    | Correct               | Correct          | Correct          | Correct       | Correct     | Will break up with Fast Forward and Fast Reverse modes.                |

| 625 PAL                                         | Yes         | 00                            | default                      |              | Correct    | Correct               | Correct          | Correct          | Correct       | Correct     | Will break up with Fast Forward and Fast Reverse modes.                |

| 625 SECAM                                       | Yes         | 00                            | default                      |              | Correct    | Correct               | Correct          | Correct          | Correct       | Correct     | Will break up with Fast Forward and Fast Reverse modes.                |

| SDTV (525 only)                                 |             |                               |                              |              |            |                       |                  |                  |               |             |                                                                        |

| Macrovision VHS O/P                             | Yes         | 00                            | default                      | See Note     | See Note   | See Note              | See Note         | See Note         | See Note      | See Note    | This operation works on most machines, but some combinations will fail |

| Macrovision DVD O/P                             | Yes         | 00                            | default                      | Bad          | See Note   | See Note              | See Note         | See Note         | See Note      | See Note    | Short drop out on one field, likely some machines will fail.           |

| EDTV Bi-Level Sync<br>No O/E output for some of | these stand | ards, becau                   | se no serratio               | ons during v | vertical   |                       |                  |                  |               |             |                                                                        |

| 480 I / (29/30)                                 | Yes         | 00                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct          | Correct       | Correct     |                                                                        |

| 480 I / (59/60)                                 | Yes         | 00                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct          | Correct       | Correct     |                                                                        |

| 480 P / (59/60)                                 | Yes         | 00                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct          | Correct       | Correct     |                                                                        |

| 576 P / (50)                                    | Yes         | 00                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct          | Correct       | Correct     |                                                                        |

| HDTV Tri-Level Sync                             |             |                               |                              |              |            |                       |                  |                  |               |             |                                                                        |

| 720 P / (59/60)                                 | Yes         | 00                            | default                      | Correct      | Correct    | Always H<br>(correct) | Correct          | Correct          | Correct       | Correct     |                                                                        |

| 1080 I /24                                      | Yes         | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct          | Correct       | Correct     |                                                                        |

| 1080 I / 25                                     | Yes         | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct          | Correct       | Correct     |                                                                        |

**Operation Summarized Table** Default register settings. All with no external analog filter. No Mode setting. 525/625 (Continued)

| OPERATING<br>STANDARD             | DEFAULT      | PINS 1 &<br>24 XTAL,<br>XTALN | DIGITAL<br>FILTER<br>ENABLED | SYNC<br>LOCK | V<br>BLANK | O/E                   | V <sub>OUT</sub> | Ноит    | BACK<br>PORCH | SYNC<br>OUT | COMMENTS               |

|-----------------------------------|--------------|-------------------------------|------------------------------|--------------|------------|-----------------------|------------------|---------|---------------|-------------|------------------------|

| 1080 I / (29/30)                  | Yes          | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct | Correct       | Correct     |                        |

| 1080 I / (48/50)                  | Yes          | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct | Correct       | Correct     |                        |

| 1080 I / (59/60)                  | Yes          | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct | Correct       | Correct     |                        |

| 1035 I / (29/30)                  | Yes          | 00                            | default                      | Correct      | Correct    | Correct               | Correct          | Correct | Correct       | Correct     |                        |

| 1080 P /<br>(24/35/30/50/59/60)   | Yes          | 00                            | default                      | Correct      | Correct    | Always H<br>(correct) | Correct          | Correct | Correct       | Correct     |                        |

| VGA<br>All standards generated by | / the Quantu | ım are supp                   | orted except ?               | 1024@42H     | z and work | ОК                    |                  |         |               |             |                        |

| 640 /X (6 standards)              | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     |                        |

| 720                               | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     |                        |

| 800/X (5 standards)               | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     |                        |

| 1024/X (4 of 5 standards)         | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     | 1024@42 not supported  |

| 1152                              | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     |                        |

| 1280/X (5 standards)              | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     |                        |

| 1600/X (5 standards)              | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     |                        |

| 1792/X (2 standards)              | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     |                        |

| 1836/X (2 standards)              | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     | Max Line rate 112.5kHz |

| 1920/X (2 standards)              | Yes          | 11                            | default                      | Correct      | Correct    | Always H              | Correct          | Correct | Correct       | Correct     | Max Line rate 112.5kHz |

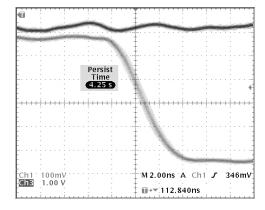

# Timing Diagram 5 - 720p Standard with Filter in Circuit

This waveform shows the output jitter present on the  $H_{OUT}$  signal. The oscilloscope is triggered from the positive reference edge of the composite sync output.

# **Description of Operation**

The EL4511 has 3 modes of operation. The first is default mode with pins 1 and 24 connected to ground with 10K. Second is using pins 1 and 24 to provide simple mode control. The third is using the serial port to use a crystal or a clock into XTALN pin 24 to determine the video sync rate and/or more extensive mode control.

The EL4511 incorporates the following functional blocks:

- · Analog I/Ps, processing, and slicing

- · Signal source and polarity detector

- Signal & H rate acquisition block

- Advanced sync separator which will detect both conventional and tri-level sync signals

- · Video lock and level indicators

- Reference counter

- · Computer and control interface

#### Analog I/Ps, Processing, and Slicing

The EL4511 has three I/P pins which may be connected to a source of external sync signals.

For YPrPb or RGB applications, Y or G should be connected to SYNCIN. For applications with separate horizontal and vertical sync inputs, these should be connected to HIN and VERTIN, respectively. (HIN may also be used for composite sync without video.)

**Composite video input signals** should be connected to SYNCIN. This should be AC coupled from a low impedance source. The input resistance is in the order of  $100k\Omega$ . After H lock is obtained, this signal will be "soft clamped" (5k $\Omega$ ) to approximately 20% of the V<sub>CCA1</sub> voltage.

In the default mode, the clamping action ensures that the correct slicing levels will be used throughout the field.

**(Serial Mode)** This operation can be modified through Register 9. The soft clamp can be disabled by setting bit 3 to

Hi. Setting bit 1 to high will disconnect the input bias network.

Once the acquisition process is complete (see below for description), the slice level will be adaptive. The sync signal is measured from sync tip to blanking level; (Tri-level is measured between negative and positive sync tips). The slice level is then set to 50% of these levels.

**(Serial Mode)** It is possible to force the slicing level to remain at the fixed level of 78mV above the sync tip; Register 2, bit 5 is set High to do this. This can help when dealing with signal that have bursts of noise, or formats that have signals that will modify the sync amplitude measurement process.

VGA type of signals will be connected to the HIN and VERTIN pins (use HIN for combined H & V). These are DC coupled signals; they will be sliced at a fixed level of approximately 1.4V. These inputs may be any combination of positive and negative polarities; the EL4511 will invert as required to keep the outputs in the correct polarity. (Serial Mode) This polarity correction process may be modified with Register 4 bits 3:0.

#### Signal and Horizontal Rate Acquisition Block

On power-up, if both HIN and SYNCIN are enabled; the

EL4511 will slice the SYNCIN input at 78mV above the negative sync tip level and monitor the sliced signal for up to 320µs. If a periodic signal within the specified frequency limits is found to be present, this is assumed to be the horizontal frequency. If no signal is found, the EL4511 will switch to slice and monitor the HIN input at a TTL level. The EL4511 will continue to monitor these two signals in turn until an appropriate signal is detected.

If only one of HIN and SYNCIN is enabled, the EL4511 will continuously monitor the selected signal until an appropriate signal is detected; this will give a shorter lock time where only one type of signal is used. At this point, the rate acquisition oscillator lock process (to the H rate signal) will begin.

### Video Format Switching

The part should be powered down for at least 500µs to reset the internal registers when the input video signal is switched from one video format to another video format. It is possible the part will generate wrong outputs if it is not powered down between two different input video signals.

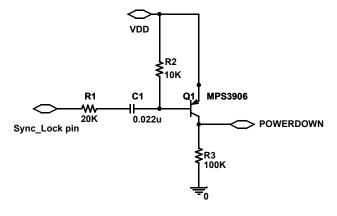

#### USE OF THE POWER DOWN FUNCTION

The Power down pin (pin 4) can be used to hard reset the internal circuit of the EL4511. To disable the internal circuit, just apply a 5V to the power down pin. To enable the internal circuit, just apply a 0V to the power down pin.

The SYNCLOCK pin 3 minus edge can be used to generate a 5V 500 $\mu$ s pulse to the PDWN pin 4 to reset the internal digital registers automatically when the video input has a changed video format.

### Horizontal Rate Acquisition Oscillator

This oscillator is frequency locked to 512 times the horizontal rate. This clock signal generates the timing and gating signals that are employed internally by the EL4511. This operation is entirely automatic and requires no input from the external circuitry or microprocessor.

(Serial Mode) It is possible to gain access to this oscillator O/P by changing the assignment of pin 2 ( $V_{BLANK}$ ) or pin 23 (ODD/EVEN).

Register 6, bits 7:6 make this selection; see Table 1 for allocations.

| TABLE 1. | ACQUISITION | сгоск | MULTIPLEXER |  |

|----------|-------------|-------|-------------|--|

|          |             | 02001 |             |  |

| CmuxCtrl      | ACTION                                            |  |  |  |  |

|---------------|---------------------------------------------------|--|--|--|--|

| Reg6<br>b7 b6 |                                                   |  |  |  |  |

| 0 0           | Normal Operation                                  |  |  |  |  |

| 0 1           | Clock multiplexed onto Odd/Even (pin 23)          |  |  |  |  |

| 1 0           | Clock multiplexed onto V <sub>BLANK</sub> (pin 2) |  |  |  |  |

| 1 1           | Reserved                                          |  |  |  |  |

(Serial Mode) The oscillator frequency is adjusted at the beginning of the line. At the time of frequency adjustment the clock O/P may have a phase discontinuity.

#### Advanced Sync Separator

Once the line rate has been determined, the signal can be analyzed by the advanced sync separator. This has been designed to be compatible with a wide range of video standards, operating with horizontal line rates up to 150kHz. PAL/NTSC/SECAM; HDTV, including bi-level and tri-level sync Standards and computer display syncs. The EL4511 can be programmed to disable the detection of either bi-level or tri-level sync signals or to prioritize the detection of one sync signal type over the other.

If the vertical sync input pin, VERTIN, is enabled, the EL4511 will automatically detect whether a valid signal is present on that pin, and incorporate that signal into the algorithm. Otherwise, the input signal on which the horizontal sync was detected will be treated as a composite sync. The sync separator also includes a qualification scheme which rejects high frequency noise and other video artifacts, such as color burst. The horizontal line rate is automatically acquired from the signal (see above.) A digital filter is included in the signal path to remove noise and glitches; this may be removed if the extra delay it incurs needs to be removed. **(Serial Mode)** Setting register 2, bit 4 to Low will remove the filter.

After the signal has been identified and the qualification process is complete, the SYNCLOCK pin will go high and the output waveforms will be enabled. **(Serial Mode)** These may be enabled all the time by setting register 1, bit 6 to a high state. This can help noisy and varying signals as the revalidation does not have to take place before the signals are available at the outputs, See Figures 4 through 7 for examples of various types of input signal.

Part of the signal recognition algorithm uses the number of horizontal lines between vertical pulses. A counter is clocked by the Hclock, this counter is also used to generate vertical timing pulses. **(Serial Mode)** This count information is available via the serial I/F; this is a 12 bit number.

(Serial Mode) The lines per frame count is available at register 8, bits 7:4 for the MSBs; the LSBs are available at register 7, bits 7:0. Register 8, bit 2 indicates that the lines/frame counter has been updated when it is high.

This counter also generates the  $V_{BLANK}$  waveform. Using a look up table, the default blanking is based on number of lines in the field. **(Serial Mode)** This operation may be disabled by setting register 3, bit 7 to a low. As this is dependent on application and product usage, this may be modified. Register 3, bits 6:0 will set the number of horizontal lines after VERTOUT leading edge. Register 4, bits 7:4 sets the number of lines before the VERTOUT leading edge.

#### Video Lock and Level Indicators

Loss of video signal can be detected by monitoring the SYNCLOCK pin 3. This pin goes high once the sync separator has detected a valid sync signal and goes low if this signal is lost for more than 20 successive lines. **(Serial Mode)** This signal is also available at register 14 pin 5. Other lock acquisition signals available from the system are listed in Table 4.

The sync tip amplitude is buffered with a nominal gain of 2.15 to produce a positive, ground-referenced signal on the LEVEL pin. This output can be used for AGC applications.

#### Decode Mode

In order to allow more flexibility when operating without a serial interface, the XTAL and XTALN pins are decoded by default to enable four control modes. These modes could be used to over-ride sync type used. See Table 2 for details.

**(Serial Mode)** The all-signal type allowed mode is the same as the default mode when the crystal oscillator is enabled (set bit 6 of Reg9 to 1) except the countsPerField function is disabled in Reg13 and Reg14.

The bi-level mode is for bi-level sync only, such as NTSC and PAL. The tri-level mode is for tri-level sync only, such as HDTV signals. The VGA only mode is for computer digital types of signals signal only.

| ENXTAL           | PIN 1<br>XTAL | PIN 24<br>XTALN | MODE<br>CONTROL       | DESCRIPTION                          |

|------------------|---------------|-----------------|-----------------------|--------------------------------------|

| Register9<br>b 6 |               |                 | Register1<br>b5 b4 b3 |                                      |

| 0                | 0             | 0               | 0 0 0                 | All signals<br>enabled               |

| 0                | 0             | 1               | 0 1 1                 | Tri-Level Only                       |

| 0                | 1             | 0               | 1 0 1                 | Bi-Level Only                        |

| 0                | 1             | 1               | 1 1 1                 | VGA only                             |

| 1                | х             | х               | Set by<br>Serial I/F  | Crystal Oscillator<br>is operational |

#### TABLE 2. MODE CONTROL USING PINS 1 & 24

### Applications Examples

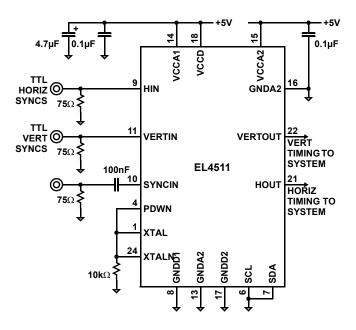

The following examples show how a system may be configured to operate the EL4511.

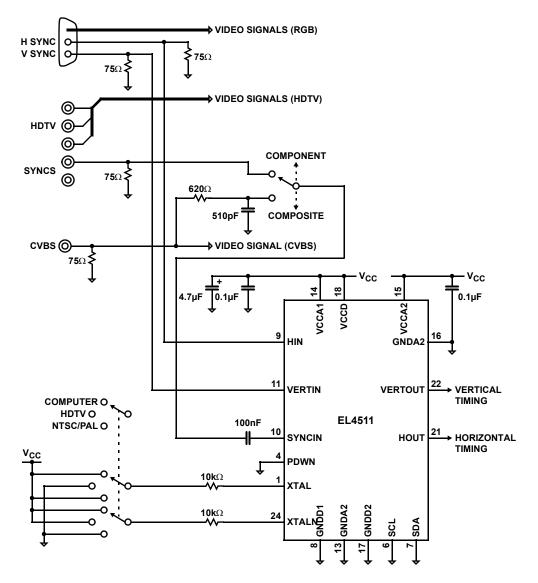

#### Application 1 (minimum circuitry application)

In this example, the requirement is for vertical and horizontal timing to be generated from either an NTSC/PAL composite video waveform, or a computer generated image with separate TTL level syncs.

The EL4511 has the advantage that the sync separation is carried out over a wide frequency range without the need to adjust " $R_{SET}$ " as required by earlier generations of sync separators.

As there is no Microcontroller connected in this example, there is no need for a XTAL at pins 1 & 24. These pins are tied low, this enables the EL4511 to check for either type of input signal (See Table 2 for details.)

The internal pull-up resistors on XTAL & XTALN are very high, these pins should use  $10k\Omega$  pull-up/down to operate when not using a crystal.

By default, the EL4511 will wake up with Register 9, bit 6 set to Low. This will allow the use of logic levels on pins 1 & 24 to drive register1, bits 5:3 and register 2 bit 0 into the combinations shown in Table 2.

**(Serial Mode)** To define the mode through the serial interface, the register 9, bit 6 must be set to High, the logic levels on pins 1 & 24 are no longer valid; (most likely now being an AC signal for the reference clock).

FIGURE 8. APPLICATIONS DRAWING 1

# Application 2 (application using mode setting logic signals)

In this example, the requirement is to provide the synchronizing information in a small display device. In this example the incoming sync signals may come from one of three sources. Computer, HDTV Set-top Box or an NTSC/PAL tuner.

The EL4511 has the advantage that the sync separation is carried out over a wide frequency range without the need to

adjust "R<sub>SET</sub>" as required by earlier generations of sync separators.

As there is no Microcontroller connected in this example, there is no need for a XTAL at pins 1 & 24. These pins can be used to force the EL4511 to select the correct operation (and speed up acquisition).

Note that a Low Pas Filter is in the NTSC/PAL signal path to reduce noise, glitches and subcarrier. (In signals with bad Croma/Luma gain balance, the subcarrier can extend into the sync slicing level) (See Table 2 for details.)

FIGURE 9. APPLICATIONS DRAWING 2

## Serial Mode Operation

See "Description of Operation" for more details of **(Serial Mode)**.

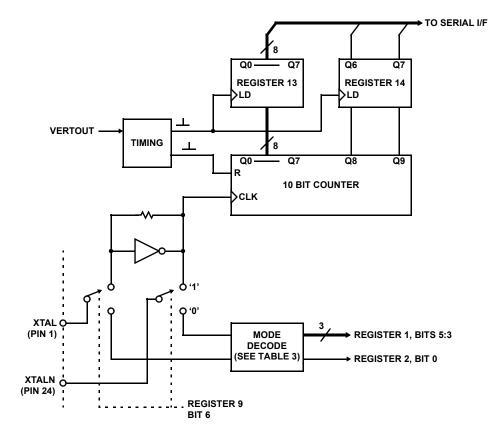

#### Using the Reference Oscillator and Counter

A counter is provided for measuring the vertical time interval; this counts the clocks at the XTAL pin 1 between vertical pulses.

This information is not necessary for the operation of the chip; only for information to the system micro-control. The count value is read from register 14 at bits 7:6 for the MSBs, the LSBs are available in register 13, bits 7:0. Register 14, bit 4 should be a high to indicate that the read operation did not collide with the up-date timing.

If the crystal oscillator is enabled through the serial interface (Register 9, bit 6, ENXTAL), the XTAL and XTALN pins will become the crystal input and crystal output pins for the 32.7kHz crystal. It is also possible to drive the XTAL pin with a logic level clock up to a maximum of 50kHz; this signal is only used to measure the vertical rate.

#### Example:

Using a 32.768kHz crystal, the count period is 30.52µs. With a 20ms vertical rate, there will be approximately 656 cycles (290 Hex) in the "counts per field" registers 13 and 14. With a 16.666'ms vertical rate, the count of 546 (222 Hex) will be seen.

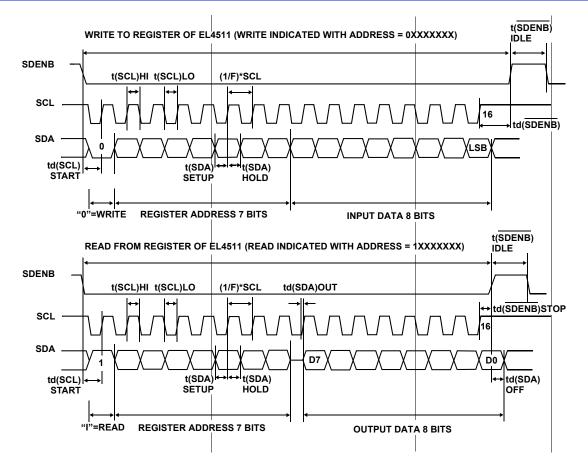

#### **Computer & Control Interface**

In addition to the mode control pins, the chips default operating mode may be changed by way of a serial interface. This is of the three-wire type, Data, clock and /enable. After the /ENABLE line (pin 5) is taken low, the 16 bits of data on the SDA pin 7 will be clocked into the chip by the clock signal SCL pin 6. See Figure 10.

The first bit of the data determines whether it will be a read or write operation. When set to a "0", a write operation will take place. The following 7 bits, select the register to be written to. Finally, the last 8 bits are the data to be written or read. For a read operation, the first bit is a "1".

In general, when registers entries are changed, the unchanged register bits must have the "Reset Values" entered as defined by Table 5.

FIGURE 10. BLOCK DIAGRAM OF REFERENCE OSCILLATOR

# TABLE 3. MODE CONTROL TRUTH TABLE (see also Table 2 for hardware over-ride)

|   |           |         | EnTri<br>Level | EnBi<br>Level | EnHin<br>Vin | TriLevel<br>Priority | Hin<br>Priority | HinVin<br>Only |

|---|-----------|---------|----------------|---------------|--------------|----------------------|-----------------|----------------|

|   | leg<br>b4 | 1<br>b3 |                |               |              |                      |                 |                |

| 0 | 0         | 0       | 1              | 1             | 1            | 0                    | 0               | 0              |

| 0 | 0         | 1       | 1              | 1             | 1            | 0                    | 1               | 0              |

| 0 | 1         | 0       | 1              | 1             | 1            | 1                    | 0               | 0              |

| 0 | 1         | 1       | 1              | 0             | 0            | 1                    | 0               | 0              |

| 1 | 0         | 0       | 0              | 1             | 1            | 0                    | 0               | 0              |

| 1 | 0         | 1       | 0              | 1             | 0            | 0                    | 0               | 0              |

| 1 | 1         | 0       | 0              | 1             | 1            | 0                    | 1               | 0              |

| 1 | 1         | 1       | 0              | 1             | 1            | 0                    | 1               | 1              |

EnTriLevel, EnBiLevel and EnHinVin; these enable tri-level sync detection, two-level sync detection and separate H/V (VGA) sync detection, respectively.

Other signals used to prioritize tri-level syncs (TriLevPriority), separate H/V (Hin Priority), or to only allow signals from HIN/VERTIN (HinVinOnly).

#### TABLE 4. ACQUISITION CONTROL SIGNALS

| REGISTER | BIT | SIGNAL<br>NAME        | DESCRIPTION                                                      |

|----------|-----|-----------------------|------------------------------------------------------------------|

| 8        | 3   | En50Slice             | 1 = Sample and Hold front<br>end is in use                       |

| 8        | 1   | Progressive           | 1 = Progressive scan<br>detected                                 |

| 8        | 0   | Tri-Level<br>Detected | 1 = Tri-Level syncs detected                                     |

| 9        | 5   | ENLEVEL<br>BLANKING   | 1 = V <sub>LEVEL</sub> is available<br>when system is not locked |

| 9        | 4   | ENLEVEL               | 1 = Disable V <sub>LEVEL</sub> Output                            |

| 9        | 2   | ENALOS                | 1 = Analog loss of signal not used in lock indication.           |

| 14       | 5   | SYNCLOCK              | Same information as SYNCLOCK pin 3                               |

| 16       | 4   | RateLocked            | Line rate is locked                                              |

| 16       | 3   | ALOS                  | Sync Amplitude is below minimum                                  |

#### TABLE 5. SERIAL INTERFACE REGISTER BIT ALLOCATIONS

| REGISTER<br>NUMBER | REGISTER<br>BIT | SIGNAL NAME                         | TYPE | RESET<br>VALUE | DESCRIPTION AND COMMENTS                                            |

|--------------------|-----------------|-------------------------------------|------|----------------|---------------------------------------------------------------------|

| 1                  |                 | General Control Reg 1               | R/W  | 00h            |                                                                     |

|                    | 7               | General Reset                       |      | 0              | Software reset. Does not affect serial interface.                   |

|                    | 6               | AlwaysEnOutputs                     |      | 0              | Overrides internal qualification of outputs.                        |

|                    | 5:3             | ModeCtrl                            |      | 0              | Sync acquisition. Selects input signal. See Table 3.                |

| 2                  |                 | General Control Reg 2               | R/W  | 10h            |                                                                     |

|                    | 5               | Select Fixed Slicing (no S/H)       |      | 0              | Necessary for SECAM. May be useful for VCRs.                        |

|                    | 4               | FILTER_ENABLED                      |      | 1              | Set Hi to include digital filter on horizontal input.               |

|                    | 1               | OE_MODE                             |      | 0              | Set Hi for Odd/Even changes on rising edge of vertical.             |

| 3                  |                 | V <sub>BLANK</sub> Control Reg 1    | R/W  | 90h            |                                                                     |

|                    | 7               | EnVBlank                            |      | 1              | Enables vertical blank interval detection algorithm.                |

|                    | 6:0             | VSTPlusBP                           |      | 10h            | Number of lines after vertical sync time.                           |

| 4                  |                 | V <sub>BLANK</sub> & Polarity Ctrl  | R/W  | 4Fh            |                                                                     |

|                    | 7:4             | VFrontPorch                         |      | 4h             | Number of lines before vertical sync time.                          |

|                    | 3               | DefaultHPolarity                    |      | 1              | HIN polarity on reset if EnHpolarityDet = Lo.                       |

|                    | 2               | DefaultVPolarity                    |      | 1              | VERTIN polarity on reset and if EnVpolarityDet = Lo.                |

|                    | 1               | EnHPolarityDet                      |      | 1              | Allows EL4511 to detect and set polarity on HIN.                    |

|                    | 0               | EnVPolarityDet                      |      | 1              | Allows EL4511 to detect and set polarity on VERTIN.                 |

| 6                  |                 | Oscillator Control 2                | R/W  | 22h            |                                                                     |

|                    | 7:6             | CMuxCtrl <1:0>                      |      | 0              | Multiplexes clock onto $V_{\mbox{BLANK}}$ or Odd/Even. See Table 1. |

| 7                  |                 | V <sub>BLANK</sub> O/P Reg 1        | R    |                | Only valid if V <sub>BLANK</sub> circuit is enabled                 |

|                    | 7:0             | LinesPerFrame <7:0>                 |      | -              | Least significant byte of lines per frame count.                    |

| 8                  |                 | V <sub>BLANK</sub> O/P Reg 2 & Misc | R    | 80h            |                                                                     |

| REGISTER<br>NUMBER | REGISTER<br>BIT | SIGNAL NAME                   | TYPE | RESET<br>VALUE | DESCRIPTION AND COMMENTS                                                                         |

|--------------------|-----------------|-------------------------------|------|----------------|--------------------------------------------------------------------------------------------------|

|                    | 7:4             | LinesPerFrame <11:8>          |      | -              | Most significant 4 bits of lines per frame count.                                                |

|                    | 3               | En50Slice                     |      | -              | Indicates sample and hold front end is being used.                                               |

|                    | 2               | LPFValid                      |      | -              | Indicates lines per frame has been updated.                                                      |

|                    | 1               | progressive                   |      | -              | Not valid for certain types of composite sync.                                                   |

|                    | 0               | tri-level detect              |      | -              | Only valid if tri-level sync detected.                                                           |

| 9                  |                 | Analog Control Reg 1          | R/W  |                |                                                                                                  |

|                    | 6               | ENXTAL                        |      | 0              | Set Hi to enable crystal oscillator.                                                             |

|                    | 5               | ENLEVELBLANKING               |      | 0              | Set Hi to enable V <sub>LEVEL</sub> when not locked.                                             |

|                    | 4               | ENLEVEL                       |      | 0              | Set Hi to disable V <sub>LEVEL</sub> output.                                                     |

|                    | 3               | ENSYCLAMP                     |      | 0              | Set Hi to disable "soft" sync tip clamping in SYNCIN.                                            |

|                    | 2               | ENALOS                        |      | 0              | Set Hi to disable analog loss of signal feature.                                                 |

|                    | 1               | ENRVIDEO                      |      | 0              | Set Hi to disable internal biasing on SYNCIN (passive resistor or soft clamp.)                   |

|                    | 0               | PWRSAVE                       |      | 0              | Set Hi to put the analog circuit into powersave mode.                                            |

| 13                 |                 | Absolute Timing Ref 1         | R    |                |                                                                                                  |

|                    | 7:0             | CountsPerField <7:0>          |      | -              | Crystal clock periods per field: L.S. Byte. (see description)                                    |

| 14                 |                 | Absolute Timing Ref 2 & Misc  | R    |                |                                                                                                  |

|                    | 7:6             | CountsPerField <9:8>          |      | -              | Crystal clock periods per field: Bits 9:8. (see description)                                     |

|                    | 5               | SyncLock                      |      |                | As sync lock pin.                                                                                |

|                    | 4               | CPFValid                      |      | -              | Counts per field valid. Set L if read occurs during an update.                                   |

|                    | 3               | SetBiLevel                    |      | -              | Lo: Tri-level mode; Hi: Bi-level mode.                                                           |

|                    | 2               | VinSyncDet                    |      | -              | Indicates vertical sync on VERTIN successfully acquired.                                         |

|                    | 1               | VinPolarity                   |      | -              | VERTIN polarity setting: Observe.                                                                |

|                    | 0               | HPolarity                     |      | -              | HIN polarity setting: Observe.                                                                   |

| 16                 |                 | Oscillator Settings Observe 2 | R    |                |                                                                                                  |

|                    | 4               | RateLocked                    |      | -              | Indicates line rate successfully acquired.                                                       |

|                    | 3               | ALOS                          |      | -              | Analog loss of signal, measured via S/H. H indicates analog signal amplitude is below threshold. |

#### TABLE 5. SERIAL INTERFACE REGISTER BIT ALLOCATIONS (Continued)

FIGURE 11. SERIAL INTERFACE TIMING DIAGRAM

© Copyright Intersil Americas LLC 2002-2010. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <u>www.intersil.com/en/support/qualandreliability.html</u>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN7009 Rev 8.00 November 12, 2010

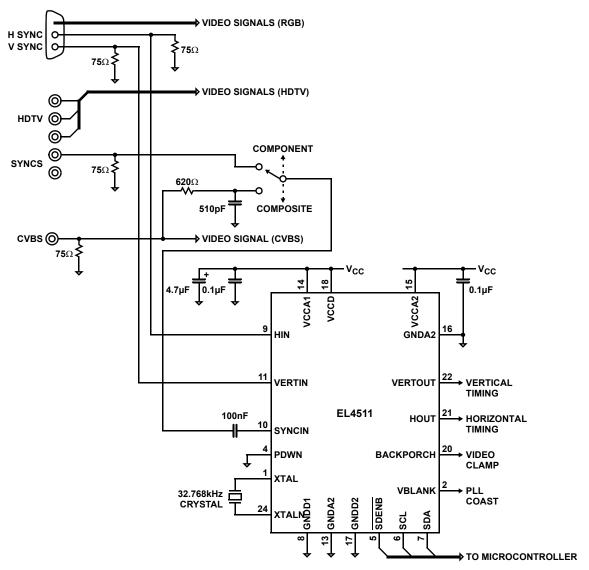

# Application 3 (application using a microcontroller interface)

In this example, the requirement is to provide the synchronizing information in a video digitizing interface. This example is very similar to the example in application 2. In this example the incoming sync signals may come from one of three sources. Computer, HDTV source or an NTSC/PAL device.

As there is a Microcontroller connected in this example, a 32.768kHz XTAL is connected to pins 1 & 24; this will allow the system microcontroller to gather timing information for the

vertical rate. To enable the crystal oscillator, register 9, bit 6 must be set to a high.

Note that a Low Pass Filter is in the NTSC/PAL signal path to reduce noise, glitches and subcarrier. (In signals with bad Croma/Luma gain balance, the subcarrier can extend into the sync slicing level).

As some of the signals in this application were non standard formats, the fixed slice mode is used by setting register 2, bit 5 to a high. Register 1, bit 6 is also set to a high. This forced the EL4511 to provide outputs even when the input signals are not recognized by the internal algorithms.

FIGURE 12. APPLICATIONS DRAWING 3

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics: EL4511CUZ EL4511CUZ-T13 EL4511CUZ-T7 EL4511CUZ-T7A