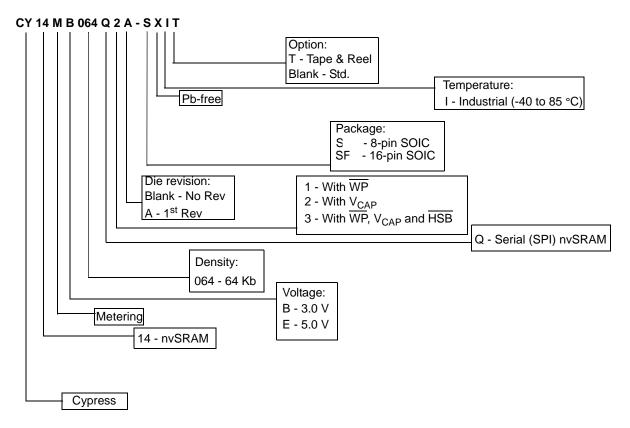

# 64-Kbit (8 K × 8) SPI nvSRAM

#### **Features**

- 64-Kbit nonvolatile static random access memory (nvSRAM) internally organized as 8 K x 8

- □ STORE to QuantumTrap nonvolatile elements initiated automatically on power-down (AutoStore) or by using SPI instruction (Software STORE) or HSB pin (Hardware STORE)

- □ RECALL to SRAM initiated on power-up (Power-Up RECALL) or by SPI instruction (Software RECALL)

- □ Support automatic STORE on power-down with a small capacitor (except for CY14MX064Q1A)

- High reliability

- ☐ Infinite read, write, and RECALL cycles

- □ 1million STORE cycles to QuantumTrap

- □ Data retention: 20 years at 85 °C

- High speed serial peripheral interface (SPI)

- □ 40-MHz clock rate SPI write and read with zero cycle delay

- □ Supports SPI mode 0 (0,0) and mode 3 (1,1)

- SPI access to special functions

- □ Nonvolatile STORE/RECALL

- □ 8-byte serial number

- □ Manufacturer ID and Product ID

- □ Sleep mode

- Write protection

- ☐ Hardware protection using Write Protect (WP) pin

- ☐ Software protection using Write Disable instruction

- □ Software block protection for 1/4, 1/2, or entire array

- Low power consumption

- □ Average active current of 3 mA at 40 MHz operation

- Average standby mode current of 150 μA

- Sleep mode current of 8 μA

- Industry standard configurations

- Operating voltages:

- CY14MB064Q:  $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$

- CY14ME064Q: V<sub>CC</sub> = 4.5 V to 5.5 V

- Industrial temperature

- □ 8- and 16-pin small outline integrated circuit (SOIC) package

- □ Restriction of hazardous substances (RoHS) compliant

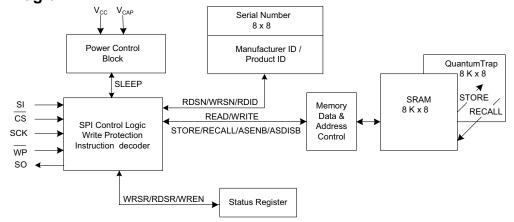

#### **Functional Overview**

The Cypress CY14MX064Q combines a 64 Kbit nvSRAM with a nonvolatile element in each memory cell with serial SPI interface. The memory is organized as 8 K words of 8 bits each. The embedded nonvolatile elements incorporate the QuantumTrap technology, creating the world's most reliable nonvolatile memory. The SRAM provides infinite read and write cycles, while the QuantumTrap cells provide highly reliable nonvolatile storage of data. Data transfers from SRAM to the nonvolatile elements (STORE operation) takes place automatically at power-down (except for CY14MX064Q1A). On power-up, data is restored to the SRAM from the nonvolatile memory (RECALL operation). You can also initiate the STORE and RECALL operations through SPI instruction.

For a complete list of related documentation, click here.

## Configuration

| Feature           | CY14MX064Q1A | CY14MX064Q2A | CY14MX064Q3A |

|-------------------|--------------|--------------|--------------|

| AutoStore         | No           | Yes          | Yes          |

| Software<br>STORE | Yes          | Yes          | Yes          |

| Hardware<br>STORE | No           | No           | Yes          |

# Logic Block Diagram

#### **Contents**

| Pinouts                                             | 3 |

|-----------------------------------------------------|---|

| Pin Definitions                                     | 3 |

| Device Operation                                    |   |

| SRAM Write                                          |   |

| SRAM Read                                           |   |

| STORE Operation                                     |   |

| AutoStore Operation                                 |   |

| Software STORE Operation                            |   |

| Hardware STORE and HSB pin Operation                |   |

| RECALL Operation                                    |   |

| Hardware RECALL (Power-Up)                          |   |

| Software RECALL                                     |   |

| Disabling and Enabling AutoStore                    |   |

| Serial Peripheral Interface                         |   |

| SPI Overview                                        |   |

| SPI Modes                                           |   |

| SPI Operating Features                              |   |

| Power-Up                                            |   |

| Power-Down                                          |   |

| Active Power and Standby Power Modes                |   |

| SPI Functional Description                          |   |

| Status Register1                                    |   |

| Read Status Register (RDSR) Instruction             |   |

| Write Status Register (WRSR) Instruction            |   |

| Write Protection and Block Protection               |   |

| Write Enable (WREN) Instruction                     |   |

| Write Disable (WRDI) Instruction1 Block Protection1 |   |

| Hardware Write Protection (WP)1                     |   |

| Memory Access1                                      |   |

| Read Sequence (READ) Instruction                    |   |

| Write Sequence (WRITE) Instruction                  |   |

| nvSRAM Special Instructions1                        |   |

| Software STORE (STORE) Instruction1                 |   |

| Software RECALL (RECALL) Instruction1               |   |

| AutoStore Enable (ASENB) Instruction                |   |

| AutoStore Disable (ASDISR) Instruction 1            |   |

| Special Instructions                        | . 15     |

|---------------------------------------------|----------|

| SLEEP Instruction                           | . 15     |

| Serial Number                               |          |

| WRSN (Serial Number Write) Instruction      | . 15     |

| RDSN (Serial Number Read) Instruction       | . 16     |

| Device ID                                   | . 16     |

| RDID (Device ID Read) Instruction           | . 16     |

| HOLD Pin Operation                          | . 17     |

| Maximum Ratings                             | . 18     |

| Operating Range                             | . 18     |

| DC Electrical Characteristics               | . 18     |

| Data Retention and Endurance                | . 19     |

| Capacitance                                 |          |

| Thermal Resistance                          |          |

| AC Test Loads and Waveforms                 |          |

| AC Test Conditions                          |          |

| AC Switching Characteristics                |          |

| Switching Waveforms                         |          |

| AutoStore or Power-Up RECALL                |          |

| Switching Waveforms                         |          |

| Software Controlled STORE and RECALL Cycles |          |

| Switching Waveforms                         |          |

| Hardware STORE Cycle                        |          |

| Switching Waveforms                         |          |

| Ordering Information                        |          |

| Ordering Code Definitions                   |          |

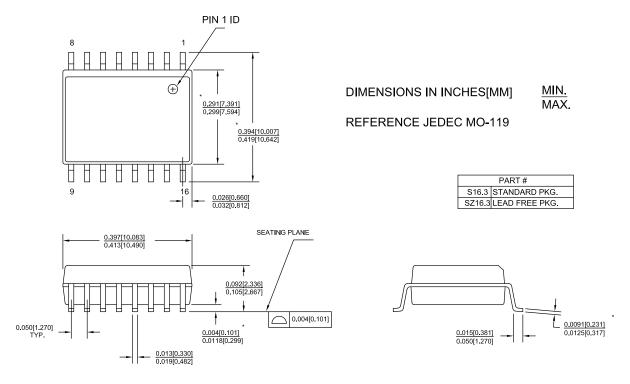

| Package Diagrams                            |          |

| Acronyms                                    |          |

| Document Conventions                        |          |

| Units of Measure                            |          |

| Document History Page                       |          |

| Sales, Solutions, and Legal Information     | . 31     |

| Worldwide Sales and Design Support          |          |

| Products                                    |          |

| PSoC® Solutions                             | $\sim 4$ |

|                                             | -        |

| Cypress Developer Community                 | . 31     |

#### **Pinouts**

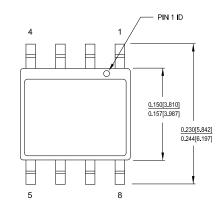

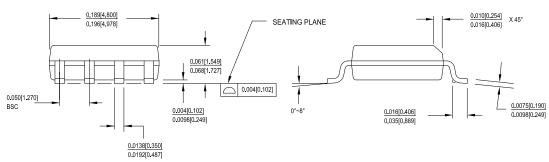

Figure 1. 8-pin SOIC pinout [1, 2, 3]

#### **Pin Definitions**

| Pin Name [1, 2, 3] | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                 | Input        | <b>Chip Select</b> . Activates the device when pulled LOW. Driving this pin high puts the device in low power standby mode.                                                                                                                                                                                                                                                                             |

| SCK                | Input        | <b>Serial Clock</b> . Runs at speeds up to a maximum of f <sub>SCK</sub> . Serial input is latched at the rising edge of this clock. Serial output is driven at the falling edge of the clock.                                                                                                                                                                                                          |

| SI                 | Input        | Serial Input. Pin for input of all SPI instructions and data.                                                                                                                                                                                                                                                                                                                                           |

| SO                 | Output       | Serial Output. Pin for output of data through SPI.                                                                                                                                                                                                                                                                                                                                                      |

| WP                 | Input        | Write Protect. Implements hardware write protection in SPI.                                                                                                                                                                                                                                                                                                                                             |

| HOLD               | Input        | HOLD Pin. Suspends serial operation.                                                                                                                                                                                                                                                                                                                                                                    |

| HSB                | Input/Output | Hardware STORE Busy: Output: Indicates busy status of nvSRAM when LOW. After each Hardware and Software STORE operation HSB is driven HIGH for a short time (t <sub>HHHD</sub> ) with standard output high current and then a weak internal pull-up resistor keeps this pin HIGH (External pull-up resistor connection optional). Input: Hardware STORE implemented by pulling this pin LOW externally. |

| V <sub>CAP</sub>   | Power supply | <b>AutoStore Capacitor</b> . Supplies power to the nvSRAM during power loss to STORE data from the SRAM to nonvolatile elements. If AutoStore is not needed, this pin must be left as No Connect. It must never be connected to ground.                                                                                                                                                                 |

| NC                 | No connect   | No Connect: This pin is not connected to the die.                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub>    | Power supply | Ground                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>CC</sub>    | Power supply | Power supply                                                                                                                                                                                                                                                                                                                                                                                            |

- 1. HSB pin is not available in 8-pin SOIC packages (CY14MX064Q1A/CY14MX064Q2A).

- CY14MX064Q1A part does not have V<sub>CAP</sub> pin and does not support AutoStore.

CY14MX064Q2A part does not have WP pin.

#### **Device Operation**

CY14MX064Q is a 64 Kbit serial (SPI) nvSRAM memory with a nonvolatile element in each memory cell. All the reads and writes to nvSRAM happen to the SRAM, which gives nvSRAM the unique capability to handle infinite writes to the memory. The data in SRAM is secured by a STORE sequence which transfers the data in parallel to the nonvolatile QuantumTrap cells. A small capacitor (V\_{CAP}) is used to AutoStore the SRAM data in nonvolatile cells when power goes down providing power-down data security. The QuantumTrap nonvolatile elements built in the reliable SONOS technology make nvSRAM the ideal choice for secure data storage.

The 64-Kbit memory array is organized as 8 K words  $\times$  8 bits. The memory can be accessed through a standard SPI interface that enables very high clock speeds up to 40 MHz with zero cycle delay read and write cycles. This device supports SPI modes 0 and 3 (CPOL, CPHA = 0, 0 and 1, 1) and operates as SPI slave. The device is enabled using the Chip Select ( $\overline{\text{CS}}$ ) pin and accessed through Serial Input (SI), Serial Output (SO), and Serial Clock (SCK) pins.

This device provides the feature for hardware and software write protection through the WP pin and WRDI instruction respectively along with mechanisms for block write protection (1/4, 1/2, or full array) using BP0 and BP1 pins in the Status Register. Further, the HOLD pin is used to suspend any serial communication without resetting the serial sequence.

CY14MX064Q uses the standard SPI opcodes for memory access. In addition to the general SPI instructions for read and write, it provides four special instructions that allow access to four nvSRAM specific functions: STORE, RECALL, AutoStore Disable (ASDISB), and AutoStore Enable (ASENB).

The major benefit of nvSRAM over serial EEPROMs is that all reads and writes to nvSRAM are performed at the speed of SPI bus with zero cycle delay. Therefore, no wait time is required after any of the memory accesses. The STORE and RECALL operations need finite time to complete and all memory accesses are inhibited during this time. While a STORE or RECALL operation is in progress, the busy status of the device is indicated by the Hardware STORE Busy (HSB) pin and also reflected on the RDY bit of the Status Register.

The device is available in three different pin configurations that enable you to choose a part which fits in best in their application.

The feature summary is given in Table 1.

**Table 1. Feature Summary**

| Feature            | CY14MX064Q1A | CY14MX064Q2A | CY14MX064Q3A |

|--------------------|--------------|--------------|--------------|

| WP                 | Yes          | No           | Yes          |

| $V_{CAP}$          | No           | Yes          | Yes          |

| HSB                | No           | No           | Yes          |

| AutoStore          | No           | Yes          | Yes          |

| Power-Up<br>RECALL | Yes          | Yes          | Yes          |

| Hardware<br>STORE  | No           | No           | Yes          |

| Software<br>STORE  | Yes          | Yes          | Yes          |

#### **SRAM Write**

All writes to nvSRAM are carried out on the SRAM and do not use up any endurance cycles of the nonvolatile memory. This allows you to perform infinite write operations. A write cycle is performed through the WRITE instruction. The WRITE instruction is issued through the SI pin of the nvSRAM and consists of the WRITE opcode, two bytes of address, and one byte of data. Write to nvSRAM is done at SPI bus speed with zero cycle delay.

The device allows burst mode writes to be performed through SPI. This enables write operations on consecutive addresses without issuing a new WRITE instruction. When the last address in memory is reached in burst mode, the address rolls over to 0x0000 and the device continues to write.

The SPI write cycle sequence is defined explicitly in the Memory Access section of SPI Protocol Description.

#### SRAM Read

A read cycle is performed at the SPI bus speed. The data is read out with zero cycle delay after the READ instruction is executed. The READ instruction is issued through the SI pin of the nvSRAM and consists of the READ opcode and two bytes of address. The data is read out on the SO pin.

This device allows burst mode reads to be performed through SPI. This enables reads on consecutive addresses without issuing a new READ instruction. When the last address in memory is reached in burst mode read, the address rolls over to 0x0000 and the device continues to read.

The SPI read cycle sequence is defined explicitly in the Memory Access section of SPI Protocol Description.

#### **STORE Operation**

STORE operation transfers the data from the SRAM to the nonvolatile QuantumTrap cells. The device STOREs data to the nonvolatile cells using one of the three STORE operations: AutoStore, activated on device power-down; Software STORE, activated by a STORE instruction; and Hardware STORE, activated by the HSB. During the STORE cycle, an erase of the previous nonvolatile data is first performed, followed by a program of the nonvolatile elements. After a STORE cycle is initiated, read/write to CY14MX064Q is inhibited until the cycle is completed.

The HSB signal or the RDY bit in the Status Register can be monitored by the system to detect if a STORE or Software RECALL cycle is in progress. The busy status of nvSRAM is indicated by HSB being pulled LOW or RDY bit being set to '1'. To avoid unnecessary nonvolatile STOREs, AutoStore and Hardware STORE operations are ignored unless at least one write operation has taken place since the most recent STORE or RECALL cycle. However, software initiated STORE cycles are performed regardless of whether a write operation has taken place.

#### **AutoStore Operation**

The AutoStore operation is a unique feature of nvSRAM which automatically stores the SRAM data to QuantumTrap cells during power-down. This STORE makes use of an external

capacitor ( $V_{CAP}$ ) and enables the device to safely STORE the data in the nonvolatile memory when power goes down.

During normal operation, the device draws current from  $V_{CC}$  to charge the capacitor connected to the  $V_{CAP}$  pin. When the voltage on the  $V_{CC}$  pin drops below  $V_{SWITCH}$  during power-down, the device inhibits all memory accesses to nvSRAM and automatically performs a conditional STORE operation using the charge from the  $V_{CAP}$  capacitor. The AutoStore operation is not initiated if no write cycle has been performed since last RECALL.

Note If a capacitor is not connected to  $V_{CAP}$  pin, AutoStore must be disabled by issuing the AutoStore Disable instruction (AutoStore Disable (ASDISB) Instruction on page 15). If AutoStore is enabled without a capacitor on the  $V_{CAP}$  pin, the device attempts an AutoStore operation without sufficient charge to complete the STORE. This will corrupt the data stored in nvSRAM, Status Register as well as the serial number and it will unlock the SNL bit. To resume normal functionality, the WRSR instruction must be issued to update the nonvolatile bits BP0, BP1, and WPEN in the Status Register.

Figure 3 shows the proper connection of the storage capacitor ( $V_{CAP}$ ) for AutoStore operation. Refer to DC Electrical Characteristics on page 18 for the size of the  $V_{CAP}$ .

**Note** CY14MX064Q1A does not support AutoStore operation. You must perform Software STORE operation by using the SPI STORE instruction to secure the data.

V<sub>CC</sub>

V<sub>CC</sub>

V<sub>CC</sub>

V<sub>CC</sub>

V<sub>CAP</sub>

V<sub></sub>

Figure 3. AutoStore Mode

#### **Software STORE Operation**

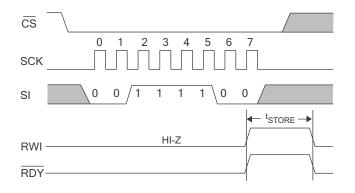

Software STORE enables the user to trigger a STORE operation through a special SPI instruction. STORE operation is initiated by executing STORE instruction irrespective of whether a write has been performed since the last NV operation.

A STORE cycle takes  $t_{STORE}$  time to complete, during which all the memory accesses to  $nv\underline{SRAM}$  are inhibited. The RDY bit of the Status Register or the HSB pin may be polled to find the Ready or Busy status of the nvSRAM. After the  $t_{STORE}$  cycle time is completed, the SRAM is activated again for read and write operations.

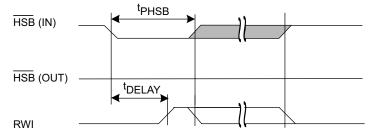

#### Hardware STORE and HSB pin Operation

The  $\overline{\text{HSB}}$  pin in CY14MX064Q3A is used to control and acknowledge STORE operations. If no STORE or RECALL is in progress, this pin can be used to request a Hardware STORE cycle. When the  $\overline{\text{HSB}}$  pin is driven LOW, nvSRAM conditionally initiates a STORE operation after  $t_{DELAY}$  duration. A STORE cycle starts only if a write to the SRAM has been performed since the last STORE or RECALL cycle. Reads and Writes to the memory are inhibited for  $t_{STORE}$  duration or as long as HSB pin is LOW. The HSB pin also acts as an open drain driver (internal 100 k $\Omega$  weak pull-up resistor) that is internally driven LOW to indicate a busy condition when the STORE (initiated by any means) is in progress.

**Note** After each Hardware and Software STORE operation  $\overline{\text{HSB}}$  is driven HIGH for a short time (t<sub>HHHD</sub>) with standard output high current and then remains HIGH by an internal 100 k $\Omega$  pull-up resistor.

**Note** For successful last data byte STORE, a hardware STORE should be initiated at least one clock cycle after the last data bit D0 is received.

Upon completion of the STORE operation, the nvSRAM memory access is inhibited for  $t_{LZHSB}$  time after HSB pin returns HIGH. The HSB pin must be left unconnected if not used.

Note CY14MX064Q1A/CY14MX064Q2A do not have HSB pin. RDY bit of the SPI Status Register may be probed to determine the Ready or Busy status of nvSRAM.

#### **RECALL Operation**

A RECALL operation transfers the data stored in the nonvolatile QuantumTrap elements to the SRAM. A RECALL may be initiated in two ways: Hardware RECALL, initiated on power-up and Software RECALL, initiated by a SPI RECALL instruction.

Internally, RECALL is a two step procedure. First, the SRAM data is cleared. Next, the nonvolatile information is transferred into the SRAM cells. All memory accesses are inhibited while a RECALL cycle is in progress. The RECALL operation does not alter the data in the nonvolatile elements.

### **Hardware RECALL (Power-Up)**

During power-up, when  $V_{CC}$  crosses  $V_{SWITCH}$ , an automatic RECALL sequence is initiated, which transfers the content of nonvolatile memory on to the SRAM. The data would previously have been stored on the nonvolatile memory through a STORE sequence.

A Power-Up RECALL cycle takes  $t_{FA}$  time to complete and the memory access is disabled during this time. HSB pin is used to detect the ready status of the device.

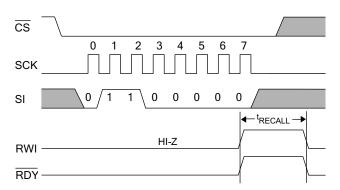

#### **Software RECALL**

Software RECALL allows you to initiate a RECALL operation to restore the content of nonvolatile memory on to the SRAM. A Software RECALL is issued by using the SPI instruction for RECALL.

A Software RECALL takes t<sub>RECALL</sub> time to complete during which all memory accesses to nvSRAM are inhibited. The controller must provide sufficient delay for the RECALL operation to complete before issuing any memory access instructions.

#### **Disabling and Enabling AutoStore**

If the application does not require the AutoStore feature, it can be disabled by using the ASDISB instruction. If this is done, the nvSRAM does not perform a STORE operation at power-down.

AutoStore can be re enabled by using the ASENB instruction. However, these operations are not nonvolatile and if you need this setting to survive the power cycle, a STORE operation must be performed following AutoStore Disable or Enable operation.

Note CY14MX064Q2A/CY14MX064Q3A comes with AutoStore enabled from the factory and CY14MX064Q1A/CY14MX064Q2A/CY14MX064Q3A comes with 0x00 written in all cells from the factory. In CY14MX064Q1A, V<sub>CAP</sub> pin is not present and AutoStore option is not available. The AutoStore Enable and Disable instructions to CY14MX064Q1A are ignored.

**Note** If AutoStore is disabled and  $V_{CAP}$  is not required, then the  $V_{CAP}$  pin must be left open. The  $V_{CAP}$  pin must never be connected to ground. The Power-Up RECALL operation cannot be disabled in any case.

#### Serial Peripheral Interface

#### **SPI Overview**

The SPI is a four-pin interface with Chip Select (CS), Serial Input (SI), Serial Output (SO), and Serial Clock (SCK) pins. CY14MX064Q provides serial access to nvSRAM through SPI interface. The SPI bus on CY14MX064Q can run at speeds up to 40 MHz.

The SPI is a synchronous serial interface which uses clock and data pins for memory access and supports multiple devices on the data bus. A device on SPI bus is activated using the CS pin.

The SPI protocol is controlled by opcodes. These opcodes specify the commands from the bus master to the slave device. After CS is activated the first byte transferred from the bus master is the opcode. Following the opcode, any addresses and data are then transferred. The CS must go inactive after an operation is complete and before a new opcode can be issued. The commonly used terms used in SPI protocol are given below:

#### SPI Master

The SPI master device controls the operations on a SPI bus. A SPI bus may have only one master with one or more slave devices. All the slaves share the same SPI bus lines and the master may select any of the slave devices using the CS pin. All the operations must be initiated by the master activating a slave device by pulling the CS pin of the slave LOW. The master also generates the SCK and all the data transmission on SI and SO lines are synchronized with this clock.

#### SPI Slave

The SPI slave device is activated by the master through the Chip Select line. A slave device gets the SCK as an input from the SPI

master and all the communication is synchronized with this clock. SPI slave never initiates a communication on the SPI bus and acts on the instruction from the master.

CY14MX064Q operates as a SPI slave and may share the SPI bus with other SPI slave devices.

#### Chip Select (CS)

For selecting any <u>slave</u> device, the master needs to pull-down the corresponding <u>CS</u> pin. <u>Any</u> instruction can be issued to a slave device only while the <u>CS</u> pin is LOW. When the device is not selected, data through the <u>SI</u> pin is ignored and the serial output pin (SO) remains in a high impedance state.

**Note** A new instruction must begin with the falling edge of  $\overline{\text{CS}}$ . Therefore, only one opcode can be issued for each active Chip Select cycle.

#### Serial Clock (SCK)

Serial clock is generated by the SPI master <u>and</u> the communication is synchronized with this clock after <u>CS</u> goes I OW.

CY14MX064Q enables SPI modes 0 and 3 for data communication. In both these modes, the inputs are latched by the slave device on the rising edge of SCK and outputs are issued on the falling edge. Therefore, the first rising edge of SCK signifies the arrival of the first bit (MSB) of SPI instruction on the SI pin. Further, all data inputs and outputs are synchronized with SCK.

#### Data Transmission - SI/SO

SPI data bus consists of two lines, SI and SO, for serial data communication. The SI is also referred to as Master Out Slave In (MOSI) and SO is referred to as Master In Slave Out (MISO). The master issues instructions to the slave through the SI pin, while the slave responds through the SO pin. Multiple slave devices may share the SI and SO lines as described earlier.

CY14MX064Q has two separate pins for SI and SO, which can be connected with the master as shown in Figure 4 on page 7.

#### Most Significant Bit (MSB)

The SPI protocol requires that the first bit to be transmitted is the Most Significant Bit (MSB). This is valid for both address and data transmission.

The 64-Kbit serial nvSRAM requires a 2-byte address for any read or write operation. However, since the address is only 13 bits, it implies that the first three bits which are fed in are ignored by the device. Although these three bits are 'don't care', Cypress recommends that these bits are treated as 0s to enable seamless transition to higher memory densities.

#### Serial Opcode

After the slave device is selected with  $\overline{\text{CS}}$  going LOW, the first byte received is treated as the opcode for the intended operation. CY14MX064Q uses the standard opcodes for memory accesses. In addition to the memory accesses, it provides additional opcodes for the nvSRAM specific functions: STORE, RECALL, AutoStore Enable, and AutoStore Disable. Refer to Table 2 on page 9 for details.

#### Invalid Opcode

If an invalid opcode is received, the opcode is ignored and the device ignores <u>any</u> additional serial data on the SI pin till the next falling edge of CS and the SO pin remains tri-stated.

#### Status Register

CY14MX064Q has an 8-bit Status Register. The bits in the Status Register are used to configure the SPI bus. These bits are described in the Table 4 on page 10.

uController

CY14MX064Q

CS HOLD

CS2

HOLD

CS2

HOLD

CS2

HOLD

CS2

HOLD

Figure 4. System Configuration Using SPI nvSRAM

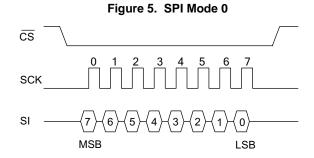

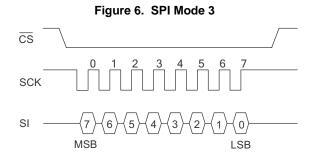

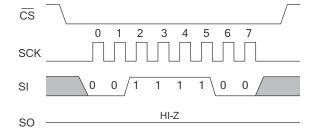

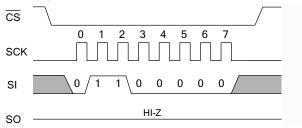

#### **SPI Modes**

CY14MX064Q may be driven by a microcontroller with its SPI peripheral running in either of the following two modes:

- SPI Mode 0 (CPOL=0, CPHA=0)

- SPI Mode 3 (CPOL=1, CPHA=1)

For both these modes, the input data is latched in on the rising edge of SCK starting from the first rising edge after  $\overline{\text{CS}}$  goes active. If the clock starts from a HIGH state (in mode 3), the first rising edge after the clock toggles, is considered. The output data is available on the falling edge of SCK.

The two SPI modes are shown in Figure 5 and Figure 6. The status of clock when the bus master is in standby mode and not transferring data is:

- SCK remains at 0 for Mode 0

- SCK remains at 1 for Mode 3

CPOL and CPHA bits must be set in the SPI controller for either Mode 0 or Mode 3. The device detects the SPI mode from  $\underline{\text{the}}$  status of SCK pin when the device is selected by bringing the CS pin LOW. If SCK pin is LOW when the device is selected, SPI Mode 0 is assumed and if SCK pin is HIGH, it works in SPI Mode 3.

#### **SPI Operating Features**

#### Power-Up

Power-up is defined as the condition when the power supply is turned on and  $\rm V_{CC}$  crosses  $\rm V_{switch}$  voltage.

As described earlier, at power-up nvSRAM performs a Power-Up RECALL operation for  $t_{\rm FA}$  duration during which, all memory accesses are disabled. The HSB pin can be probed to check the Ready/Busy status of nvSRAM after power-up.

The following are the device status after power-up.

- Selected (Active power mode) if CS pin is LOW

- Deselected (Standby power mode) if CS pin is HIGH

- Not in the Hold condition

- Status Register state:

- □ Write Enable (WEN) bit is reset to '0'.

- □ WPEN, BP1, BP0 unchanged from previous STORE operation.

The WPEN, BP1, and BP0 bits of the Status Register are nonvolatile bits and remain unchanged from the previous STORE operation.

#### Power-Down

At power-down (continuous decay of  $V_{CC}$ ), when  $V_{CC}$  drops from the normal operating voltage and below the  $V_{SWITCH}$  threshold voltage, the device stops responding to any instruction sent to it. If a write cycle is in progress and the last data bit D0 has been received when the power goes down, it is allowed  $t_{DELAY}$  time to complete the write. After this, all memory accesses are inhibited and a conditional AutoStore operation is performed (AutoStore is not performed if no writes have happened since the last RECALL cycle). This feature prevents inadvertent writes to nvSRAM from happening during power-down.

However, to completely avoid the possibility of inadvertent writes during power-down, ensure that the device is deselected and is in standby power mode, and the  $\overline{\text{CS}}$  follows the voltage applied on  $V_{\text{CC}}$ .

#### **Active Power and Standby Power Modes**

When CS is LOW, the device is selected and is in the active power mode. The device consumes  $I_{CC}$  current, <u>as</u> specified in DC Electrical Characteristics on page 18. When CS is HIGH, the device is deselected and the device goes into the standby power mode after  $t_{SB}$  time if a STORE or RECALL cycle is not in progress. If a STORE/RECALL cycle is in progress, the device goes into the standby power mode after the STORE or RECALL cycle is completed. In the standby power mode, the current drawn by the device drops to  $I_{SB}$ .

# **SPI Functional Description**

The CY14MX064Q uses an 8-bit instruction register. Instructions and their opcodes are listed in Table 2. All instructions, addresses, and data are transferred with the MSB first and start

with a HIGH to LOW  $\overline{\text{CS}}$  transition. There are, in all, 14 SPI instructions which provide access to most of the functions in nvSRAM. Further, the WP, HOLD and HSB pins provide additional functionality driven through hardware.

Table 2. Instruction Set

| Instruction Category          | Instruction Name | Opcode    | Operation                                 |

|-------------------------------|------------------|-----------|-------------------------------------------|

| Status Register Control Inst  | ructions         | •         |                                           |

| Status Pogistor access        | RDSR             | 0000 0101 | Read Status Register                      |

| Status Register access        | WRSR             | 0000 0001 | Write Status Register                     |

| Write protection and block    | WREN             | 0000 0110 | Set write enable latch                    |

| protection                    | WRDI             | 0000 0100 | Reset write enable latch                  |

| SRAM Read/Write Instructio    | ns               |           |                                           |

| Memory access                 | READ             | 0000 0011 | Read data from memory array               |

| Memory access                 | WRITE            | 0000 0010 | Write data to memory array                |

| Special NV Instructions       |                  |           |                                           |

|                               | STORE            | 0011 1100 | Software STORE                            |

| nvSRAM special functions      | RECALL           | 0110 0000 | Software RECALL                           |

| TIVONAINI SPECIAI TUTICIIOTIS | ASENB            | 0101 1001 | AutoStore Enable                          |

|                               | ASDISB           | 0001 1001 | AutoStore Disable                         |

| Special Instructions          |                  |           |                                           |

| Sleep                         | SLEEP            | 1011 1001 | Sleep mode enable                         |

| Serial number                 | WRSN             | 1100 0010 | Write serial number                       |

| Genai number                  | RDSN             | 1100 0011 | Read serial number                        |

| Device ID read                | RDID             | 1001 1111 | Read manufacturer JEDEC ID and product ID |

| Reserved                      | - Reserved -     | 0001 1110 |                                           |

The SPI instructions are divided based on their functionality in the following types:

- $\ensuremath{\square}$  Status Register control instructions:

- Status Register access: RDSR and WRSR instructions

- Write protection and block protection: WREN and WRDI instructions along with WP pin and WEN, BP0, and BP1 bits

- □ SRAM read/write instructions

- Memory access: READ and WRITE instructions

- □ Special NV instructions

- nvSRAM special instructions: STORE, RECALL, ASENB, and ASDISB

- □ Special instructions

- SLEEP, WRSN, RDSN, RDID

### Status Register

The Status Register bits <u>are listed in Table 3</u>. The Status Register consists of a Ready bit (<u>RDY</u>) and data protection bits BP1, BP0, WEN, and WPEN. The RDY bit can be polled to check the Ready or Busy status while a nvSRAM STORE or Software RECALL cycle is in progress. The Status Register can be modified by WRSR instruction and read by RDSR instruction. However, only the WPEN, BP1, and BP0 bits of the Status Register can be modified by using the WRS<u>R instruction</u>. The WRSR instruction has no effect on WEN and RDY bits. The default value shipped

from the factory for WEN, BP0, BP1, bits 4 -5, SNL and WPEN is '0'.

SNL (bit 6) of the Status Register is used to lock the serial number written using the WRSN instruction. The serial number can be written using the WRSN instruction multiple times while this bit is still '0'. When set to '1', this bit prevents any modification to the serial number. This bit is factory programmed to '0' and can only be written to once. After this bit is set to '1', it can never be cleared to '0'.

**Table 3. Status Register Format**

| Bit 7    | Bit 6   | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1   | Bit 0 |

|----------|---------|-------|-------|---------|---------|---------|-------|

| WPEN (0) | SNL (0) | X (0) | X (0) | BP1 (0) | BP0 (0) | WEN (0) | RDY   |

Table 4. Status Register Bit Definition

| Bit          | Definition               | Description                                                                                                                                                                |

|--------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0 (RDY)  | Ready                    | Read only bit indicates the ready status of device to perform a memory access. This bit is set to '1' by the device while a STORE or Software RECALL cycle is in progress. |

| Bit 1 (WEN)  | Write Enable             | WEN indicates if the device is write enabled. This bit defaults to '0' (disabled) on power-up. WEN = '1'> Write enabled WEN = '0'> Write disabled                          |

| Bit 2 (BP0)  | Block Protect bit '0'    | Used for block protection. For details see Table 5 on page 12.                                                                                                             |

| Bit 3 (BP1)  | Block Protect bit '1'    | Used for block protection. For details see Table 5 on page 12.                                                                                                             |

| Bit 4-5      | Don't care               | These bits are non-writable and always return '0' upon read.                                                                                                               |

| Bit 6 (SNL)  | Serial Number Lock       | Set to '1' for locking serial number                                                                                                                                       |

| Bit 7 (WPEN) | Write Protect Enable bit | Used for enabling the function of Write Protect Pin ( $\overline{\text{WP}}$ ). For details see Table 6 on page 12.                                                        |

#### Read Status Register (RDSR) Instruction

The Read Status Register instruction provides access to the Status Register. This instruction is used to probe the Write Enable status of the device or the Ready status of the device. RDY bit is set by the device to 1 whenever a STORE or Software RECALL cycle is in progress. The block protection and WPEN bits indicate the extent of protection employed.

This instruction is issued after the falling edge of  $\overline{CS}$  using the opcode for RDSR.

#### Write Status Register (WRSR) Instruction

The WRSR instruction enables the user to write to the Status Register. However, this instruction cannot be used to modify bit 0 (RDY), bit 1 (WEN) and bits 4-5. The BP0 and BP1 bits can be used to select one of four levels of block protection. Further, WPEN bit must be set to '1' to enable the use of Write Protect (WP) pin.

WRSR instruction is a write instruction and needs writes to be enabled (WEN bit set to '1') using the WREN instruction before

it is issued. The instruction is issued after the falling edge of  $\overline{\text{CS}}$  using the opcode for WRSR followed by eight bits of data to be stored in the Status Register. WRSR instruction can be used to modify only bits 2, 3, 6 and 7 of the Status Register.

**Note** In CY14MX064Q, the values written to Status Register are saved to nonvolatile memory only after a STORE operation. If AutoStore is disabled (or while using CY14MX064Q1A), any modifications to the Status Register must be secured by performing a Software STORE operation.

**Note** CY14MX064Q2A does not have  $\overline{\text{WP}}$  pin. Any modification to bit 7 of the Status Register has no effect on the functionality of CY14MX064Q2A.

Figure 7. Read Status Register (RDSR) Instruction Timing

Figure 8. Write Status Register (WRSR) Instruction Timing

#### Write Protection and Block Protection

CY14MX064Q provides features for both software and hardware write protection using WRDI instruction and WP. Additionally, this device also provides block protection mechanism through BP0 and BP1 pins of the Status Register.

The write enable and disable status of the device is indicated by WEN bit of the Status Register. The write instructions (WRSR, WRITE and WRSN) and nvSRAM special instruction (STORE, RECALL, ASENB and ASDISB) need the write to be enabled (WEN bit = '1') before they can be issued.

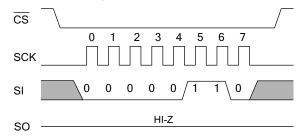

#### Write Enable (WREN) Instruction

On power-up, the device is always in the write disable state. The following WRITE, WRSR, WRSN, or nvSRAM special instruction must therefore be preceded by a Write Enable instruction. If the device is not write enabled (WEN = '0'), it igno<u>res</u> the write instructions and <u>returns</u> to the standby state when  $\overline{CS}$  is brought HIGH. A new  $\overline{CS}$  falling edge is required to re-initiate serial communication. The instruction is issued following the falling edge of  $\overline{CS}$ . When this instruction is used, the WEN bit of Status Register is set to '1'. WEN bit defaults to '0' on power-up.

**Note** After completion of a write instruction (WRSR, WRITE, WRSN) or nvSRAM special instruction (STORE, RECALL, ASENB, and ASDISB) instruction, WEN bit is cleared to '0'. This is done to provide protection from any inadvertent writes. Therefore, WREN instruction needs to be used before a new write instruction is issued.

Figure 9. WREN Instruction

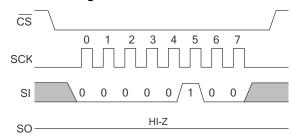

#### Write Disable (WRDI) Instruction

Write Disable instruction disables the write by clearing the WEN bit to '0' in order to protect the device against inadve<u>rte</u>nt writes. This instruction is issued following the falling edge of CS followed by opcode for <u>WRDI</u> instruction. The WEN bit is cleared on the rising edge of CS following a WRDI instruction.

Figure 10. WRDI Instruction

#### **Block Protection**

Block protection is provided using the BP0 and BP1 pins of the Status Register. These bits can be set using WRSR instruction and probed using the RDSR instruction. The nvSRAM is divided into four array segments. One-quarter, one-half, or all of the memory segments can be protected. Any data within the protected segment is read only. Table 5 shows the function of Block Protect bits.

Table 5. Block Write Protect Bits

| Level   | Status Register<br>Bits |     | Array Addresses Protected |  |

|---------|-------------------------|-----|---------------------------|--|

|         | BP1                     | BP0 |                           |  |

| 0       | 0                       | 0   | None                      |  |

| 1 (1/4) | 0                       | 1   | 0x1800-0x1FFF             |  |

| 2 (1/2) | 1                       | 0   | 0x1000-0x1FFF             |  |

| 3 (All) | 1                       | 1   | 0x0000-0x1FFF             |  |

#### **Hardware Write Protection (WP)**

The write <u>protect</u> pin  $(\overline{WP})$  is used to provide hardware write protection. WP pin enables <u>all normal read</u> and write operations when held HIGH. When the  $\overline{WP}$  pin is brought LOW and WPEN bit is '1', all write operations to the Status Register are inhibited. The hardware write protection function is blocked when the WPEN bit is '0'. This allows you to install the device in a system with the  $\overline{WP}$  pin tied to ground, and still write to the Status Register.

WP pin can be used along with WPEN and Block Protect bits (BP1 and BP0) of the Status Register to inhibit writes to memory. When WP pin is LOW and WPEN is set to '1', any modifications to the Status Register are disabled. Therefore, the memory is protected by setting the BP0 and BP1 bits and the WP pin inhibits any modification of the Status Register bits, providing hardware write protection.

**Note** WP going LOW when  $\overline{CS}$  is still LOW has no effect on any of the ongoing write operations to the Status Register.

**Note** CY14MX064Q2A does not have  $\overline{WP}$  pin and therefore does not provide hardware write protection.

Table 6 summarizes all the protection features of this device.

**Table 6. Write Protection Operation**

| WPEN | WP   | WEN | Protected Blocks | Unprotected Blocks | Status<br>Register |

|------|------|-----|------------------|--------------------|--------------------|

| Х    | Χ    | 0   | Protected        | Protected          | Protected          |

| 0    | Χ    | 1   | Protected        | Writable           | Writable           |

| 1    | LOW  | 1   | Protected        | Writable           | Protected          |

| 1    | HIGH | 1   | Protected        | Writable           | Writable           |

#### **Memory Access**

All memory accesses are done using the READ and WRITE instructions. These instructions cannot be used while a STORE or RECALL cycle is in progress. A STORE cycle in progress is indicated by the RDY bit of the Status Register and the HSB pin.

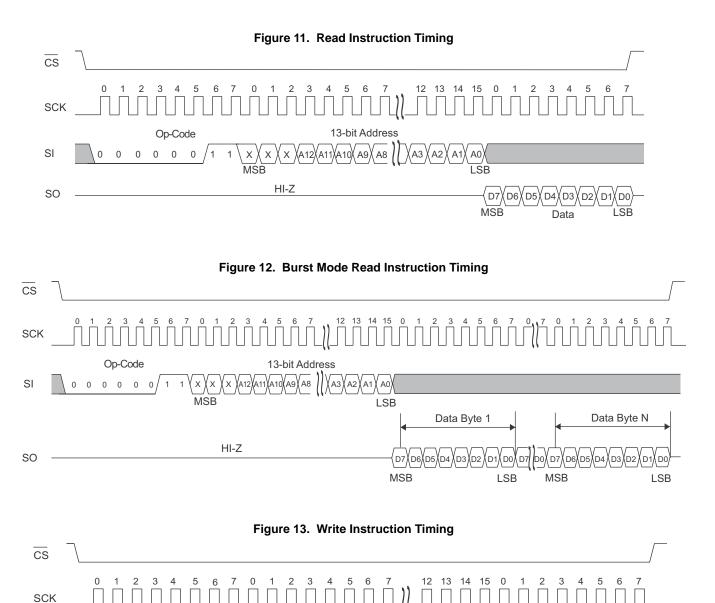

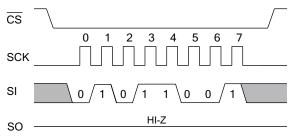

#### Read Sequence (READ) Instruction

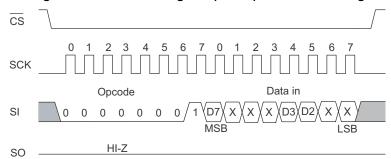

The read operations on this device are performed by giving the instruction on the SI pin and reading the output on SO pin. The following <u>sequence</u> needs to be followed for a read operation: After the CS line is pulled LOW to select a device, the read opcode is transmitted through the SI line followed by two bytes of address (A12–A0). The most significant address bits (A15–A13) are don't cares. After the last address bit is transmitted on the SI pin, the data (D7–D0) at the specific address is shifted out on the SO line on the falling edge of SCK starting with D7. Any other data on SI line after the last address bit is ignored.

CY14MX064Q allows reads to be performed in bursts through SPI which can be used to read consecutive addresses without issuing a new READ instruction. If only one byte is to be read, the CS line must be driven HIGH after one byte of data comes out. However, the read sequence may be continued by holding the CS line LOW and the address is automatically incremented and data continues to shift out on SO pin. When the last data memory address (0x1FFF) is reached, the address rolls over to 0x0000 and the device continues to read.

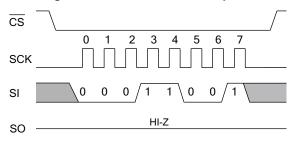

#### Write Sequence (WRITE) Instruction

The write operations on this device are performed through the SI pin. To perform a write operation, if the device is write disabled, then the device must first be write enabled through the WREN instruction. When the writes are enabled (WEN = '1'), WRITE instruction is issued after the falling edge of CS. A WRITE instruction constitutes transmitting the WRITE opcode on SI line followed by two bytes of address (A12–A0) and the data (D7–D0) which is to be written. The most significant address bits (A15–A13) are don't cares.

CY14MX064Q enables writes to be performed in bursts through SPI which can be used to write consecutive addresses without issuing a new WRITE instruction. If only one byte is to be written, the CS line must be driven HIGH after the D0 (LSB of data) is transmitted. However, if more bytes are to be written, CS line must be held LOW and address is incremented automatically. The following bytes on the SI line are treated as data bytes and written in the successive addresses. When the last data memory address (0x1FFF) is reached, the address rolls over to 0x0000 and the device continues to write. The WEN bit is reset to '0' on completion of a WRITE sequence.

**Note** When a burst write reaches a protected block address, it continues the address increment into the protected space but does not write any data to the protected memory. If the address roll over takes the burst write to unprotected space, it resumes writes. The same operation is true if a burst write is initiated within a write protected block.

13-bit Address  $\sqrt{10}\sqrt{9}\sqrt{8}$

HI-Z

0 XD7XI

SI

SO

Op-Code

0

LSB

Figure 14. Burst Mode Write Instruction Timing

#### **nvSRAM Special Instructions**

CY14MX064Q provides four special instructions which enables access to the nvSRAM specific functions: STORE, RECALL, ASDISB, and ASENB, Table 7 lists these instructions.

Table 7. nvSRAM Special Instructions

| Function Name | Opcode    | Operation         |  |

|---------------|-----------|-------------------|--|

| STORE         | 0011 1100 | Software STORE    |  |

| RECALL        | 0110 0000 | Software RECALL   |  |

| ASENB         | 0101 1001 | AutoStore Enable  |  |

| ASDISB        | 0001 1001 | AutoStore Disable |  |

#### Software STORE (STORE) Instruction

When a STORE instruction is executed, nvSRAM performs a Software STORE operation. The STORE operation is performed irrespective of whether a write has taken place since the last STORE or RECALL operation.

To issue this instruction, the device must be write enabled (WEN bit = '1'). The instruction is performed by transmitting the STORE opcode on the SI pin following the falling edge of  $\overline{CS}$ . The WEN bit is cleared on the positive edge of  $\overline{CS}$  following the STORE instruction.

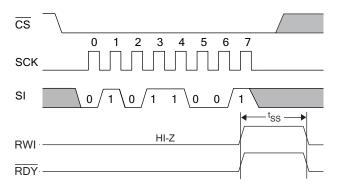

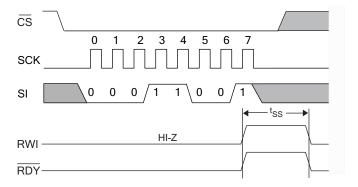

Figure 15. Software STORE Operation

#### Software RECALL (RECALL) Instruction

When a RECALL instruction is executed, nvSRAM performs a Software RECALL operation. To issue this instruction, the device must be write enabled (WEN = '1').

The instruction is performed by transmitting  $\underline{\text{the}}$  RECALL opcode on the SI pin following the falling edge of  $\overline{\text{CS}}$ . The WEN bit is

cleared on the positive edge of  $\overline{\text{CS}}$  following the RECALL instruction.

Figure 16. Software RECALL Operation

#### AutoStore Enable (ASENB) Instruction

The AutoStore Enable instruction enables the AutoStore on CY14MX064Q2A/CY14MX064Q3A. This setting is not nonvolatile and needs to be followed by a STORE sequence to survive the power cycle.

To issue this instruction, the device must be write enabled (WEN = '1'). The instruction is performed by transmitting the ASENB opcode on the SI pin following the falling edge of CS. The WEN bit is cleared on the positive edge of CS following the ASENB instruction.

**Note** If ASDISB and ASENB instructions are executed in CY14MX064Q2A/CY14MX064Q3A, the device is busy for the duration of software sequence processing time ( $t_{SS}$ ). However, ASDISB and ASENB instructions have no effect on CY14MX064Q1A as AutoStore is internally disabled.

Figure 17. AutoStore Enable Operation

#### AutoStore Disable (ASDISB) Instruction

AutoStore is enabled by default in CY14MX064Q2A/CY14MX064Q3A. The ASDISB instruction disables the AutoStore. This setting is not nonvolatile and needs to be followed by a STORE sequence to survive the power cycle.

To issue this instruction, the device must be write enabled (WEN = '1'). The instruction is performed by transmitting the ASDISB opcode on the SI pin following the falling edge of CS. The WEN bit is cleared on the positive edge of CS following the ASDISB instruction.

Figure 18. AutoStore Disable Operation

#### **Special Instructions**

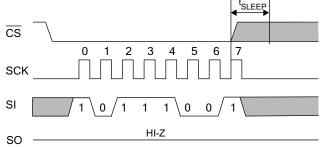

#### **SLEEP Instruction**

SLEEP instruction puts the nvSRAM in sleep mode. When the SLEEP instruction is issued, the nvSRAM takes  $t_{SS}$  time to process the SLEEP request. Once the SLEEP command is successfully registered and processed, the nvSRAM toggles HSB LOW, performs a STORE operation to secure the data to nonvolatile memory and then enters into SLEEP mode. The device starts consuming  $I_{ZZ}$  current after  $t_{SLEEP}$  time from the instance when SLEEP instruction is registered. The device is not accessible for normal operations after SLEEP instruction is issued. Once in sleep mode, the SCK and SI pins are ignored and SO will be Hi-Z but device continues to monitor the CS pin.

To wake the nvSRAM from the sleep mode, the device must be selected by toggling the CS pin from HIGH to LOW. The device wakes up and is accessible for normal operations after t<sub>WAKE</sub> duration after a falling edge of CS pin is detected.

**Note** Whenever nvSRAM enters into sleep mode, it initiates nonvolatile STORE cycle which results in an endurance cycle per sleep command execution. A STORE cycle starts only if a write

to the SRAM has been performed since the last STORE or RECALL cycle.

Figure 19. Sleep Mode Entry

#### **Serial Number**

The serial number is an 8 byte programmable memory space provided to you uniquely identify this device. It typically consists of a two byte Customer ID, followed by five bytes of unique serial number and one byte of CRC check. However, nvSRAM does not calculate the CRC and it is up to the system designer to utilize the eight byte memory space in whatever manner desired. The default value for eight byte locations are set to '0x00'.

#### **WRSN (Serial Number Write) Instruction**

The serial number can be written using the WRSN instruction. To write serial number the write must be enabled using the WREN instruction. The WRSN instruction can be used in burst mode to write all the 8 bytes of serial number.

The serial number is locked using the SNL bit of the Status Register. Once this bit is set to '1', no modification to the serial number is possible. After the SNL bit is set to '1', using the WRSN instruction has no effect on the serial number.

A STORE operation (AutoStore or Software STORE) is required to store the serial number in nonvolatile memory. If AutoStore is disabled, you must perform a Software STORE operation to secure and lock the serial Number. If SNL bit is set to '1' and is not stored (AutoStore disabled), the SNL bit and serial number defaults to '0' at the next power cycle. If SNL bit is set to '1' and is stored, the SNL bit can never be cleared to '0'. This instruction requires the WEN bit to be set before it can be executed. The WEN bit is reset to '0' after completion of this instruction.

Figure 20. WRSN Instruction

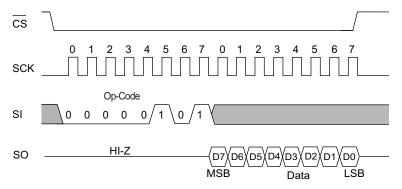

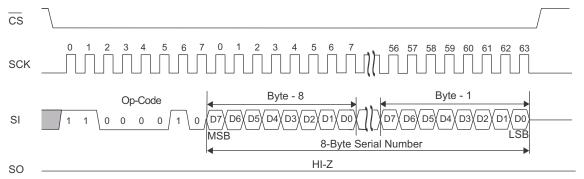

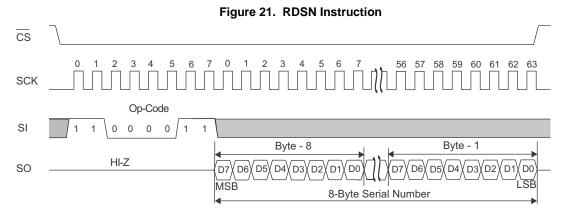

#### **RDSN (Serial Number Read) Instruction**

The serial number is read using RDSN instruction. A serial number read may be performed in burst mode to read all the eight bytes at once. After the last byte of serial number is read,

the device does not loop back. RDSN instruction can be issued by shifting the <u>op-code</u> for RDSN in through the SI pin of nvSRAM after CS goes LOW. This is followed by nvSRAM shifting out the eight bytes of serial number through the SO pin.

#### **Device ID**

Device ID is 4-byte read only code identifying a type of product uniquely. This includes the product family code, configuration and density of the product.

Table 8. Device ID

|              |                        | Device ID Description |                   |                 |                 |  |

|--------------|------------------------|-----------------------|-------------------|-----------------|-----------------|--|

| Device       | Device ID<br>(4 bytes) | 31–21<br>(11 bits)    | 20–7<br>(14 bits) | 6–3<br>(4 bits) | 2–0<br>(3 bits) |  |

|              |                        | Manufacture ID        | Product ID        | Density ID      | Die Rev         |  |

| CY14MB064Q1A | 0x06810888             | 00000110100           | 00001000010001    | 0001            | 000             |  |

| CY14MB064Q2A | 0x06818808             | 00000110100           | 00001100010000    | 0001            | 000             |  |

| CY14MB064Q3A | 0x06818888             | 00000110100           | 00001100010001    | 0001            | 000             |  |

| CY14ME064Q1A | 0x06811088             | 00000110100           | 00001000100001    | 0001            | 000             |  |

| CY14ME064Q2A | 0x06819008             | 00000110100           | 00001100100000    | 0001            | 000             |  |

| CY14ME064Q3A | 0x06819088             | 00000110100           | 00001100100001    | 0001            | 000             |  |

The device ID is divided into four parts as shown in Table 8:

1. Manufacturer ID (11 bits)

This is the JEDEC assigned manufacturer ID for Cypress. JEDEC assigns the manufacturer ID in different banks. The first three bits of the manufacturer ID represent the bank in which ID is assigned. The next eight bits represent the manufacturer ID.

Cypress's manufacturer ID is 0x34 in bank 0. Therefore the manufacturer ID for all Cypress nvSRAM products is:

Cypress ID - 000\_0011\_0100

2. Product ID (14 bits)

The product ID is defined as shown in the Table 8

3. Density ID (4 bits)

The 4 bit density ID is used as shown in Table 8 for indicating the 64 Kb density of the product.

4. Die Rev (3 bits)

This is used to represent any major change in the design of the product. The initial setting of this is always 0x0.

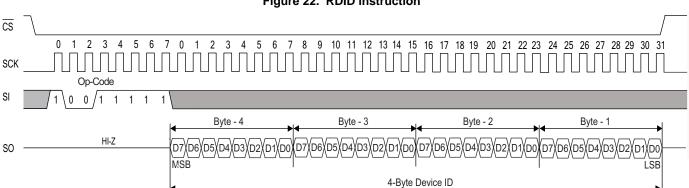

#### **RDID (Device ID Read) Instruction**

This instruction is used to read the JEDEC assigned manufacturer ID and product ID of the device. This instruction can be used to identify a device on the bus. RDID instruction can be issued by shifting the op-code for RDID in through the SI pin of nvSRAM after CS goes LOW. This is followed by nvSRAM shifting out the four bytes of device ID through the SO pin.

Figure 22. RDID instruction

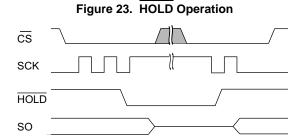

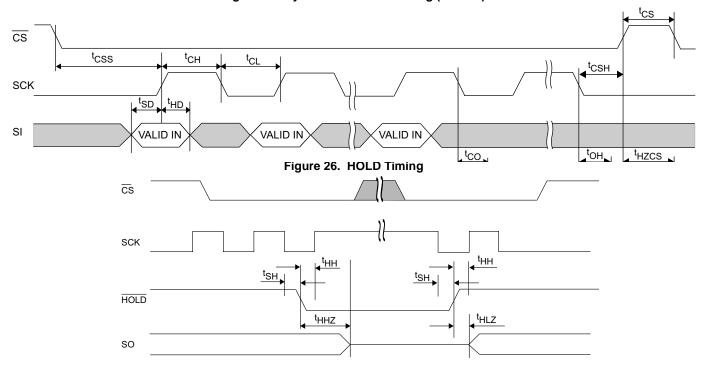

# **HOLD** Pin Operation

The HOLD pin is used to pause the serial communication. When the device is selected and a serial sequence is underway, HOLD is used to pause the serial communication with the master device without resetting the ongoing serial sequence. To pause, the HOLD pin must be brought LOW when the SCK pin is LOW. To resume serial communication, the HOLD pin must be brought HIGH when the SCK pin is LOW (SCK may toggle during HOLD). While the device serial communication is paused, inputs to the SI pin are ignored and the SO pin is in the high impedance state.

This pin can be used by the master with the  $\overline{CS}$  pin to pause the serial communication by bringing the pin HOLD LOW and deselecting an SPI slave to establish communication with another slave device, without the serial communication being reset. The communication may be resumed at a later point by selecting the device and setting the HOLD pin HIGH.

### **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. These user guidelines are not tested. Storage temperature ......-65 °C to +150 °C Maximum accumulated storage time At 150 °C ambient temperature ...... 1000 h At 85 °C ambient temperature ...... 20 Years Maximum junction temperature ...... 150 °C Supply voltage on V<sub>CC</sub> relative to V<sub>SS</sub> CY14MB064Q: .....-0.5 V to +4.1 V CY14ME064Q: .....-0.5 V to +7.0 V DC voltage applied to outputs in High Z state ......-0.5 V to V<sub>CC</sub> + 0.5 V Input voltage ......–0.5 V to  $V_{CC}$  + 0.5 V

## **Operating Range**

| Device     | Range      | Ambient<br>Temperature | V <sub>CC</sub> |

|------------|------------|------------------------|-----------------|

| CY14MB064Q | Industrial | -40 °C to +85 °C       | 2.7 V to 3.6 V  |

| CY14ME064Q |            |                        | 4.5 V to 5.5 V  |

#### **DC Electrical Characteristics**

Over the Operating Range

| Parameter                     | Description                             | Test Con                                                                                         | ditions                   | Min                   | Typ <sup>[4]</sup> | Max            | Unit |

|-------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|-----------------------|--------------------|----------------|------|

| V <sub>CC</sub>               | Power supply                            |                                                                                                  | CY14MB064Q                | 2.7                   | 3.0                | 3.6            | V    |

|                               |                                         |                                                                                                  | CY14ME064Q                | 4.5                   | 5.0                | 5.5            | V    |

| I <sub>CC1</sub>              | Average V <sub>CC</sub> current         | $f_{SCK} = 40 \text{ MHz};$                                                                      | CY14MB064Q                | _                     | _                  | 3              | mA   |

|                               |                                         | Values obtained                                                                                  | CY14ME064Q                | _                     | _                  | 4              | mA   |

|                               |                                         | without output loads (I <sub>OUT</sub> = 0 mA)                                                   |                           |                       |                    |                |      |

| laas                          | Average V <sub>CC</sub> current during  | All inputs don't care                                                                            |                           | _                     | _                  | 3              | mA   |

| I <sub>CC2</sub>              | STORE                                   | Average current for                                                                              | r duration tetore         |                       |                    |                | ША   |

| I <sub>CC3</sub>              | Average V <sub>CC</sub> current,        | All inputs cycling at                                                                            |                           | _                     | _                  | 1              | mA   |

| 003                           | $f_{SCK} = 1 \text{ MHz},$              | Values obtained wi                                                                               | thout output              |                       |                    |                |      |

|                               | $V_{CC} = V_{CC(Typ)}$ , 25 °C          | loads (I <sub>OUT</sub> = 0 mA                                                                   | •                         |                       |                    |                |      |

| I <sub>CC4</sub>              | Average V <sub>CAP</sub> current during | All inputs don't care                                                                            |                           | _                     | _                  | 3              | mA   |

|                               | AutoStore cycle                         | current for duration                                                                             |                           |                       |                    | 450            |      |

| I <sub>SB</sub>               | V <sub>CC</sub> standby current         | $CS \ge (V_{CC} - 0.2 \text{ V})$<br>$V_{IN} \le 0.2 \text{ V or } \ge (V_{CC} - 0.2 \text{ V})$ | ).                        | _                     | _                  | 150            | μΑ   |

|                               |                                         | Standby current lev                                                                              | cc – u.z v).<br>/el after |                       |                    |                |      |

|                               |                                         | nonvolatile cycle is                                                                             |                           |                       |                    |                |      |

|                               |                                         | Inputs are static. f <sub>S</sub>                                                                |                           |                       |                    |                |      |

| I <sub>ZZ</sub>               | Sleep mode current                      | t <sub>SLEEP</sub> time after SI                                                                 |                           | _                     | _                  | 8              | μΑ   |

|                               |                                         | is registered. All inp                                                                           |                           |                       |                    |                |      |

| 1 [5]                         | Input lookage current (aveent           | and configured at C                                                                              | JiviOS logic level.       | -1                    |                    | . 1            |      |

| I <sub>IX<sup>[5]</sup></sub> | Input leakage current (except HSB)      |                                                                                                  |                           | -1                    | _                  | +1             | μА   |

|                               | Input leakage current (for HSB)         |                                                                                                  |                           | -100                  | -                  | +1             | μΑ   |

| I <sub>OZ</sub>               | Off-state output leakage current        |                                                                                                  |                           | -1                    | _                  | +1             | μΑ   |

| V <sub>IH</sub>               | Input HIGH voltage                      |                                                                                                  |                           | 2.0                   | _                  | $V_{CC} + 0.5$ | V    |

| $V_{IL}$                      | Input LOW voltage                       |                                                                                                  |                           | $V_{ss} - 0.5$        | _                  | 0.8            | V    |

| V <sub>OH</sub>               | Output HIGH Voltage                     | $I_{OUT} = -2 \text{ mA}$                                                                        | CY14MB064Q                | 2.4                   | ı                  | _              | V    |

|                               |                                         |                                                                                                  | CY14ME064Q                | V <sub>CC</sub> – 0.4 | -                  | _              |      |

| $V_{OL}$                      | Output LOW voltage                      | $I_{OUT} = 4 \text{ mA}$                                                                         |                           | _                     | _                  | 0.4            | V    |

Typi<u>cal values</u> are at 25 °C, V<sub>CC</sub> = V<sub>CC(Typ)</sub>. Not 100% tested.

The HSB pin has I<sub>OUT</sub> = -2 μA for V<sub>OH</sub> of 2.4 V when both active high and LOW drivers are disabled. When they are enabled standard V<sub>OH</sub> and V<sub>OL</sub> are valid. This parameter is characterized but not tested.

### **DC Electrical Characteristics** (continued)

Over the Operating Range

| Parameter                       | Description                                | Test Cond                      | ditions             | Min | Typ <sup>[4]</sup> | Max             | Unit |

|---------------------------------|--------------------------------------------|--------------------------------|---------------------|-----|--------------------|-----------------|------|

| V <sub>CAP</sub> <sup>[6]</sup> | Storage capacitor                          | Between V <sub>CAP</sub> pin a | and V <sub>SS</sub> | 42  | 47                 | 180             | μF   |

| V <sub>VCAP</sub> [7, 8]        | Maximum voltage driven on V <sub>CAP</sub> | V <sub>CC</sub> = Max          | CY14MB064Q          | _   | _                  | V <sub>CC</sub> | V    |

|                                 | pin by the device                          |                                | CY14ME064Q          | _   | _                  | $V_{CC} - 0.5$  |      |

#### **Data Retention and Endurance**

Over the Operating Range

| Parameter         | Description                  | Min   | Unit  |

|-------------------|------------------------------|-------|-------|

| DATA <sub>R</sub> | Data retention               | 20    | Years |

| NV <sub>C</sub>   | Nonvolatile STORE operations | 1,000 | K     |

# Capacitance

| Parameter [8]    | Description            | Test Conditions                                | Max | Unit |

|------------------|------------------------|------------------------------------------------|-----|------|

| C <sub>IN</sub>  | Input capacitance      | $T_A = 25 ^{\circ}\text{C}, f = 1 \text{MHz},$ | 7   | pF   |

| C <sub>OUT</sub> | Output pin capacitance | $V_{CC} = V_{CC(Typ)}$                         | 7   | pF   |

#### **Thermal Resistance**

| Parameter [8]     | Description                           | Test Conditions                                                           | 8-pin SOIC | 16-pin SOIC | Unit |

|-------------------|---------------------------------------|---------------------------------------------------------------------------|------------|-------------|------|

| $\Theta_{JA}$     |                                       | Test conditions follow standard test methods and procedures for measuring |            | 56.68       | °C/W |

| $\Theta_{\sf JC}$ | Thermal resistance (junction to case) | thermal impedance, per EIA / JESD51.                                      | 37.86      | 32.11       | °C/W |

#### Notes

<sup>6.</sup> Min V<sub>CAP</sub> value guarantees that there is a sufficient charge available to complete a successful AutoStore operation. Max V<sub>CAP</sub> value guarantees that the capacitor on V<sub>CAP</sub> is charged to a minimum voltage during a Power-Up RECALL cycle so that an immediate power-down cycle can complete a successful AutoStore. Therefore it is always recommended to use a capacitor within the specified min and max limits. Refer application note AN43593 for more details on V<sub>CAP</sub> options.

Maximum voltage on V<sub>CAP</sub> pin (V<sub>VCAP</sub>) is provided for guidance when choosing the V<sub>CAP</sub> capacitor. The voltage rating of the V<sub>CAP</sub> capacitor across the operating temperature range should be higher than the V<sub>VCAP</sub> voltage.

These parameters are guaranteed by design and are not tested.

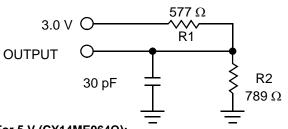

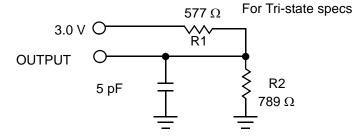

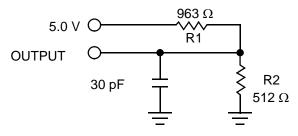

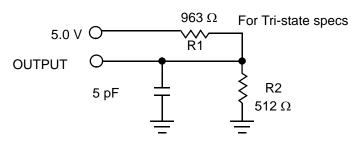

### **AC Test Loads and Waveforms**

#### For 3 V (CY14MB064Q):

Figure 24. AC Test Loads and Waveforms

For 5 V (CY14ME064Q):

### **AC Test Conditions**

| Input pulse levels                       | . 0 V to 3 V |

|------------------------------------------|--------------|

| Input rise and fall times (10% to 90%)   | < 3 ns       |

| Input and output timing reference levels | 1.5 V        |

# **AC Switching Characteristics**

Over the Operating Range

| Param                             | eters <sup>[9]</sup> |                        | 40 [ | ИНz |      |

|-----------------------------------|----------------------|------------------------|------|-----|------|

| Cypress<br>Parameter              | Alt.<br>Parameter    | Description            | Min  | Max | Unit |

| f <sub>SCK</sub>                  | f <sub>SCK</sub>     | Clock frequency, SCK   | -    | 40  | MHz  |

| t <sub>CL</sub> <sup>[10]</sup>   | t <sub>WL</sub>      | Clock pulse width LOW  | 11   | _   | ns   |

| t <sub>CH</sub> <sup>[10]</sup>   | t <sub>WH</sub>      | Clock pulse width HIGH | 11   | _   | ns   |

| t <sub>CS</sub>                   | t <sub>CE</sub>      | CS HIGH time           | 20   | _   | ns   |

| t <sub>CSS</sub>                  | t <sub>CES</sub>     | CS setup time          | 10   | _   | ns   |

| t <sub>CSH</sub>                  | t <sub>CEH</sub>     | CS hold time           | 10   | _   | ns   |

| t <sub>SD</sub>                   | t <sub>SU</sub>      | Data in setup time     | 5    | _   | ns   |

| t <sub>HD</sub>                   | t <sub>H</sub>       | Data in hold time      | 5    | _   | ns   |

| t <sub>HH</sub>                   | t <sub>HD</sub>      | HOLD hold time         | 5    | _   | ns   |

| t <sub>SH</sub>                   | t <sub>CD</sub>      | HOLD setup time        | 5    | _   | ns   |

| t <sub>CO</sub>                   | t <sub>V</sub>       | Output Valid           | _    | 9   | ns   |

| t <sub>HHZ</sub> <sup>[10]</sup>  | t <sub>HZ</sub>      | HOLD to output HIGH Z  | _    | 15  | ns   |

| t <sub>HLZ</sub> [10]             | $t_{LZ}$             | HOLD to output LOW Z   | -    | 15  | ns   |

| t <sub>OH</sub>                   | t <sub>HO</sub>      | Output hold time       | 0    | _   | ns   |

| t <sub>HZCS</sub> <sup>[10]</sup> | t <sub>DIS</sub>     | Output disable time    | -    | 20  | ns   |

<sup>Notes

9. Test conditions assume signal transition time of 3 ns or less, timing reference levels of V<sub>CC</sub>/2, input pulse levels of 0 to V<sub>CC</sub> (typ), and output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and load capacitance shown in Figure 24.

10. These parameters are guaranteed by design and are not tested.</sup>

# **Switching Waveforms**

Figure 25. Synchronous Data Timing (Mode 0)

# **AutoStore or Power-Up RECALL**

Over the Operating Range

| Parameter                            | Description                                              |            | CY14MX064Q |      | Unit |

|--------------------------------------|----------------------------------------------------------|------------|------------|------|------|

| Parameter                            | Description                                              |            | Min        | Unit |      |

| t <sub>FA</sub> <sup>[11]</sup>      | Power-Up RECALL duration                                 |            | _          | 20   | ms   |

| t <sub>STORE</sub> [12]              | STORE cycle duration                                     |            | _          | 8    | ms   |

| t <sub>DELAY</sub> [13]              | Time allowed to complete SRAM write cycle                |            | _          | 25   | ns   |

| V <sub>SWITCH</sub>                  | Low voltage trigger level                                | CY14MB064Q | _          | 2.65 | V    |

|                                      |                                                          | CY14ME064Q | _          | 4.40 | V    |