# JZ8FC003 Series MCU

# **User Guide**

Built-in 16 Bit PWM / 12 Bit ADC / 1T 8051 18K Flash MCU

# **Table of Contents**

| 1 Introduction                                                                       | 6  |

|--------------------------------------------------------------------------------------|----|

| 2 Basic Features                                                                     | 6  |

| 3 Chip Model and Function Description                                                | 9  |

| 4 Block Diagram                                                                      | 10 |

| 5 Pin Package and Description                                                        | 11 |

| 5.1 Package Definition                                                               | 11 |

| 5.2 Pin Description                                                                  | 13 |

| 6 Central Processing Unit (CPU)                                                      | 16 |

| 6.1 CPU Introduction                                                                 | 16 |

| 6.2 Register Description                                                             | 16 |

| 7 Memory Architecture                                                                | 20 |

| 7.1 Random Access Memory (RAM)                                                       | 20 |

| 7.2 Special Function Register (SFR)                                                  | 20 |

| 7.3 Flash                                                                            | 22 |

| 7.3.1 Function Introduction                                                          | 22 |

| 7.3.2 Flash Architecture                                                             | 23 |

| 7.3.3 Flash Register Description                                                     | 23 |

| 7.3.4 Flash Control Example                                                          | 26 |

| 7.4 External RAM Mapped to Program Area                                              | 28 |

| 8 Interruption System                                                                | 29 |

| 8.1 Function Introduction                                                            | 29 |

| 8.2 Interrupt logic                                                                  | 29 |

| 8.3 Interrupt vector table                                                           | 30 |

| 8.4 Interrupt Control Register                                                       | 31 |

| 8.5 External Interrupt                                                               | 34 |

| 8.5.1 External Interrupt Introduction                                                | 34 |

| 8.5.2 External Interrupt Register                                                    | 35 |

| 8.5.3 External Interrupt Control Routines                                            | 38 |

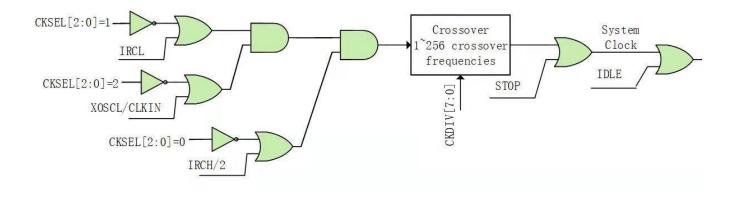

| 9 Clock System                                                                       | 40 |

| 9.1 Clock System Introduction                                                        |    |

| 9.1.1 Clock Specific Name Definition                                                 | 40 |

| 9.1.2 32 MHz Internal RC Oscillator(IRCH)                                            | 41 |

| 9.1.3 131 kHz Internal RC Oscillator (IRCL)                                          | 41 |

| 9.1.4 External high-speed crystal resonator (XOSCH) and external clock input (CLKIN) | 41 |

| 9.2 Clock Control Register Description                                               | 42 |

| 9.3 System Clock                                                                     |    |

| 9.3.1 System clock Architecture                                                      |    |

| 9.3.2 System Clock Control Register Description                                      | 45 |

| 9.3.3 System Clock Control Method and Example                                        | 46 |

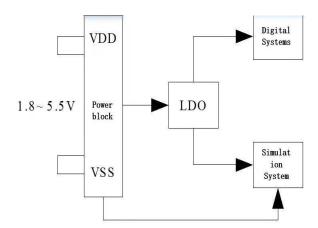

| 10 Power supply and reset system                                                     | 48 |

| 10.1 Power Supply                                                                    |    |

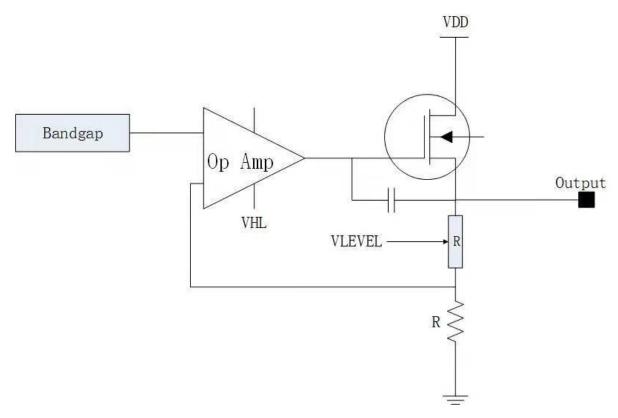

| 10.1.1 LDO Function Introduction                                                     |    |

| 10.1.2 LDO Control Register                                                          | 49 |

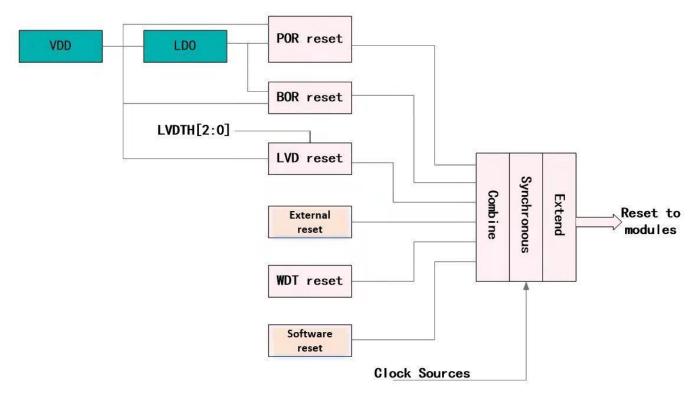

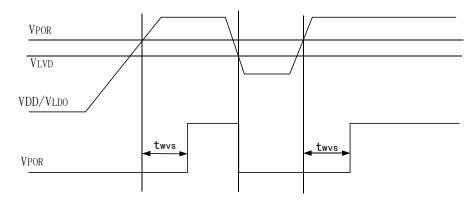

| 10.2 Reset System                                                                    | 52 |

| 11 Power Consumption Management                               | 54  |

|---------------------------------------------------------------|-----|

| 11.1 IDLE mode                                                | 54  |

| 11.2 STOP mode                                                | 54  |

| 11.3 Low Speed Mode                                           | 55  |

| 11.4 Low Power Related Register Description                   | 55  |

| 11.5 Low power Consumption Control Example                    | 57  |

| 12 General Timer (Timer0,Timer1,Timer2)                       | 60  |

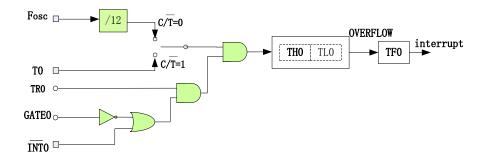

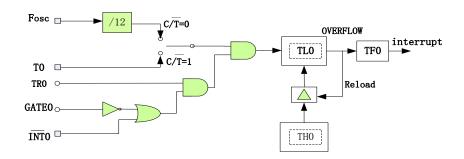

| 12.1 Timer0                                                   | 60  |

| 12.1.1 Timer0 Introduction                                    |     |

| 12.1.2 Timer0 Register Descriptions                           | 61  |

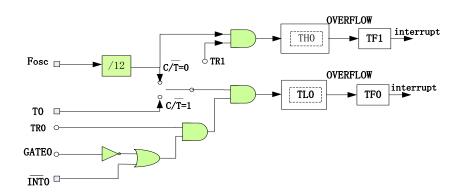

| 12.2 Timer1                                                   |     |

| 12.2.1 Timer1 Introduction                                    |     |

| 12.2.2 Timer1 Register Description                            | 65  |

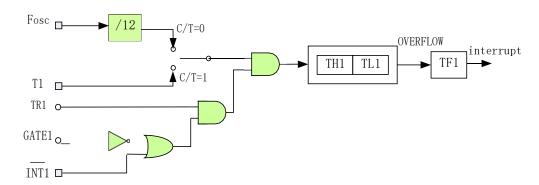

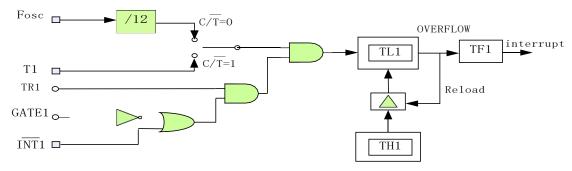

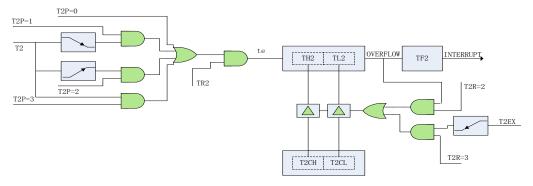

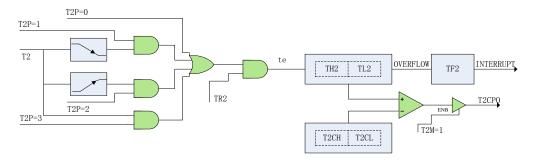

| 12.3 Timer2                                                   | 66  |

| 12.3.1 Timer2 Introduction                                    |     |

| 12.3.2 Timer2 Register Description                            | 67  |

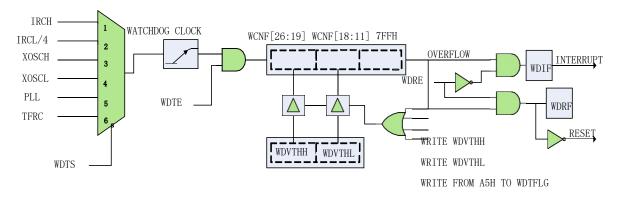

| 13 Watchdog Timer(WDT)                                        | 73  |

| 13.1 Watchdog Timer (WDT) Function Introduction               | 73  |

| 13.2 Watchdog Timer (WDT) Register Description                |     |

| 13.3 Watchdog Timer Control Example                           | 75  |

| 14 TMC Timer                                                  | 77  |

| 14.1 TMC Function Introduction                                | 77  |

| 14.2 TMC Register Description                                 | 77  |

| 14.3 TMC Control Routines                                     | 78  |

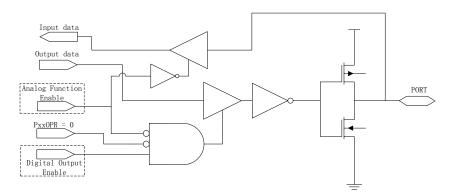

| 15 General Purpose Input/Output(GPIO) and Alternate Functions | 79  |

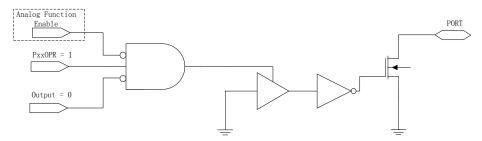

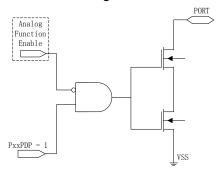

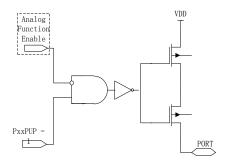

| 15.1 Function Introduction                                    | 79  |

| 15.2 Pin Register Description                                 | 81  |

| 15.3 Pin control Example                                      |     |

| 16 Universal Asynchronous Receiver/Transmitter (UART1/UART2)  | 90  |

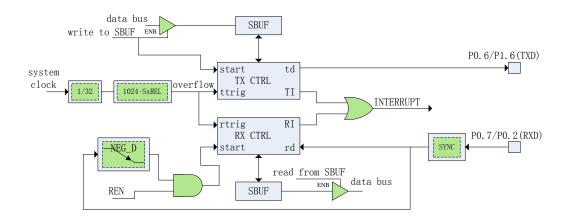

| 16.1 UART1 And UART2                                          |     |

| 16.1.1 Introduction                                           |     |

| 16.1.2 UARTx Register Description-                            |     |

| 17 I <sup>2</sup> C Interface                                 | 95  |

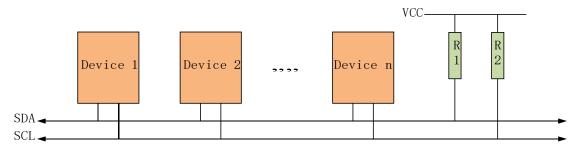

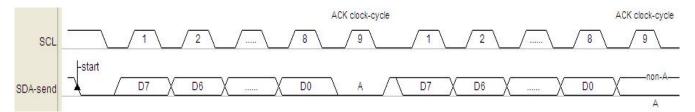

| 17.1 Function Introduction                                    | 95  |

| 17.2 I <sup>2</sup> C Main Features                           | 95  |

| 17.3 I <sup>2</sup> C Function Description                    | 95  |

| 17.4 I <sup>2</sup> C Communication Pin Mapping               | 97  |

| 17.5 Register Description                                     |     |

| 17.6 I <sup>2</sup> C Control Example                         |     |

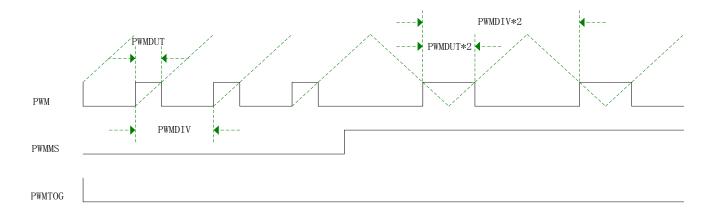

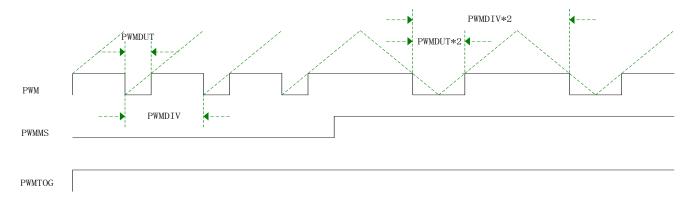

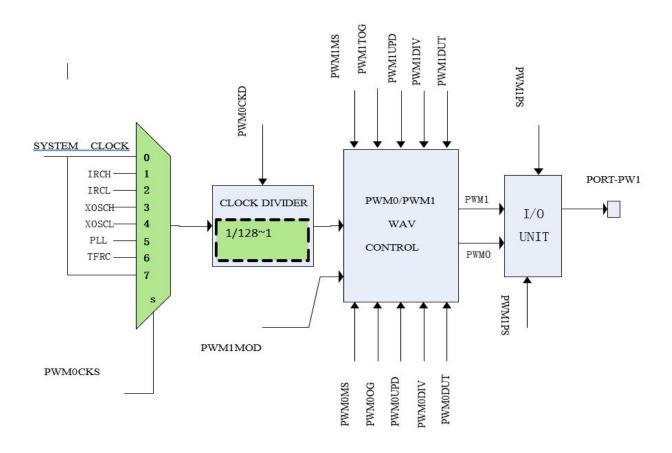

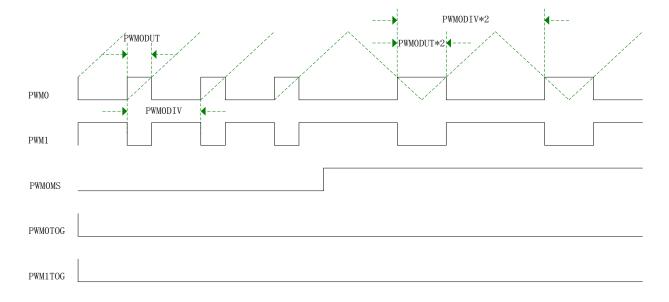

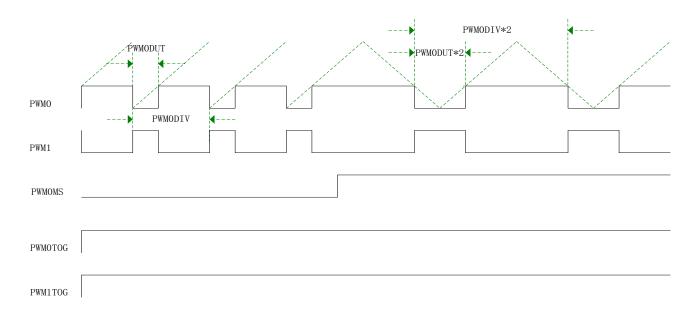

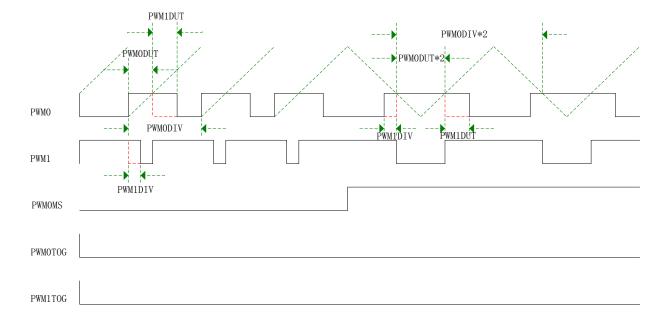

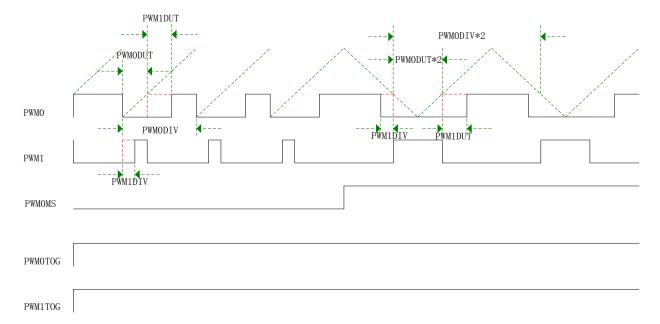

| 18 PWM                                                        | 108 |

| 18.1 PWM Function Introduction                                | 108 |

| 18.2 PWM Function Description                                 |     |

| 18.3 PWM Register Description                                 | 113 |

| 18 4 PWM Control Example                                      | 122 |

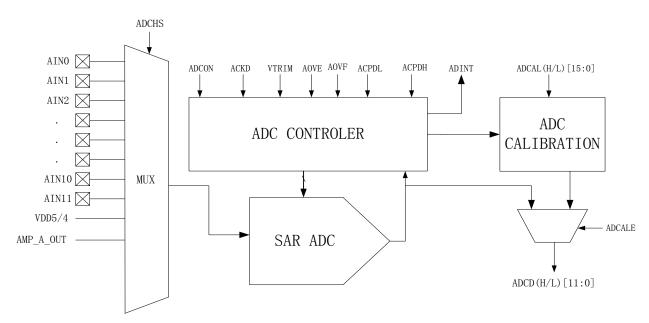

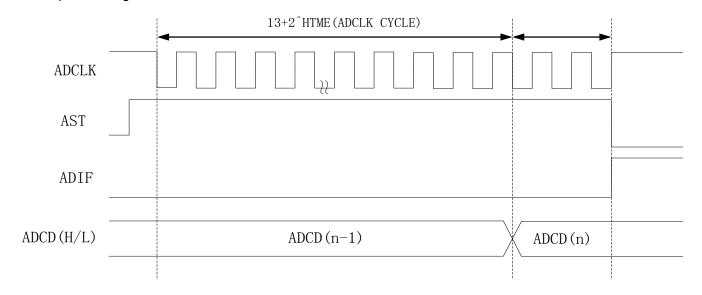

| 19 Analog/Digital Converter (ADC)  | 124 |

|------------------------------------|-----|

| 19.1 Function Introduction         | 124 |

| 19.2 Main Features                 | 124 |

| 19.3 Block Diagram                 | 125 |

| 19.4 Function Introduction         | 125 |

| 19.5 Register Description          | 126 |

| 19.6 ADC Control Example           | 130 |

| 20 Operational Amplifier (AMP)     |     |

| 20.1 Function Introduction         | 131 |

| 20.2 Register Description          | 131 |

| 21 Buzzer (BUZZER)                 | 133 |

| 21.1 Function Description          | 133 |

| 21.2 Register Description          | 133 |

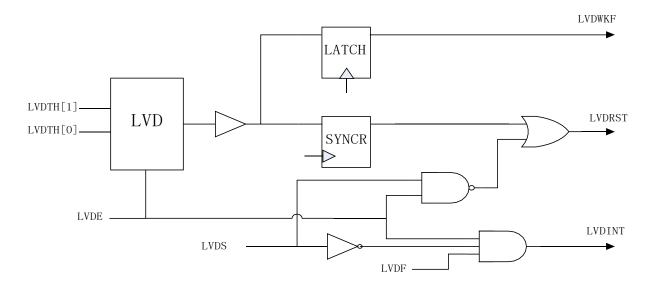

| 22 Low Voltage Detection (LVD)     | 135 |

| 22.1 Function Introduction         | 135 |

| 22.2 Function Description          | 135 |

| 22.3 Register Description          | 136 |

| 22.4 LVD Control Example           | 137 |

| 23 Wireless Charger Decoding       | 138 |

| 23.1 Function Introduction         | 138 |

| 23.2 Register Description          | 138 |

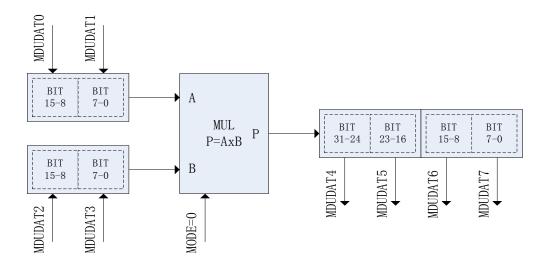

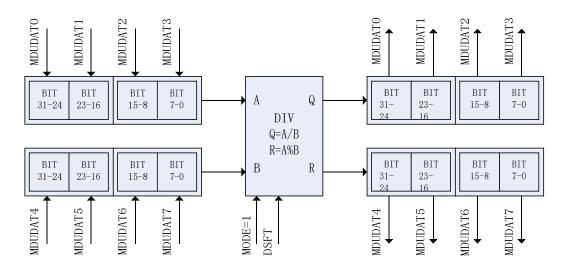

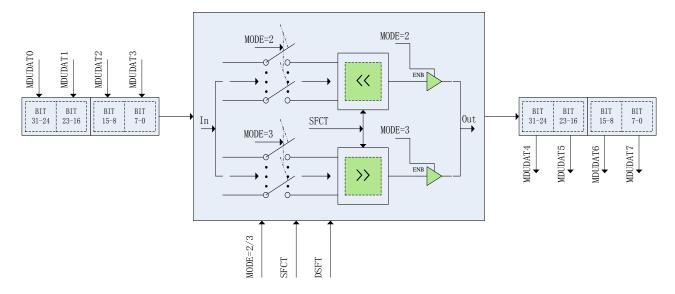

| 24 Multiplier/Divider Unit(MDU)    | 143 |

| 24.1 Function Introduction         | 143 |

| 24.2 Architecture                  | 143 |

| 24.3 Function Description          | 144 |

| 24.3.1 Multiplier                  |     |

| 24.3.2 Divider                     |     |

| 24.3.3 Shifter                     |     |

| 24.4 Register Description          | 145 |

| 24.5 MDU Control Example           | 148 |

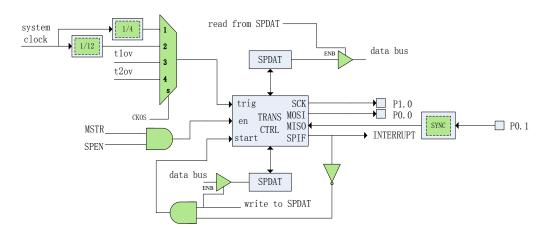

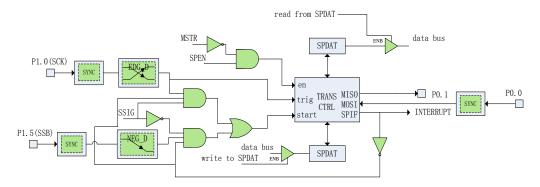

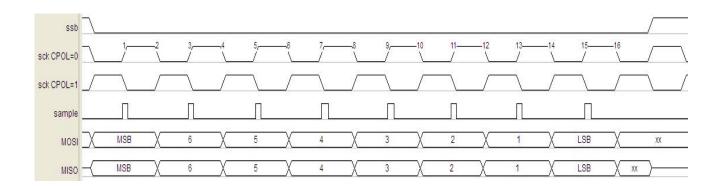

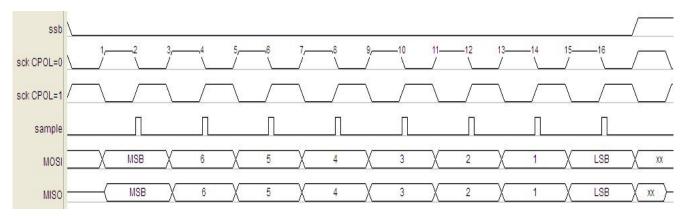

| 25 SPI                             | 152 |

| 25.1 Function Introduction         | 152 |

| 25.2 Register Description          | 155 |

| 25.3 SPI Control Example           | 157 |

| 26 SWIM                            | 160 |

| 26.1 Introduction                  | 160 |

| 26.2 Register Description          | 160 |

| 27 Program Download and Simulation | 163 |

| 27.1 Program Download              | 163 |

| 27.2 Online Simulation             | 163 |

| 28 Electrical Characteristics      | 164 |

| 28.1 Limit Parameter               | 164 |

| 28.2 DC Electrical Specification   |     |

| 28.3 AC Electrical Specification   |     |

| 29 Package Type                                  | 167 |

|--------------------------------------------------|-----|

| 30 Appendix                                      | 170 |

| Appendix 1 Instruction Set Quick Reference Table |     |

# 1 Introduction

JZ8FC003 series chip is an 8-bit MCU based on 1T 8051 core, which usually runs 10 times faster than the traditional 8051 chip and has more superior performance. The built-in 18K Flash program memory, which can be repeatedly programmed many times, brings great convenience to users' development. It not only retains the basic features of traditional 8051 chip, but also integrates function modules such as 12 Bit ADC, 16 Bit PWM, UART, I<sup>2</sup> C, OP-AMP and low voltage detection (LVD), and supports online simulation function. Three power-saving modes, IDLE, STOP and low-speed operation, are supported to accommodate applications with different power requirements. Widely used in consumer electronics and home appliances.

## 2 Basic Features

#### Core

- CPU: 1T 8051, up to 10 times faster than traditional 8051

- > Compatible with 8051 instruction set, dual DPTR operation mode

#### Memory

- Flash: 18 bytes, supports multiple rewrites

- Flash can be divided into program space and data space, the data space can be used to store the power down need to save data, can omit the EEPROM

- RAM:256 bytes of internal RAM, 1024 bytes of external RAM

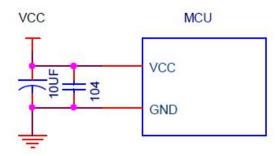

#### **Operating Voltage**

Operating voltage: 1.8 - 5.5V

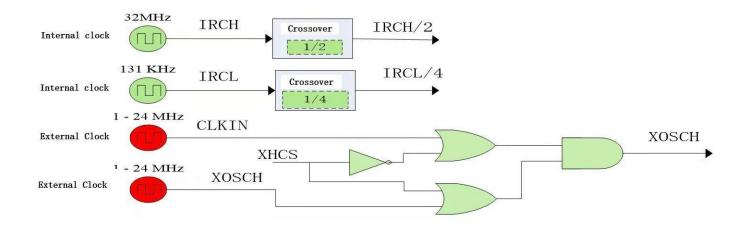

#### **Clock System**

- Internal Low Speed RC Oscillator: 131KHz

- ➤ Internal High Speed RC Oscillator: 32MHz, accuracy ±1% (3.3V@25°C) (default 2 divisions when used as system clock, i.e.16MHz)

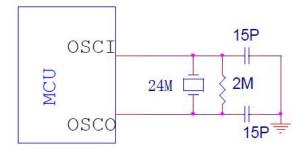

- External High Speed Oscillator: 1 24MHz, External Clock Input: 1 24MHz

#### **TMC Functions**

- The clock source is the Internal low Speed RC Oscillator, and the minimum unit of interrupt time is 512 Low Speed RC Oscillator clock cycles.

- ➤ Configurable interrupt time from 1 to 256 minimum units of time

#### **Interruption System**

- ➤ 15 effective interrupt sources

- > Two levels of interrupt priority which also supports interrupt nesting

- > 10 external interrupt sources, each external interrupt can be configured with any signal pin as an interrupt input pin

#### **Timer**

Three 16-bit general-purpose timers: Timer 0, Timer 1, Timer 2

#### **General Purpose IO (GPIO)**

Supports up to 18 GPIO ports, support push-pull, open-drain, strong pull-up, weak pull-up, strong pull-down, weak pull-down, high resistance mode

#### Analog/Digital Converter (ADC)

- > Supports 12 channel 12-bit SAR ADC with the function of operational amplification and comparison embedded

- > Supports 3 Reference Voltage : VDD, Internal Reference Voltage ,External Reference Voltage

- VDD voltage can be measured when internal voltage is selected as reference voltage

- > Supports configurable comparator modes

- Supports the detection signal through the op-amp reduction and then conversion, reduction multiplier can be selected

- > ADC can directly detect op-amp A output

- > ADC can be used in conjunction with PWM, with the PWM interrupt initiating the ADC conversion

#### Operational Amplifier (AMP)

> Op-amp A has built-in correction mechanism, after correction, the offset voltage is less than 0.5mV under full temperature condition.

#### **PWM**

- Supports 6 channel 12-bit SAR ADC with the function of operational amplification and comparison embedded

- ➤ PWM0 ~ PWM5 can select any IO pins as PWM output pins

- Supports Complementary Mode and Deadtime Control which could be used to drive Burushless DC motor

- Supports center fixed mode or edge fixed mode

- Support software brake and hardware brake

- Supports PWM pause function

- Supports to output of internal clock directly

- Supports PWM interrupt

#### Low Voltage Detection (LVD)

- Configurable voltage detection range, four grades selectable: 2.0V/2.7V/3.7V/4.4V

- ➤ Low voltage reset /interruptconfigurable

#### Reset mode

➤ The chip supports multiple reset sources: Hard Reset, Soft Reset, Watch Dog Reset, LVD Reset, Power On/Down

#### Watchdog

➤ 27-bit Watch Dog Timer, 16 bit precision configurable, with Watch Dog Reset and Interrupt configurable as well

7

#### **UART (UART1/UART2)**

- Supports 2 UART ports

- Supports 1-byte receive buffer

#### SPI

➤ Internal 1 x 4-wire SPI interface, supporting master-slave mode

#### **I2C** interface

➤ Internal 1-channel I²C interface, support master-slave mode, support standard/fast/high-speed mode

#### Buzzer

➤ Internal 1-channel buzzer drive output

### Multiplying / Dividing Unit (MDU)

- Supports 1 clock cycle 16-bit×16-bit multiplication

- ➤ Supports 8 clock cycles of 32 bit÷32-bit division

- Supports 1 clock cycle 32-bit data shift operation left and right

#### **Program Download and Simulation**

- Supports ISP and IAP

- ➤ Supports dual-line and single-line online simulation function

#### Low power consumption

- ➤ For STOP mode, current <7uA

- ➤ For IDLE mode, current <15uA

- ➤ For Low speed mode, current <25uA

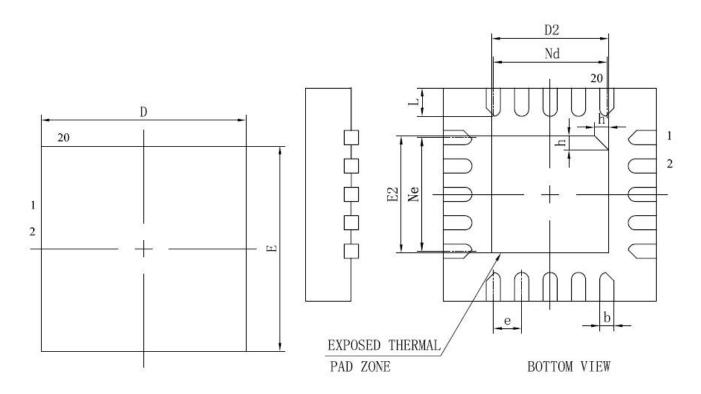

Package Type: TSSOP20/QFN20/SOP20

# 3 Chip Model and Function Description

Table 3-1 JZ8FC003 Specific Models and Their Features

| Models     | Flash Storage [BYTE]] | External Ram[BYTE] | Internal high-speed RC oscillator | Internal low-speed RC oscillator | External high-speed crystal oscillator | GPIO | UART | I <sup>2</sup> C | 16 bit PWM channels | SPI      | 12-bit ADC channels | General-purpose op-amps | Multiplier and Divider | ISP Upgrade | Simulation On Chip | Operating Voltage | Package Type |

|------------|-----------------------|--------------------|-----------------------------------|----------------------------------|----------------------------------------|------|------|------------------|---------------------|----------|---------------------|-------------------------|------------------------|-------------|--------------------|-------------------|--------------|

| JZ8FC003T3 | 18K                   | 1024               | √                                 | √                                | √                                      | 18   | 2    | √                | 6                   | √        | 12                  | 1                       | √                      | √           | √                  | 1.8-5.5           | TSSOP20      |

| JZ8FC003N2 | 18K                   | 1024               | <b>√</b>                          | 1                                | 1                                      | 18   | 2    | 1                | 6                   | 1        | 12                  | 1                       | 1                      | 1           | <b>√</b>           | 1.8-5.5           | QFN20        |

| JZ8FC003S4 | 18K                   | 1024               | √                                 | <b>√</b>                         | <b>√</b>                               | 18   | 2    | <b>√</b>         | 6                   | <b>√</b> | 12                  | 1                       | 1                      | <b>√</b>    | <b>√</b>           | 1.8-5.5           | SOP20        |

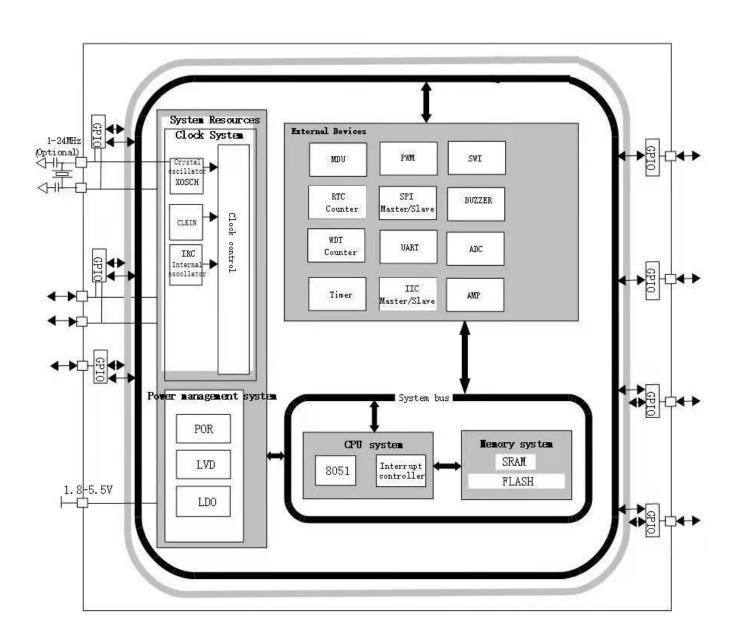

# 4 Block Diagram

Figure 4-1-1 Chip Block Diagram

# 5 Pin Package and Description

# **5.1 Package Definition**

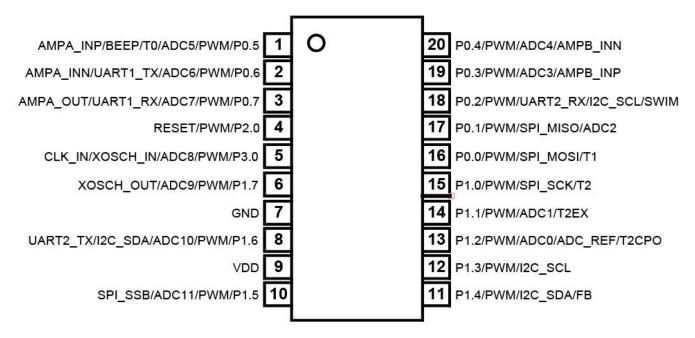

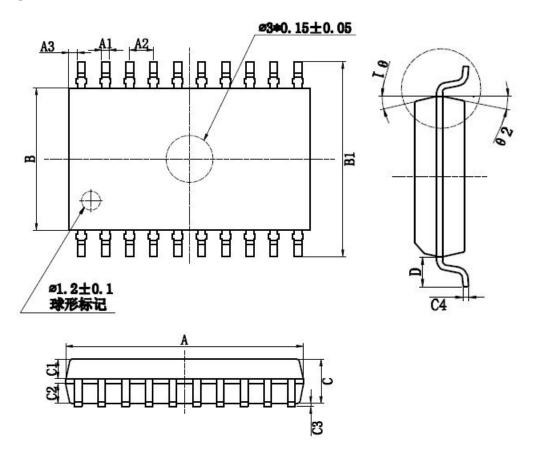

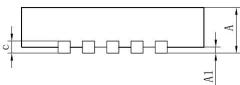

Model: JZ8FC003T3/S4

Figure 5-1-1 TSSOP20/SOP20 Package Diagram

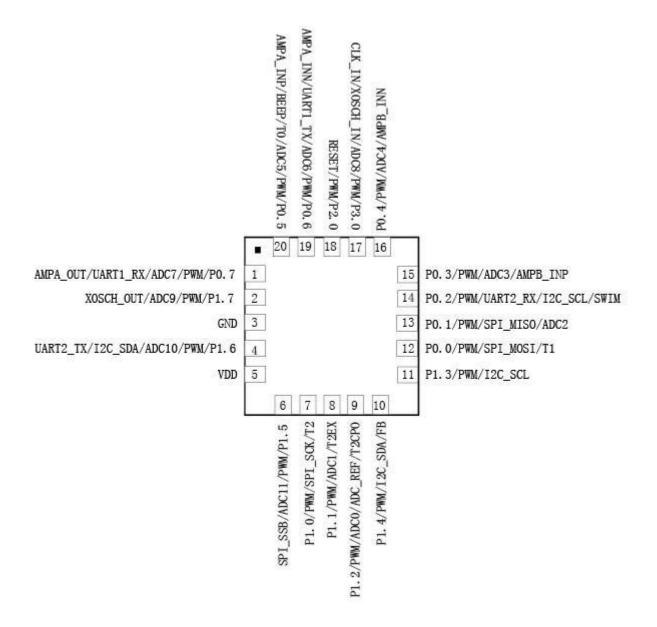

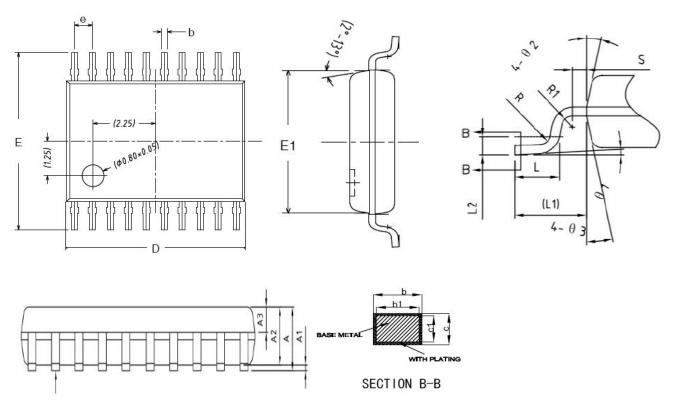

### Model: JZ8FC003N2

Figure 5-1-2 QFN20 package diagram

# **5.2 Pin Description**

Table 5-2-1 Pin Description

| Pin Seq<br>Num    |       | - Pin Name                               | Pin Function                                                                                                                                                         | Default Function                   |

|-------------------|-------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| TSSOP20/<br>SOP20 | QFN20 | Pin Name                                 | Pin Function                                                                                                                                                         | Default Function                   |

| 1                 | 20    | P0.5/T0/ADC_CH[5]/BEEP/PWM/AMP_A_P/T2CP  | General bi-directional I/O port Timer 0 T0 port ADC analog channel input Buzzer output PWM signal output Op-amp A input T2CP signal input                            | General bi-directional<br>I/O port |

| 2                 | 19    | P0.6/ADC_CH[6]/UART1_TX/PWM/AMP_A_N/T2CP | General bi-directional I/O port ADC analog channel input UART1 data sending port PWM signal output Op-amp A input T2CP signal input                                  | General bi-directional<br>I/O port |

| 3                 | 1     | P0.7/ADC_CH[7]/UART1_RX/PWM/AMP_A_O/T2CP | General bi-directional I/O port ADC analog channel input UART1 data reception port PWM signal output Op-amp A output T2CP signal input                               | General bi-directional<br>I/O port |

| 4                 | 18    | P2.0/RESET/PWM/T2CP                      | General bi-directional I/O port  Hard reset pins  PWM signal output  T2CP signal input                                                                               | Hard reset                         |

| 5                 | 17    | P3.0/ADC_CH[8]/XOSCH_IN/PWM/XCLK_IN/T2CP | General bi-directional I/O port  ADC analog channel input External high-speed crystal input PWM signal output External high speed clock input port T2CP signal input | General bi-directional<br>I/O port |

| 6  | 2  | P1.7/ ADC_CH[9]/ XOSCH_OUT/PWM/T2CP       | General bi-directional I/O port ADC analog channel input External high speed crystal output PWM signal output T2CP signal input                             | General bi-directional<br>I/O port |

|----|----|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 7  | 3  | VSS                                       | Power ground pin                                                                                                                                            | Power ground pin                   |

| 8  | 4  | P1.6/ADC_CH[10]/UART2_TX/PWM/I2C_SDA/T2CP | General bi-directional I/O port ADC analog channel input UART2 data sending port PWM signal output I2C data transfer port T2CP signal input                 | I2C data transfer port             |

| 9  | 5  | VDD                                       | Chip power supply pins                                                                                                                                      | Chip power supply pins             |

| 10 | 6  | P1.5/ADC_CH[11]/PWM/SPI_SSB/T2CP          | General bi-directional I/O port  ADC analog channel input  PWM signal output  SPI_SSB port  T2CP signal input                                               | General bi-directional I/O port    |

| 11 | 10 | P1.4/FB/PWM/I2C_SDA/T2CP                  | General bi-directional I/O port FB port PWM signal output I2C data transfer port T2CP signal input                                                          | I2C data transfer port             |

| 12 | 11 | P1.3/PWM/I2C_SCL/T2CP                     | General bi-directional I/O port PWM signal output I2C clock transfer port T2CP signal input                                                                 | I2C clock<br>transmission port     |

| 13 | 9  | P1.2/ ADC_CH[0]/ADC_REF/PWM/T2CPO/T2CP    | General bi-directional I/O port  ADC analog channel input  ADC external reference  voltage input  PWM signal output  T2CPO signal output  T2CP signal input | General bi-directional             |

|    |    |                                     | 1                                                                                                                                                             |                                           |

|----|----|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 14 | 8  | P1.1/ADC_CH[1]/ PWM /T2CP           | General bi-directional I/O port  ADC analog channel input  PWM signal output  T2CP signal input                                                               | General bi-directional                    |

| 15 | 7  | P1.0/T2/PWM/SPI_SCK/T2CP            | General bi-directional I/O port Timer 2 T2 port PWM signal output SPI clock transfer port T2CP signal input                                                   | General bi-directional<br>I/O port        |

| 16 | 12 | P0.0/T1/PWM/SPI_MOSI/T2CP           | General bi-directional I/O port Timer 1 T1 port PWM signal output SPI_MOSI port T2CP signal input                                                             | General purpose<br>bi-directional IO port |

| 17 | 13 | P0.1/ADC_CH[2]/PWM/SPI_MISO/T2CP    | General bi-directional I/O port  ADC analog channel input  PWM signal output  SPI_MISO port T2CP  signal input                                                | General bi-directional                    |

| 18 | 14 | P0.2/SWIM/UART2_RX/PWM/I2C_SCL/T2CP | General bi-directional I/O port Single-wire communication data port UART2 data reception port PWM signal output I2C clock transmission port T2CP signal input | Single wire<br>communication data<br>port |

| 19 | 15 | P0.3/ADC_CH[3]/PWM/AMP_B_P/T2CP     | General bi-directional I/O port  ADC analog channel input  PWM signal output  Op-amp B input port  T2CP signal input                                          | General bi-directional I/O port           |

| 20 | 16 | P0.4/ ADC_CH[4]/PWM/AMP_B_N/T2CP    | General bi-directional I/O port  ADC analog channel input  PWM signal output  Op-amp B input port  T2CP signal input                                          | General bi-directional                    |

Note: See Table 15-2-5 and Table 15-2-7 for details on how to set the signal pin multiplexing function

# 6 Central Processing Unit (CPU)

#### 6.1 CPU Introduction

The JZ8FC003 series chips use a single-cycle 8051 CPU, which is fully compatible with the original MCS-51 instruction set. the CPU uses a pipelined architecture, and typically, the single-cycle 8051 CPU runs 10 times faster than a standard 8051 processor.

The features of this CPU are:

1T 8051 CPU

Compatible with 8051instruction set, for more you may refer to instruction set in Appendix Double DPTR, so that the data could be moved quickly

## **6.2 Register Description**

#### **Program Counter (PC)**

Program Counter (PC) is a 16-bit register without register address which is used to control the sequence of instructions. It is set to 0 after reset/power on and the machine will execute the program from zero address.

#### Accumulator (ACC)

Accumulator (ACC) is a special register and 'A' is used as its instruction mnemonic. It is often used to store the operand and result of logical/arithmetic computing.

#### **General Register B**

Register B cannot to be used without ACC in multiplying/dividing computing. Instruction MUL AB multiplies 8-bit unsigned number in ACC and B. The lower bytes (16 bit) and higher bytes(16 bit) of the computing result will be stored in A and B respectively. Furthermore, instruction DIV AB divides B by A, and the integer quotient will be stored in A with remainder stored in B. In addition, register B can also be used as general temporary storage register.

#### Stack Pointer (SP)

Stack Pointer(SP) is a 8 bit special register and indicates where the top of stack is in the internal RAM. It is initialized to 07H after a reset which makes stack actually starts from 08H. Since 08H~1FH belongs to working register group 1~3, if they are used in program development, SP is recommended to be set to 80H or even higher.

#### **Data Pointer (DPTR)**

Data pointer DPTR0/DPTR1 are two 16-bit special register with their higher stored in register DP0H/DP1H respectively and lower bytes stored in register DP0H/DP1H respectively. By setting DPS(PSW.1) either of them can be used. For each DPTR, it can be seen as one 16-bit register or two independent 8-bit registers DP0H/DP1H and DP0L/DP1L.

## **Program Status Word (PSW)**

Program Status Word(PSW) is a register indicates the statues of the CPU. The status bit of it will change correspondingly when the CPU is doing arithmetic or logical operations.

#### **Table 6-2-1 Accumulator ACC**

| EOH           | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------------|---|----------|---|---|---|---|---|---|--|--|

| ACC           |   | ACC[7:0] |   |   |   |   |   |   |  |  |

| R/W           |   | R/W      |   |   |   |   |   |   |  |  |

| Initial Value | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

### Table 6-2-2 General Register B

| FOH           | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------------|---|--------|---|---|---|---|---|---|--|--|--|

| В             |   | B[7:0] |   |   |   |   |   |   |  |  |  |

| R/W           |   | R/W    |   |   |   |   |   |   |  |  |  |

| Initial Value | 0 | 0      | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

#### **Table 6-2-3 Stack Pointer SP**

| 81H           | 7 | 6       | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------------|---|---------|---|---|---|---|---|---|--|--|--|

| SP            |   | SP[7:0] |   |   |   |   |   |   |  |  |  |

| R/W           |   | R/W     |   |   |   |   |   |   |  |  |  |

| Initial Value | 0 | 0       | 0 | 0 | 0 | 1 | 1 | 1 |  |  |  |

#### Table 6-2-4 Data Pointer DP0L

| 82H           | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------------|---|-----------|---|---|---|---|---|---|--|--|--|

| DPOL          |   | DPOL[7:0] |   |   |   |   |   |   |  |  |  |

| R/W           |   | R/W       |   |   |   |   |   |   |  |  |  |

| Initial Value | 0 | 0         | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

#### Table 6-2-5 Data Pointer DP0H

| 83H           | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------------|---|-----------|---|---|---|---|---|---|--|--|--|

| DP0H          |   | DP0H[7:0] |   |   |   |   |   |   |  |  |  |

| R/W           |   | R/W       |   |   |   |   |   |   |  |  |  |

| Initial Value | 0 | 0         | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

#### **Table 6-2-6 Data Pointer DP1L**

| 84H           | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------------|---|-----------|---|---|---|---|---|---|--|--|--|

| DP1L          |   | DP1L[7:0] |   |   |   |   |   |   |  |  |  |

| R/W           |   | R/W       |   |   |   |   |   |   |  |  |  |

| Initial Value | 0 | 0         | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

### Table 6-2-7 Data Pointer DP1H

| 85H           | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------------|---|-----------|---|---|---|---|---|---|--|--|--|

| DP1H          |   | DP1H[7:0] |   |   |   |   |   |   |  |  |  |

| R/W           |   | R/W       |   |   |   |   |   |   |  |  |  |

| Initial Value | 0 | 0         | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

## **Table 6-2-8 Status Register PSW**

| D0H           | 7          | 6   | 5           | 4       | 3 | 2   | 1   | 0 |  |  |

|---------------|------------|-----|-------------|---------|---|-----|-----|---|--|--|

| PSW           | CY         | AC  | F0          | RS[1:0] |   | ov  | DPS | Р |  |  |

| R/W           | R/W        | R/W | R/W         | R/W     |   | R/W | R   | R |  |  |

| Initial Value | 0          | 0   | 0           | 0       | 0 | 0   | 0   | 0 |  |  |

|               |            |     |             |         |   |     |     |   |  |  |

| Bit Number    | Bit Symbol |     | Description |         |   |     |     |   |  |  |

| Bit Number | Bit Symbol | Description                                                                                                                                                                             |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | CY         | Carry flag  0: There is no carry or borrow happened in arithmetic/logical operation 1:  There is carry or borrow happened in arithmetic/logical operation                               |

| 6          | AC         | Auxiliary Carry Flag  0: There is no auxiliary carry or borrow happened in arithmetic/logical operation 1:  There is auxiliary carry or borrow happened in arithmetic/logical operation |

| 5          | F0         | F0 flag It is defined by the user                                                                                                                                                       |

| 4~3        | RS         | R0~R7 registers' page selection 00: page 0(mapping to 00H-07H) 01: page 1(mapping to 08H-0FH) 10: page 2(mapping to 10H-17H) 11: page 3(mapping to 18H-1FH)                             |

| 2          | ov         | Overflow flag 0: no overflow 1: overflow happened                                                                                                                                       |

| 1          | DPS        | DPTR selector, 0 for DPTR0, 1 for DPTR1                                                                                                                                                 |

| 0          | Р          | Parity flag  0: the number of 1 in ACC is even 1: the number of 1 in ACC in odd                                                                                                         |

## Table 6-2-9 Register SPMAX

| 8100H         | 7          | 6                       | 5                                                                                                                                                           | 4 | 3           | 2 | 1 | 0 |  |  |  |

|---------------|------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|---|---|---|--|--|--|

| SPMAX         |            | SPMAX[7:0]              |                                                                                                                                                             |   |             |   |   |   |  |  |  |

| R/W           | R/W        | R/W R/W R/W R/W R/W R/W |                                                                                                                                                             |   |             |   |   |   |  |  |  |

| Initial Value | 0          | 0                       | 0                                                                                                                                                           | 0 | 0           | 0 | 0 | 0 |  |  |  |

|               |            |                         |                                                                                                                                                             |   |             |   |   |   |  |  |  |

| Bit Number    | Bit Symbol |                         |                                                                                                                                                             |   | Description |   |   |   |  |  |  |

| 7~0           | SPMAX      |                         | SPMAX is used to record the maximum value of SP. Users can check this register using software to decide whether there is a risk that the stack may overflow |   |             |   |   |   |  |  |  |

# 7 Memory Architecture

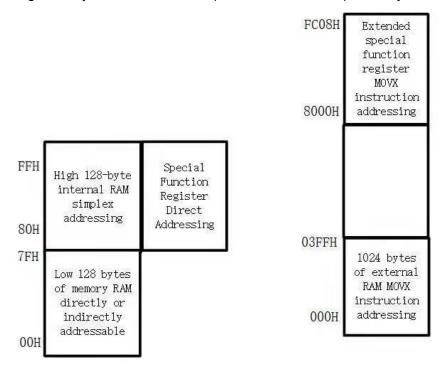

# 7.1 Random Access Memory (RAM)

The JZ8FC003 series chips provide 256 bytes of internal RAM and 1024 bytes of external RAM with the following memory address assignments:

- The low 128 bytes of internal RAM (address: 00H ~ 7FH) can be addressed directly or indirectly.

- The high 128 bytes of internal RAM (address: 80H ~ FFH) can only be indirectly addressed.

Figure 7-1-1 RAM Architecture

# 7.2 Special Function Register (SFR)

internal RAM share the address  $80H \sim FFH$ , can only be directly addressed, SFR mapping as shown in Table 7-2-1.

Table 7-2-1 Special Function Register (SFR) Mapping Table

|     | Bit-address<br>able |         |         | Non     | -bit addressal | ole    |        |         |

|-----|---------------------|---------|---------|---------|----------------|--------|--------|---------|

|     | 0/8                 | 1/9     | 2/A     | 3/B     | 4/C            | 5/D    | 6/E    | 7/F     |

| F8H | EXIP                | EPIE    | EPIF    | EPCON   | IDLSTL         | IDLSTH | STPSTL | STPSTH  |

| F0H | В                   | _       | _       | _       | -              | -      | -      | INDEX   |

| E8H | EXIE                | -       | _       | -       | -              | -      | -      | LVDCON  |

| ЕОН | ACC                 | -       | _       | -       | -              | -      | MDUCON | MDUDAT  |

| D8H | -                   | -       | PWMEN   | PWMUPD  | PWMCMX         | PWMCON | PWMCFG | PWMDIVL |

| D0H | PSW                 | PWMDIVH | PWMDUTL | PWMDUTH | PWMAIF         | PWMBIF | PWMCIF | PWMDIF  |

| C8H | T2CON               | T2MOD   | T2CL    | T2CH    | TL2            | TH2    | -      | -       |

| СОН | -                   | -       | -       | -       | -              | -      | -      | -       |

| В8Н | IP                  | ADCON   | ADCFGL  | ADCFGH  | ADCDL          | ADCDH  |        |         |

| вон | P3                  | 12CCON  | I2CADR  | I2CADM  | 12CCCR         | 12CDAT | I2CSTA | 12CFLG  |

| A8H | IE                  | -       | WDCON   | WDFLG   | WDVTHL         | WDVTHH | -      | -       |

| АОН | P2                  | S2CON   | S2BUF   | S2RELL  | S2RELH         | SPCON  | SPDAT  | SPSTA   |

| 98H | -                   | -       | S1CON   | S1BUF   | S1RELL         | S1RELH | -      | -       |

| 90H | P1                  | -       | -       | -       | -              | -      | -      | -       |

| 88H | TCON                | TMOD    | TL0     | TL1     | TH0            | TH1    | IT1CON | IT0CON  |

| 80H | P0                  | SP      | DPOL    | DP0H    | DP1L           | DP1H   | PWCON  | PCON    |

Due to the limited SFR address space, the JZ8FC003 series chips add extended special function registers to the external RAM address space, and the extended special function register mapping is shown in Figure 7-2-2.

**Table 7-2-2 Extended Special Function Register Mapping Table**

|       | 0/8    | 1/9     | 2/A    | 3/B    | 4/C    | 5/D      | 6/E          | 7/F   |

|-------|--------|---------|--------|--------|--------|----------|--------------|-------|

| 8000H | P00F   | P01F    | P02F   | P03F   | P04F   | P05F     | P06F         | P07F  |

| 8008H | P10F   | P11F    | P12F   | P13F   | P14F   | P15F     | P16F         | P17F  |

| 8010H | P20F   | -       | -      | -      | -      | -        | -            | -     |

| 8018H | P30F   | -       | -      | -      | -      | -        | -            | -     |

| 8080H | CKCON  | CKSEL   | CKDIV  | IHCFGL | IHCFGH | ILCFG[L] | XHISEL       | -     |

| 8088H | ADCALL | ADCALH  | ACPDLL | ACPDLH | ACPDHL | ACPDHH   | ADPWMT<br>RG | ADOPC |

| 8098H | PWMPS  | PWMHS   | PWMFBC | PWMFBS | PWMSBC | PWMBD    |              |       |

| 80A0H | T2CPPS | T2CPCHS | T2CPF  | T2CPL  | T2CPH  |          |              |       |

| 80A8H | TMCON  | TMSNU   |        |        |        |          |              |       |

| 80B0H | SWICON | SWIDAT  | SWISTA | SWIOVT |        |          |              |       |

| 80B8H | AMPCON | AMPAOS  |        |        |        |          |              |       |

| 80C0H | BZCON  | BZDIVL  | BZDIVH | BZDUTL | BZDUTH |          |              |       |

| 8100H | SPMAX  | I2CIOS  | -      | -      | ı      | -        | -            | -     |

| 8118H | UDCKS1 | UDCKS2  | -      | -      | -      | -        | FTCTL        | TPCTL |

| 8120H | P00C  | P01C  | P02C  | P03C | P04C  | P05C | P06C | P07C   |

|-------|-------|-------|-------|------|-------|------|------|--------|

| 8128H | P10C  | P11C  | P12C  | P13C | P14C  | P15C | P16C | P17C   |

| 8130H | P20C  | -     | -     | -    | -     | -    | -    | -      |

| 8138H | P30C  | -     | -     | -    | -     | -    | -    | -      |

| FC00H | MECON | FSCMD | FSDAT | LOCK | PADRD | PTSL | PTSH | REPSET |

| FC08H |       |       |       |      |       |      |      |        |

# 7.3 Flash

# 7.3.1 Function Introduction

Flash memory contains 18K bytes of Flash main data area, Flash memory is rewritable, Flash memory is controlled by a specific set of registers, users can use these registers to read, write and erase, set the write protection and other operations.

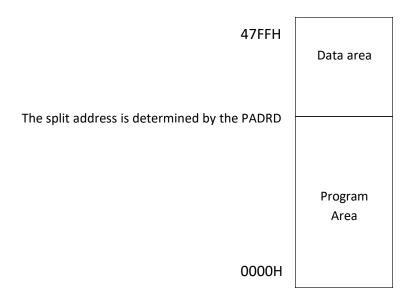

## 7.3.2 Flash Architecture

- Flash consists of several sectors which are the smallest units for erasure. Each sector is 128 bytes.

- Flash can be divided into DATA area and PROGRAM area and the division unit is 128 byte. PROGRAM

area is used to store use's program and DATA area is used to store data that needs to be protected

during power off period.

Figure 7-3-1 18K Flash Memory Structure

# 7.3.3 Flash Register Description

**Table 7-3-3-1 Register MECON**

| FC00H         | 7          | 6                                          | 5 | 4 | 3           | 2 | 1 | 0    |  |  |

|---------------|------------|--------------------------------------------|---|---|-------------|---|---|------|--|--|

| MECON         | -          | DPSTB                                      | - | - | -           | - | - | воот |  |  |

| R/W           | -          | R/W                                        | 1 | ı | -           | 1 | - | R/W  |  |  |

| Initial Value | -          | 0                                          | = | = | -           | = | - | 0    |  |  |

|               |            |                                            |   |   |             |   |   |      |  |  |

| Bit Number    | Bit Symbol |                                            |   |   | Description |   |   |      |  |  |

| 7             | -          |                                            | - |   |             |   |   |      |  |  |

| 6             | DPSTB      | Flash SLEEP mode control in IDLE/STOP mode |   |   |             |   |   |      |  |  |

|     |      | 0: Flash in NORMAL mode while IDLE/STOP 1: Flash in SLEEP mode while IDLE/STOP Note: If DPSTB=1, when the chip enters IDLE/STOP mode, the Flash will enter SLEEP mode simultaneously and the power consumption of the Flash in SLEEP mode is 50nA. When the chip exits IDLE/STOP mode, Flash exits SLEEP mode as well. |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5~1 | -    | -                                                                                                                                                                                                                                                                                                                      |

| 0   | воот | Set the program start space selection bit field after soft reset 0:  Program runs from FLASH after soft reset  1: Program starts running from XRAM after soft reset                                                                                                                                                    |

## Table 7-3-3-2 Register FSCMD

| FC01H         | 7          | 6                                                                                                                     | 5                                                                                                                                                                       | 4                                                | 3                                             | 2 | 1                       | 0    |  |  |  |  |  |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------|---|-------------------------|------|--|--|--|--|--|

| FSCMD         | -          | CMD[2:0]                                                                                                              |                                                                                                                                                                         |                                                  |                                               |   |                         |      |  |  |  |  |  |

| R/W           | -          | -                                                                                                                     | R/W                                                                                                                                                                     |                                                  |                                               |   |                         |      |  |  |  |  |  |

| Initial Value | -          | -                                                                                                                     | -                                                                                                                                                                       | -                                                | -                                             | 0 | 0                       | 0    |  |  |  |  |  |

|               |            |                                                                                                                       |                                                                                                                                                                         |                                                  |                                               |   |                         |      |  |  |  |  |  |

| Bit Number    | Bit Symbol |                                                                                                                       |                                                                                                                                                                         |                                                  | Description                                   |   |                         |      |  |  |  |  |  |

| 7~3           | -          | -                                                                                                                     |                                                                                                                                                                         |                                                  |                                               |   |                         |      |  |  |  |  |  |

| 2~0           | CMD        | the whole Flash DATA a Write Flash I 011: Erase o 101: Read F 110: Write 111: Erase o Note: 1. The CMD i 2. The CMD i | as 100: Erase<br>ash 001: Rea<br>rea 010:<br>DATAarea<br>one sector of tall<br>clash program<br>Flash program<br>one sector of tall<br>s automaticalla<br>emains unchai | the Flash DATA<br>area<br>area<br>the Flash prog | ram area<br>r the erase con<br>read and write |   | uted.<br>re written and | then |  |  |  |  |  |

## **Table 7-3-3-3 Register FSDAT**

| FC02H         | 7                         | 6                      | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|---------------------------|------------------------|---|---|---|---|---|---|

| FSDAT         |                           | FSDAT[7:0]             |   |   |   |   |   |   |

| R/W           |                           | R/W                    |   |   |   |   |   |   |

| Initial Value | 0                         | 0                      | 0 | 0 | 0 | 0 | 0 | 0 |

|               |                           |                        |   |   |   |   |   |   |

| Bit Number    | Bit Sy                    | Bit Symbol Description |   |   |   |   |   |   |

| 7~0           | FSDAT Flash Data Register |                        |   |   |   |   |   |   |

24

## Table 7-3-3-4 Register LOCK

| FC03H         | 7          | 6                                                  | 5                                                                  | 4           | 3           | 2    | 1    | 0    |  |  |

|---------------|------------|----------------------------------------------------|--------------------------------------------------------------------|-------------|-------------|------|------|------|--|--|

| LOCK          |            |                                                    |                                                                    |             |             |      |      |      |  |  |

| R             |            | REPE                                               |                                                                    |             | FLKF        | PLKF | DLKF | ILKF |  |  |

| W             |            |                                                    |                                                                    | LOCK        | ([7:0]      |      |      |      |  |  |

| Initial Value | 0          | 0                                                  | 0                                                                  | 0           | 0           | 0    | 0    | 0    |  |  |

|               |            |                                                    |                                                                    |             |             |      |      |      |  |  |

| Bit Number    | Bit Symbol |                                                    |                                                                    |             | Description |      |      |      |  |  |

|               |            |                                                    | Write                                                              | operation   |             |      |      |      |  |  |

| 7~0           | LOCK       | 29H: Unloc<br>Unlock Flash                         | k Flash progra<br>k Flash progra<br>I DATA area<br>is locked, no v | m area 2AH: |             | ible |      |      |  |  |

|               |            |                                                    | Read                                                               | operation   |             |      |      |      |  |  |

| 7~4           | -          |                                                    |                                                                    |             |             |      |      |      |  |  |

| 3             | FLKF       | KF Programmable zone unlock flag, 1 means unlocked |                                                                    |             |             |      |      |      |  |  |

| 2             | PLKF       | Program area unlock flag, 1 means unlocked         |                                                                    |             |             |      |      |      |  |  |

| 1             | DLKF       | Data area unlock flag, 1 means unlocked            |                                                                    |             |             |      |      |      |  |  |

| 0             | -          | -                                                  |                                                                    |             |             |      |      |      |  |  |

### **Table 7-3-3-5 Register PADRD**

| FC04H         | 7             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                  | 4  | 3                                              | 2                | 1               | 0      |  |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----|------------------------------------------------|------------------|-----------------|--------|--|

| PADRD         |               | PADRD[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |    |                                                |                  |                 |        |  |

| R/W           |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    | R/ | ′W                                             |                  |                 |        |  |

| Initial Value | 0             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                  | 0  | 0                                              | 0                | 0               | 0      |  |

|               |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |    |                                                |                  |                 |        |  |

| Bit Number    | Bit<br>Symbol |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |    | Description                                    |                  |                 |        |  |

| 7~0           | PADRD         | The unit for of the address of the a | livision is 128 lispace for PROG<br>space for DATA |    | en PADRD>0:<br>~ (PADRD × 12<br>D × 128) ~ 47F | 28 - 1),<br>FFH. | llue of PADRD ( | cannot |  |

## Table 7-3-3-6 Register PTS

|  | FC05H | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--|-------|---|---|---|---|---|---|---|---|--|

|--|-------|---|---|---|---|---|---|---|---|--|

| PTSL          |            | PTS[7:0]     |                                 |   |             |     |   |   |  |  |

|---------------|------------|--------------|---------------------------------|---|-------------|-----|---|---|--|--|

| R/W           |            |              | R/W                             |   |             |     |   |   |  |  |

| Initial Value | 0          | 0            | 0 0 0 0 0 0                     |   |             |     |   |   |  |  |

| FC06H         | 7          | 6            | 5                               | 4 | 3           | 2   | 1 | 0 |  |  |

| PTSH          | -          | -            | - PTS[12:8]                     |   |             |     |   |   |  |  |

| R/W           | -          | -            | -                               |   |             | R/W |   |   |  |  |

| Initial Value | -          | -            | -                               | 0 | 0           | 0   | 0 | 0 |  |  |

|               |            |              |                                 |   |             |     |   |   |  |  |

| Bit Number    | Bit Symbol |              |                                 |   | Description |     |   |   |  |  |

| 15~13         | -          | -            |                                 |   |             |     |   |   |  |  |

| 12~0          | PTS        | target addre | target address pointer register |   |             |     |   |   |  |  |

# 7.3.4 Flash Control Example

#### Divide Flash into DATA area and PROGRAM area

For instance, if the user wants to divide a 18K Flash (128 byte DATA area and the remains for PROGRAM area), the program may like this:

PADRD=0x8F;//Program area space address is: 0~0x477F,data area space address is: 0x4780~0x47FF

Note: The physical address of the above set data area in FLASH is 0x4780~0x47FF, but the logical address is

0x0000~0x007F, the logical address should be filled in when reading and writing data area.

#### Sector erasure of DATA area

Sector n of DATA area needs to be erased, for example, the program may as follows:

\_\_\_\_\_

FSCMD = 0; //Set CMD = 0LOCK = 0x2A; //unlock DATA area

PTSH = (unsigned char)((n\*0x80)>>8); //set the higher bytes of the sector 's address PTSL = (unsigned char)(n\*0x80); //set the lower bytes of the sector 's address

FSCMD = 3; //set clear LOCK = 0xAA; //lock FLASH

\_\_\_\_\_

Note: Sector serial number n=0, 1, 2 ......

#### Write data into DATA area

For instance, to write data 0xAA to the data space address n~(n+100), the program is as follows:

\_\_\_\_\_

unsigned char i;

FSCMD = 0; //set CMD = 0

LOCK = 0x2A; //unlock DATA area

PTSH = (unsigned char)(n>>8); //set the higher 8 bits of data's original address

PTSL = (unsigned char)n; //set the lower 8 bits of data's original address FSCMD = 2; //set WRITE command

for(i=0;i<100;i++)

```

{

FSDAT = 0xAA; //write data continuously

}

LOCK = 0xAA; //lock FLASH

```

#### Note:

- 1. When data is written continuously, only original address has be set. PTS will increase automatically after writing FSDAT each time.

- 2. For DATA area R/W, only the logical address of the DATA area which starts from 0 needs to be set, instead of the physical address.

#### Read data from DATA area

For instance, to read data from data space address n~(n+100) to pointer pBuf, the program is as follows:

```

unsigned char i, pBuf;

FSCMD = 0;  // set CMD = 0

LOCK = 0x2A;  //unlock DATA area

PTSH = (unsigned char)(n>>8);  //set the higher 8 bits of data's original address

PTSL = (unsigned char)n;  //set the lower 8 bits of data's original address FSCMD = 1; //setREAD command for(i=0;i<100;i++)

{

*pBuf++ = FSDAT ;//read data continuously

}

FSCMD=0;

LOCK = 0xAA;  //lock FLASH

```

Note: When data is read continuously, only original address has be set. PTS will increase automatically after writing FSDAT each time.

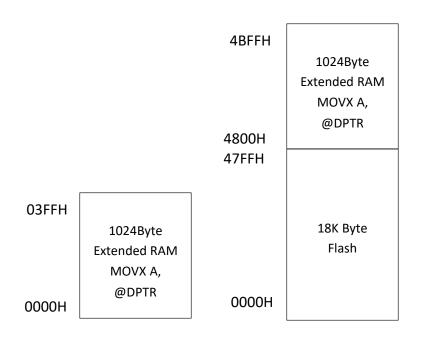

# 7.4 External RAM Mapped to Program Area

The 1024 bytes of external RAM can be mapped for use as program space with mapped addresses of 4800H~4BFFH, and the mapping diagram is shown in Figure 7-4-1. Users can download the program to the external RAM space, and when the program is running directly execute the jump instruction to jump to the mapped program area for execution. For the same effect, the value of BOOT (see register MECON for details) can also be set to 1, and then a soft reset is executed, and the program starts to execute from the external RAM space after the reset (the mapped address is 0000H~03FFH at this time). The mapped program area is particularly convenient for implementing functions such as IAP.

Figure 7-4-1 XRAM Address Mapping

# **8 Interruption System**

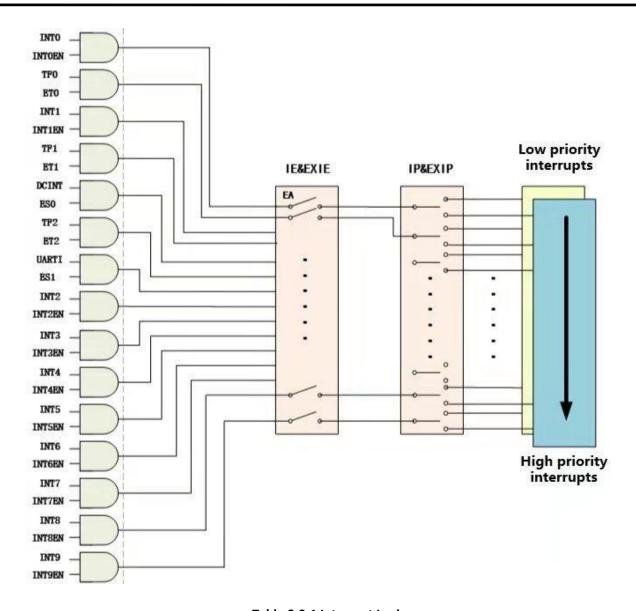

### 8.1 Function Introduction

JZ8FC003 Series include a enhanced interrupt control system with 15 interrupt entries. For each interrupt entry, there are several interrupt sources with 2 level interrupt priorities for each source. Each interrupt source has its independent interrupt vector, priority setting, interrupt enable control and interrupt flag. CPU enters corresponding Interrupt Service Routine after responding to the interrupt. It will then returns to the former status after receiving RETI. If there are multiple valid sources requesting interrupts, CPU will respond sequentially according to the interrupt priority set before. If the sources share the same priority, CPU will respond according to their natural priority (from the smallest address to largest address of the interrupt entries).

# 8.2 Interrupt logic

Table 8-2-1 Interrupt Logic

# 8.3 Interrupt vector table

| Interruptions | Interrupt source           | vector | Default Priority |

|---------------|----------------------------|--------|------------------|

| INT0          | INT0                       | 03H    | 0                |

| TF0           | Timer 0                    | ОВН    | 1                |

| INT1          | INT1                       | 13H    | 2                |

| TF1           | Timer1                     | 1BH    | 3                |

| FSK           | Wireless charger decoding  | 23H    | 4                |

| TF2           | Timer 2                    | 2BH    | 5                |

| UART1         | UART1                      | 33H    | 6                |

| INT2          | ADC/External Interrupt 2   | 3BH    | 7                |

| INT3          | UART2/External Interrupt 3 | 43H    | 8                |

| INT4          | LVD/External Interrupt 4   | 4BH    | 9                |

| INT5 | SPI/External Interrupts5     | 53H | 10 |

|------|------------------------------|-----|----|

|      |                              |     | 11 |

| INT6 | I2C/SWI/External Interrupt 6 | 5BH | 11 |

| INT7 | WDT/External Interrupt 7     | 63H | 12 |

| INT8 | TMC/External Interrupt 8     | 6BH | 13 |

| INT9 | PWM/External Interrupt 9     | 73H | 14 |

# 8.4 Interrupt Control Register

Table 8-4-1 Register IE

| IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Аоп           | /          | 0                                | J                                    | 4               | ٠,          | 2   | 1   | U   |  |  |