VC0882 Data Book

# VC0882 Data Book

# **Revision 0.92**

Notes1: The information is subject to change without notice. Before using this document, please confirm that this is the latest version.

Notes2: Not all products and/or types are available in every country. Please check with a Vimicro sales representative availability and additional information.

## **Important Notice**

Vimicro Corporation and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to Vimicro's terms and conditions of sale supplied at the time of order acknowledgment.

Vimicro does not warrant or represent that any license, either express or implied, is granted under any Vimicro patent right, copyright, mask work right, or other Vimicro intellectual property right relating to any combination, machine, or process in which Vimicro products or services are used. Information published by Vimicro regarding third-party products or services does not constitute a license from Vimicro to use such products or service or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Vimicro under the patents or other intellectual property of Vimicro.

Reproduction of information in Vimicro data books or data sheets is permissible only if preproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. Vimicro is not responsible or liable for such altered documentation.

Resale of Vimicro products or services with statements different from or beyond the parameters stated by Vimicro for that product or service voids all express and any implied warranties for the associated Vimicro product or service and is an unfair and deceptive business practice. Vimicro is not responsible or liable for any such statements.

| Revision Table |      |        |                     |          |  |  |  |  |

|----------------|------|--------|---------------------|----------|--|--|--|--|

| Date           | Rev. | Author | Content of revision | Approval |  |  |  |  |

| 2011-1-20      | 0.10 |        | Original version    | IC team  |  |  |  |  |

| 2011-4-01      | 0.21 |        | Modify version      | Yanghui  |  |  |  |  |

| 2011-5-01      | 0.90 |        | Release Version     |          |  |  |  |  |

# CONTENTS

| 1             | OVER                                                                                                                           | VIEW                                                                                           | 8                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 2             | FEATU                                                                                                                          | JRE DESCRIPTION                                                                                | 10                                                                                             |

|               | 2.1 \$                                                                                                                         | System Block Diagram                                                                           | 10                                                                                             |

|               |                                                                                                                                | lighlight Feature                                                                              |                                                                                                |

|               |                                                                                                                                | CPU Subsystem                                                                                  |                                                                                                |

|               |                                                                                                                                | /lemory Subsystem/ideo Subsystem                                                               |                                                                                                |

|               |                                                                                                                                | Storage Subsystem                                                                              |                                                                                                |

|               |                                                                                                                                | Peripheral Subsystem                                                                           |                                                                                                |

|               |                                                                                                                                | Power Management                                                                               |                                                                                                |

|               | 2.9 F                                                                                                                          | PAD and PAD Control                                                                            | 22                                                                                             |

| 3             | PIN DI                                                                                                                         | ESCRIPTION AND PACKAGE INFO                                                                    | 24                                                                                             |

|               | 3.1 E                                                                                                                          | Ball Map                                                                                       | 24                                                                                             |

|               |                                                                                                                                | Pin description                                                                                |                                                                                                |

|               | 3.3 F                                                                                                                          | Package Information                                                                            | 52                                                                                             |

| _             |                                                                                                                                |                                                                                                | 67                                                                                             |

| 4             | CPU S                                                                                                                          | UBSYSTEM                                                                                       | J/                                                                                             |

| 4             |                                                                                                                                | CORTEX-A8 Features                                                                             |                                                                                                |

| 4             | 4.1 (<br>4.2 (                                                                                                                 | CORTEX-A8 Features<br>Clock and Reset                                                          | 57<br>59                                                                                       |

| 4             | 4.1 (<br>4.2 (<br>4.3                                                                                                          | CORTEX-A8 Features<br>Clock and Reset<br>nterrupt controller                                   | 57<br>59<br>60                                                                                 |

| 4             | 4.1 (<br>4.2 (<br>4.3  <br>4.4 ]                                                                                               | CORTEX-A8 Features<br>Clock and Reset<br>nterrupt controller<br>īmer                           | 57<br>59<br>60<br>61                                                                           |

| •             | 4.1 ()<br>4.2 ()<br>4.3  <br>4.4  <br>4.5 E                                                                                    | CORTEX-A8 Features<br>Clock and Reset<br>nterrupt controller<br>Timer<br>EFUSE                 | 57<br>59<br>60<br>61<br>62                                                                     |

| <b>4</b><br>5 | 4.1 ()<br>4.2 ()<br>4.3  <br>4.4  <br>4.5 E                                                                                    | CORTEX-A8 Features<br>Clock and Reset<br>nterrupt controller<br>Timer<br>EFUSE                 | 57<br>59<br>60<br>61                                                                           |

| •             | 4.1 (<br>4.2 (<br>4.3  <br>4.4  <br>4.5  <br><b>MEMC</b>                                                                       | CORTEX-A8 Features<br>Clock and Reset<br>nterrupt controller<br>Timer<br>EFUSE                 | 57<br>59<br>60<br>61<br>62<br><b>65</b>                                                        |

| •             | 4.1 (<br>4.2 (<br>4.3  <br>4.4  <br>4.5  <br><b>MEMC</b><br>5.1                                                                | CORTEX-A8 Features<br>Clock and Reset<br>nterrupt controller<br>Timer<br>FUSE                  | 57<br>59<br>60<br>61<br>62<br><b>65</b>                                                        |

| •             | 4.1 (<br>4.2 (<br>4.3  <br>4.4  <br>4.5 E<br><b>MEMC</b><br>5.1  <br>5.2 [<br>5.3 ]                                            | CORTEX-A8 Features<br>Clock and Reset<br>Interrupt controller<br>Timer<br>FUSE<br>ORY SUBSYTEM | 57<br>59<br>60<br>61<br>62<br><b>65</b><br>65<br>66<br>67                                      |

| •             | 4.1 (<br>4.2 (<br>4.3  <br>4.4  <br>4.5  <br><b>MEMC</b><br>5.1  <br>5.2  <br>5.3  <br>5.4                                     | CORTEX-A8 Features<br>Clock and Reset<br>Interrupt controller<br>Timer<br>FUSE<br>ORY SUBSYTEM | 57<br>59<br>60<br>61<br>62<br><b>65</b><br>65<br>66<br>67<br>68                                |

| •             | 4.1 (<br>4.2 (<br>4.3  <br>4.4  <br>4.5  <br><b>MEMC</b><br>5.1  <br>5.2  <br>5.3  <br>5.4                                     | CORTEX-A8 Features<br>Clock and Reset<br>Interrupt controller<br>Timer<br>FUSE<br>ORY SUBSYTEM | 57<br>59<br>60<br>61<br>62<br><b>65</b><br>65<br>66<br>67<br>68                                |

| •             | 4.1 (<br>4.2 (<br>4.3  <br>4.4  <br>4.5 E<br><b>MEMC</b><br>5.1  <br>5.2 [<br>5.3 ]<br>5.4 F<br>5.5 [                          | CORTEX-A8 Features<br>Clock and Reset<br>Interrupt controller<br>Timer<br>FUSE<br>ORY SUBSYTEM | 57<br>59<br>60<br>61<br>62<br><b>65</b><br>65<br>66<br>67<br>68<br>68                          |

| 5             | 4.1 (<br>4.2 (<br>4.3  <br>4.4  <br>4.5  <br><b>MEMC</b><br>5.1  <br>5.2  <br>5.3  <br>5.4  <br>5.5  <br><b>VIDEC</b><br>6.1 \ | CORTEX-A8 Features<br>Clock and Reset                                                          | 57<br>59<br>60<br>61<br>62<br><b>65</b><br>65<br>66<br>67<br>68<br>68<br>68<br><b>71</b><br>71 |

|   | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8 | Encoding Features<br>Pre-processing features | 73<br>74<br>75<br>75<br>75<br>77<br>82<br>83<br>83<br>84<br>86<br>87<br>88 |

|---|-----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------|

|   | ט.ט                                           | GPU<br>General Features                      | •                                                                          |

|   |                                               | Full-featured 3D Graphics Pipeline           |                                                                            |

|   |                                               | Full-featured 2D Graphic Pipeline            |                                                                            |

| 7 | ST                                            | ORAGE SUBSYSTEM                              | 95                                                                         |

| 1 |                                               |                                              | 55                                                                         |

|   | 7.1                                           | USB OTG                                      |                                                                            |

|   | 7.2                                           | USB HOST                                     |                                                                            |

|   | 7.3<br>7.4                                    | SDIO Controller<br>NAND Flash Controller     |                                                                            |

|   | 7.5                                           | SPI (Serial Peripheral Interface)            |                                                                            |

| 0 |                                               |                                              |                                                                            |

| 8 | PE                                            | RIPHERAL SUBSYSTEM1                          | UΖ                                                                         |

|   | 8.1                                           | Audio Module 1                               |                                                                            |

|   | 8.2                                           | UART                                         |                                                                            |

|   | 8.3                                           | IIC Module 1                                 |                                                                            |

|   | 8.4<br>8.5                                    | PWM                                          |                                                                            |

|   | 8.6                                           | Touch Panel Interface                        |                                                                            |

| 9 | FU                                            | ECTRICAL PARAMETERS AND TIMING1              | na                                                                         |

| 5 |                                               |                                              | 55                                                                         |

|   | 9.1                                           | Absolute Maximum Ratings 1                   |                                                                            |

|   | 9.2                                           | Recommended Operating Conditions             |                                                                            |

|   | 9.3                                           | DC Characteristics                           |                                                                            |

|   |                                               | Standard Digital IO                          |                                                                            |

|   |                                               |                                              |                                                                            |

| MEMORY IO                       | 114                                                                                                                                                                                                                                                                                     |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Analog IO                   |                                                                                                                                                                                                                                                                                         |

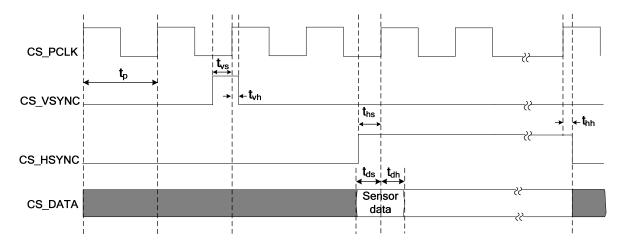

| CIF Interface Timing            |                                                                                                                                                                                                                                                                                         |

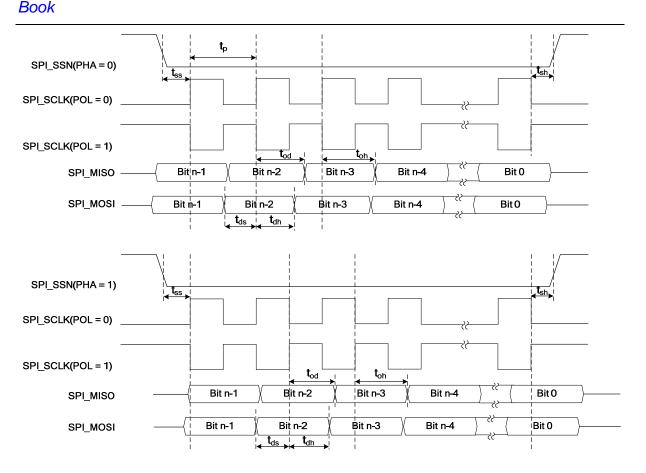

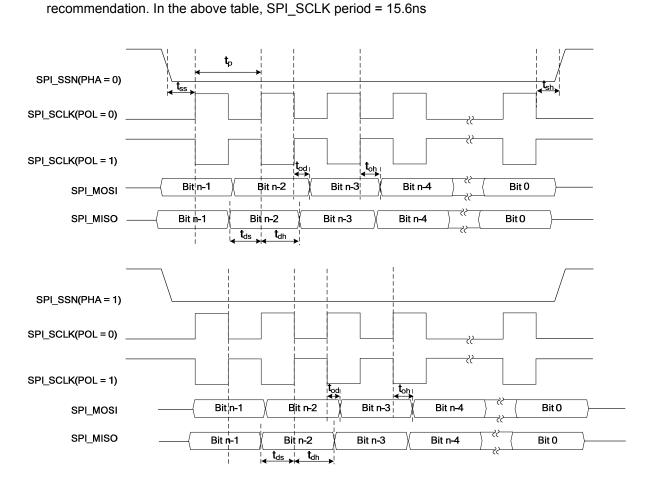

| SPI Interface Timing            | 117                                                                                                                                                                                                                                                                                     |

| SPI in Slave Mode               |                                                                                                                                                                                                                                                                                         |

| SPI in Master Mode              |                                                                                                                                                                                                                                                                                         |

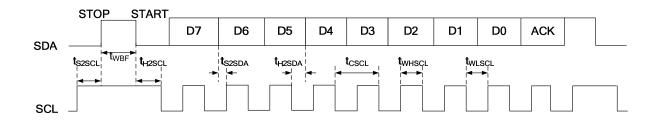

| I2C Interface Timing            | 119                                                                                                                                                                                                                                                                                     |

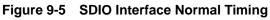

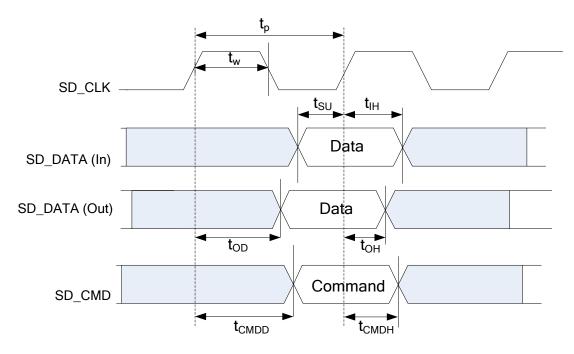

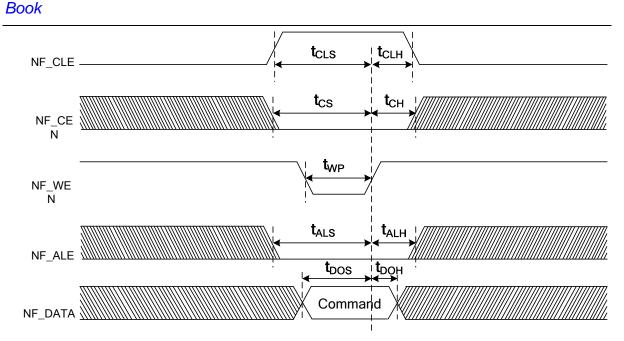

| SDIO Interface Timing           | 121                                                                                                                                                                                                                                                                                     |

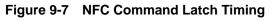

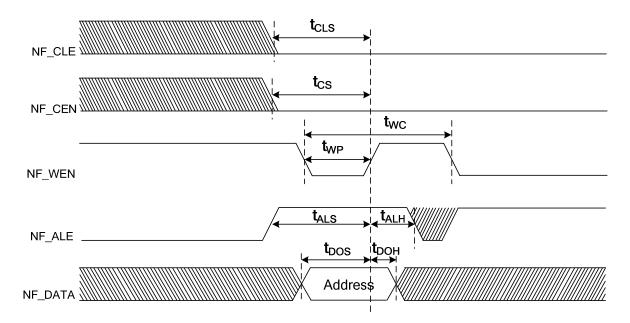

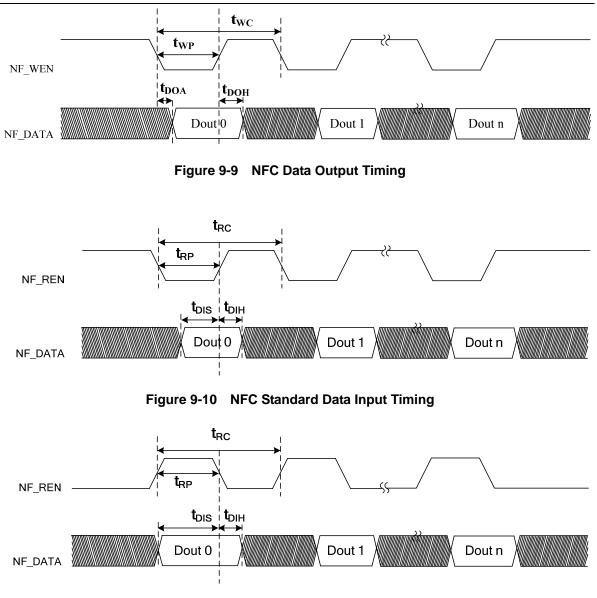

| NFC Interface Timing            | 123                                                                                                                                                                                                                                                                                     |

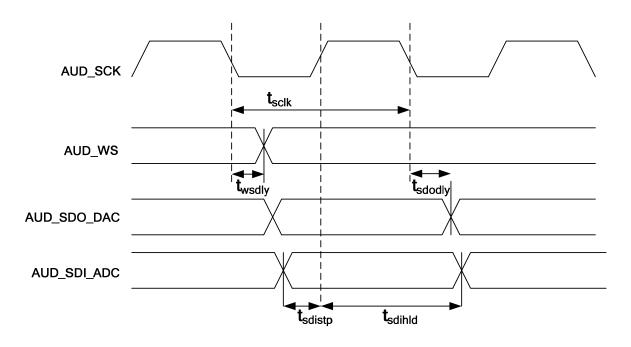

| AUD Interface Timing            | 126                                                                                                                                                                                                                                                                                     |

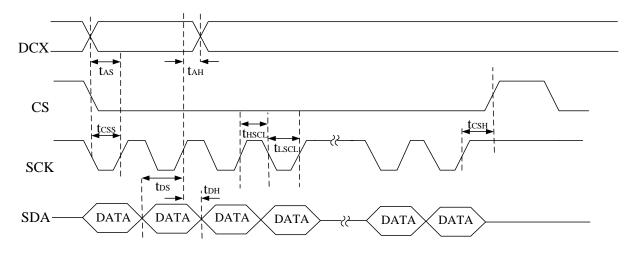

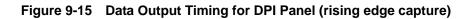

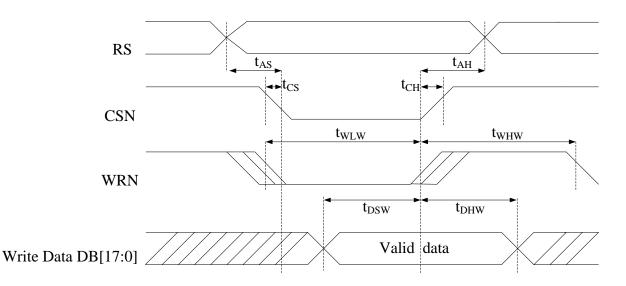

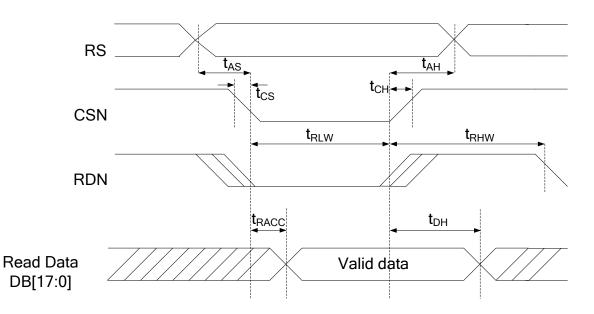

| D LCD Interface Timing          | 127                                                                                                                                                                                                                                                                                     |

| LCD Serial Interface            | 127                                                                                                                                                                                                                                                                                     |

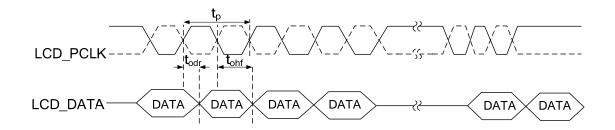

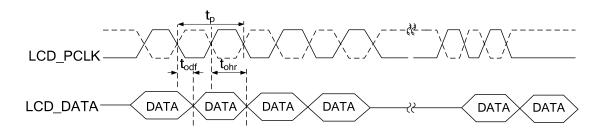

| Data Output for DPI Panel       | 128                                                                                                                                                                                                                                                                                     |

| Interface Timing with DBI Panel | 129                                                                                                                                                                                                                                                                                     |

|                                 | USB Analog IO<br>CIF Interface Timing<br>SPI Interface Timing<br>SPI in Slave Mode<br>SPI in Master Mode<br>I2C Interface Timing<br>SDIO Interface Timing<br>NFC Interface Timing<br>AUD Interface Timing<br>CLCD Interface Timing<br>LCD Serial Interface<br>Data Output for DPI Panel |

VC0882 Data Book

# Chapter 01

# **Overview**

Vimicro Copyright© 1999-2011

Page 7 of 131

# **1 Overview**

The Vimicro VC0882, is a high performance, low power, multimedia application and high integrated system-on-chip (SOC) targeted at Application Processor (AP) of Tablet PC and Smart Phone. It is implemented on TSMC 65nm low power process technology.

The embedded microprocessor in VC0882 is based on 1.3Ghz ARM Cortex-A8 with NEON coprocessor. Also it is integrated with the high performance video decoder up to 1080P with 30fps for H.264, H.263, RMVB, MPEG4, MPEG2,VC1 etc. And it can support H.264, MPEG4, H.263 video encoder up to 30fps for 720p.

VC0882 is embedded for 2D and 3D graphic acceleration processor (GPU) to support display and gaming. This GPU delivers the scalable ultra-threaded unified shader architecture up to 15MTriangle rate per second. Also it supports the industry standard API such as Open GL ES1.1 and 2.0, Open VG1.0

Camera interface supports multiple formats from parallel sensors, ccir656 interface and raw image data. Display engine can deal with overlay of 4 display layers plus background and HW cursors. The video subsystem also supports SDTV and HDTV with 10-bit 3-channel 250Mhz analog Video DAC output. 24 bits LCD interface is applied with most of post processing and 1920x1080 maximum display sizes for all of panels and HDMI Bridge. It also supports the face detection function through the cooperation of hardware and software.

VC0882 can support most of high-level operation systems such as Android OS and Linux. And it integrates the state-of-the-art power management technologies for dynamic voltage control with multi power domains.

Integrated DDR controller can be compatible to external LPDDR, DDR2 and DDR3 with the data rates up to 667Mb/s. It supports 6 high performance and low power PLLs for flexible clock switch. VC0882 includes 3 SDIO/MMC card interfaces and 8bits/16bits NAND Flash with ECC, 2 PWMs, 3 UART interfaces, 2 SPI controller interfaces. One USB OTG 2.0 and one USB Host 2.0 can implement the data transfer between SOC and PC. Also, VC0882 contains the embedded 10-bit SAR ADC with 4-wire touch panel interface and carries one high quality 24-bit stereo ADC and DAC for audio processing. It can support the EFUSE function to program electrical fuse IP.

VC0882 Data Book

# Chapter 02

# Feature Description

# **2 Feature Description**

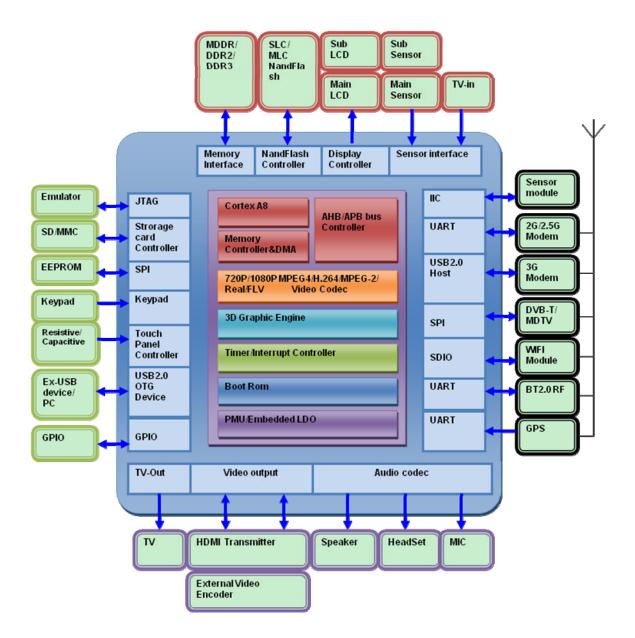

# 2.1 System Block Diagram

Figure 2-1 System Diagram of 445BGA

# 2.2 Highlight Feature

- Embedded up to 1.3Ghz ARM CORTEX-A8 CPU with v7-A instruction set

- Embedded up to 720p H.264, MPEG-4, H-263 video encoder with 30fps

- Embedded up to 1080p H.264, SVC, MPEG-4, MPEG-2, MPEG-1, H.263, VC-1, JPEG, RV, VP6 and DivX video decoder with 30fps

- Embedded with graphic 3D engine for compliant with the OpenGL ES 2.0; OpenGL ES1.1; OpenVG 1.1

- Embedded with Data rates of up to 667 Mb/s (333 MHz) for LPDDR, DDR2 and DDR3

- Embedded 6 PLLs for flexible clock switch

- Support parallel cameral sensor interface with max 4Kx4K resolution

- Support LCD interface for DBI, DPI and HDMI bridge

- Support NTSC and PAL SDTV and YPbPr analog signals output on 480i /480p /576i /576p /720p /1080i /1080p systems

- Embedded 8 bit/16 bit NAND Flash controller with up to 48 bits ECC

- Supports 4 SDIO devices

- One USB host and one USB OTG compliant with USB2.0 specification

- Contains a high-quality 24-bit audio stereo ADC and a high-quality 24-bit stereo DAC

- Support Touch Panel Interface with10-bit SAR ADC: DNL  $\pm\,1$  LSB, INL  $\pm\,2$  LSB

- Embedded with multi-power domains and smart DVFS scheme

- Power consumption value: 108mW for audio playing, 183mW for screen display, 630mW for 1080P player and 800uW for sleep mode

# 2.3 CPU Subsystem

- Embedded ARM CORTEX-A8

- Full implementation of the ARM architecture v7-A instruction set

- 64-bit high-speed Advanced Microprocessor Bus

- Programmable CPU frequency up to 1.3Ghz for typical case

- memory interface supporting multiple outstanding transactions

- A pipeline for executing ARM integer instructions

- A NEON pipeline for executing Advanced SIMD and VFP instruction sets

- Dynamic branch prediction with branch target address cache, global history buffer, and 8-entry return stack

- Memory Management Unit (MMU) and separate instruction and data Translation

- Look-aside Buffers (TLBs) of 32 entries each

- Level 1 32KB instruction cache and 32KB data caches

- Level 2 128KB cache

- Level 2 cache with parity and Error Correction Code (ECC) configuration option

- Embedded Trace Macrocell (ETM) support for non-invasive debug

- Static and dynamic power management including Intelligent Energy Management (IEM)

- ARMv7 debug with watch point and breakpoint registers and a 32-bit Advanced

- Peripheral Bus (APB) slave interface to a CoreSight debug system.

- Interrupt Controller

- Hierarchical interrupt scheme which process 1<sup>st</sup> level interrupts in Interrupt Controller while handling 2<sup>nd</sup> level interrupt in the associated sub-modules

- Support both FIQ and IRQ

- Support up to 32 interrupts

- Using interrupt source based MASK scheme and source pending registers to avoid losing interrupts

- Programmable interrupt prioritization

#### Timers

- 3 general purpose timers, 4 dual timers and 1 watchdog timer

- Programmable timer period and timer operation mode

- Individual interrupt for each timer

- Unique 24MHz clock for all timer

- CLOCK & RST

- Supports 1 oscillator (or crystal): 26 MHz XCLK

- Embeds 6 high performance, low power PLLs

- Includes configurable clock dividers to produce desired clock frequencies

- Implements clock gating technology to save power

- Inserts clock multiplexers to enhance flexibility

- Seamlessly dynamic clock switching between XCLK and all 6 PLLs

- Integrates pmu hardware reset, watchdog reset, global software reset and each module's individual software reset

- Inserts clock multiplexers to enhance flexibility

- EFUSE

- Support to manage the electrical fuse IP by APB bus in normal mode or by

PAD on ATE test mode

- Embedded power switch

- Support to program to 1 bit at a time according to the configured address

- Software can read 1-8 bytes at a time according to configured address and configured read byte length

- Provide power down and standby mode

- Asynchronous signal interface

# 2.4 Memory Subsystem

- DDR controller

- Compatible with JEDEC standard LPDDR, DDR2, DDR3

- Data rates of up to 667 Mb/s (333 MHz)

- Compatible with the AMBA 3 AXI protocol

- Compatible with the AMBA 3 APB protocol

- Supported AXI burst type: incremental and wrap

- Register programmable timing parameters support DDR2/DDR3/LPDDR1 components from DRAM various vendors

- Support LPDDR1/DDR2 read/write command interrupt access

- Advanced features such ODT, ZQ Calibration and *additive latency*

- Support for two CSs (chip select) with shared clock pins, command pins, address pins and data pins

- Support for DDR device density ranging from 64Mbit to 2Gbit

- Support 16bit/32bit LPDDR1/DDR2/DDR3 device

- Supports autonomous DDR power down entry and exit based on programmable idle periods

- Support for self refresh entry on software command and automatic exit on DRAM access command arrival

- Automated Read DQS recognition and Automated Dynamic DQS Drift Compensation

- Built-in DQS Gate Training

- Support DDR3 DLL-off Mode

- Support LPDDR1 Deep Power Down Mode

- DMA Controller

- Compliance to the AMBA 3.0 Specification---AXI protocol for integration into SoC implementation.

- One DMA channel which can support unidirectional transfer for software request

- Support memory-to-memory transfers

- Support Software link list descriptor-based DMA transfers

- Support programming max burst length

- SRAM Controller

- Embedded 32Kbyte SRAM in chip

- Supports 14 bit address and 16 bit data

- Acts as single-port SRAM for test program and as dual-port SRAM

- ROM Controller

- Embedded with 64Kbyte ROM

- Supports with 14 bit address and 64 bit data

- For system boot only

## 2.5 Video Subsystem

- Camera Interface

- Support master type sensor module and 8-bit parallel data output from sensor

- Support two camera sensors (only one works at the same time)

- Support max sensor resolution: 4096x4096 and 100Mhz max pixel clock

- Support max output image size (to memory): 4096x4096

- Support parallel interface for SYNC mode or ITU-R BT656 mode

- Support YCbCr422-format data/RAW image data/JPEG compressed data/RGB data (Bypass post-processing for RAW data/JPEG data/RGB data)

- Support two post-processing paths for capture and display

- Support up-scaling and down-scaling for capture path/preview path

- Capture path support slice mode and frame mode

- Support auto-focus

- Special Effect

- o Mono color

- o Sepia

- o Special color

- o Negative

- o Four blocks

- o Grid color

- Display Engine

- Support 4 display layers plus background and HW cursor

- Support HW cursor with max resolution 64x64

- Using Pipeline architecture to implement overlay & alpha-blending operation

- Support up-scaling for overlay pixel data up to 1920x1080

- Support brightness/contrast/hue/saturation adjustment

- Support programmable gamma correction

- Support dithering for less than 24-bit color display

- Provide capture path to implement the function as "capture with frame"

- Max panel resolution: 1600x1200 for TV/1920x1080 for LCD panel and Max pixel rate up to 162MHz

- Support BT601 and BT609 color domain

- Programmable bits-per-pixel when output to LCDIF module: 16/18/24-bpp such as YUV422, RGB565, RGB666, RGB888, and etc.

- Support programmable multi-cycle output mode: 1/2/3/4 cycles per pixel

- Face Detection

- Includes the calculation of integral and LAB (Locally Assembled Binary) in hardware and some functions implemented by software

- Support maximum sizer image width is 320 pixels, height is 240 pixels, minimum sizer image width is 24 pixels, height is 24 pixels and no limitation for original image size

- About process 5~10 QVGA frames in a second

- Support detection of smile faces, but not wink faces and report the eyes position.

- Support the face in profile angle is -20 ~ 20 degrees, pitching angle is -30 ~ 30 degrees.

- Support detection of black skin faces, color eyes and white hair

- Video Encoder

- Supports H.264 baseline Levels 1-3.1, I-Slice and P-Slice CAVLC encoding, contained intra prediction, image size up to 1280x1024

- Supports MPEG-4 Levels 1-5, I-VOP and P-VOP, Max MV range +-16 pixels, image size up to 1280x1024

- Supports H.263 Profile 0 Level 10-70

- Supports JPEG baseline image size up to 4672x3504

- Supports cropping and rotation (90 or 270 degrees) functions

- Video Decoder

- Supports to decode H.264, SVC, MPEG-4, MPEG-2, MPEG-1, H.263, VC-1, JPEG, RV, VP6 and DivX profile and level for up to 1920x1080

- Supports most of post-processing, up-scaling, down-scaling, dithering, alpha-blending, color conversion, de-interlacing.

- Also supports contrast, brightness, saturation, cropping, digital zoom, picture in picture, image rotation etc.

- 3D Graphic Engine

- OpenGL ES 2.0 compliant, including extensions; OpenGL ES1.1; OpenVG 1.1

- IEEE 32-bit floating-point pipeline supports long shader instructions (maximum 256 instruction)

- Up to 256 threads per shader

- Up to 16 programmable Scalable Ultra-threaded, unified vertex and pixel shaders

- FSAA mechanisms: MSAA 4x, high quality FSAA 16x

- Vertex processing supported format: BYTE, UBYTE, SHORT, USHORT, INT, UINT, DEC, UDEC, FLOAT, FLOAT16, D3DCOLOR, FIXED16DOT16

- Up to 8 programmable elements per vertex

- Dependent texture operation with high-performance

- Alpha blending

- Support for 4 vertex shader and 8 pixel shader simultaneous textures

- 2D Graphic Engine

- Bit blit, stretch blit, pattern blit and fast clear

- Line drawing and Rectangle fill and clear

- Mono expansion for text rendering

- Anti-aliased font support

- ROP2, ROP3, ROP4

- Alpha blending

- 90/180/270 degree rotation and Vertical and Horizontal mirror

- Transparency by monochrome mask, chroma key or pattern mask

- High quality 9-tap filter for scaling

- 32K x 32K coordinate system

- Color space conversion between YUV and RGB for both BT709 and BT601

- Clipping window

- Color Index Input conversion Support

- Filter Blit

- Input Formats: (Only Filter Blit support YUV input)

- A1R5G5B5

- A4R4G4B4

- A8R8G8B8

- X1R5G5B5

- X4R4G4B4

- X8R8G8B8

- RGB565

- NV12 (semi-planer YUV420)

- NV16 (semi-planer YUV422)

- YUY2(package YUV422)

- UYVY(package YUV422)

- YV12(planer YUV420)

- 8-bit color index

- 1-bit monochrome

- The output data Formats:

- A1R5G5B5

- A4R4G4B4

- A8R8G8B8

- X1R5G5B5

- X4R4G4B4

- X8R8G8B8

- RGB565

- LCD Interface

- Supports Display Bus Interface (DBI) output mode, compliant to the MIPI Alliance Display Bus Interface protocol v2.0

- Supports accessing (including writing and reading) in through mode

- Supports dual LCD panels work at different time(DBI & DBI, DBI&DPI)

- Supports up to 24 bits per pixel (BPP)

- Display size programmable up to 1080p(1920\*1080) with configured interlaced or progressed mode

- Supports Display Pixel Interface (DPI) output mode, compliant to the MIPI Alliance Display Pixel Interface protocol V2.0

- Display size programmable up to 1080p(1920 x1080) with configured interlaced or progressed mode;

- Support for 12 & 16&18BPP&24BPP modes for RGB parallel output format (RGB444, RGB565, RGB666, RGB888);

- Support programmable pixel clock and asynchronous reset signal ;

- Support flexible 3-wire and 4-wire serial interface(including write operation and read operation of panel registers)

- Support parallel dpi interface with up to 24 bits interface;

- Support CCIR656 interface (PAL mode and NTSC mode, 8 bit interface only);

- Support CCIR601 interface.

- Support UPS051&UPS052 interface (8 bit interface only).

- Support 24BPP modes for UPS051&UPS052 interface.

VC0882 Data Book

- Support 16BPP modes for CCIR656 and 24BPP modes for CCIR601.

- Programmable 24-bit/18-bit/16-bit/12-bit/8-bit digital output interface

- Supports various RGB format (RGB888, RGB565, RGB666, RGB555), YUV format (YUV444, YUV422) with 1X, 2X, 3X, 4X multiplexed output.

- Support Max pixel rate up to 150MHz in DPI mode

- TV Encoder

- Support NTSC-M/J/4.43 and PAL- /B/D/G/H/M/N/I/Nc SDTV Composite signal (480i/576i) output.

- Support YPbPr analog signals output on 480i /480p /576i /576p /720p /1080i /1080p systems

- Embedded with 10 bits Video DAC for analog signal output

# 2.6 Storage Subsystem

- NAND Flash Controller

- Compliant to open NAND Flash Interface (ONFI) 1.0 Specification

- Hardware BCH (Bose, Chaudhuri & Hocquenghem Type of code) encoder and decoder are included

- Error detection/correction capability of 4/8/16 bits per 512 bytes

- Error detection/correction capability of 24/32/40/48 bits per 1024 bytes

- 8-bit parallel architecture and calculation based on 1-bit length

- Support SLC, MLC and TLC NAND flash

- Support interlaced storage of ECC and user data

- Support Asynchronous Interface Bus Operation, Clock Frequency 50M for 8-bit interface and Clock Frequency 100M for 16-bit interface

- Support booting from NAND flash with built-in bootloader

#### SDIO Host

- Supports 3 SD IO devices

- Compatible with SD Memory Card Spec 2.0 and supports SDHC up to 32GB card

- Compatible with SDIO Card Spec 2.0

- Compatible with JESD84-A43 standard (MMC 4.3), up to 8-bit data bus

- Support for SD Memory, SDIO, SD Combo, miniSD, MMC, MMC plus, MMC RS and Trans-Flash cards

- Support dual voltage cards typically operating at 1.8V and 3.3V

- Support programmable protocol bus clock for different cards, up to 52MHz

- USB Host

- High-speed single-port USB host controller. Support one USB downstream port.

- Fully compliant with the USB 2.0 specification, Enhanced Host Controller Interface (EHCI) Specification, Revision 1.0, and the Open Host Controller Interface (OHCI) Specification Release 1.0a.

- Supports high-speed, 480-Mbps transfers using an EHCI Host Controller, as well as full and low speeds through one integrated OHCI Host Controllers.

- The supported peripherals are determined by OS software.

- Also supported: USB-HDD, USB-DVDRW, USB Mouse, USB Keyboard, USB Modem.

- USB OTG

- USB 2.0 high-speed dual-role controller:

- Operates either as the host/peripheral in point-to-point communications with another USB function or as a function controller for a USB peripheral

- Complies with the USB 2.0 standard for high-speed (480 Mbps) functions and with the On-The-Go supplement to the USB 2.0 specification

- Supports point-to-point communications with one high-, full- or low-speed device

# 2.7 Peripheral Subsystem

- PWM

- Supports up to 2 channels

- The pulse ratio of the output waveform ranges from 0/256 to 255/256 The frequency of the output waveform ranges from 6KHz to 12MHz

- UART

- Support 3 UART controllers.

- Functional compatible with the 16550A

- Full-duplex operation.

- Fully programmable serial interface, Data bit: 7-bit or 8-bit, Parity bit: None, Even, Odd, or Stick check, Stop bit: 1-bit or 2-bit.

- Break condition detection and generation.

- Programmable integer and fractional divisor for baud rate generation.

- Programmable Baud rate computation method support up to 12Mbps baud rate.

- Loop-back mode for self test.

- Slow infrared asynchronous interface that conforms to the Infrared Data Association (IrDA) specification.

- Modem control functions with DSR, DCD, RI and DTR signals.

- SPI

- Support 2 SPI controllers;

- Provide master/slave modes selectable by control registers;

- Full duplex synchronous serial data transfer;

- The max transfer speed in master mode is 54MHz

- The max transfer speed in slave mode is 27MHz

- I2C

- Master mode only

- Compliant to Philips I2C-Bus Specification v2.1

- Supports for standard mode (up to 100Kbps) and fast mode (up top 400Kbps)

- Support 7-bit and 10-bit device addressing modes

- Max transfer length of each transaction is 65535 for read or write operation

- Arbitration lost detection and bus busy detection

- Touch Panel Interface

- Master mode only

- Embedded 10-bit SAR ADC: DNL  $\pm$  1 LSB, INL  $\pm$  2 LSB

- Support control function of resistive 4-wire touch panel

- Support pen down detect

- Support 4-channel analog input measurement

- multi-touch supported in Software including zoom in & out and rotation

- Audio Codec

- Master mode only

- Contains a high-quality 24-bit stereo ADC and a high-quality 24-bit stereo DAC

- Provides 6 mono differential line inputs with boost gain stage (0/4/8/12/16/20 dB), they can be used either for line in or microphone in application

- Provides 1 stereo single-end 16/32 Ohm headphone output

- Provides 2 mono differential line output that but can't be driven simultaneously

- Provides 1 mono differential BTL 16/32 Ohm receiver output

- Provides a stereo differential speaker output and one of them can also be configured to the mono differential BTL 8 ohm output

- Provides 2 microphone bias output

- Supports audio sampling rates (Fs) from 8KHz to 96KHz (88.2KHz not supported)

- Supports the Automatic Gain Control (AGC) function to better sound recording performances

- Provides 2 I2S/PCM Interfaces of master mode through VC0882 PADs, so as

to connect external devices of slave mode

- Includes two 32-bit stereo digital mixer (produce Y = A + B result)

- Supports 6 memory formats of audio raw data: Stereo-32bit, Stereo-16bit, Stereo-8bit, Mono-32bit, Mono-16bit, and Mono-8bit

## 2.8 Power Management

- Robust power on/off control and sequence

- AP Software is allowed to control variable voltage output of abundant power supply devices in PMIC via I2C interface.

- AP is partitioned into multi power domains to allow power off of inactive domains and down-scaling of supply voltage when the domain can work with low frequency.

- AP is divided into two Power domains: PMU (always-on domain) & PSO (shut-off domain). PMU power domain includes PMU logic and all digital IO domains. These digital IO should be powered on/off with PMU logic power at the same time, including DDR memory IO. PSO power domain is divided into four voltage domains to support individual power on/off control, down/up scaling of voltage level for each voltage domain depending on applications. These four voltage domains are ARM, GPU, Video Codec, Other Core. Each voltage domain has its own supply from PMIC with variable voltage output.

| Power  | POWER | NORMAL | IDLE     | HALT     | SLEEP |

|--------|-------|--------|----------|----------|-------|

| modes  | OFF   |        |          |          |       |

| PMU    | Off   | On     | On       | On       | On    |

| domain |       |        |          |          |       |

| PSO    | Off   | On     | On       | On       | Off   |

| domain |       |        | with ARM | With all |       |

|        |       |        | clock    | module   |       |

|        |       |        | gating   | clock    |       |

|        |       |        |          | gating   |       |

- AP has the following power modes to support low power design.

- Static and dynamic clock gating to decrease dynamic power consumption in AP chip.

- Seamless clock switch to support low power mode in AP chip.

- DVFS(Dynamic Voltage & Frequency Scaling) Technology allows adaptive down/up scaling of clock frequency and voltage level inside one scenario or between scenarios to reduce further dynamic power and also leakage power consumption. Temperature & Process change can also be compensated for by

hardware.

# 2.9 PAD and PAD Control

- Support 1.7v ~ 3.6v normal digital I/O

- Support 2.4v ~ 3.6v normal analog I/O and 5v special analog I/O

- Support 1.4v ~ 1.9v high-speed MDDR/DDR2/DDR3 I/O

- 4mA/8mA/12mA/16mA drive strength of I/O

- Schmitt trigger input for special signals such as clock, reset

- 16bit strap pins for Software

- Up to 59 GPIO interrupt controllers and 8 Hardware interrupt controllers

- Multi IO power domain to support connecting to external devices with different voltage supply

VC0882 Data Book

# Chapter 03

# Pin Description And Package information

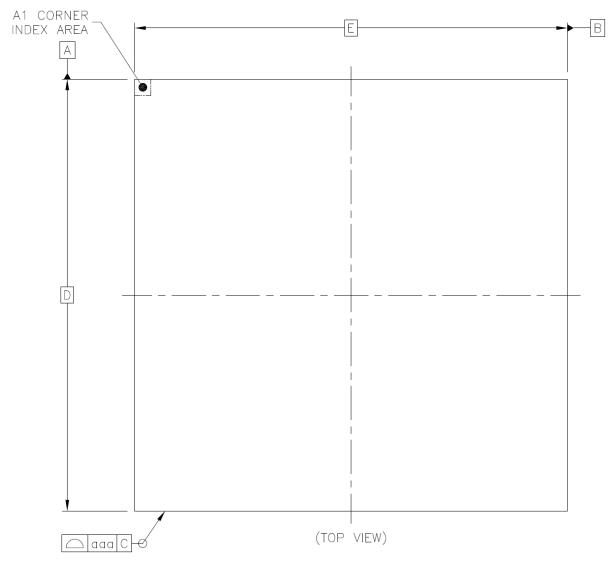

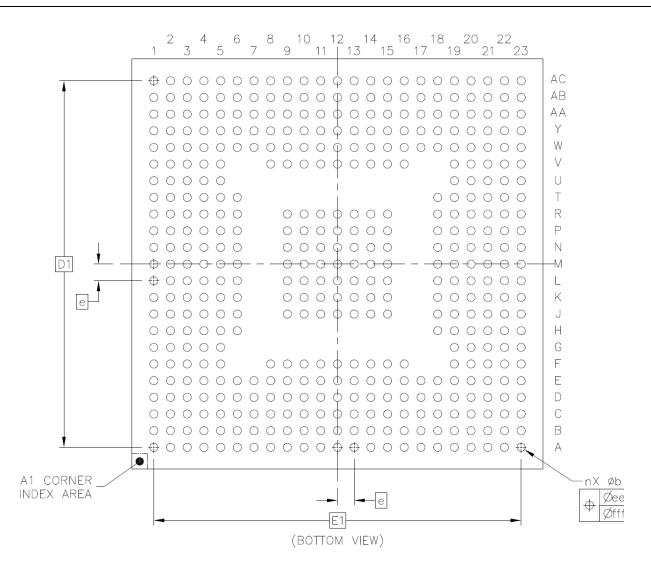

# 3.1 Ball Map

中星微 IMICRO

|                  | 1            | 2          | 3        | 4       | 5      | 6      | 7        | 8       | 9       | 10      | 11     |

|------------------|--------------|------------|----------|---------|--------|--------|----------|---------|---------|---------|--------|

|                  | DDR_DQS      | DDR_DQ     |          | DDR_DQ  | DDR_DQ | DDR_DQ | SPI0_MIS | SPI0_SC |         | KEYPAD  | KEYPA  |

| Α                | _INV0        | M1         | DDR_DQ10 | 8       | 2      | 0      | 0        | LK      | KEYPAD1 | 0       | D2     |

| _                | DDR_DQ       | DDR_DQ     |          | DDR_DQ  | DDR_DQ | DDR_DQ | SPI0_MO  | SPI0_SS | UART1_S | KEYPAD  | KEYPA  |

| В                | M0           | <b>S</b> 0 | DDR_DQ13 | 15      | 5      | 7      | SI       | 0N      | DO      | 3       | D6     |

| ~                | DDR_DQS      | DDR_DQ     | AUD1_SD  | UART0_S | UART1_ | UART1_ | UART1_   | UART1_  |         | KEYPAD  | KEYPA  |

| С                | _INV1        | <b>S</b> 1 | O_DAC    | DO      | DCDN   | DSRN   | CTSN     | SDI     | KEYPAD4 | 7       | D11    |

| P                | DDR_DQ1      | DDR_DQ     | AUD1_SDI | AUD1_W  | UART0_ | UART1_ | UART1_   | UART1_  | VEVDAD5 | KEYPAD  | KEYPA  |

| D                | 2            | 11         | _ADC     | S       | SDI    | RIN    | DTRN     | RTSN    | KEYPAD5 | 9       | D12    |

| Б                | DDR_DQ1      | DDR_DQ     | VDD_IO_D | VDD_IO_ | AUD1_S | PWM0   | PWM1     | VSS     | VSS     | VSSA_PL | VSSA_P |

| E                | 4            | 9          | DR       | DDR     | СК     | PWM0   | PWMI     | V 3 3   | V 33    | L12_1   | LL12_3 |

| F                |              | DDR_DQ     | VDD_IO_D | VDD_IO_ | VDD_CO |        |          | AUD0_S  | AUD0_WS | AUD0_SD | AUD0_S |

| F                | DDR_DQ4      | 6          | DR       | DDR     | RE_PMU |        |          | DI_ADC  | AUD0_wS | O_DAC   | СК     |

| G                | DDR DQ1      | DDR_DQ     | VSS      | VSS     | DDR_VR |        |          |         |         |         |        |

| G                | DDK_DQ1      | 3          | V 33     | V 33    | EF     |        |          |         |         |         |        |

| н                | DDR_A3       | DDR_A5     | VSS      | VSS     | VSS    | DDR_ZQ |          |         |         |         |        |

| J                | DDR_RST      | DDR_A7     | VSS      | VSS     | VSS    | DDR_OD |          |         | VSS     | VSS     | VSS    |

| J                | Ν            | DDR_A/     | V 33     | V 33    | 100    | Т0     |          |         | v 33    | 122     | v 33   |

| к                | DDR A13      | DDR_A9     | VSS      | VSS     | VSS    | DDR_BA |          |         | VSS     | VSS     | VSS    |

| K                | DDR_A15      | DDR_A9     | V 33     | 133     | *35    | 0      |          |         | v 35    | 133     | 133    |

| L                | DDR_A0       | DDR_A2     | VSS      | VSS     | VSS    | DDR_CS |          |         | VSS     | VSS     | VSS    |

| L                | DDR_N0       | DDR_R2     | 100      | 100     | 100    | 0N     |          |         | 100     | 100     | 100    |

| м                | DDR CLK      | DDR_CL     | VSS      | VSS     | VSS    | DDR_CK |          |         | VSS     | VSS     | VSS    |

|                  | DDR_CER      | K_INV      | 155      | 100     | 155    | E0     |          |         | 155     |         |        |

| $\sum_{i=1}^{n}$ |              |            |          |         |        |        |          |         |         |         |        |

|                  |              |            |          |         |        |        |          |         |         |         |        |

|                  |              |            |          |         |        |        |          |         |         |         |        |

| /                |              |            |          |         |        |        |          |         |         |         |        |

|                  | $\mathbf{N}$ |            |          |         |        |        |          |         |         |         |        |

Figure 3-1 Pin Allocation of 445BGA (left-top)

| N   | DDR_A      | DDR_A  | VSS     | VSS     | VSS      | DDR_RA  |            |                  | VSS          | VSS    | VSS     |

|-----|------------|--------|---------|---------|----------|---------|------------|------------------|--------------|--------|---------|

| IN  | 1          | 12     | v 33    | v 33    | 133      | SN      |            |                  | v 33         | v 33   | v 33    |

| Р   | DDR_A      | DDR_A  | VSS     | VSS     | VSS      | DDR_CA  |            |                  | VSS          | VSS    | VSS     |

| •   | 11         | 10     | 100     | 100     | 155      | SN      |            |                  | 100          | 100    | 100     |

| R   | DDR_A      | DDR_B  | VSS     | VSS     | VSS      | DDR_WE  |            |                  | VSSA_AU      | VSSA_A | VSSA_A  |

| n – | 4          | A1     |         | 155     | 100      | Ν       |            |                  | D_PA         | UD_PA  | UD      |

| т   | DDR_A      | DDR_A  | VDD_IO_ | VDD_IO_ | VSS      | DDR_BA  |            |                  |              |        |         |

|     | 8          | 6      | DDR     | DDR     |          | 2       |            |                  |              |        |         |

| U   | DDR_D      | DDR_D  | VDD_IO_ | VDD_IO_ | DDR_ODT1 |         |            |                  |              |        |         |

|     | Q23        | Q21    | DDR     | DDR     | _        |         |            |                  |              |        |         |

|     | DDR_D      | DDR_D  | VDD_CO  | VDD_COR |          |         |            | AUDC_S           | AUDC_SP      | AUDC_  | USBOTG  |

| V   | Q16        | Q18    | RE_GPU  | E_GPU   | DDR_CKE1 |         |            | PKOUTL           | KOUTL_       | MICBIA | _RREFEX |

|     | -          | ,      | _       | _       |          |         |            | _P               | N            | S1     | Т       |

|     | DDR_D      | DDR_D  | DDR_CS1 |         |          | VSSA_A  | VSSA_A     | AUDC_S           | AUDC_SP      | VSSA_A | VSSA_A  |

| W   | Q27        | Q29    | Ν       | DDR_A14 | DDR_A15  | UD      | UD_PA      | PKOUTL           | KOUTL_       | UD     | UD      |

|     |            |        |         |         |          |         |            | _P               | N            |        |         |

| Y   | DDR_D      | DDR_D  | VDD_CO  | VDDA_A  | VDDA_AU  | AUDC_LI | AUDC_L     | AUDC_S<br>PKOUTR | AUDC_H       | AUDC_V | USBOTG  |

| I   | Q25        | Q31    | RE_PMU  | UD_RCV  | D_OPA    | NER2_P  | INER1_N    | _N               | SOUTR        | CAP    | _VBUS   |

|     |            |        |         |         |          | VDDA_A  |            | AUDC_S           |              |        | VDDA_U  |

| AA  | DDR_D      | DDR_D  | VDD_CO  | VDDA_A  | VDDA_AU  | UD_VOU  | AUDC_L     | PKOUTR           | AUDC_H       | VDDA_  | SBHOST3 |

|     | QS2        | QM3    | RE_PMU  | UD_VIN  | D_OPA    | т       | INER1_P    | _P               | SOUTL        | AUD_HP | 3       |

|     | DDR_D      |        |         |         |          |         | AUDC_R     |                  | AUDC_LI      |        |         |

| AB  | <br>QS_INV | DDR_D  | DDR_DQ2 | DDR_DQ3 | DDR_DQ19 | DDR_DQ  | <br>CVOUT_ | AUDC_LI          | _<br>NEOUT1_ | USBOTG | USBHOS  |

|     | 2          | QM2    | 8       | 0       | -        | 22      | Р          | NEL1_P           | Ν            | _DPLUS | T_DPLUS |

|     |            | DDR_D  |         |         |          |         | AUDC_R     |                  | AUDC_LI      | USBOTG | USBHOS  |

| AC  | DDR_D      | QS_INV | DDR_DQ2 | DDR_DQ2 | DDR_DQ20 | DDR_DQ  | CVOUT_     | AUDC_LI          | NEOUT1_      | _DMINU | T_DMIN  |

|     | QS3        | 3      | 4       | 6       |          | 17      | Ν          | NEL1_N           | Р            | S      | US      |

|     | 1          | 2      | 3       | 4       | 5        | 6       | 7          | 8                | 9            | 10     | 11      |

| 12                   | 13                   | 14                   | 15                   | 16                   | 17                | 18                     | 19               | 20               | 21                   | 22            | 23            |   |

|----------------------|----------------------|----------------------|----------------------|----------------------|-------------------|------------------------|------------------|------------------|----------------------|---------------|---------------|---|

| KEYPA<br>D8          | I2C_SCK<br>0         | X32K_O<br>UT0        | X32K_IN              | XCLKO<br>UT          | XCLK<br>IN        | NF_CLE                 | NF_DAT<br>A2     | NF_DAT<br>A8     | NF_CE<br>N2          | NF_DAT<br>A11 | NF_WEN        | A |

| KEYPA<br>D10         | KEYPA<br>D13         | I2C_SCK<br>1         | X32K_O<br>UT1        | XCLK_O<br>UT0        | XCLK<br>_OUT<br>1 | NF_CEN1                | NF_DAT<br>A10    | NF_DAT<br>A1     | NF_DA<br>TA3         | NF_REN        | NF_WPN        | в |

| KEYPA<br>D14         | I2C_SDA<br>0         | PMIC_IR<br>Q         | JTG_TD<br>O          | JTG_TR<br>STN        | JTG_T<br>CK       | NF_CEN0                | NF_CEN3          | VDD_IO_<br>NF    | NF_DA<br>TA12        | NF_DAT<br>A13 | NF_RB0        | С |

| KEYPA<br>D15         | I2C_SDA<br>1         | TEST                 | EN_VDD<br>_CORE      | JTG_TM<br>S          | JTG_T<br>DI       | NF_DAT<br>A0           | NF_DAT<br>A4     | NF_DAT<br>A9     | NF_AL<br>E           | NF_DAT<br>A14 | NF_DATA<br>6  | D |

| VSSA_P<br>LL12_4     | VSSA_P<br>LL12_2     | VSSA_P<br>LL12_5     | VSSA_P<br>LL12_6     | VDD_IO<br>_SYS       | RSTN              | VDDA_P<br>LL12_1       | VDDA_P<br>LL12_3 | VDDA_P<br>LL12_4 | NF_DA<br>TA5         | NF_DAT<br>A7  | NF_DATA<br>15 | E |

| VDD_C<br>ORE_AR<br>M | VDD_C<br>ORE_AR<br>M | VDD_C<br>ORE_AR<br>M | VDD_C<br>ORE_AR<br>M | VDD_C<br>ORE_AR<br>M |                   |                        | VDDA_P<br>LL12_5 | VDDA_P<br>LL12_6 | VDDA_<br>PLL12_<br>2 | GPIO_J2<br>7  | GPIO_J28      | F |

|                      |                      |                      |                      |                      |                   |                        | GPIO_A4          | GPIO_A2          | GPIO_A<br>12         | GPIO_J2<br>9  | GPIO_J30      | G |

|                      |                      |                      |                      |                      |                   | VDD_CO<br>RE_PMU       | GPIO_A5          | GPIO_A3          | GPIO_A<br>1          | GPIO_A<br>0   | SD2_CLK       | н |

| VDD_C<br>ORE_AR<br>M | VDD_C<br>ORE_AR<br>M | VDD_C<br>ORE_AR<br>M | VDD_C<br>ORE_AR<br>M |                      |                   | VSS                    | VSS              | SD2_DA<br>TA0    | SD2_C<br>MD          | SD2_DA<br>TA2 | SD2_DAT<br>A1 | J |

| VSS                  | VSS                  | VSS                  | VSS                  |                      |                   | VSS                    | VSS              | SD2_DA<br>TA3    | SD2_D<br>ATA4        | SD2_DA<br>TA5 | SD2_RST<br>N  | к |

| VSS                  | VSS                  | VSS                  | VSS                  |                      |                   | VSS                    | VSS              | SD2_DET<br>ECTN  | VDD_I<br>O_SD23      | SD2_DA<br>TA6 | SD2_DAT<br>A7 | L |

| VSS                  | VSS                  | VSS                  | VSS                  |                      |                   | VDD_CO<br>RE_VIDE<br>O | VSS              | VDD_IO_<br>LCD   | VDD_I<br>O_LCD       | LCD_SD<br>A   | LCD_RDN       | М |

| 12                      | 13                    | 14                    | 15                    | 16                    | 17                  | 18                     | 19            | 20                  | 21             | 22             | 23             |        |

|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------------|------------------------|---------------|---------------------|----------------|----------------|----------------|--------|

| VDAC_V<br>REFOUT        | VDDA_<br>VDAC         | SD0_CL<br>K           | SD0_DE<br>TECTN       | SD0_DA<br>TA3         | SD1_C<br>LK         | TP_XINN                | TP_YIN<br>N   | TP_BA<br>T_VOL<br>T | CS_DATA<br>4   | CS_DATA<br>2   | CS_PCLK        | A      |

| VDAC_C<br>OMP           | VDD_V<br>DAC          | SD0_CM<br>D           | SD0_DA<br>TA0         | SD0_DA<br>TA2         | SD1_D<br>ETECT<br>N | TP_XINP                | TP_YINP       | CS_DA<br>TA1        | CS_DATA<br>0   | CS_DATA<br>3   | CS_CLK         | A      |

| VDAC_V<br>REFIN         | VDAC_<br>OUTR         | VDAC_R<br>SET         | SD1_DA<br>TA0         | SD1_DA<br>TA2         | SD1_D<br>ATA3       | TP_BAT_<br>ID          | VDD_TP<br>33  | VDD_I<br>O_CS       | CS_HSYN<br>C   | CS_DATA<br>7   | CS_SCK         | A<br>A |

| USBHOST<br>_RREFEX<br>T | VDAC_<br>OUTG         | VDAC_O<br>UTB         | SD0_DA<br>TA1         | SD1_DA<br>TA1         | SD1_C<br>MD         | TP_BAT_<br>TEMP        | VDDA_T<br>P33 | CS_RS<br>TN0        | CS_PWD0        | LCD_DA<br>TA1  | LCD_RST<br>0N  | Y      |

| VSSA_US<br>B            | VSSA_U<br>SB          | VSSA_V<br>DAC         | VSSA_V<br>DAC         | VDD_EF<br>USE         | VDD_I<br>O_SD0<br>1 | TP_KEYS<br>CAN         | VSSA_T<br>P33 | LCD_C<br>SON        | LCD_DA<br>TA6  | LCD_DA<br>TA7  | LCD_DA<br>TA3  | v      |

| USBOTG_<br>ID           | VDDA_<br>USBOTG<br>33 | VDD_CO<br>RE_COR<br>E | VDD_CO<br>RE_COR<br>E | VDD_CO<br>RE_COR<br>E |                     |                        | VSS_TP3<br>3  | LCD_D<br>ATA0       | LCD_DA<br>TA17 | LCD_DA<br>TA15 | LCD_DA<br>TA11 | v      |

|                         |                       |                       |                       |                       |                     |                        | TP_VRE<br>F   | LCD_D<br>ATA2       | LCD_DA<br>TA22 | LCD_DA<br>TA20 | LCD_DA<br>TA19 | τ      |

|                         |                       |                       |                       |                       |                     | CS_DAT<br>A6           | CS_SDA        | LCD_D<br>ATA4       | LCD_RS         | LCD_DA<br>TA8  | LCD_DA<br>TA9  | г      |

| VSSA_US<br>B            | VSSA_U<br>SB          | VSSA_V<br>DAC         | VSSA_V<br>DAC         |                       |                     | CS_DAT<br>A5           | VSS           | LCD_D<br>ATA5       | LCD_DA<br>TA10 | LCD_WR<br>N    | LCD_PCL<br>K   | F      |

| VSS                     | VSS                   | VSS                   | VSS                   |                       |                     | CS_VSY<br>NC           | VSS           | LCD_D<br>ATA12      | LCD_DA<br>TA14 | LCD_DA<br>TA16 | LCD_SCK        | P      |

| VSS                     | VSS                   | VSS                   | VSS                   |                       |                     | VDD_CO<br>RE_VIDE<br>O | VSS           | LCD_D<br>ATA18      | LCD_DA<br>TA23 | LCD_DA<br>TA13 | LCD_DA<br>TA21 | r      |

Figure 3-4 Pin Allocation of 445BGA (right-bottom)

# 3.2 Pin description

| Pin Name        | Pin<br>No. | Pin<br>Typ      | Drive<br>Strength | I/O<br>Power | State<br>After    | Pin Description                                                                                           |

|-----------------|------------|-----------------|-------------------|--------------|-------------------|-----------------------------------------------------------------------------------------------------------|

|                 |            | е               | (mA)              | Or           | Reset             |                                                                                                           |

|                 |            |                 |                   | Range(v)     | Release           |                                                                                                           |

| RSTN            | E17        | l,Sh            | 4                 | VDD_IO_SYS   | I,RSTN            | Reset Signal Input                                                                                        |

| XCLKIN          | A17        | I,Sh            |                   | VDD_IO_SYS   | I,XCLKIN          | External Crystal Input for System Clock                                                                   |

| XCLKOUT         | A16        | 0               |                   | VDD_IO_SYS   | O,XCLKOUT         | External Crystal Ouput for System Clock                                                                   |

| X32K_IN         | A15        | B,<br>Sh,<br>PD | 4                 | VDD_IO_SYS   | I,XCLK_32K_IN     | External 32.768K Clock Input, Share with GPIO_A26                                                         |

| X32K_OUT0       | A14        | B,P<br>D        | 8                 | VDD_IO_SYS   | I,GPIO_A22,PD     | 32.768K Clock Output 0, Share with GPIO_A22                                                               |

| X32K_OUT1       | B15        | B,P<br>D        | 8                 | VDD_IO_SYS   | I,GPIO_A23,PD     | 32.768K Clock Output 1, Share with GPIO_A23                                                               |

| XCLK_OUT0       | B16        | B,P<br>D        | 8                 | VDD_IO_SYS   | I,GPIO_A27,PD     | System Clock Output 0, Share with GPIO_A27                                                                |

| XCLK_OUT1       | B17        | B,P<br>D        | 8                 | VDD_IO_SYS   | I,GPIO_A24,PD     | System Clock Output 1,GPIO_A24                                                                            |

| TEST            | D14        | I,PD            | 4                 | VDD_IO_SYS   | I,TEST            | Test Mode Enable                                                                                          |

| PMIC_IRQ        | C14        | B,P<br>D        | 4                 | VDD_IO_SYS   | I,GPIO_A28,PD     | Interrupt Source and Wakeup Source from PMIC, <b>Share</b> with GPIO_A28                                  |

| EN_VDD_CO<br>RE | D15        | B,P<br>D        | 4                 | VDD_IO_SYS   | O,EN_VDD_CO<br>RE | Enable Power Supply To Digital Core, except Video Codec<br>Core and 3D Core, <b>Share</b> with GPIO_A29   |

| GPIO_A0         | H22        | B,P<br>D        | 8                 | VDD_IO_SYS   | I,GPIO_A0,PD      | GPIO_A0, <b>Share</b> with NF_CEN8(NAND Chip Enable 8), <b>Share</b> with UMOUT0(ASIC debug)              |

| GPIO_A1         | H21        | B,P<br>D        | 8                 | VDD_IO_SYS   | I,GPIO_A1,PD      | GPIO_A1, <b>Share</b> with NF_CEN9(NAND Chip Enable<br>9), <b>Share</b> with UMOUT1(ASIC debug)           |

| GPIO_A2         | G20        | B,P<br>D        | 8                 | VDD_IO_SYS   | I,GPIO_A2,PD      | GPIO_A2, Share with NF_CEN10(NAND Chip Enable 10), Share with UMOUT2(ASIC debug)                          |

| GPIO_A3         | H20        | B,P<br>D        | 8                 | VDD_IO_SYS   | I,GPIO_A3,PD      | GPIO_A3, <b>Share</b> with NF_CEN11(NAND Chip Enable 11), <b>Share</b> with UMOUT3(ASIC debug)            |

| GPIO_A4         | G19        | B,P<br>U        | 8                 | VDD_IO_SYS   | I,GPIO_A4,PU      | GPIO_A4, <b>Share</b> with NF_CEN12(NAND Chip Enable 12), <b>Share</b> with UMOUT4(ASIC debug)            |

| GPIO_A5         | H19        | B,P<br>U        | 8                 | VDD_IO_SYS   | I,GPIO_A5,PU      | GPIO_A5, <b>Share</b> with NF_CEN13(NAND Chip Enable 13), <b>Share</b> with UMOUT5(ASIC debug)            |

| GPIO_A12        | G21        | B,P<br>U        | 8                 | VDD_IO_SYS   | I,GPIO_A12,PU     | GPIO_A12, <b>Share</b> with SPI0_SS1N(SPI0 Slave Select 1, only in SPI0 Master Mode), UMOUT12(ASIC debug) |

#### Table 3-1 Signal Description of 445BGA

| Pin Name  | Pin | Pin      | Drive            | I/O         | State          | Pin Description                                       |

|-----------|-----|----------|------------------|-------------|----------------|-------------------------------------------------------|

|           | No. | Тур      | Strength<br>(mA) | Power<br>Or | After<br>Reset |                                                       |

|           |     | e        | (IIIA)           | Range(v)    | Release        |                                                       |

|           | C17 | B,       |                  |             |                |                                                       |

| JTG_TCK   |     | PU,      | 4                | VDD_IO_SYS  | I,JTG_TCK,PU   | JTAG Test Clock, Share with GPIO_A17                  |

|           |     | Sh       |                  |             |                |                                                       |

| JTG_TMS   | D16 | B,<br>PU | 4                | VDD_IO_SYS  | I,JTG_TMS,PU   | JTAG Test Mode Select, Share with GPIO_A18            |

|           | C16 | В,       |                  |             | I,JTG_TRSTN,P  |                                                       |

| JTG_TRSTN |     | PD,      | 4                | VDD_IO_SYS  | D              | JTAG Test Reset, <b>Share</b> with GPIO_A19           |

|           | D17 | Sh<br>B, |                  |             |                |                                                       |

| JTG_TDI   |     | ь,<br>PU | 4                | VDD_IO_SYS  | I,JTG_TDI,PU   | JTAG Test Data Input, Share with GPIO_A20             |

|           | C15 |          |                  |             |                |                                                       |

| JTG_TDO   |     | B,<br>PU | 4                | VDD_IO_SYS  | B,JTG_TDO      | JTAG Test Data Output, Share with GPIO_A21            |

|           |     |          |                  |             |                |                                                       |

| PWM0      | E6  | B,P<br>D | 4                | VDD_IO_SYS  | I,GPIO_C0,PD   | PWM0 output, Share with GPIO_C0                       |

|           | E7  | B,P      |                  |             |                |                                                       |

| PWM1      |     | D, I     | 4                | VDD_IO_SYS  | I,GPIO_C1,PD   | PWM1 output, Share with GPIO_C1                       |

|           | A13 | В,       |                  |             |                |                                                       |

| I2C_SCK0  |     | PU       | 8                | VDD_IO_SYS  | I,GPIO_C16,PU  | I2C0 Serial Clock, Share with GPIO_C16                |

|           | C13 | B,       |                  |             |                |                                                       |

| I2C_SDA0  | 013 | в,<br>PU | 8                | VDD_IO_SYS  | I,GPIO_C17,PU  | I2C0 Serial Data, Share with GPIO_C17                 |

|           | B14 | B,       |                  |             |                |                                                       |

| I2C_SCK1  |     | PU       | 8                | VDD_IO_SYS  | I,GPIO_C18,PU  | I2C1 Serial Clock, Share with GPIO_C18                |

|           | D13 | В,       | _                |             |                |                                                       |

| I2C_SDA1  |     | PU       | 8                | VDD_IO_SYS  | I,GPIO_C19,PU  | I2C1 Serial Data, <b>Share</b> with GPIO_C19          |

|           | C4  | В,       |                  |             |                |                                                       |

| UART0_SDO |     | PU       | 4                | VDD_IO_SYS  | I,GPIO_C2,PU   | UART0 Serial Data Output, Share with GPIO_C2          |

|           | D5  | В,       |                  |             |                |                                                       |

| UART0_SDI |     | PU       | 4                | VDD_IO_SYS  | I,GPIO_C3,PU   | UART0 Serial Data Input, <b>Share</b> with GPIO_C3    |

| UART1_DSR | C6  | В,       | 4                |             |                | UART1 Data Set Ready, Share with UART3_SDO(UART3      |

| Ν         |     | PU       | 4                | VDD_IO_SYS  | I,GPIO_C4,PU   | Serial Data Output), Share with GPIO_C4               |

| UART1_DCD | C5  | В,       | 4                | VDD_IO_SYS  | I,GPIO_C5,PU   | UART1 Data Carrier Detect, Share with UART3_SDI(UART3 |

| Ν         |     | PU       |                  | 0_010_010   | 1,0110_03,50   | Serial Data Input), Share with GPIO_C5                |

| UART1_RIN | D6  | В,       | 4                | VDD_IO_SYS  | I,GPIO_C6,PU   | UART1 Ring Indicator, Share with UART3_CTSN(UART3     |

| 2         |     | PU       |                  |             | ,              | Clear to Send), <b>Share</b> with GPIO_C6             |

| Pin Name       | Pin | Pin      | Drive    | I/O        | State         | Pin Description                                                                                                                      |

|----------------|-----|----------|----------|------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                | No. | Тур      | Strength | Power      | After         |                                                                                                                                      |

|                |     | е        | (mA)     | Or         | Reset         |                                                                                                                                      |

|                |     |          |          | Range(v)   | Release       |                                                                                                                                      |

| UART1_DTR<br>N | D7  | B,<br>PD | 4        | VDD_IO_SYS | I,GPIO_C7,PD  | UART1 Data Terminal Ready, <b>Share</b> with UART3_RTSN(UART3 Request to Send), <b>Share</b> with GPIO_C7                            |

| UART1_CTS<br>N | C7  | B,<br>PU | 4        | VDD_IO_SYS | I,GPIO_C8,PU  | UART1 Clear to Send, Share with GPIO_C8                                                                                              |

| UART1_RTSN     | D8  | B,<br>PD | 4        | VDD_IO_SYS | I,GPIO_C9,PD  | UART1 Request to Send, Share with GPIO_C9                                                                                            |

| UART1_SDO      | В9  | B,<br>PU | 4        | VDD_IO_SYS | I,GPIO_C10,PU | UART1 Serial Data Output, Share with GPIO_C10                                                                                        |

| UART1_SDI      | C8  | B,<br>PU | 4        | VDD_IO_SYS | I,GPIO_C11,PU | UART1 Serial Data Input, Share with GPIO_C11                                                                                         |

| SPI0_SCLK      | A8  | B,<br>PU | 12       | VDD_IO_SYS | I,GPIO_C20,PU | SPI0 Serial Clock, Share with GPIO_C20                                                                                               |

| SPI0_SSON      | B8  | B,<br>PU | 8        | VDD_IO_SYS | I,GPIO_C21,PU | SPI0 Slave Select 0, Share with GPIO_C21                                                                                             |

| SPI0_MOSI      | B7  | B,<br>PU | 8        | VDD_IO_SYS | I,GPIO_C22,PU | SPI0 Master Out Slave In, <b>Share</b> with GPIO_C22                                                                                 |

| SPI0_MISO      | A7  | B,<br>PU | 8        | VDD_IO_SYS | I,GPIO_C23,PU | SPI0 Master In Slave Out, Share with GPIO_C23                                                                                        |

| KEYPAD0        | A10 | B,P<br>U | 4        | VDD_IO_SYS | I,GPIO_D0,PU  | Keypad 0, <b>Share</b> with TRACE_DATA0(Trace data0 for ARM debug), <b>Share</b> with UMOUT16(ASIC debug), <b>Share</b> with GPIO_D0 |

| KEYPAD1        | A9  | B,P<br>U | 4        | VDD_IO_SYS | I,GPIO_D1,PU  | Keypad 1, <b>Share</b> with TRACE_DATA1(Trace data1 for ARM debug), <b>Share</b> with UMOUT17(ASIC debug), <b>Share</b> with GPIO_D1 |

| KEYPAD2        | A11 | B,P<br>U | 4        | VDD_IO_SYS | I,GPIO_D2,PU  | Keypad 2, <b>Share</b> with TRACE_DATA2(Trace data2 for ARM debug), <b>Share</b> with UMOUT18(ASIC debug), <b>Share</b> with GPIO_D2 |

| KEYPAD3        | B10 | B,P<br>U | 4        | VDD_IO_SYS | I,GPIO_D3,PU  | Keypad 3, <b>Share</b> with TRACE_DATA3(Trace data3 for ARM debug), <b>Share</b> with UMOUT19(ASIC debug), <b>Share</b> with GPIO_D3 |

| KEYPAD4        | C9  | B,P<br>U | 4        | VDD_IO_SYS | I,GPIO_D4,PU  | Keypad 4, <b>Share</b> with TRACE_DATA4(Trace data4 for ARM debug), <b>Share</b> with UMOUT20(ASIC debug), <b>Share</b> with GPIO_D4 |

| Pin Name | Pin<br>No. | Pin<br>Typ<br>e | Drive<br>Strength<br>(mA) | I/O<br>Power<br>Or | State<br>After<br>Reset | Pin Description                                                                                                                          |

|----------|------------|-----------------|---------------------------|--------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|          |            |                 | (                         | Range(v)           | Release                 |                                                                                                                                          |

| KEYPAD5  | D9         | B,P<br>U        | 4                         | VDD_IO_SYS         | I,GPIO_D5,PU            | Keypad 5, <b>Share</b> with TRACE_DATA5(Trace data5 for ARM debug), <b>Share</b> with UMOUT21(ASIC debug), <b>Share</b> with GPIO_D5     |

| KEYPAD6  | B11        | B,P<br>U        | 4                         | VDD_IO_SYS         | I,GPIO_D6,PU            | Keypad 6, <b>Share</b> with TRACE_DATA6(Trace data6 for ARM debug), <b>Share</b> with UMOUT22(ASIC debug), <b>Share</b> with GPIO_D6     |

| KEYPAD7  | C10        | B,P<br>U        | 4                         | VDD_IO_SYS         | I,GPIO_D7,PU            | Keypad 7, <b>Share</b> with TRACE_DATA7(Trace data7 for ARM debug), <b>Share</b> with UMOUT23(ASIC debug), <b>Share</b> with GPIO_D7     |

| KEYPAD8  | A12        | B,P<br>U        | 4                         | VDD_IO_SYS         | I,GPIO_D8,PU            | Keypad 8, <b>Share</b> with TRACE_DATA8(Trace data8 for ARM debug), <b>Share</b> with UMOUT24ASIC debug), <b>Share</b> with GPIO_D8      |

| KEYPAD9  | D10        | B,P<br>U        | 4                         | VDD_IO_SYS         | I,GPIO_D9,PU            | Keypad 9, <b>Share</b> with TRACE_DATA9(Trace data9 for ARM debug), <b>Share</b> with UMOUT25(ASIC debug), <b>Share</b> with GPIO_D9     |

| KEYPAD10 | B12        | B,P<br>U        | 4                         | VDD_IO_SYS         | I,GPIO_D10,PU           | Keypad 10, <b>Share</b> with TRACE_DATA10(Trace data10 for ARM debug), <b>Share</b> with UMOUT26(ASIC debug), <b>Share</b> with GPIO_D10 |

| KEYPAD11 | C11        | B,P<br>U        | 4                         | VDD_IO_SYS         | I,GPIO_D11,PU           | Keypad 11, <b>Share</b> with TRACE_DATA11(Trace data11 for ARM debug), <b>Share</b> with UMOUT27(ASIC debug), <b>Share</b> with GPIO_D11 |