# **IRPS5401 PMIC Datasheet**

### **IRPS5401 PMIC**

### Flexible Power Management Unit

#### **Features**

- Full power system including 5 integrated outputs

- 4A, 4A, 2A and 2A Switching Regulators

- 500mA Source/Sink Linear regulator

- Single rail operation 5.5V to 12V

- Output Range from 0.25V to 5.1V for outputs A-D and 0.5V to 3.6V for LDO

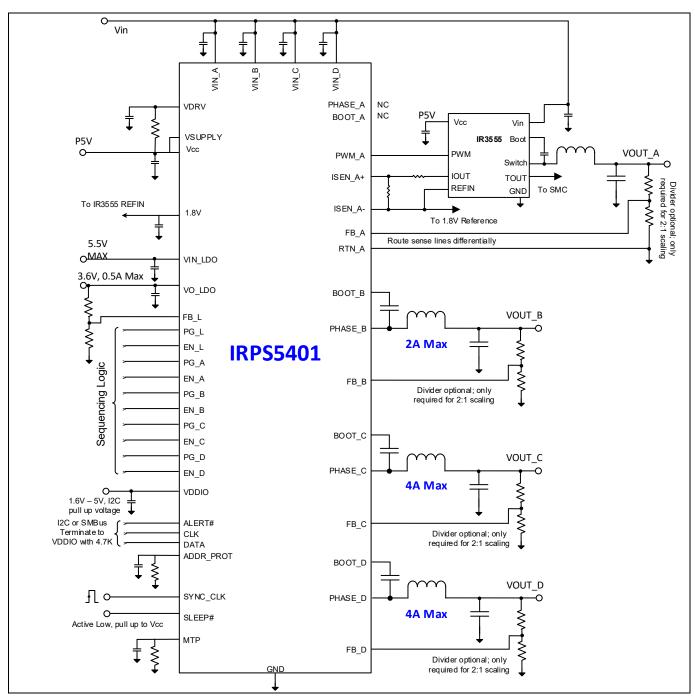

- Allows combining outputs and/or the use of an external IR MOSFET™ Power Stage to increase output current to as high as 50A

- Emulated current mode control without external compensation

- Differential voltage sensing on Switcher A for higher accuracy

- I2C / PMBus with integrated level shifter

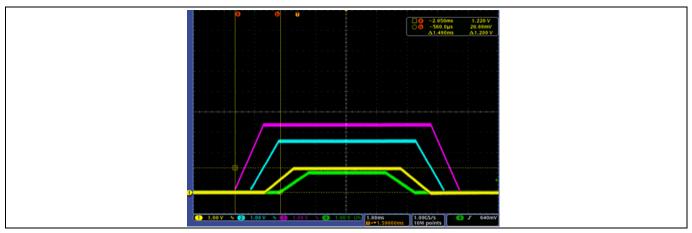

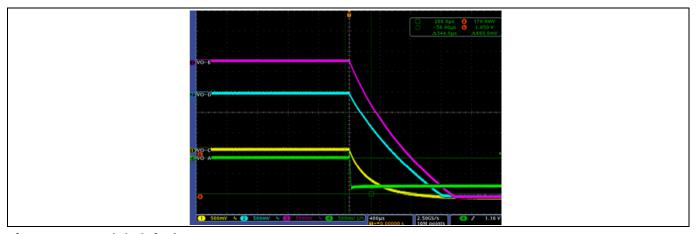

- Advanced Sequencing control

- Extensive PMBus command set of 74 commands

- Integrated current sensing and full telemetry including voltage, current, temperature and faults

- Rated for -40°C to +125°C T<sub>J</sub> operation

- Pb-Free, RoHS6, 7x7mm, 56-pin, 0.4mm pitch QFN

### **Potential applications**

- High density ASIC, FPGA & CPU multi-rail systems

- · Embedded Computing systems

- Communications and Storage systems

### **Description**

The IRPS5401 is a complete power management unit delivering up to 5 output voltages to processors, FPGA's and other multi-rail power systems. Four high efficiency configurable switching regulators and a Source/Sink Linear regulator provide the typical rails required such as core voltage, memory voltage and I/O voltages.

Integrated, accurate current, voltage and temperature sensing allows telemetry and fault reporting through the I2C/PMBus.

The IRPS5401 switching regulators utilize fixed frequency emulated current mode control, and thus no external compensation is required.

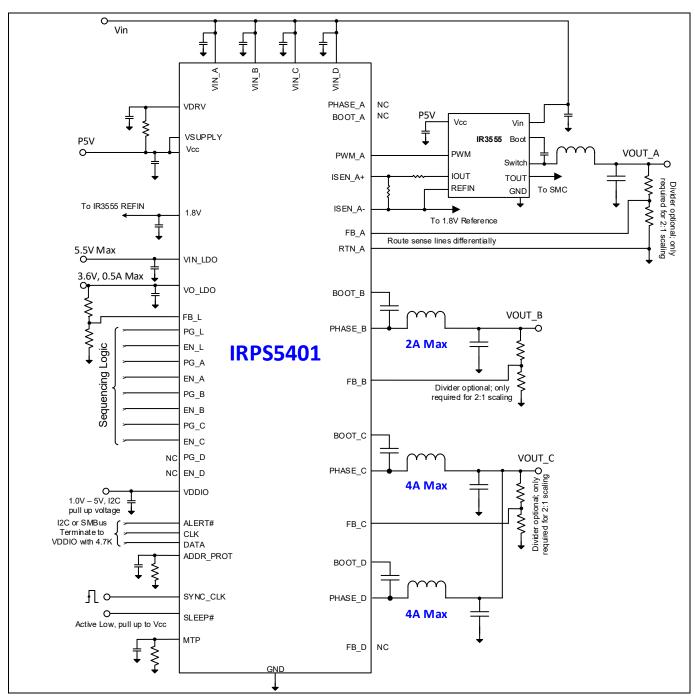

The IRPS5401 is highly flexible. Switchers A and B deliver 2A each. Switchers C and D, deliver 4A each and can also be combined to deliver 8A. Further, Switcher A can be configured to use an external IR MOSFET™ Power Stage to deliver up to 50A or more.

## Flexible Power Management Unit

### **Table of contents**

## **Table of contents**

| Feat         | ures                                                                                | 1  |

|--------------|-------------------------------------------------------------------------------------|----|

| Pote         | ntial applications                                                                  | 1  |

| Desc         | ription                                                                             | 1  |

| Table        | e of contents                                                                       | 2  |

| 1            | Ordering Information                                                                | 4  |

| 2            | Application Circuit                                                                 | 6  |

| 3            | Pinout Diagram                                                                      | 7  |

| 4            | Pin Function                                                                        | 8  |

| 5            | Block Diagram                                                                       | 11 |

| 6            | Absolute Maximum Ratings                                                            | 12 |

| 7            | Electrical Specifications                                                           | 13 |

| 8            | Typical Application Diagrams                                                        |    |

| 9            | Description                                                                         | 24 |

| 9.1          | One-time Programmable (OTP) Memory                                                  | 24 |

| 9.2          | MTP pin (pin 54)                                                                    | 24 |

| 9.3          | Device Power-up and Initialization                                                  |    |

| 9.4          | Addressing the IRPS5401                                                             |    |

| 9.5          | Switching Frequency                                                                 |    |

| 9.6          | Synchronizing to an External Clock                                                  |    |

| 9.7          | Switcher A in External Powerstage Mode                                              |    |

| 9.8<br>9.9   | Digital Controller & PWMDiode Emulation / Discontinuous Mode Operation/AOT          |    |

| 9.9<br>9.10  | Output Voltage Sensing, Telemetry and Faults                                        |    |

| 9.11         | Output Voltage Sensing, Felemetry and Fauts                                         |    |

| 9.12         | Output Under Voltage Protection (UVP)                                               |    |

| 9.13         | Current Sensing, Telemetry and Faults                                               |    |

| 9.14         | Over-current Protection (OCP)                                                       | 34 |

| 9.15         | Input Voltage Sensing, Telemetry and Faults                                         | 35 |

| 9.16         | Die Temperature Sensing, Telemetry and Faults                                       |    |

| 9.17         | Power Sequencing and Global Faults                                                  |    |

| 9.18         | Sleep                                                                               |    |

| 9.19<br>9.20 | Combined Switcher C and D Operation                                                 |    |

| 9.20         | Linear RegulatorLDO Monitoring and Faults                                           |    |

| 9.22         | Output Voltage Reporting, Output Overvoltage Protection and Undervoltage Protection |    |

| 9.23         | Input Voltage Reporting, Input UVLO and Input Overvoltage Protection                |    |

| 9.24         | Over Current Protection                                                             |    |

| 9.25         | I2C Security                                                                        | 40 |

| 9.26         | Password Protection                                                                 | 41 |

| 9.27         | Pin Protection                                                                      | 41 |

| 10           | Layout Guidelines                                                                   |    |

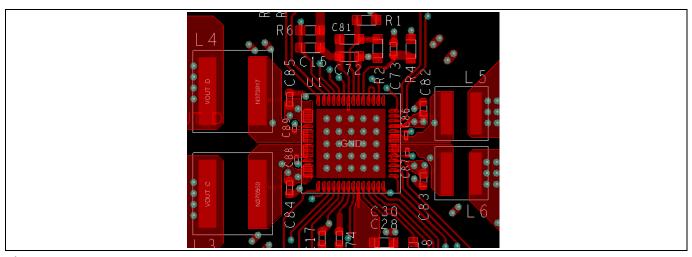

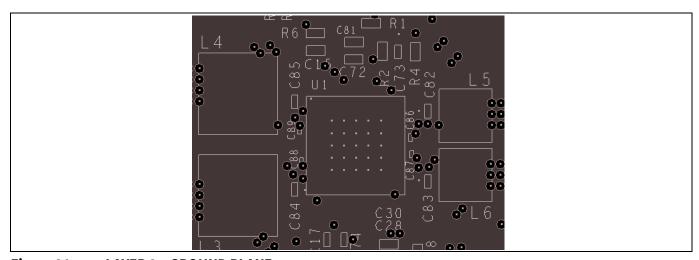

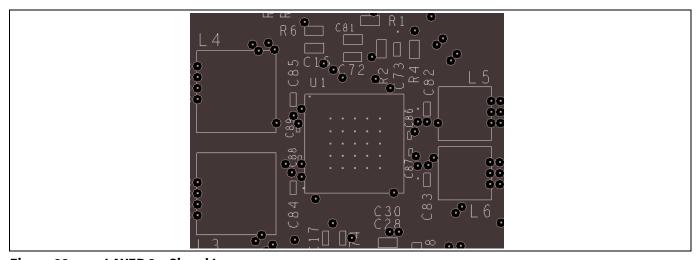

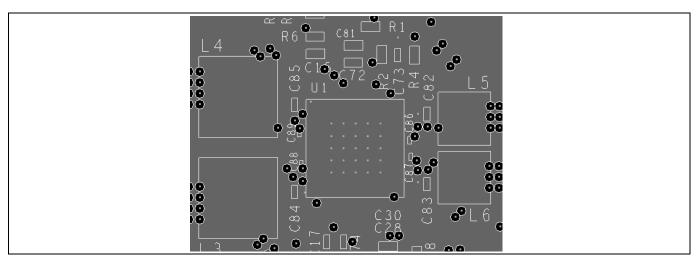

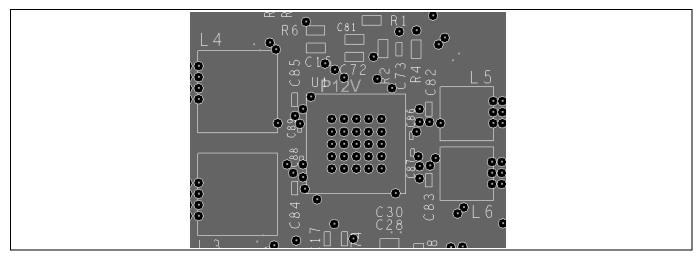

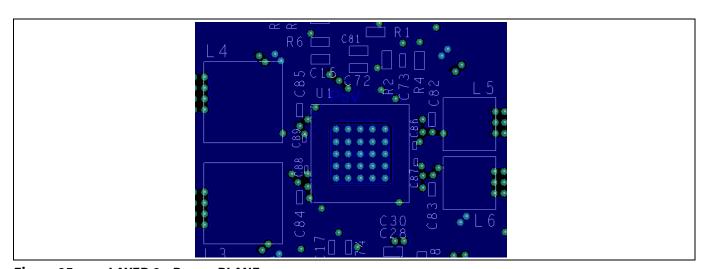

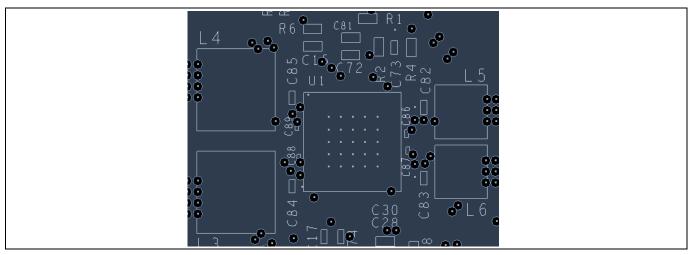

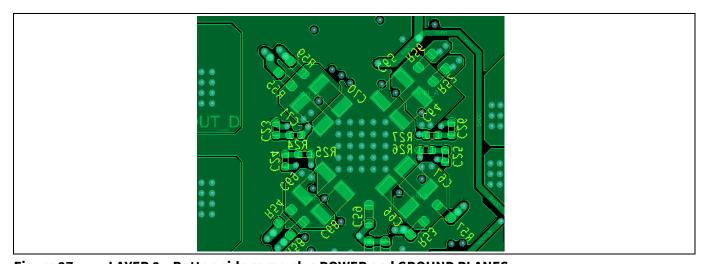

| 10.1         | Sample layout                                                                       | 44 |

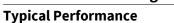

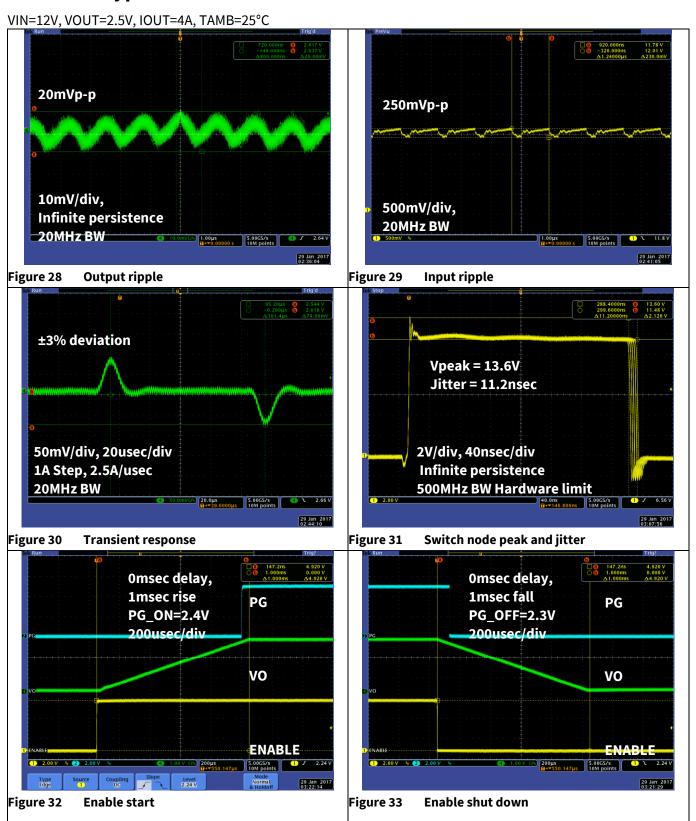

| 11           | Typical Performance                                                                 |    |

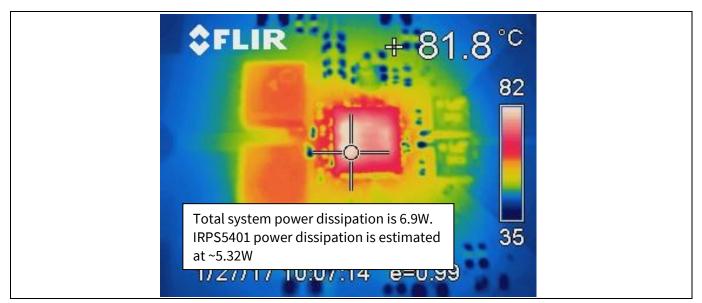

| 11.1         | Typical thermal performance at max output power                                     | 48 |

| 12           | PMBUS Commands                                                                      | 49 |

# Flexible Power Management Unit

### **Table of contents**

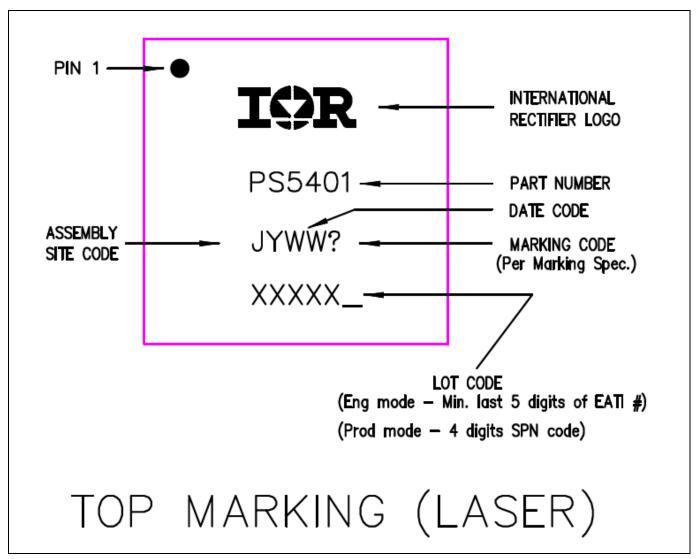

| 13    | Marking Information              | 55 |

|-------|----------------------------------|----|

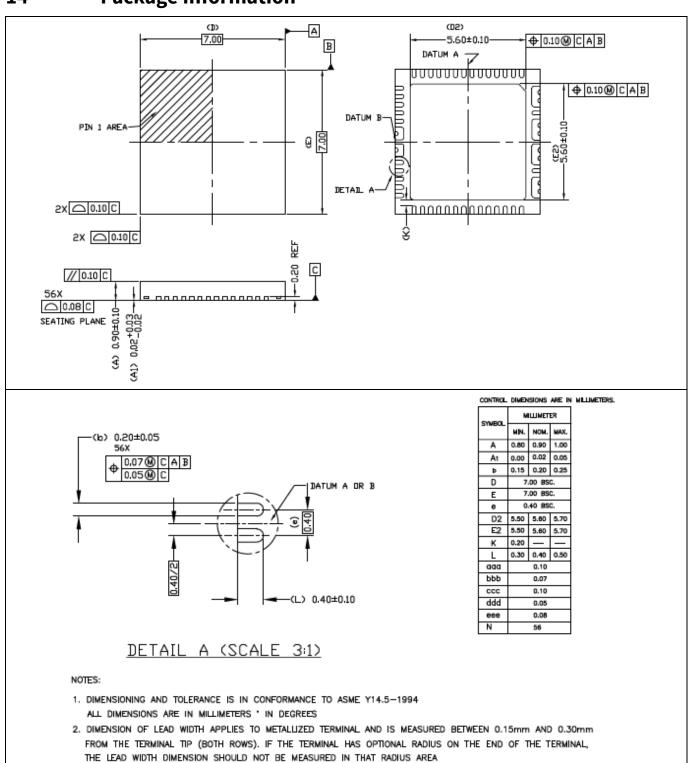

| 14    | Package Information              | 56 |

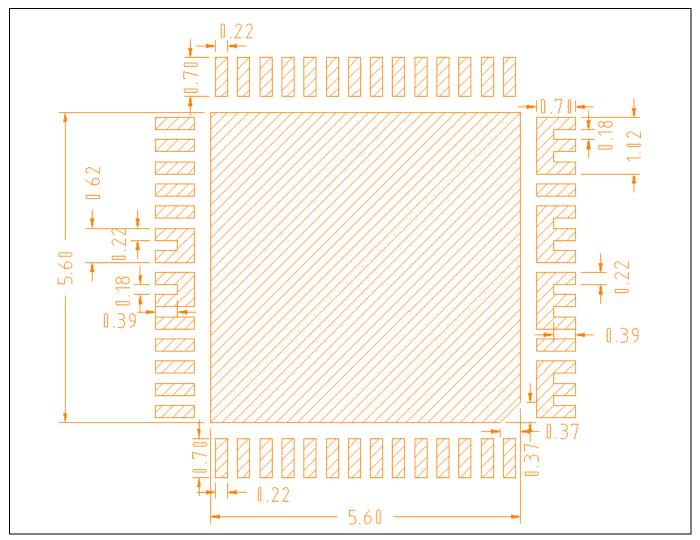

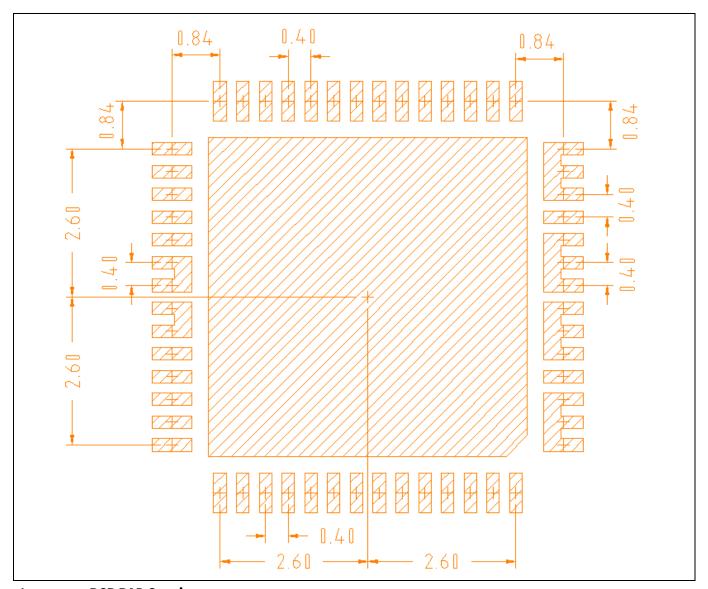

| 14.1  | PCB Pad Size                     | 57 |

| 14.2  | PCB Pad Spacing                  | 58 |

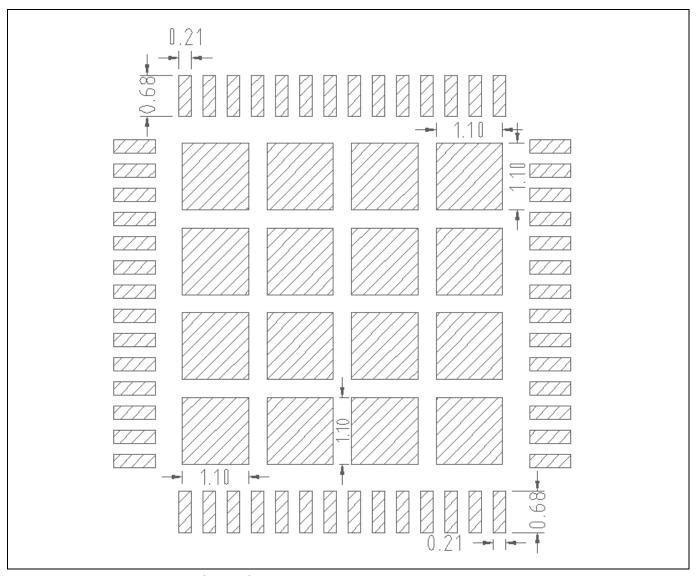

| 14.3  | Solder Paste Stencil Pad Size    |    |

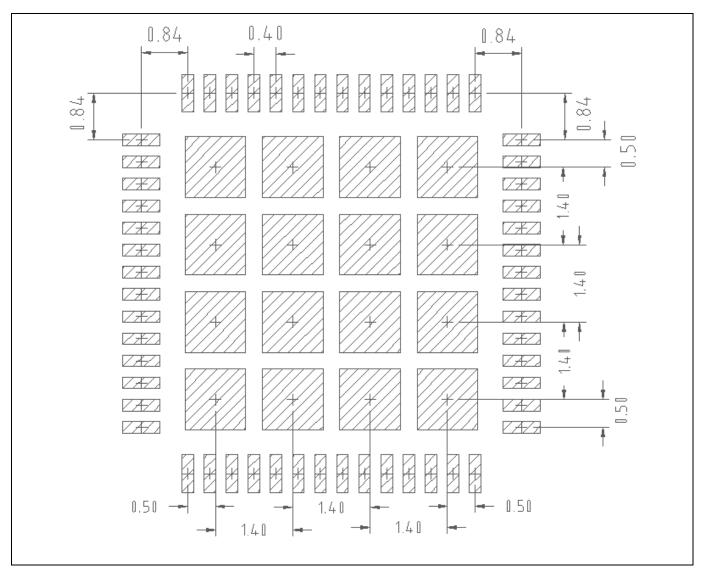

| 14.4  | Solder Paste Stencil Pad Spacing | 60 |

| 15    | Environmental Qualifications     | 61 |

| Revis | sion History                     | 62 |

### Flexible Power Management Unit

# **1** Ordering Information

Table 1 Ordering Information

| Base part number | Package type    | Standard pack | Orderable part number | Description                   |

|------------------|-----------------|---------------|-----------------------|-------------------------------|

| IRPS5401M        | QFN 7 mm x 7 mm | Tape and Reel | IRPS5401MTRPBF        | Unprogrammed                  |

| IRPS5401M        | QFN 7 mm x 7 mm | Tape and Reel | IRPS5401MXI03TRP      | Pre-programmed per<br>Table 2 |

| IRPS5401M        | QFN 7 mm x 7 mm | Tape and Reel | IRPS5401MXI04TRPAUMA1 | Pre-programmed per<br>Table 3 |

### Table 2 IRPS5401MXI03TRP Loop Configurations

| Config | R_MTP<br>R_ADDR | A (bold = external PS) | В          | С          | D          | LDO<br>(supplied from) |  |

|--------|-----------------|------------------------|------------|------------|------------|------------------------|--|

| 1      | 8.87kΩ          | 1.8V/0.5A              | 1.8V/1.4A  | 0.85V/0.6A | 0.85V/3.7A | 1.2V (B)               |  |

| 2      | 10kΩ            | 1.2V/1.2A              | 0.85V/0.6A | 3.3V/1.5A  | 0.85V/4A   | 1.8V (C)               |  |

| 3      | 11kΩ            | 1.8V/0.5A              | 5V/1.5A    | 3.3V/3.3A  | 0.85V/2A   | 1.8V (C)               |  |

| 4      | 2.32kΩ          | 0.85V/16A              | 1.2V/1.5A  | 1.8V/1A    | 1.8V/4A    | 1.2V (D or external)   |  |

| 5      | 2.87kΩ          | 0.85V/25A              | 1.2V/1.5A  | 1.8V/1A    | 1.8V/4A    | 1.2V (D or external)   |  |

| 6      | 3.48kΩ          | 3.3V/1.4A              | 1.8V/1A    | 0.9V/3A    | 1.2V/3A    | 0.85V (A)              |  |

| 7      | 4.12kΩ          | 0.72V/9A               | 3.3V/2A    | 0.85V/7A   |            | 1.2V (B)               |  |

| 8      | 4.75kΩ          | 0.72V/15A              | 3.3V/2A    | 0.85V/7A   |            | 1.2V (B)               |  |

| 9      | 5.49kΩ          | 1.8V/1A                | 1.2V/1.5A  | 1.8V/4A    | 2.5V/1.5A  | 1.8V (D)               |  |

| 10     | 6.19kΩ          | 0.9V/2A                | 1.2V/1.5A  | 1.8V/2.5A  | 1.2V/2A    | 0.85V (C)              |  |

| 11     | 6.98kΩ          | 0.72V/9A               | 1.2V/1.5A  | 0.85V/4A   | 1.8V/2A    | 1.2V (D or external)   |  |

| 12     | 7.87kΩ          | 0.72V/20A              | 1.2V/1.2A  | 0.85V/4A   | 1.8V/2A    | 1.2V (D or external)   |  |

### Flexible Power Management Unit

### **Ordering Information**

### Table 3 IRPS5401MXI04TRPAUMA1 Loop Configurations

| Config | Config. B MTD A/hold- B C D |                        |           |                 |                        |                               |  |  |

|--------|-----------------------------|------------------------|-----------|-----------------|------------------------|-------------------------------|--|--|

| Config | R_MTP<br>R_ADDR             | A (bold = external PS) | В         | С               | D                      | LDO<br>(supplied from)        |  |  |

| 1      | Not<br>used                 |                        |           |                 |                        |                               |  |  |

| 2      | Not<br>used                 |                        |           |                 |                        |                               |  |  |

| 3      | Not<br>used                 |                        |           |                 |                        |                               |  |  |

| 4      | 2.32kΩ                      | 0.85V/ 15A             | 1.8V/2A   | 1.2V/5A         |                        | 0.9V/0.5A<br>(external 2.5V)  |  |  |

| 5      | 2.87kΩ                      | 3.3V/10A               | 1.13V/1A  | 5V/2.1A 1.8V/3A |                        | 0.85V/0.5A (external 2.5V)    |  |  |

| 6      | 3.48kΩ                      | 0.85V/15A              | 1.8V/2A   | 0.85V/7A        |                        | 3.3V/0.5A (optional)          |  |  |

| 7      | 4.12kΩ                      | 3.3V/10A               | 2.5V/2A   | 1.2V/6A         |                        | 0.85V/0.5A<br>(external 2.5V) |  |  |

| 8      | 4.75kΩ                      | 1.2V/6A                | 2.5V/0.5A | 1.8V/5A         | 1.8V/5A 1.8V/0 (extern |                               |  |  |

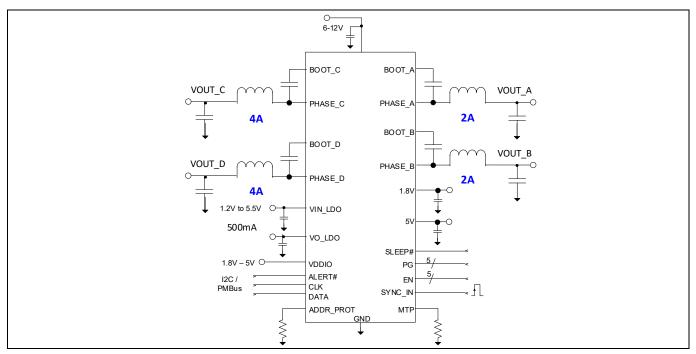

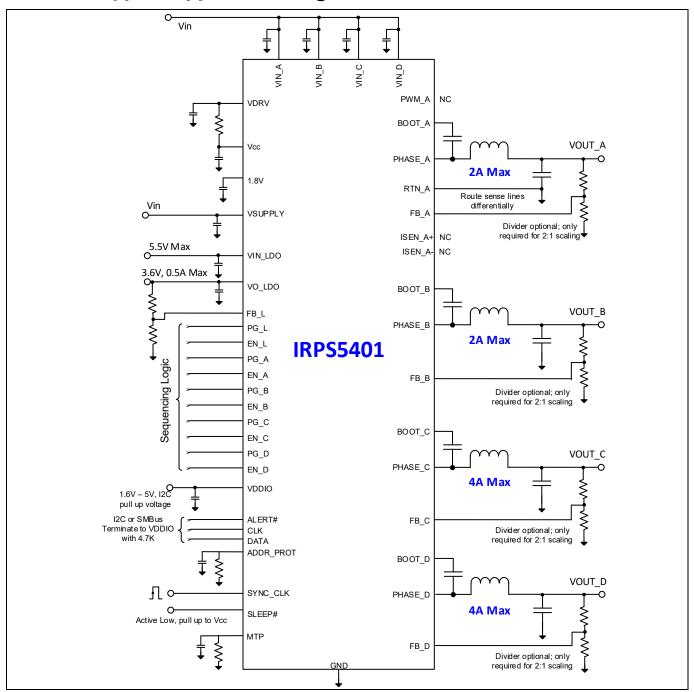

#### **Application Circuit** 2

Figure 1 **IRPS5401 Basic application circuit**

Figure 2 System efficiency with VO= 2.5V, FSW=800kHz, Tj=45°C

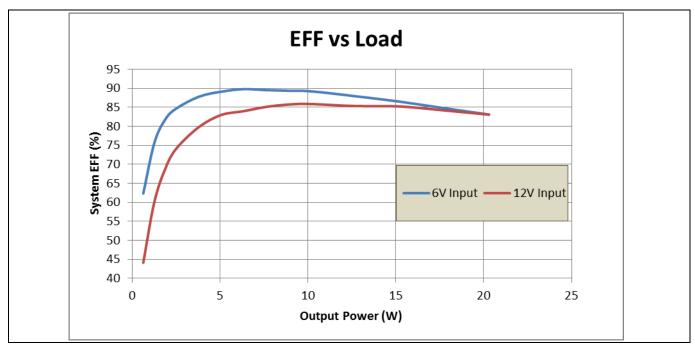

**Pinout Diagram**

## **3** Pinout Diagram

7 of 64

Figure 3 Pinout diagram 7mm x 7mm QFN (Top View)

### Flexible Power Management Unit

# 4 Pin Function

Table 4 PIN Function

| PIN # Name TYP |         |       | Description                                                                                                                                                                                                                                                                     | If not used     |  |

|----------------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

|                |         |       |                                                                                                                                                                                                                                                                                 |                 |  |

| 1,2,3          | VIN_D   | P [I] | Input supply voltage pins for Switcher D. Decouple locally by connecting a ceramic capacitor from this pin to GND.                                                                                                                                                              | Short To<br>GND |  |

| 4              | BOOT_D  | A [B] | Supply input for Switcher D high side FET gate drive. Connect a 0.1uF MLCC between this pin and PHASE_ D pins. An internal diode is connected between VDRV and this pin                                                                                                         | Open            |  |

| 5,6,7          | PHASE_D | P [O] | Switch node of Switcher D. Connect directly to the output inductor.                                                                                                                                                                                                             | Open            |  |

| 8,9,<br>10     | PHASE_C | P [O] | Switch node of Switcher C. Connect directly to the output inductor.                                                                                                                                                                                                             | Open            |  |

| 11             | BOOT_C  | A [B] | Supply input for Switcher C high side FET gate drive. Connect a 0.1uF MLCC between this pin and PHASE_C pins. An internal diode is connected between VDRV and this pin                                                                                                          | Open            |  |

| 12,<br>13,14   | VIN_C   | P [I] | Input supply voltage pins for Switcher C. Decouple locally by connecting a ceramic capacitor from this pin to GND.                                                                                                                                                              | Short To<br>GND |  |

| 15             | FB_C    | A [I] | Switcher C feedback input. Connect directly to VOUT_C for output voltages less than 2.55V. Connect to VOUT_C with a 2:1 resistor divider for output voltages greater than 2.55V.                                                                                                |                 |  |

| 16             | PG_D    | D [O] | Open drain power good output indicating Switcher D is powered up                                                                                                                                                                                                                | Open            |  |

| 17             | ALERT#  | D [O] | I2C/PMBus Alert line. This alert signal can indicate one or more faults, allowing the system bus manager to poll the device and identify the root cause. All faults or customer selected faults such as overcurrent or over-temperature may be specifically masked to this pin. | Open            |  |

| 18             | CLK     | D [B] | I2C/PMBus Clock Line. Pull up to VDDIO with 10K                                                                                                                                                                                                                                 | n/a             |  |

| 19             | DATA    | D [B] | I2C/PMBus Data Line. Pull up to VDDIO with 10K                                                                                                                                                                                                                                  | n/a             |  |

| 20             | VDDIO   | P [I] | Pull-up signal voltage for I2C communications. Connect to the same I/O rail used by the I2C master.                                                                                                                                                                             | n/a             |  |

| 21             | 1V8     | A [O] | 1.8V reference used by the device for internal analog and digital control. Decouple using a 1.0uF X7R type ceramic capacitor                                                                                                                                                    | n/a             |  |

| 22             | VIN_LDO | P [I] | Input to the linear regulator. See linear regulator section for specific requirements. This voltage can range from 1.2V to 5.5V, with restrictions on overall power dissipation                                                                                                 | Short To<br>GND |  |

| 23             | VO_LDO  | A[O]  | LDO output                                                                                                                                                                                                                                                                      | Open            |  |

| 24             | FB_L    | A [I] | LDO feedback input                                                                                                                                                                                                                                                              | Open            |  |

| 25             | PG_L    | D[I]  | Open drain power good output indicating LDO is powered up. Pull up to 5V with 10K                                                                                                                                                                                               | Open            |  |

| 26             | PG_A    | D[I]  | Open drain power good output indicating switcher A is powered up. Pull up to 5V with 10K                                                                                                                                                                                        | Open            |  |

# Flexible Power Management Unit

### **Pin Function**

| PIN   |            |       | Description                                                                                                                                                                                                                                                                                                                                                                                                              | If not used       |  |

|-------|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| #     | # Name TYP |       |                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |  |

| 27    | PG_C       | D[I]  | Open drain power good output indicating switcher C is powered up. Pull up to 5V with 10K                                                                                                                                                                                                                                                                                                                                 | Open              |  |

| 28    | EN_L       | D[I]  | LDO enable input control. Active High, external termination required, do not leave floating. LVTTL threshold levels. 'ON' threshold is 2.1V minimum                                                                                                                                                                                                                                                                      | Short To<br>GND   |  |

| 29    | SLEEP#     | D[I]  | Active low signal to place the device in a low power mode LVTTL threshold levels. 'SLEEP ENABLED' threshold is 0.8V maximum                                                                                                                                                                                                                                                                                              | Short to<br>VCC   |  |

| 30    | PG_B       | D[I]  | Open drain power good output indicating switcher B is powered up. Pull up to 5V with 10K                                                                                                                                                                                                                                                                                                                                 | Open              |  |

| 31    | FB_B       | A [I] | Switcher B feedback input. Connect directly to VOUT_B for output voltages less than 2.55V. Connect to VOUT_B with a 2:1 resistor divider for output voltages greater than 2.55V.                                                                                                                                                                                                                                         | Open              |  |

| 32    | VIN_B      | P [I] | Input supply voltage pin for Switcher B. Decouple locally by connecting a ceramic capacitor from this pin to GND.                                                                                                                                                                                                                                                                                                        | Short To<br>GND   |  |

| 33    | BOOT_B     | A [B] | Supply input for Switcher B high side FET gate drive. Connect a 0.1uF MLCC between this pin and PHASE_B pins. An internal diode is connected between VDRV and this pin                                                                                                                                                                                                                                                   | Open              |  |

| 34,35 | PHASE_B    | P [O] | Switch node of Switcher B. Connect directly to the output inductor.                                                                                                                                                                                                                                                                                                                                                      | Open              |  |

| 36,37 | PHASE_A    | P [O] | Switch node of Switcher A. Connect directly to the output inductor.                                                                                                                                                                                                                                                                                                                                                      | Open              |  |

| 38    | BOOT_A     | A [B] | Supply input for Switcher A high side FET gate drive. Connect a 0.1uF MLCC between this pin and PHASE_A pins. An internal diode is connected between VDRV and this pin                                                                                                                                                                                                                                                   | Open              |  |

| 39    | VIN_A      | P [I] | Input supply voltage pin for Switcher A. Decouple locally by connecting a ceramic capacitor from this pin to GND.                                                                                                                                                                                                                                                                                                        | Short To<br>GND   |  |

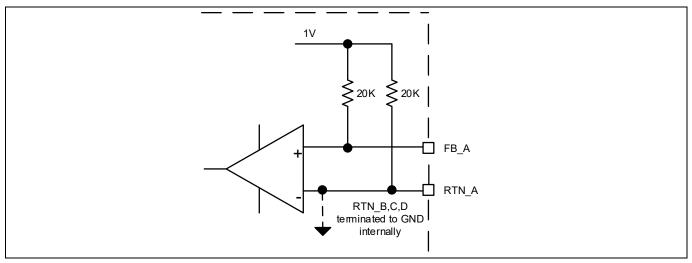

| 40    | RTN_A      | A [I] | Differential feedback return signal for Switcher A. This can be connected remotely to the return location of VOUT_A.                                                                                                                                                                                                                                                                                                     | Short<br>together |  |

| 41    | FB_A       | A [I] | Differential feedback positive signal for Switcher A. Connect directly to VOUT_A for output voltages less than 2.55V. Connect to VOUT_A with a 2:1 resistor divider for output voltages greater than 2.55V.                                                                                                                                                                                                              | Short<br>together |  |

| 42    | EN_A       | D [I] | Switcher A enable input control; external termination required, do not leave floating. LVTTL threshold levels. 'ON' threshold is 2.1V minimum                                                                                                                                                                                                                                                                            | Short To<br>GND   |  |

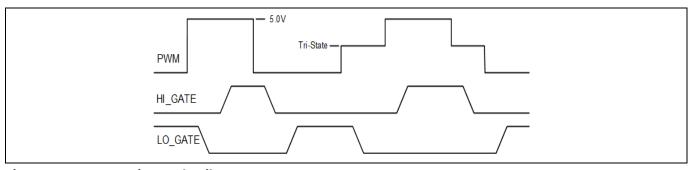

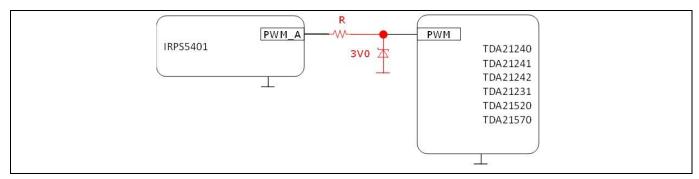

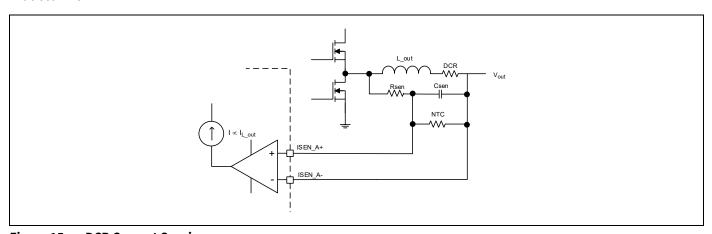

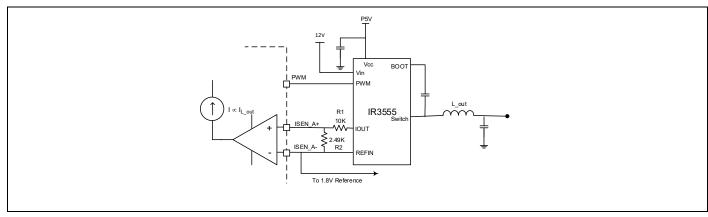

| 43    | PWM_A      | A [O] | PWM signal for Switcher A to be used when Switcher A is configured for use with an external IR MOSFET™ Power Stage. This PWM pin is a 5V PWM. This pin is used to drive a 5V capable external power stage such as an IR355x power stage and is a tri-state or tri-level signal. A resistor and zener clamp must be used when paired with a 3.3V only power stage (see figure 11). Leave floating if this pin is not used | Open              |  |

| 44    | EN_B       | D [I] | Switcher B enable input control; external termination required, do not leave floating. LVTTL threshold levels. 'ON'                                                                                                                                                                                                                                                                                                      | Short To<br>GND   |  |

# Flexible Power Management Unit

### **Pin Function**

| PIN |           |       | Description                                                                                                                                                                                                                                                                                                                                                                        | If not used       |  |

|-----|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| #   | Name      | TYP   |                                                                                                                                                                                                                                                                                                                                                                                    |                   |  |

|     |           |       | threshold is 2.1V minimum                                                                                                                                                                                                                                                                                                                                                          |                   |  |

| 45  | ISEN_A-   | A[I]  | Negative (return) sense point for Switcher A external IOUT sense.                                                                                                                                                                                                                                                                                                                  | Short<br>together |  |

| 46  | ISEN_A+   | A[I]  | Positive sense point for Switcher A external IOUT sense.                                                                                                                                                                                                                                                                                                                           | Short<br>together |  |

| 47  | VDRV      | A [O] | 5V drive voltage used to power the internal MOSFET drivers. Use a $2.2\Omega$ , $2.2uF$ filter from VCC to insure noise from this switching node is not injected into the VCC pin. See the application section. Terminate decoupling cap to GND (pin 57)                                                                                                                           | n/a               |  |

| 48  | VCC       | A [O] | 5V source used by the device to power internal analog and digital control. When VCC is self-generated by the device (from VSUPPLY), do not load this pin with any load other than VDRV. Decouple using a 2.2uF X7R type ceramic capacitor. Terminate decoupling cap to AGND (pin 50)                                                                                               | n/a               |  |

| 49  | VSUPPLY   | A [I] | Input voltage for internal LDO for internally generated VCC                                                                                                                                                                                                                                                                                                                        |                   |  |

| 50  | AGND      |       | Ground reference for the analog and digital control.                                                                                                                                                                                                                                                                                                                               | n/a               |  |

| 51  | EN_C      | D[I]  | Switcher C enable input control; external termination required, do not leave floating. LVTTL threshold levels. 'ON' threshold is 2.1V minimum                                                                                                                                                                                                                                      | Short To<br>GND   |  |

| 52  | SYNC_CLK  | D[I]  | External Synchronization pin. LVTTL threshold levels. 'HIGH' threshold is 2.1V minimum, 'LOW' is 0.8V maximum                                                                                                                                                                                                                                                                      | Short to<br>GND   |  |

| 53  | EN_D      | D [I] | Switcher D enable input control; external termination required, do not leave floating. LVTTL threshold levels. 'ON' threshold is 2.1V minimum                                                                                                                                                                                                                                      | Short to<br>GND   |  |

| 54  | МТР       | A [I] | A resistor placed to ground on this pin selects which of 15 MTP banks of memory are used. By allowing up to 15 MTP memory banks, a user can use up to 15 identical IRPS5401 devices on a single board using just one customer-configuration file. If this pin is above 2V when POR occurs, the device will not load OTP and the I2C address will be 0Ah. Decouple with 0.01uF cap. | n/a               |  |

| 55  | ADDR_PROT |       | Use a resistor on this pin to set the I2C and/or PMBus Address offset for the device If the I2C register R/W protect security function is used and 'PIN' protect is enabled, this pin must be asserted high to disable the R/W protection. Decouple with 0.01uF cap.                                                                                                               | n/a               |  |

| 56  | FB_D      | A [I] | Switcher D feedback input. Connect directly to VOUT_D for output voltages less than 2.55V. Connect to VOUT_D with a 2:1 resistor divider for output voltages greater than 2.55V.                                                                                                                                                                                                   | Open              |  |

| 57  | GND       |       | Ground. The large metal pad on the bottom must be connected to Ground.                                                                                                                                                                                                                                                                                                             | n/a               |  |

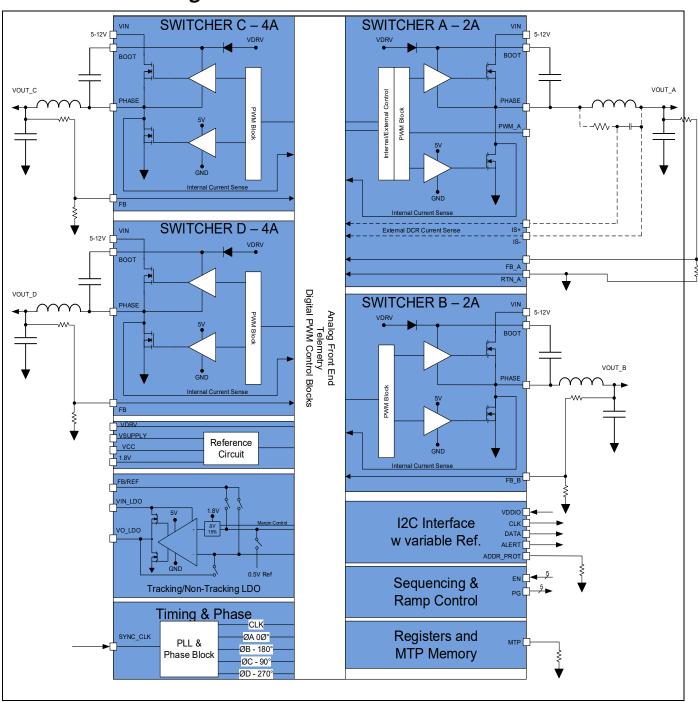

**Block Diagram**

#### **Block Diagram** 5

Figure 4 **IRPS5401 Block Diagram**

#### **Flexible Power Management Unit**

**Absolute Maximum Ratings**

# 6 Absolute Maximum Ratings

Stresses beyond these listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied.

#### Table 5 Voltage Ratings

| Vin [A_B_C_D], VSUPPLY         | -0.3V to 16V               |

|--------------------------------|----------------------------|

| VCC, VDRIVE                    | -0.3V to 6V                |

| VDDIO                          | -0.3 to 5.5V               |

| 1V8                            | -0.3V to 2V                |

| BOOT [A_B_C_D]                 | -0.3V to 22V               |

| BOOT [A_B_C_D] <10ns transient | -0.3V to 24V               |

| SW [A_B_C_D]                   | -0.3V to 16V               |

| SW [A_B_C_D] <10ns transient   | -4V to 18V                 |

| BOOT to SW [A_B_C_D]           | -0.3V to VCC +0.3V (Note2) |

| Input / Output Pins            | -0.3V to VCC +0.3V (Note1) |

| GND to AGND                    | -0.3V to +0.3V             |

#### Table 6 Thermal Information

| Junction to Ambient Thermal Resistance $\Theta_{JA}$        | 13.5°C/W                |

|-------------------------------------------------------------|-------------------------|

| Junction to PCB Thermal Resistance $\Theta_{	extsf{J-PCB}}$ | 3°C/W                   |

| Maximum Storage Temperature Range                           | -55°C To 150°C          |

| Maximum Junction Operating Temperature Range                | -40°C To 125°C (Note 3) |

| Maximum Lead Temperature (Soldering 10s)                    | 300°C                   |

#### Note:

- 1. Voltages referenced to GND unless otherwise specified

- 2. Must not exceed 6V

- 3. Cold temperature performance is verified via correlation using statistical quality control. Not tested in production.

#### **Flexible Power Management Unit**

# **7** Electrical Specifications

#### RECOMMENDED OPERATING CONDITIONS FOR RELIABLE OPERATION WITH MARGIN

#### Table 7

| Recommended Operating Ambient Temperature Range* | -40°C to 85°C                   |

|--------------------------------------------------|---------------------------------|

| VIN [A to D]                                     | 1.2V to 14V (with external VCC) |

| VSUPPLY (for Internal VCC)                       | 6V to 14V                       |

| External VCC and VDRIVE Voltage Range            | 4.5V to 5.5V                    |

| VDDIO                                            | 3.3V                            |

| SWA and SWB Output Load                          | 0A to 2A                        |

| SWC and SWD Output Load                          | 0A to 4A                        |

| Combined SWC+SWD Output Load                     | 0A to 8A                        |

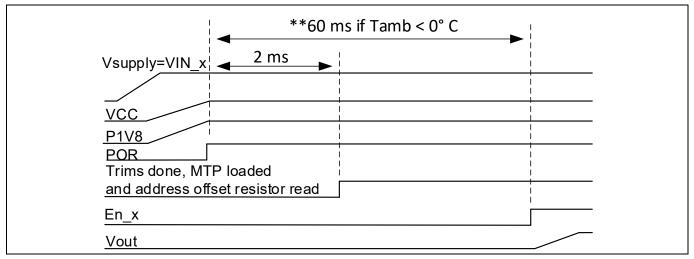

Note: The electrical characteristics table lists the spread of values verified within the recommended

operating conditions. Typical values represent the median values, which are related to 25°C.

Note: \*For operation below 0°C, a delay of 60ms between applying power and output ramp up is

required. See more details in 9.3

**Table 8 Electrical Characteristics**

| Parameter                   | Symbol            | Conditions                                                                                                         | Min. | Тур. | Max. | Unit |

|-----------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| UVLO Turn-on<br>Threshold   |                   |                                                                                                                    |      | 4.2  | 4.5  | V    |

| UVLO Turn-off<br>Threshold  |                   |                                                                                                                    | 3.6  | 3.9  |      | V    |

| Supply Current              | I <sub>vcc</sub>  | All outputs disabled (low power disabled)                                                                          |      | 40   | 45   | mA   |

| Supply Current              | Ivcc              | All outputs disabled (low power enabled)                                                                           |      | 25   | 30   | mA   |

| Supply Current              | I <sub>vcc</sub>  | SLEEP# = low<br>(Sleep Mode Enabled)                                                                               |      | 10   | 25   | uA   |

| VDRV                        |                   |                                                                                                                    |      |      |      |      |

| UVLO Turn-on<br>Threshold   |                   |                                                                                                                    |      | 4.2  | 4.5  | V    |

| UVLO Turn-off<br>Threshold  |                   |                                                                                                                    | 3.6  | 3.9  |      | V    |

| Supply Current              | I <sub>vdrv</sub> | All outputs Enabled, fsw<br>=800kHz                                                                                |      | 15   |      | mA   |

| Internal Supply VCC<br>LDO  |                   |                                                                                                                    |      |      |      |      |

| Input Voltage               |                   |                                                                                                                    | 6    | -    | 14   | V    |

| Output Voltage (on Vcc pin) | V <sub>cc</sub>   | Ta=25°C, 6.0V <vsupply<14v, 0ma<lout<50ma<="" td=""><td>4.6</td><td>4.85</td><td>5.1</td><td>V</td></vsupply<14v,> | 4.6  | 4.85 | 5.1  | V    |

### Flexible Power Management Unit

| Parameter                                                         | Symbol             | Conditions                          | Min.  | Тур. | Max.  | Unit |

|-------------------------------------------------------------------|--------------------|-------------------------------------|-------|------|-------|------|

| Output Current                                                    | loutmax            |                                     |       | -    | 75    | mA   |

|                                                                   |                    |                                     |       |      |       |      |

| VDDIO                                                             |                    |                                     |       |      |       |      |

| Input Voltage <sup>1</sup>                                        |                    | I2C termination voltage             | 1.62  | -    | 5.5   | V    |

| Input High Voltage                                                |                    | % of VDDIO                          | 60    | -    | _     | %    |

| Input Low Voltage                                                 |                    | % of VDDIO                          | -     | -    | 30    | %    |

| Input Leakage                                                     |                    | Vpad = 0 to 5.5V                    | -1    | -    | 1     | μΑ   |

| Reference Voltage<br>(DAC) [A to D]                               |                    |                                     |       |      |       |      |

| Range                                                             |                    |                                     | 0.25  |      | 2.55  | V    |

| Resolution                                                        |                    |                                     |       | 5    |       | mV   |

| Accuracy<br>(0°C to 85°C junction<br>temperature)                 |                    | VID = 1.0 to 2.55V                  | -0.8  | -    | 0.8   | %    |

|                                                                   |                    | VID = 0.5V to 0.995V                | -8    | -    | 8     | mV   |

|                                                                   |                    | VID = 0.25V to 0.495V               | -10   | -    | 10    | mV   |

| Accuracy <sup>1</sup><br>(-40°C to 125°C junction<br>temperature) |                    | VID = 1.0 to 2.55V                  | -1.5  | -    | 1.5   | %    |

|                                                                   |                    | VID = 0.5V to 0.995V                | -15   | -    | 15    | mV   |

|                                                                   |                    | VID = 0.25V to 0.495V               | -20   | -    | 20    | m۷   |

| Oscillator & PWM<br>Generator                                     |                    |                                     |       |      |       |      |

| Internal Oscillator¹                                              |                    |                                     | -     | 48   | -     | MHz  |

| Frequency Accuracy                                                |                    | 0°C to 85°C junction<br>temperature | -3    | -    | 3     | %    |

| Frequency Accuracy                                                |                    | -40°C to 125°C                      | -6.25 |      | +6.25 | %    |

| PWM Frequency Range <sup>1</sup>                                  |                    |                                     | 200   | -    | 2000  | kHz  |

| PWM Resolution <sup>1</sup>                                       |                    |                                     | -     | 2.6  | -     | ns   |

| Digital Inputs – TTL                                              | ADDR_PROT,<br>EN_x |                                     |       |      |       |      |

| Input High Voltage                                                |                    |                                     | 2.1   | -    | -     | V    |

| Input Low Voltage                                                 |                    |                                     | -     | -    | 0.8   | V    |

| Input Leakage                                                     |                    | Vpad = 0 to 5.5V                    | -1    | -    | 1     | μΑ   |

| Digital Inputs – TTL                                              | SLEEP#             |                                     |       |      |       |      |

| Input High Voltage                                                |                    |                                     | 2.1   | -    | -     | V    |

| Input Low Voltage                                                 |                    |                                     | -     | -    | 0.8   | V    |

| Input Leakage                                                     |                    | Vpad = 0 to 5.5V                    | -10   | -    | 10    | μΑ   |

| External Sync                                                     | SYNC               |                                     |       |      |       |      |

| Frequency range                                                   |                    |                                     | 200   |      | 1000  | kHz  |

| Voltage Range                                                     |                    |                                     | 0     |      | 5     | Vdc  |

| Input High voltage                                                |                    |                                     | 2.1   |      |       | V    |

### Flexible Power Management Unit

| Parameter                                        | Symbol                | Conditions            | Min.          | Тур. | Max.  | Unit |

|--------------------------------------------------|-----------------------|-----------------------|---------------|------|-------|------|

| Input Low Voltage                                |                       |                       |               |      | 0.8   | V    |

| Input Leakage current                            |                       | Vpad = 0 to 5.5V      |               |      | ±5    | μΑ   |

| Sync pin capacitance                             |                       | Vpad = 0 to 5.5V      |               |      | 10    | pF   |

| Synchronization Range (From OTP setting)         |                       | 0°C to 85°C           | -6.25         |      | +6.25 | %    |

| Synchronization Range (From OTP setting)         |                       | -40°C to 125°C        | -3            |      | +3    | %    |

| Sync signal Duty Cycle                           |                       |                       | 45            | 50   | 55    | %    |

| Remote Voltage Sense Inputs                      | FB [A to D],<br>RTN_A |                       |               |      |       |      |

| FB_x Input Current                               |                       | VOUT = 0.25V to 2.55V | -35           | -    | 90    | μΑ   |

| RTN_A Input Current                              |                       |                       | -             | -50  | -     | μΑ   |

| Differential Input<br>Voltage Range <sup>1</sup> |                       | RTN_A = ±100mV        | 0             |      | 2.55  | V    |

| RTN_A Input CM<br>Voltage¹                       |                       |                       | -100          | -    | 100   | mV   |

| Remote Current Sense                             | ISEN_A+/ISEN_A        |                       |               |      |       |      |

| Inputs                                           | -                     |                       |               |      |       |      |

| Common Mode Voltage<br>Range <sup>1</sup>        |                       |                       | -0.1          | -    | Vcc-1 | V    |

| Differential Voltage<br>Range¹                   |                       |                       | -10           | -    | 60    | mV   |

| Analog Address/Level Inputs                      | ADDR_PROT, MTP        |                       |               |      |       |      |

| Output Current <sup>1</sup>                      |                       | Vpad = 0 to 1.2V      | 96            | 100  | 104   | μΑ   |

| Open-Drain Outputs                               | PG_x, DATA,<br>ALERT# |                       |               |      |       |      |

| Output Low Voltage                               |                       | 4mA                   | -             | -    | 0.3   | V    |

| Output Leakage                                   |                       | Vpad = 0 to 5.5V      | -             | -    | ±5    | μΑ   |

| PWM I/O                                          | PWM_A                 |                       |               |      |       |      |

| Output Low Voltage                               |                       | I = -4mA              | -             | -    | 0.4   | ٧    |

| Output High Voltage                              |                       | I = +4mA              | VCC-<br>0.45V | -    | -     | V    |

| Tri-State Leakage                                |                       | Vpad = 0 to Vcc       | -             | -    | ±1    | μΑ   |

| I2C/PMBus                                        |                       |                       |               |      |       |      |

| Bus Speed <sup>1</sup>                           |                       | Normal                | -             | 100  | -     | kHz  |

|                                                  |                       | Fast                  | -             | 400  | -     | kHz  |

|                                                  |                       | Maximum               | _             | 1000 | -     | kHz  |

### Flexible Power Management Unit

| Telemetry Reporting -<br>Switching Outputs [A<br>to D]        |                                                                                                               |                                                                                  |                         |                                                         |      |     |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------|------|-----|

| Iout, Iin, Vin and<br>Temperature Filter<br>Rate <sup>1</sup> |                                                                                                               | Selectable<br>(Selected Frequency applies<br>to all parameters for all<br>loops) | -                       | 0.97,<br>1.9,<br>3.8,<br>7.7,<br>15.5,<br>31,63,<br>126 | -    | Hz  |

| lout, lin, Vin,<br>Temperature Update<br>Rate <sup>1</sup>    |                                                                                                               |                                                                                  | -                       | 25                                                      | -    | kHz |

| Vin Reporting Range <sup>1</sup>                              |                                                                                                               |                                                                                  | 0                       | -                                                       | 17.5 | ٧   |

| Vin Reporting Accuracy (-2 to 2%)                             |                                                                                                               | VIN = 12V                                                                        | -2                      | -                                                       | 2    | %   |

| Vin Reporting Accuracy                                        |                                                                                                               | VIN = 5V                                                                         | -5                      | -                                                       | 5    | %   |

| Vin Reporting<br>Resolution <sup>1</sup>                      |                                                                                                               |                                                                                  | -                       | 31.25                                                   | -    | mV  |

| Vout Reporting Range <sup>1</sup>                             |                                                                                                               | With 2:1 scaling                                                                 | -                       | -                                                       | 5.1  | V   |

| Vout Reporting<br>Accuracy <sup>1</sup>                       |                                                                                                               | READ_VOUT reports DAC setting                                                    |                         | 0.5                                                     |      | %   |

| Vout Reporting<br>Resolution <sup>1</sup>                     | User Selectable per output through VOUT_MODE command. Actual resolution is 5mV/10mV depending on VOUT_SCALING | -                                                                                | 0.244<br>1.953<br>3.906 | -                                                       | mV   |     |

| Iout Reporting Gain<br>Accuracy¹                              | gain_error                                                                                                    | Iread=Iout(1±gain_error)±I_o<br>s*full scale                                     | -5                      |                                                         | 5    | %   |

| Iout Reporting Offset<br>Accuracy¹                            | I_os                                                                                                          | full Scale = 2A for A/B<br>and 4A for C/D                                        | -2.5                    |                                                         | 2.5  | %   |

| Iout Reporting<br>Resolution <sup>1</sup>                     |                                                                                                               |                                                                                  | -                       | 15.625                                                  | -    | mA  |

| Iin Reporting<br>Resolution <sup>1</sup>                      |                                                                                                               |                                                                                  | -                       | 7.8125                                                  | -    | mA  |

| P_in Reporting<br>Resolution <sup>1</sup>                     |                                                                                                               |                                                                                  | -                       | 31.25                                                   | -    | mW  |

| P_out Reporting<br>Resolution <sup>1</sup>                    |                                                                                                               |                                                                                  | -                       | 31.25                                                   | -    | mW  |

| Temperature Reporting<br>Resolution <sup>1</sup>              |                                                                                                               |                                                                                  |                         | 0.25                                                    |      | °C  |

| Temperature Reporting                                         |                                                                                                               |                                                                                  | -2                      |                                                         | 2    | %   |

### Flexible Power Management Unit

| Accuracy <sup>1</sup>                                                                  |                                                          |     |                         |      |    |

|----------------------------------------------------------------------------------------|----------------------------------------------------------|-----|-------------------------|------|----|

| Telemetry Reporting -<br>Switching Output A<br>with External IR<br>MOSFET™ Power Stage |                                                          |     |                         |      |    |

| Iout Reporting<br>Resolution <sup>1</sup>                                              |                                                          | -   | 125                     | -    | mA |

| Iout Reporting<br>Accuracy <sup>1</sup>                                                | At 100% full load. Assumes ± 5% accurate external source | -6  |                         | 6    | %  |

| lin Reporting<br>Resolution <sup>1</sup>                                               |                                                          | -   | 62.5                    | -    | mA |

| P_in Reporting<br>Resolution <sup>1</sup>                                              |                                                          | -   | 250                     | -    | mW |

| P_out Reporting<br>Resolution¹                                                         |                                                          | -   | 250                     | -    | mW |

| Telemetry Reporting -<br>LDO                                                           |                                                          |     |                         |      |    |

| Vin Reporting Range <sup>1</sup>                                                       |                                                          | 0   | -                       | 8    | ٧  |

| Vin Reporting<br>Resolution <sup>1</sup>                                               |                                                          | -   | 7.812                   | -    | mV |

| Vin Reporting Accuracy                                                                 |                                                          | -2  | -                       | 2    | %  |

| Vout Reporting Range <sup>1</sup>                                                      | Vout is measured                                         | 0   | -                       | 4    | ٧  |

| Vout Reporting<br>Resolution <sup>1</sup>                                              | User Selectable through VOUT_MODE command.               | -   | 0.244<br>1.953<br>3.906 | -    | mV |

| Vout Reporting Accuracy                                                                |                                                          | -2  | -                       | 2    | %  |

| Iout Reporting Range <sup>1</sup>                                                      |                                                          | 0   | -                       | 0.72 | Α  |

| Iout Reporting<br>Resolution <sup>1</sup>                                              |                                                          | -   | 0.976                   | -    | mA |

| Iout Reporting Accuracy <sup>1</sup>                                                   | At 500mA                                                 | -10 |                         | 10   | %  |

| P_in Reporting<br>Resolution <sup>1</sup>                                              |                                                          | -   | 15.625                  | -    | mW |

| P_out Reporting<br>Resolution¹                                                         |                                                          | -   | 15.625                  | -    | mW |

## Flexible Power Management Unit

| Fault Protection -                                                                       |                                        |                 |       |       | T   |

|------------------------------------------------------------------------------------------|----------------------------------------|-----------------|-------|-------|-----|

| Switchers [A to D]                                                                       |                                        |                 |       |       |     |

| OVP Threshold During<br>Start-up (until output<br>reaches 1V)                            |                                        | 1.2             | 1.35  | 1.5   | V   |

| OVP Threshold During<br>Start-up (until output<br>reaches 1V)                            |                                        | 2.4             | 2.75  | 3.0   | V   |

| OVP and UVP Operating Threshold¹ Range:                                                  | Relative to VID,                       | 1:1 scaling 50  | -     | 400   | mV  |

| Resolution:                                                                              |                                        | -               | 50    | -     | mV  |

| OVP and UVP Operating Threshold <sup>1</sup> Range:                                      | Relative to VID,                       | 2:1 scaling 100 |       | 800   | mV  |

| Resolution:                                                                              |                                        | -               | 100   | -     | mV  |

| OVP and UVP delay <sup>1</sup>                                                           | After exceeding                        | threshold -     | -     | 150   | ns  |

| OVP and UVP threshold<br>Tolerance <sup>1</sup>                                          | For thresholds >                       | · 200mV -20     |       | 20    | %   |

| OC WARN and FAULT<br>Range <sup>2</sup>                                                  | Switcher A and                         | 0               | -     | 4     | Α   |

| OC WARN and FAULT<br>Range <sup>2</sup>                                                  | Switcher C and                         | 0               | -     | 8     | A   |

| OC WARN and FAULT<br>Range <sup>2</sup>                                                  | Switcher C in C+                       | D mode 0        | -     | 15.97 | А   |

| OC WARN and FAULT Resolution                                                             |                                        | -               | 31.25 | -     | mA  |

| OC FAULT Threshold<br>Tolerance<br>(0°C to 85°C junction<br>temperature)                 | At 3A for A and E<br>D, at 12A for C+E | · 1 -10         |       | +10   | %   |

| OC FAULT Threshold<br>Tolerance <sup>1</sup><br>(-40°C to 125°C junction<br>temperature) | At 3A for A and E<br>D, at 12A for C+E | - 20            |       | +20   | %   |

| OT WARN and FAULT<br>Range <sup>1</sup>                                                  |                                        | 0               |       | 255   | °C  |

| OT WARN and FAULT<br>Resolution <sup>1</sup>                                             |                                        | -               | 1     | -     | °C  |

| Fault Protection -<br>Switcher A with<br>External IR MOSFET™<br>Power Stage              |                                        |                 |       |       |     |

| OC WARN and FAULT<br>Range <sup>2</sup>                                                  |                                        | 0               | -     | 255   | А   |

| OC WARN and FAULT<br>Resolution                                                          |                                        | -               | 0.25  | -     | А   |

| External ISENSE Filter<br>Bandwidth                                                      |                                        |                 | 62    | -     | kHz |

### Flexible Power Management Unit

| Fault Protection - LDO                               |                       |                                                                                                |     |       |      |    |

|------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------|-----|-------|------|----|

| OV FAULT                                             |                       | Read Only, % of VOUT as set in Ido_target_register - Non tracking OR measured VIN/2 - Tracking | -   | 125   | -    | %  |

| OV WARN                                              |                       |                                                                                                | _   | 112.5 | -    | %  |

| UV FAULT                                             |                       |                                                                                                | -   | 75    | -    | %  |

| UV WARN                                              |                       |                                                                                                | -   | 87.5  | -    | %  |

| OC FAULT                                             |                       | Read Only                                                                                      | -   | 0.72  | -    | Α  |

| OC WARN Range                                        |                       |                                                                                                | 0   | -     | 0.72 | Α  |

| OC WARN Resolution                                   |                       |                                                                                                | -   | 3.9   | -    | mA |

| MOSFET - Switcher A and B                            |                       |                                                                                                |     |       |      |    |

| High Side Switch<br>Resistance                       |                       | Tj = 20°C, BOOT-PHASE = 5V                                                                     | -   | 150   | -    | mΩ |

| Low Side Switch<br>Resistance                        |                       | Tj = 20°C, VDRV = 5V                                                                           | -   | 45    | -    | mΩ |

| MOSFET - Switcher C and D                            |                       |                                                                                                |     |       |      |    |

| High Side Switch<br>Resistance                       |                       | Tj = 20°C, BOOT-PHASE = 5V                                                                     | -   | 85    | -    | mΩ |

| Low Side Switch<br>Resistance                        |                       | Tj = 20°C, VDRV = 5V                                                                           | -   | 25    | -    | mΩ |

| LDO                                                  |                       |                                                                                                |     |       |      |    |

| Input Voltage                                        | $V_{in\_ldo}$         |                                                                                                | 1.2 | -     | 5.5  | ٧  |

| Output Voltage                                       | $V_{out\_ldo}$        |                                                                                                | 0.5 | -     | 3.6  | ٧  |

| Dropout Voltage                                      | $V_{dropout\_ldo}$    | Iout=0.5A, Tj=125°C                                                                            | -   | -     | 0.5  | V  |

| Output Current                                       | $I_{\text{out\_ldo}}$ |                                                                                                | -   | -     | 0.5  | Α  |

| Reference Voltage                                    | $V_{ref\_ldo}$        | Ta = 25°C                                                                                      | 490 | 500   | 510  | mV |

|                                                      |                       | -40°C <tj 85°c<="" <="" td=""><td>485</td><td>500</td><td>515</td><td>mV</td></tj>             | 485 | 500   | 515  | mV |

| Timing Information                                   |                       |                                                                                                |     |       |      |    |

| Automatic<br>Configuration from<br>MTP <sup>1</sup>  |                       | Time from POR to end of configuration loaded from NVM to working registers                     | -   | 1     | -    | ms |

| Isense AMP Automatic Trim Time¹                      |                       |                                                                                                | -   | 1     | -    | ms |

| Delay from Enable high<br>to ramp start <sup>1</sup> |                       | Low power mode disabled                                                                        | -   | 3     | -    | μs |

| Delay from Enable high<br>to ramp start <sup>1</sup> |                       | Low power mode enabled                                                                         | -   | 600   | -    | μs |

<sup>1.</sup> Verified by design

<sup>2.</sup> Actual OC limit (MAX sustained load the VR can handle) is a function of inductor ISAT and system thermal solution. SW A and B limited to 2A max DC load. SW C and D limited to 4A max DC load

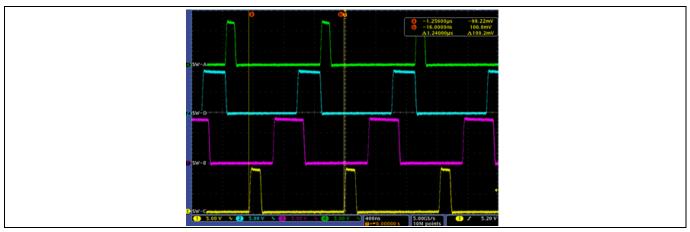

**Typical Application Diagrams**

#### **Typical Application Diagrams** 8

IRPS5401 in 5 output configuration with Vcc from internal LDO Figure 5

#### **Flexible Power Management Unit**

#### **Typical Application Diagrams**

Figure 6 IRPS5401 using external IR MOSFET™ Power Stage for high Current Output

### **Flexible Power Management Unit**

### **Typical Application Diagrams**

Figure 7 IRPS5401 using Switcher C and Switcher D in parallel for higher current applications

#### **Flexible Power Management Unit**

#### **Typical Application Diagrams**

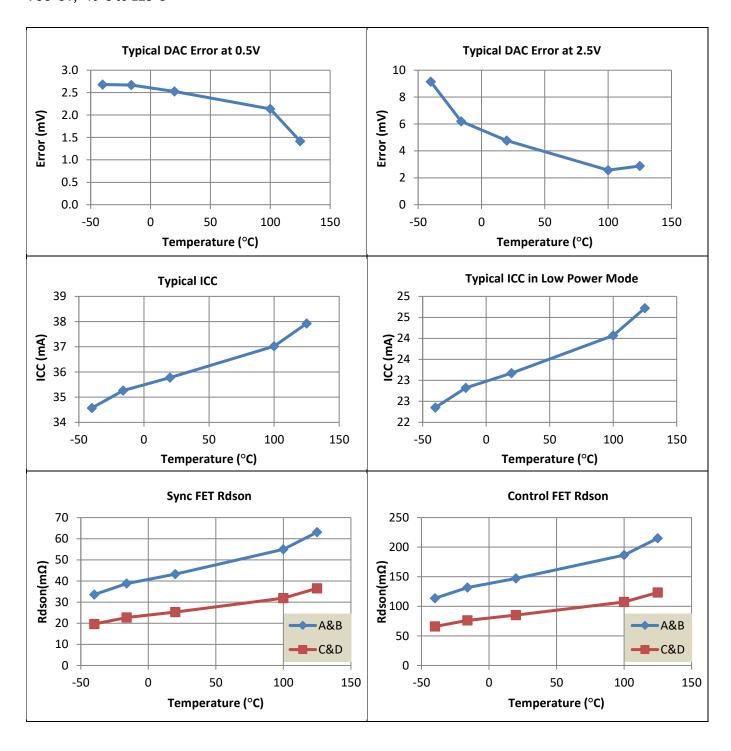

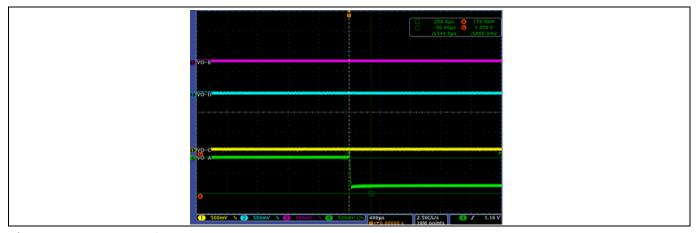

#### **TYPICAL OPERATING CHARACTERISTICS**

VCC=5V, -40°C to 125°C

#### **Flexible Power Management Unit**

### 9 Description

The IRPS5401 is a digitally configurable flexible power management unit, with an I2C/PMBus interface. It can support up to 5 rails, with 4 independent switching regulators and one linear regulator.

The switching frequency is programmable from 200 kHz to 2MHz and provides the capability of optimizing the design in terms of size and performance.

The IRPS5401 switchers provide precisely regulated output voltages programmable from 0.25V to 2.55V without a resistor divider and up to 5.1V with a resistor divider.

The IRPS5401 can operate with an internal bias supply (LDO), typically 5.0V. This allows operation with a single supply by connecting the input of the LDO (VSUPPLY) to the bus voltage (Vin\_x). A 1uF capacitor should be used at the VSUPPLY pin for decoupling purposes. The output of this LDO is brought out at the Vcc pin and must be bypassed to the analog ground (pin 50) with a 1.0uF decoupling capacitor. An additional voltage, VDRV, required by the internal driver circuitry is derived by using a 2 ohm-1uF filter from the Vcc pin to the VDRV pin. Note that the 1uF at the VDRV pin must be bypassed to the system power ground (pin 57). The Vcc pin may also be connected to the VSUPPLY pin, and an external Vcc supply between 4.5V and 5.5V may be used, allowing for an extended operating bus voltage (Vin\_x) range from 1.2V to 14V.

The device utilizes the on-resistance of the low side MOSFET (synchronous MOSFET) as the current sense element. This method enhances the converter's efficiency and reduces cost by eliminating the need for external current sense resistors.

### 9.1 One-time Programmable (OTP) Memory

The IRPS5401 has 64K of OTP non-volatile memory. The OTP design is based on a patented split-channel non-volatile anti-fuse memory cell. The OTP memory has a data retention rating of 20 years and an operating temperature range of -40°C to 150°C (-55°C to 150°C storage rating)

This memory space is divided up into 26 OTP segments that can be programmed 1 time. The memory space is therefore referred to as Multiple-times Programmable (MTP). This allows the user to; a) change the configuration registers and re-program the MTP up to 26 times or b) save up to 15 configuration files during initial programing and use the MTP pin to choose which file to load at start up. If option b is used, the remaining unused MTP segments are available for the user to make additional changes to the configuration file and save to MTP using the PowIRCenter GUI device programmer utility.

### 9.2 MTP pin (pin 54)

The table below shows the MTP segment that will be selected with a given resistor value connected to the MTP pin. The resistor must be connected to the AGND pin and bypassed with a 10nF X7R type multi-layer ceramic capacitor.

#### **Flexible Power Management Unit**

#### **Description**

#### Table 9

| MTP pin Resistor | MTP Segment selected |

|------------------|----------------------|

| *0.845kΩ         | +0                   |

| *1.30kΩ          | +1                   |

| *1.78kΩ          | +2                   |

| 2.32kΩ           | +3                   |

| 2.87kΩ           | +4                   |

| 3.48kΩ           | +5                   |

| 4.12kΩ           | +6                   |

| 4.75kΩ           | +7                   |

| 5.49kΩ           | +8                   |

| 6.19kΩ           | +9                   |

| 6.98kΩ           | +10                  |

| 7.87kΩ           | +11                  |

| 8.87kΩ           | +12                  |

| 10.00kΩ          | +13                  |

| 11.00kΩ          | +14                  |

Note: Do not use these values for applications with ambient temperatures <0°C

Note:

The number of segments that the user chooses to program with multiple configuration files is set by a configuration register called max\_prog. The max\_prog register value needs to be set to the number of configuration files that will be programmed. For example, if the user programs segments +0, +1, and +2, then the max\_prog register needs to have a value of 3. For applications with junction temperatures below  $0^{\circ}$ C, segments +0, +1, and +2 are not available.

### 9.3 Device Power-up and Initialization

During the power-up sequence, when VIN is brought up, the internal LDO converts it to a regulated 5.0V at VCC. There is another LDO which further converts this down to 1.8V to supply the internal digital circuitry. An undervoltage lockout circuit monitors the voltage of the VCC pin and the P1V8 pin, and holds the POR low until these voltages exceed their thresholds and the internal 48 MHz oscillator is stable. When the device comes out of reset, it initializes an MTP load cycle, where the contents of the MTP are loaded into the working registers. Once the registers are loaded from MTP, the designer can use I2C/PMBus to re-configure the registers to suit the specific VR design requirements if desired, irrespective of the status of the enable pins.

#### **Flexible Power Management Unit**