# CHT-ATLAS

CISSOID

Version: 3.5 5-Mar-15 (Last Modification Date)

# **Dual Channel Power Transistor Driver**

### **General description**

CHT-ATLAS is a high-temperature, high reliability power transistor driver integrated circuit specifically designed to drive widebandgap power transistors, in particular Gallium Nitride (GaN) and Silicon Carbide (SiC) devices including normally-On and normally-Off JFETs, MOSFETs and BJTs. It is also used with standard silicon MOSFETs and IGBTs in standard temperature applications (e.g. 125°C) where it brings an increase in reliability and lifetime by an order of magnitude compared to traditional solutions. The circuit features 2 independent push-pull channels capable of sourcing/sinking 2A each. When configured together to drive a single power switch, the combination of the 2 distinct channels allows driving of specific devices that require for instance a dynamic pulse of current in combination with a continuous current in order to be properly turned-on. The circuit includes a soft-shut-down capability that slowly shuts down the power transistor in case of fault.

### Features

- Operating junction temperature: from -55°C to +225°C

- Gate drive supply voltage: 5 to 30V

- 2 channels

- Separate logic level control inputs

- Output current: up to 2 x ±2A @ 225°C

- Propagation delay: 40 ns typ

- Rise time / fall time: 10ns Typ. (with C<sub>Load</sub>=1nF and V<sub>CC</sub>=15V)

- Soft-shut down

- High Impedance mode

- Capable to drive normally-On and normally-Off devices

- Validated at 225°C for 1000 hours (and still on-going)

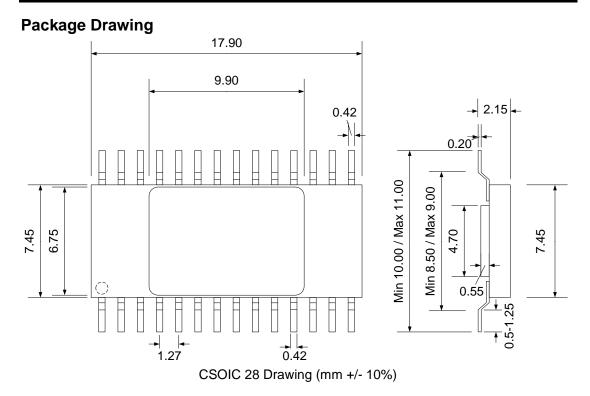

- Package: CSOIC28

### **Applications**

- Intelligent Power Modules (IPM)

- Power conversion, power generation and actuator controls in aeronautics

- Solar inverters

- Motor drives, battery chargers and DC-DC converters in EV / HEV

- Power conversion and motor drive in railway

- Switched mode power supplies (SMPS)

- Wind turbine power converters

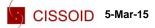

## **Functional Block Diagram**

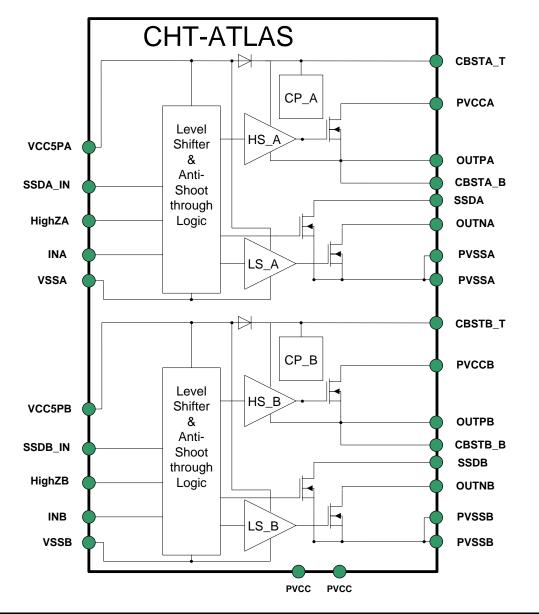

### Package Configuration and Pin Description:

| Pin # | Pin Name          | Pin Description                                                                                                                                                                                                                                                              |

|-------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SSDA              | Soft Shutdown output pin of channel A.                                                                                                                                                                                                                                       |

|       |                   | When SSDA_IN pin is low, this node is pulled down to PVSSA.                                                                                                                                                                                                                  |

| 2     | PVCC              | To be connected to PVCCA and PVCCB                                                                                                                                                                                                                                           |

| 3     | INA               | Schmitt triggered input of channel A driver.                                                                                                                                                                                                                                 |

| -     |                   | 5V CMOS input with respect to VSS.                                                                                                                                                                                                                                           |

| 4     | HIGHZA            | Schmitt triggered input of the tri-state control<br>signal for channel A driver. 5V CMOS input<br>with respect to VSSA.<br>When driven low, sink, source and SSDA<br>output transistors are turned off (see ATLAS<br>Logic Table). Channel A output is in high<br>impedance. |

| 5     | SSDA_IN           | Schmitt triggered input controlling the soft<br>shut-down transistor for the channel A (see<br>ATLAS Logic Table)                                                                                                                                                            |

| 6     | VCC5PA<br>(input) | 5V positive power supply with respect to VSSA. To be bypassed to VSSA by a 1µF capacitor.                                                                                                                                                                                    |

| 7     | VSSA              | Analogue negative power supply for channel A                                                                                                                                                                                                                                 |

| 8     | VSSB              | Analogue negative power supply for channel B                                                                                                                                                                                                                                 |

| 9     | VCC5PB            | 5V positive power supply with respect to                                                                                                                                                                                                                                     |

|       | (input)           | VSSB. To be bypassed to VSSB by a 1µF capacitor.                                                                                                                                                                                                                             |

| 10    | SSDB_IN           | Schmitt triggered input controlling the soft<br>shut-down transistor for the channel B (see<br>ATLAS Logic Table)                                                                                                                                                            |

| 11    | HIGHZB            | Schmitt triggered input of the tri-state control<br>signal for Channel B driver. 5V CMOS input<br>with respect to VSSB.<br>When driven low, both sink and source<br>output transistors are turned off. Channel B<br>output is in high impedance.                             |

| 12    | INB               | Schmitt triggered input of Channel B driver.<br>5V CMOS input with respect to VSSB.                                                                                                                                                                                          |

| 13    | PVCC              | To be connected to PVCCA and PVCCB                                                                                                                                                                                                                                           |

| 14    | SSDB              | Soft Shutdown output pin of channel B.<br>When SSDB_IN pin is low, this node is<br>internally pulled down to PVSSB.                                                                                                                                                          |

| 15    | CBSTB_T           | Connection for the top plate of the bootstrap capacitor for channel B                                                                                                                                                                                                        |

| 16    | CBSTB_B           | Connection for the bottom plate of the boot-<br>strap capacitor for channel B                                                                                                                                                                                                |

| 17    | OUTPB             | Channel B sourcing output<br>(Isource_max=2A)                                                                                                                                                                                                                                |

| 18    | OUTNB             | Channel B sinking output (Isinking_max=2A)                                                                                                                                                                                                                                   |

| 19    | PVCCB             | Positive power supply of channel B driver.                                                                                                                                                                                                                                   |

| 20    | PVSSB1            | Negative power supply for channel B (First Pin)                                                                                                                                                                                                                              |

| 21    | PVSSB2            | Negative power supply for channel B (Second Pin <sup>1</sup> )                                                                                                                                                                                                               |

| 22    | PVSSA2            | Negative Power supply for channel A (Second Pin <sup>2</sup> )                                                                                                                                                                                                               |

| 23    | PVSSA1            | Negative power supply for channel A (First Pin)                                                                                                                                                                                                                              |

| 24    | PVCCA             | Positive power supply for channel A.                                                                                                                                                                                                                                         |

| 25    | OUTNA             | Channel A sinking output (Isinking_max=2A)                                                                                                                                                                                                                                   |

| 26    | OUTPA             | Channel A sourcing output<br>(Isource_max=2A)                                                                                                                                                                                                                                |

| 27    | CBSTA_B           | Connection for the bottom plate of the boot-<br>strap capacitor for channel A                                                                                                                                                                                                |

| 28    | CBSTA_T           | Connection for the top plate of the bootstrap capacitor for channel A                                                                                                                                                                                                        |

<sup>&</sup>lt;sup>1</sup>To minimize parasitic inductors and ringing, both PVSSB1 and PVSSB2 must be connected to the negative power supply with minimum parasitic inductors <sup>2</sup> To minimize parasitic inductors and ringing, both PVSSA1 and PVSSA2 must be connected to the negative power

supply with minimum parasitic inductors

### Logic Table

|        | Inputs               |           |          | Outputs  |         |

|--------|----------------------|-----------|----------|----------|---------|

| INA(B) | SSDA_IN<br>(SSDB_IN) | HIGHZA(B) | OUTPA(B) | OUTNA(B) | SSDA(B) |

| 0      | 1                    | 1         | highZ    | PVSSA    | highZ   |

| 1      | 1                    | 1         | PVCCA    | highZ    | highZ   |

| Х      | 0                    | 1         | highZ    | highZ    | PVSSA   |

| Х      | Х                    | 0         | highZ    | highZ    | highZ   |

In normal operation pins HIGHZA/B and pins SSDA/B\_IN are set to logic-1 (VCC5PA/B=5V). Applying logic-0 (0V) to pin INA/B turns the low-side driver on, pulling pin OUTA/B down to PVSSA/B. OUTPA/B is in high-impedance state. Applying logic-1 (5V) to pin INA/B, pin OUTNA/B is set to high-impedance state while the high-side driver is turned on pulling OUTPA/B to PVCCA/B.

Maintaining the device enabled (HIGHZA/B set to logic-1) the soft-shutdown is activated by setting pin SSDA/B\_IN to logic-0. Both high-side and low-side drivers are turned off setting pints OUTPA/B and OUTNA/B to high impedance state. SSDA/B pin is pulled down to PVSSA/B. The logic level at pin INA/B does not matter.

The device is disabled when pin HIGHZA/B is set to logic-0, whatever the logic level at the other control signals.

Absolute Maximum Ratings These ratings are considered individually (not in combination). If not specified, voltages are related to VSSA for channel A and to VSSB for channel B. VSSA and VSSB must be at the same potential.

Operating Conditions Supply Voltage VCC5P to VSS Supply Voltage PVCC to PVSS Junction temperature

4.75V to 5.25V 5V to 30V -55°C to +225°C

| Supply Voltage PVCCA/B              | -0.5 to 35V        |

|-------------------------------------|--------------------|

| to PVSSA/B                          |                    |

| Supply Voltage                      | -0.5 to 5.5V       |

| VCC5PA/B to VSSA/B                  |                    |

| Voltage on IN, HIGHZ,               | -0.5 to VCC5P+0.5V |

| SSD_IN to VSS                       |                    |

| Voltage on CBST_T to                | VCC5P-0.5 to       |

| PVSS                                | PVCC+5.5           |

| Driver Output voltage               | PVSS-0.5 to        |

| (OUT, CBST_B)                       | PVCC+5.5           |

| Junction temperature T <sub>j</sub> | 250°C              |

### **ESD** Rating (expected) Human Body Model

1.5kV

Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Frequent or extended exposure to absolute maximum rating conditions or above may affect device reliability.

### **Electrical Characteristics**

Unless otherwise stated: (VCC-VSS)=5V, (PVCC-PVSS)=15V,  $\underline{T_j=25^{\circ}C}$ . Bold underlined values indicate values over the whole temperature range (-55°C < T j < +225°C).

| Parameter                                                 | Condition                                                  | Min         | Тур  | Max         | Units |

|-----------------------------------------------------------|------------------------------------------------------------|-------------|------|-------------|-------|

| External Power Supply                                     |                                                            |             |      | •           | •     |

| External Power Supply <sup>3</sup><br>PVCCA/B versus PVSS |                                                            | 5           |      | 30          | V     |

| PVCCA/B quiescent current                                 | INA/INB=0                                                  |             |      | 0.1         | mA    |

| PVCCA/B quiescent current                                 | INA/INB=5V                                                 |             |      | 0.2         | mA    |

| PVCCA/B average current                                   | 20kHz, 50% duty cycle<br>PVCCA/B = 25V<br>$C_{LOAD} = 1nF$ |             |      | <u>0.4</u>  | mA    |

| VCC5PA/B quiescent cur-<br>rent                           | INA/INB=0 and HighZA/B=X                                   |             |      | <u>0.1</u>  | mA    |

| VCC5PA/B quiescent cur-<br>rent                           | INA/INB=X and HighZA/B=0                                   |             |      | <u>0.1</u>  | mA    |

| VCC5PA/B quiescent cur-<br>rent <sup>4</sup>              | INA/INB=5V and HighZA/B=5V                                 |             |      | 1           | mA    |

| VCC5PA/B average current                                  | 20kHz, 50% duty cycle                                      |             |      | 0.5         | mA    |

| External Power Supply<br>VCC5P versus VSS                 |                                                            | 4.75        |      | 5.25        | V     |

| Input signals (INA/B, HighZ                               | A/B)                                                       |             |      | •           |       |

| Input start threshold                                     |                                                            | <u>3.03</u> | 3.43 | <u>3.83</u> | V     |

| Input stop threshold                                      |                                                            | <u>1.1</u>  | 1.39 | <u>1.85</u> | V     |

| Hysteresis                                                |                                                            | <u>1.68</u> | 2.04 | <u>2.39</u> | V     |

| Drivers                                                   |                                                            |             |      |             | -     |

| OUTNA/B sink current <sup>5</sup>                         |                                                            | <u>2</u>    |      |             | А     |

| OUTPA/B source current <sup>6</sup>                       |                                                            | <u>1.95</u> |      |             | А     |

| High state output resistance                              |                                                            |             |      | 2.1         | Ω     |

| Low state output resistance                               |                                                            |             |      | 2           | Ω     |

| Propagation delay when<br>output rising<br>(IN→OUTPA/B)   | CLoad=1nF; (PVCC-PVSS)=15V<br>(50%→ 50%)                   |             | 40   |             | ns    |

| Propagation delay when<br>output falling<br>(IN→OUTNA/B)  | CLoad=1nF; (PVCC-PVSS)=15V<br>(50%→ 50%)                   |             | 40   |             | ns    |

| Rise Time (10%-90%)                                       | CLoad=1nF; (PVCC-PVSS)=15V                                 |             | 10   |             | ns    |

| Fall Time (10%-90%)                                       | CLoad=1nF; (PVCC-PVSS)=15V                                 |             | 10   |             | ns    |

| Soft Shut-down outputs (SS                                | SDA/B)                                                     |             |      |             |       |

| Delay from SSDA/B_IN to<br>SSDA/B output                  |                                                            |             | 120  |             | ns    |

| Open-drain transistor ON-<br>Resistance                   |                                                            | <u>15</u>   | 35   | <u>65</u>   | Ω     |

| Thermal resistance                                        |                                                            |             |      |             |       |

| Junction–to-air thermal resistance (Θ <sub>JA)</sub>      |                                                            |             | 42   |             | °C/W  |

$<sup>^3</sup>$  Voltage externally supplied to the chip

<sup>&</sup>lt;sup>4</sup> In this case, quiescent current means the average current over several Charge-Pump turn-on/off periods <sup>5</sup>In practice, the maximum sink current is N multiplied by the number of ATLAS channels used in the application

<sup>&</sup>lt;sup>6</sup>In practice, the maximum source current is N multiplied by the number of ATLAS channels used in the application

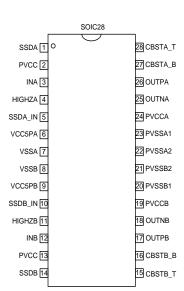

ture

(Last Modification Date)

# **Typical Performance Characteristics**

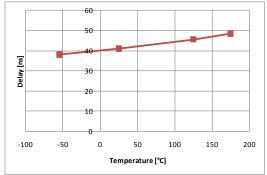

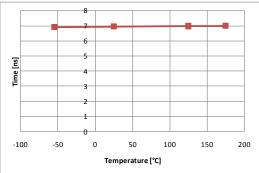

Figure 2: Turn-High Propagation Delay vs. Temperature

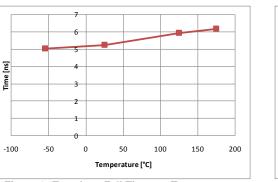

Figure 3: Turn-Low Fall Time vs. Temperature

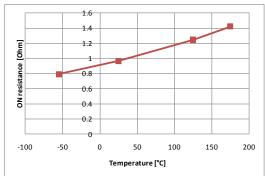

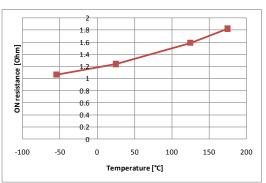

Figure 5: Low-state output resistance vs. Temperature

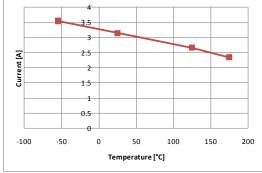

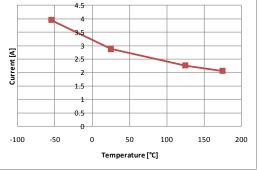

Figure 7: Sink Current vs. Temperature

Figure 4: Turn-High Rise Time vs. Temperature

Figure 6: High-state output resistance vs. Temperature

Figure 8: Source Current vs. Temperature

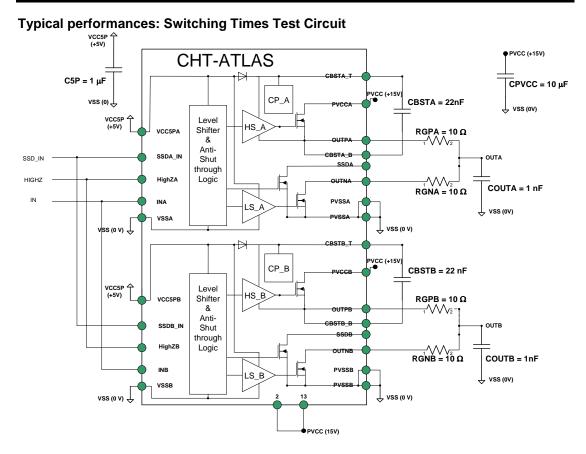

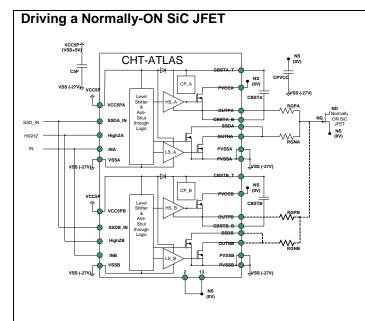

# Application Diagrams

The normally-ON SiC JFET is turned off once the gate-source voltage drops below the negative pinch-off voltage of the JFET. At zero gate-source voltage, the device is fully ON. For proper gate drive, CHT-ATLAS has its positive supply pins (PVCCA/B) tied to the source of the JFET (NS). Its negative supply pins (PVSSA/B) are connected to a negative voltage power supply with respect to NS.

The logical control signals (INA/B, HIGHZA/B, SSDA/B\_IN) belong to the VCC5P supply domain (5V with respect to VSS). VSS and PVSS must be electrically tied together in the application board.

Local decoupling between PVCC(=NS) and PVSS is mandatory as large current peaks flow through those supply connections during gate switching. The decoupling capacitor must deliver the total gate charge with minimum supply voltage loss.

CHT-ATLAS features 2 channels (A and B) with equal drive capabilities (>2A, <2 $\Omega$ ). For higher drive capability, the channels can be connected in parallel.

The high-side (pins OUTPA/B) and low-side (pin OUTNA/B) drivers inside CHT-ATLAS pull the JFET gate voltage up and down through series resistors RGPA/B and RGNA/B

Resistors RGPA/B and RGNA/B limit the gate current at turn-on and turn-off and control the switching time of the JFET and therefore the dV/dt in order to reduce probability of shoot-through current (parasitic turn-on of the blocking device in a half-bridge configuration). They also help damping oscillations and limiting voltage overshoot at the JFET gate which could result from stray inductances in the gate drive circuit and which could cause damage to the devices. Typical values range from 5 to 10 ohms.

At positive switching, the bootstrap capacitors CBSTA/B bias the high-side drivers above the positive supply voltage PVCC. The typical bootstrap capacitance is 22nF. After the transition, the internal charge-pumps keep the high-side drivers on till the next negative transition without any minimum switching frequency constraint.

SSDA/B offer soft-shutdown of the JFET by controlling the input signal SSDA/B\_IN. Both high-side and low-side drives are turned off and the gate is pulled down through RGNA/B via pin SSDA/B by weaker pull-down transistors.

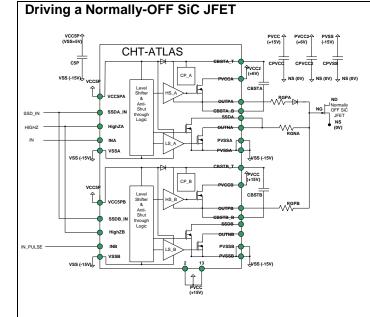

Unlike the normally-on JFET, the gatesource junction of the normally-off SiC JFET is forward biased in the device conduction state. In addition to the dynamic current for charging/discharging the total gate capacitance, some steadystate current has to be provided to maintain conduction after the device has been switched on.

The two channels of CHT-ATLAS are combined in a way to deliver both dynamic and steady-state currents.

Channel A must be driven with the regular PWM control signal (IN) while channel B must be driven by a second control signal (IN\_PULSE) giving a shorter impulse at the turn-on.

The dynamic current is supplied by the high-side driver of channel B (OUTPB) at turn-on and the low-side driver of channel A (OUTNB) at turn-off through resistances RGPB and RGNA.

The steady-state current is provided by the high-side driver in channel A (OUTPA). Similar considerations as with the normally-on JFET apply to the selection of resistors RGPA and RGPB. Avoiding too small value for RGPB, the positive supply voltage PVCCB is typically  $+15V^{7}$ .

The threshold voltage of the normally-off JFET being low, the gate should best be pulled down to a negative voltage with respect to the JFET source when the device is turned off. The lower the voltage, the better the immunity to shoot-through current in a half-bridge application. The negative supply PVSS depends on the SiC device gatesource voltage rating. A typical assumption for PVSS is -15V.

The steady-state current is supplied by the positive supply of channel A (PVCC2) through pin OUTPA and resistor RGPA. RGPA and PVCC2 must be sized in order to deliver the current required by the SiC device which is of the order of 100mA<sup>7</sup>. PVCC2 can be identical to PVCC but a smaller voltage could be used for power saving, a diode must then be inserted between RGPA and the gate of the SiC device.

Local decoupling of PVCC, PVCC2 and PVSS to NS is mandatory.

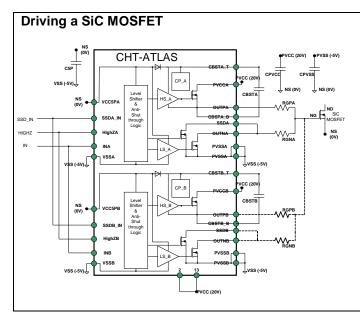

Driving a SiC MOSFET requires a gate driver capable of a large gate voltage swing and fast gate voltage transitions.

Both CHT-ATLAS channels can be connected in parallel for fast gate switching.

The high-side driver pulls the MOSFET gate voltage to PVCC (typically 20 V for best performance<sup>8</sup>) and the low-side divers pulls it down to negative PVSS<sup>8</sup> (typically -2V to -5V).

Considerations similar to those mentioned with SiC JFETS apply with respect to the gate resistances and the importance of proper decoupling of the supplies.

<sup>8</sup> Bob Callanan, "Application Considerations for SiC MOSFETS", Cree Inc., January 2011.

<sup>&</sup>lt;sup>7</sup> Robin Kelley et al., "Optimized Gate Driver for Enhancement-mode SiC JFET"

## **Ordering Information**

| Ordering Reference     | Package  | Temperature Range | Marking      |

|------------------------|----------|-------------------|--------------|

| CHT-TIT3345E-CSOIC28-T | CSOIC-28 | -55°C to +225°C   | CHT-TIT3345E |

### Contact & Ordering

### CISSOID S.A.

| Headquarters and contact EMEA: | CISSOID S.A. – Rue Francqui, 3 – 1435 Mont Saint Guibert - Belgium<br>T : +32 10 48 92 10 - F: +32 10 88 98 75<br>Email: <u>sales@cissoid.com</u> |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Sales<br>Representatives:      | Visit our website: http://www.cissoid.com                                                                                                         |

### Disclaimer

Neither CISSOID, nor any of its directors, employees or affiliates make any representations or extend any warranties of any kind, either express or implied, including but not limited to warranties of merchantability, fitness for a particular purpose, and the absence of latent or other defects, whether or not discoverable. In no event shall CISSOID, its directors, employees and affiliates be liable for direct, indirect, special, incidental or consequential damages of any kind arising out of the use of its circuits and their documentation, even if they have been advised of the possibility of such a damage. The circuits are provided "as is". CISSOID has no obligation to provide maintenance, support, updates, or modifications.