# 2.2 V memory module temperature sensor with a 4 Kb SPD EEPROM

Datasheet - production data

### **Features**

- 2.2 V memory module temperature sensor with integrated 4 Kb SPD EEPROM

- Fully compliant with JEDEC TSE2004B2 specifications

- Operating temperature range:

-20 °C to +125 °C

- Single supply voltage 2.2 V to 3.6 V

- 2 mm x 3 mm TDFN8, height: 0.80 mm (max): JEDEC MO-229, W2030D compliant RoHS compliant, halogen-free

### **Temperature sensor**

- Temperature sensor resolution: programmable (9-12 bits)

0.25 °C (typ)/LSB - (10-bit) default

- Temperature sensor accuracy (max) of:

- ± 1 °C (from +75 °C to +95 °C);

- ± 2 °C (from +40 °C to +125 °C);

- ± 3 °C (from -20 °C to +125 °C)

- ADC conversion time: 125 ms (max) / 70 ms (typ) at default resolution (10-bit)

- Typical operating supply current 160 μA (EEPROM standby)

- Temperature hysteresis selectable set points from 0, 1.5, 3, 6.0 °C

### 4 Kb SPD EEPROM

- Functionality identical to ST's M34E04 SPD EEPROM

- 4 Kbits organized as two pages of 256 bytes each

- Each page is composed of two 128-byte blocks

- Software data protection for each 128-byte block

- Byte Write within 5 ms

- 16 bytes Page Write within 5 ms

- More than 1 million write cycles

- More than 40-year data retention

#### Two-wire bus

- Two-wire I<sup>2</sup>C compatible serial interface

- Supports up to 1 MHz transfer rate (I<sup>2</sup>C Fast Mode+)

- · Does not initiate clock stretching

- Supports SMBus timeout 25 ms 35 ms

Contents STTS2004

# **Contents**

| 1 | Des   | ription                                               | 6  |

|---|-------|-------------------------------------------------------|----|

| 2 | Seria | Il communications                                     | 8  |

|   | 2.1   | Device type identifier (DTI) code                     | 8  |

|   |       | 2.1.1 I <sup>2</sup> C slave sub-address decoding     | 9  |

|   | 2.2   | Pin descriptions                                      | 12 |

|   |       | 2.2.1 A0, A1, A2                                      | 12 |

|   |       | 2.2.2 V <sub>SS</sub> (ground)                        | 12 |

|   |       | 2.2.3 SDA (open drain)                                | 12 |

|   |       | 2.2.4 SCL                                             | 12 |

|   |       | 2.2.5 EVENT (open drain)                              | 12 |

|   |       | 2.2.6 V <sub>DD</sub> (power)                         | 12 |

| 3 | Tem   | perature sensor operation                             | 14 |

|   | 3.1   | I <sup>2</sup> C communications                       | 14 |

|   | 3.2   | SMBus/I <sup>2</sup> C AC timing consideration        | 16 |

| 4 | Tem   | perature sensor registers                             | 17 |

|   | 4.1   | Capability register (read-only)                       | 18 |

|   | 4.2   | Configuration register (read/write)                   | 20 |

|   |       | 4.2.1 Event thresholds                                | 20 |

|   |       | 4.2.2 Interrupt mode                                  | 20 |

|   |       | 4.2.3 Comparator mode                                 | 20 |

|   |       | 4.2.4 Shutdown mode                                   | 20 |

|   |       | 4.2.5 Event output pin functionality                  | 24 |

|   | 4.3   | Temperature register (read-only)                      | 26 |

|   |       | 4.3.1 Temperature format                              | 26 |

|   | 4.4   | Temperature trip point registers (read/write)         | 27 |

|   |       | 4.4.1 Alarm window trip                               | 28 |

|   |       | 4.4.2 Critical trip                                   | 28 |

|   | 4.5   | Manufacturer ID register (read-only)                  | 29 |

|   | 4.6   | Device ID and device revision ID register (read-only) | 30 |

|   | 4.7   | Temperature resolution register (read/write)          | 30 |

|   |       |                                                       |    |

| STTS2004 | Contents |

|----------|----------|

| 71102004 | Contents |

|    | 4.0                 | 01.15    |                                                   |      |  |  |  |  |  |

|----|---------------------|----------|---------------------------------------------------|------|--|--|--|--|--|

|    | 4.8                 |          | timeout                                           |      |  |  |  |  |  |

|    | 4.9                 | Device i | reset and initialization                          | 32   |  |  |  |  |  |

| 5  | SPD E               | EEPRO    | M operation                                       | 33   |  |  |  |  |  |

|    | 5.1                 | 4 Kb SF  | PD EEPROM operation                               | 33   |  |  |  |  |  |

|    | 5.2                 | Internal | device reset - SPD EEPROM                         | 33   |  |  |  |  |  |

|    | 5.3                 | Memory   | addressing                                        | 33   |  |  |  |  |  |

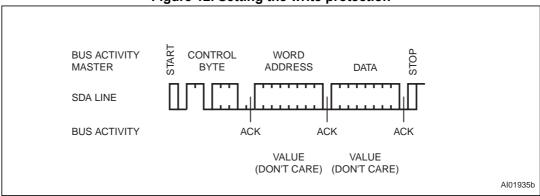

|    | 5.4                 | Setting  | the write protection                              | 34   |  |  |  |  |  |

|    |                     | 5.4.1    | Set and clear the write protection (SWPn and CWP) |      |  |  |  |  |  |

|    |                     | 5.4.2    | RPSn: read protection status                      | . 35 |  |  |  |  |  |

|    |                     | 5.4.3    | SPAn: set SPD page address                        | . 35 |  |  |  |  |  |

|    |                     | 5.4.4    | RPA: read SPD page address                        | 35   |  |  |  |  |  |

|    | 5.5                 | Write op | perations                                         | 35   |  |  |  |  |  |

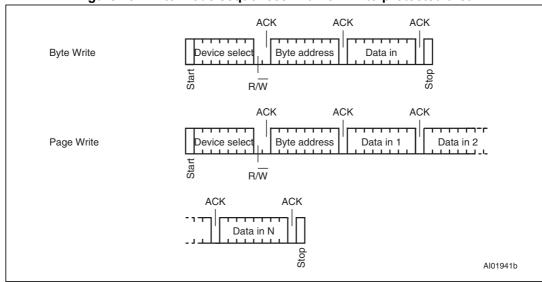

|    |                     | 5.5.1    | Byte write                                        | 36   |  |  |  |  |  |

|    |                     | 5.5.2    | Page write                                        | 36   |  |  |  |  |  |

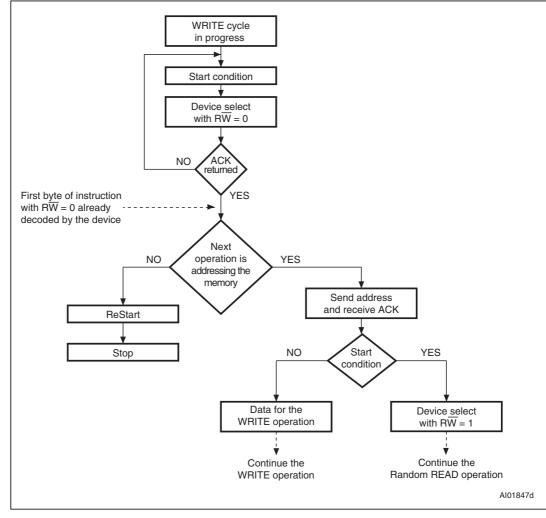

|    |                     | 5.5.3    | Minimizing system delays by polling on ACK        | . 36 |  |  |  |  |  |

|    | 5.6                 | Read or  | perations                                         | 37   |  |  |  |  |  |

|    |                     | 5.6.1    | Random address read                               | . 37 |  |  |  |  |  |

|    |                     | 5.6.2    | Current address read                              | . 38 |  |  |  |  |  |

|    |                     | 5.6.3    | Sequential read                                   | . 38 |  |  |  |  |  |

|    |                     | 5.6.4    | Acknowledge in read mode                          | . 38 |  |  |  |  |  |

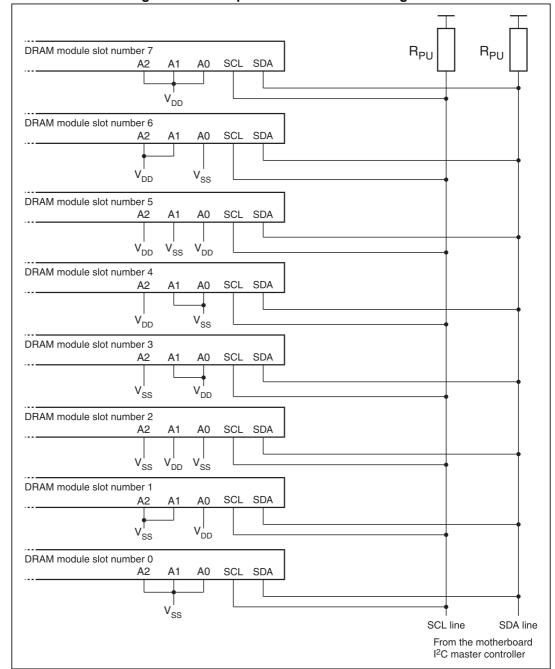

| 6  | Use ii              | n a men  | nory module                                       | 40   |  |  |  |  |  |

|    | 6.1                 | Progran  | nming the SPD                                     | 40   |  |  |  |  |  |

|    |                     | 6.1.1    | Isolated DIMM                                     | 40   |  |  |  |  |  |

|    |                     | 6.1.2    | DIMM inserted in the application motherboard      | . 41 |  |  |  |  |  |

| 7  | Maxin               | num rat  | ings                                              | 43   |  |  |  |  |  |

| 8  | DC ar               | nd AC p  | arameters                                         | 44   |  |  |  |  |  |

| 9  | Package information |          |                                                   |      |  |  |  |  |  |

| 10 | Part r              | numberi  | ng                                                | 54   |  |  |  |  |  |

| 11 | Revision history 55 |          |                                                   |      |  |  |  |  |  |

List of tables STTS2004

# List of tables

| Table 1.  | Logical serial address according to A2, A1, A0                                      | 9  |

|-----------|-------------------------------------------------------------------------------------|----|

| Table 2.  | Device select code                                                                  | 10 |

| Table 3.  | Signal names                                                                        |    |

| Table 4.  | Temperature sensor registers summary                                                | 17 |

| Table 5.  | Pointer register format                                                             |    |

| Table 6.  | Pointer register select bits (type, width, and default values)                      | 18 |

| Table 7.  | Capability register format                                                          | 18 |

| Table 8.  | Capability register bit definitions                                                 | 19 |

| Table 9.  | Configuration register format                                                       | 21 |

| Table 10. | Configuration register bit definitions                                              | 21 |

| Table 11. | Hysteresis as applied to temperature movement                                       | 23 |

| Table 12. | Legend for Figure 9: Event output boundary timings                                  | 25 |

| Table 13. | Temperature register format                                                         |    |

| Table 14. | Temperature register coding examples (for 10 bits)                                  | 27 |

| Table 15. | Temperature register bit definitions                                                |    |

| Table 16. | Temperature trip point register format                                              | 28 |

| Table 17. | Alarm temperature upper boundary register format                                    | 28 |

| Table 18. | Alarm temperature lower boundary register format                                    | 28 |

| Table 19. | Critical temperature register format                                                | 29 |

| Table 20. | Manufacturer ID register (read-only)                                                |    |

| Table 21. | Device ID and device revision ID register (read-only)                               |    |

| Table 22. | Temperature resolution register (TRES) (read/write)                                 |    |

| Table 23. | TRES details                                                                        |    |

| Table 24. | Operating modes                                                                     | 34 |

| Table 25. | DRAM DIMM connections                                                               | 40 |

| Table 26. | Acknowledge when writing data or defining the write-protection status               |    |

|           | (instructions with R/W_n bit = 0)                                                   | 41 |

| Table 27. | Acknowledge when reading the protection status                                      |    |

|           | (instructions with R/W_n bit = 1)                                                   |    |

| Table 28. | Absolute maximum ratings                                                            |    |

| Table 29. | Operating and AC measurement conditions                                             |    |

| Table 30. | DC characteristics - temperature sensor component with EEPROM                       |    |

| Table 31. | Input parameters                                                                    |    |

| Table 32. | Temperature to digital conversion performance                                       |    |

| Table 33. | AC characteristics of STTS2004 for SMBus and I <sup>2</sup> C compatibility timings |    |

| Table 34. | TDFN8 – 8-lead thin dual flat, no-lead (2 mm x 3 mm) mechanical data (DN)           |    |

| Table 35. | Parameters for landing pattern - TDFN8 package (DN)                                 |    |

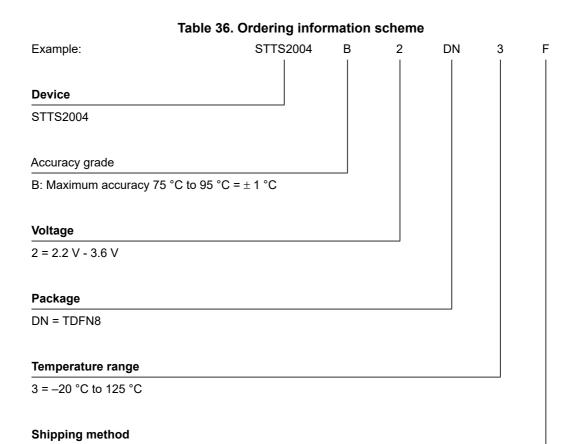

| Table 36. | Ordering information scheme                                                         |    |

| Table 37. | Document revision history                                                           | 55 |

|           |                                                                                     |    |

STTS2004 List of figures

# **List of figures**

| Figure 1.  | Logic diagram                                                                                                  | 11 |

|------------|----------------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | TDFN8 connections (top view)                                                                                   | 11 |

| Figure 3.  | Device select code                                                                                             | 12 |

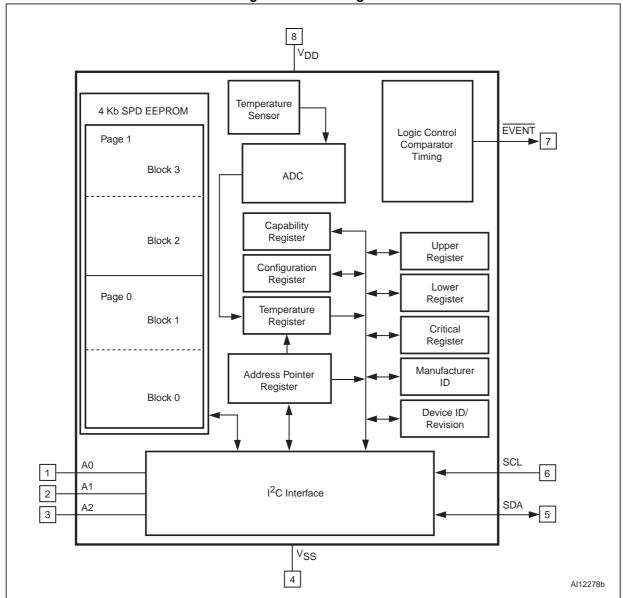

| Figure 4.  | Block diagram                                                                                                  | 13 |

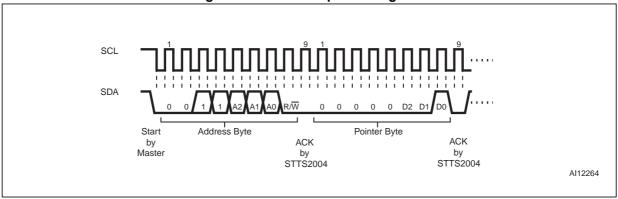

| Figure 5.  | I2C write to pointer register                                                                                  | 15 |

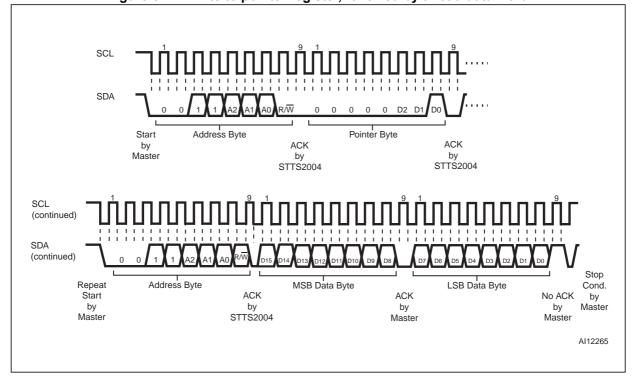

| Figure 6.  | I <sup>2</sup> C write to pointer register, followed by a read data word                                       | 15 |

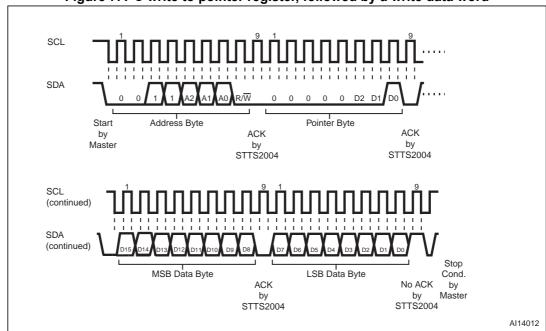

| Figure 7.  | I <sup>2</sup> C write to pointer register, followed by a write data word                                      | 16 |

| Figure 8.  | Hysteresis                                                                                                     | 23 |

| Figure 9.  | Event output boundary timings                                                                                  | 25 |

| Figure 10. | SMBus timeout timing diagram                                                                                   | 31 |

| Figure 11. | STTS2004 reset and initialization                                                                              | 32 |

| Figure 12. | Setting the write protection                                                                                   | 35 |

| Figure 13. | Write mode sequences in a non write-protected area                                                             | 36 |

| Figure 14. | Write cycle polling flowchart using ACK                                                                        | 37 |

| Figure 15. | Read mode sequences                                                                                            | 39 |

| Figure 16. | Serial presence detect block diagram                                                                           | 42 |

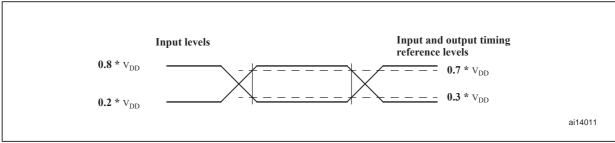

| Figure 17. | AC measurement I/O waveform                                                                                    |    |

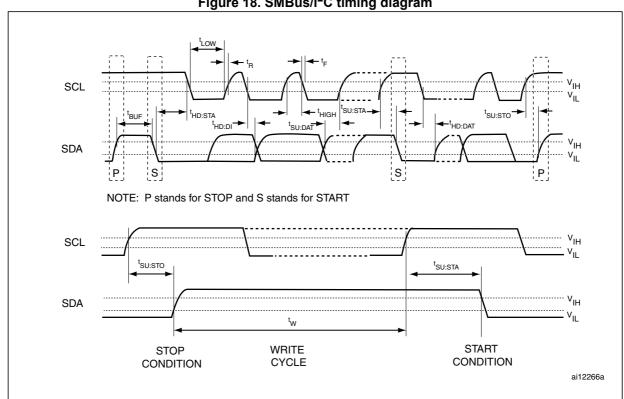

| Figure 18. | SMBus/I <sup>2</sup> C timing diagram                                                                          | 46 |

| Figure 19. | Maximum R <sub>PU</sub> value versus bus parasitic capacitance (C <sub>BUS</sub> ) for an I <sup>2</sup> C bus |    |

|            | at maximum frequency f <sub>C</sub> = 1 MHz                                                                    |    |

| Figure 20. | Pull-up resistor values versus bus line capacitance                                                            |    |

| Figure 21. | TDFN8 – 8-lead thin dual flat, no-lead (2 mm x 3 mm) package outline (DN)                                      |    |

| Figure 22. | DN package topside marking information (TDFN8)                                                                 |    |

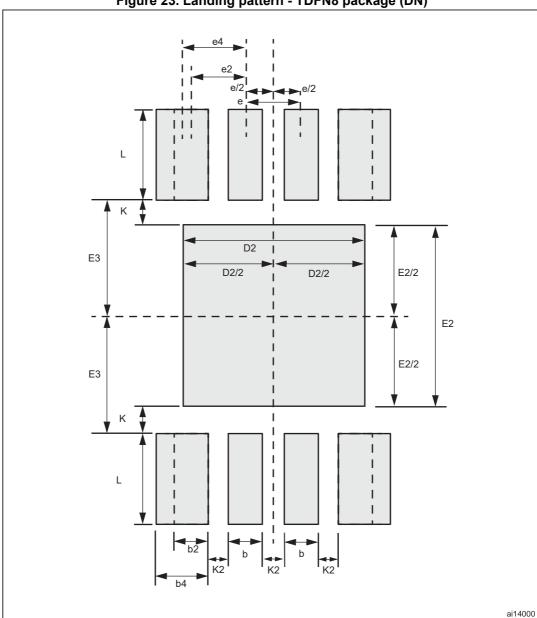

| Figure 23. | Landing pattern - TDFN8 package (DN)                                                                           | 52 |

Description STTS2004

# 1 Description

The STTS2004 is targeted for DDR4 DIMM modules in servers, desktops, and mobile personal computing platforms (laptops and other industrial applications). The thermal sensor (TS) in the STTS2004 is compliant with the JEDEC specification TSE2004a2, which defines memory module thermal sensor requirements for use in DRAM DIMMs (Dual Inline Memory Modules) with Serial Presence Detect (SPD), in which all the information concerning the DRAM module configuration (such as access speed, size, and organization) can be kept write-protected in one or more of the blocks of memory. The 4-Kbit serial EEPROM (SPD) in the STTS2004 is organized as two pages of 256 bytes each, or 512 bytes of total memory. Each page is comprised of two 128-byte blocks. The SPD is able to selectively lock the data in any or all of the four 128-byte blocks. The STTS2004 can interface to buses which have multiple devices on a shared bus, and each device has its own unique address on this bus. The device can achieve substantial power savings by using the software-programmed shutdown mode.

The TS-SPD EEPROM combination provides space as well as cost savings for mobile and server platform dual inline memory modules (DIMM) manufacturers, as it is packaged in the compact 2 mm x 3 mm 8-lead TDFN package with a thinner maximum height of 0.80 mm. The DN package is compliant to JEDEC MO-229, variation W2030D.

The digital temperature sensor has a programmable 9-12 bit analog-to-digital converter (ADC) which monitors and digitizes the temperature to a resolution of up to 0.0625 °C. The default resolution is 0.25 °C/LSB (10-bit). The typical accuracies over these temperature ranges are:

±2 °C over the full temperature measurement range of -20 °C to 125 °C

±1 °C in the +40 °C to +125 °C active temperature range, and

±0.5 °C in the +75 °C to +95 °C monitor temperature range

The temperature sensor in the STTS2004 is specified for operating at supply voltages from 2.2 V to 3.6 V. Operating at 3.3 V, the typical supply current is 160  $\mu$ A (includes I<sup>2</sup>C communication current).

The on-board sigma-delta ADC converts the measured temperature to a digital value that is calibrated in °C. For Fahrenheit applications, a lookup table or conversion routine is required. The STTS2004 is factory-calibrated and requires no external components to measure temperature.

The digital temperature sensor component has user-programmable registers that provide the capabilities for DIMM temperature-sensing applications. The open drain event output pin is active when the monitoring temperature exceeds a programmable limit, or it falls above or below an alarm window. The user has the option to set the event output as a critical temperature output. This pin can be configured to operate in either a comparator mode for thermostat operation or in interrupt mode.

The STTS2004 is protocol-compatible with the 2 Kbit SPD in the STTS2002 and uses a page selection method which is applied to the lower or upper pages of the 4 Kbit SPD. Unlike the STTS2002, the STTS2004 does not support the Permanently Set Write Protect (PSWP) feature.

Locking a 128-byte block of the EEPROM is accomplished by using a software write protection mechanism in conjunction with a high input voltage  $V_{HV}$  on the A0 input pin. A specific  $I^2C$  sequence is used to protect each block from writes until write protection is

STTS2004 Description

electrically reversed using a separate  $I^2C$  sequence which also requires  $V_{HV}$  on input A0 pin of the device.

Write protection for all four blocks is cleared simultaneously, and write protection may be reasserted after being cleared.

STTS2004 Serial communications

#### Serial communications 2

The STTS2004 has a simple 2-wire I<sup>2</sup>C-compatible digital serial interface which allows the user to access both the 4 Kb serial EEPROM and the data in the temperature register at any time. It communicates via the serial interface with a master controller which operates at speeds of up to 1 MHz. It also gives the user easy access to all of the STTS2004 registers in order to customize device operation.

The device behaves as a slave device in the I<sup>2</sup>C protocol, with all operations synchronized by the serial clock. Read and write operations are initiated by a START condition, generated by the bus master. The START condition is followed by a device select code and R/W bit (as described in Table 2 on page 10), terminated by an acknowledge bit.

The STTS2004 device is selected when decoding the correct device select byte. The device select byte is comprised of the 4-bit Device Type Identifier (DTI) and the 3-bit select address.

The SPD and TS portions of the STTS2004 device are designed to operate in parallel. Accesses to each portion of the device may be interleaved as long as the command protocol is followed.

When writing data to the memory, the STTS2004 inserts an acknowledge bit during the 9<sup>th</sup> clock cycle, following the bus master's 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a bus master generated STOP condition after an ACK for WRITE, and after a No ACK for READ.

The TS portion of the STTS2004 device uses a pointer register to access all registers in the device. Additionally, all data transfers to and from this section of the device are performed as block read/write operations. The data is transmitted/received as 2 bytes, Most Significant Byte (MSB) first, and terminated with a No ACK and STOP after the Least Significant Byte (LSB). Data and address information is transmitted and received Most Significant Bit first.

Note: Clock stretching is not supported by the device.

Violations of the command protocol result in unpredictable operation.

#### 2.1 Device type identifier (DTI) code

The JEDEC temperature sensor and EEPROM each have their own unique I<sup>2</sup>C address, which ensures that there are no compatibility or data translation issues. This is due to the fact that each of the devices have their own 4-bit DTI code, while the remaining three bits are configurable. This enables the EEPROM and thermal sensors to provide their own individual data via their unique addresses and still not interfere with each other's operation in any way.

The TS registers of the STTS2004 are accessed using a DTI of (0011).

A0, A1, and A2 inputs are directly combined with the DTI and the SPD page address bit to qualify I<sup>2</sup>C addresses. Each of the address pins (A0, A1, A2) is tied to V<sub>DD</sub> or V<sub>SS</sub> for the Logical Serial Address (LSA) which is equal to the code on the address pins (refer to Table 1).

STTS2004 Serial communications

The SPD memory may be accessed using a DTI of (1010), and to perform the SWPn, RSPn, or CWP operations, a DTI of (0110) is required.

The DTI codes are:

- '0011' for the TS, and

- '1010' for addressing the EEPROM memory array, and

- '0110' to access the software write protection settings of the EEPROM

# 2.1.1 I<sup>2</sup>C slave sub-address decoding

The 7-bit address for STTS2004 device consists of the 4-bit DTI code and the 3-bit device select code from the state of the 3 address pins (device select code) which are combined as shown in *Table 2*.

The 8<sup>th</sup> bit is the Read/Write bit (R/W). This bit is set to 1 for Read and 0 for Write operations.

If a match occurs on the device select code, the corresponding device gives an acknowledgment on serial data (SDA) during the 9<sup>th</sup> bit time.

The physical address for the TS is different than that used by the EEPROM. The TS physical address is binary 0 0 1 1 A2 A1 A0 RW, where A2, A1, and A0 are the three slave sub- address pins, and the LSB "RW" is the READ/WRITE flag.

The EEPROM physical address is binary 1 0 1 0 A2 A1 A0 RW for the memory array and is 0 1 1 0 A2 A1 A0 RW for permanently set write protection mode.

Thus up to eight STTS2004 devices can be connected on a single I<sup>2</sup>C bus. Each device is given a unique 3-bit Logical Serial Address code. The LSA is a decoding of information on the address pins A0, A1, and A2 as described in *Table 1*. When the Device Select Code is received, the device only responds if the Select Address is the same as the Logical Serial Address.

| Table 1. Logical Schaladaress according to A2, A1, A0 |                      |                      |                      |  |  |  |  |  |

|-------------------------------------------------------|----------------------|----------------------|----------------------|--|--|--|--|--|

| Logical serial address                                |                      |                      |                      |  |  |  |  |  |

| (LSA)                                                 | A2                   | A1                   | A0                   |  |  |  |  |  |

| 000                                                   | 0 (V <sub>SS</sub> ) | 0 (V <sub>SS</sub> ) | 0 (V <sub>SS</sub> ) |  |  |  |  |  |

| 001                                                   | 0 (V <sub>SS</sub> ) | 0 (V <sub>SS</sub> ) | 1 (V <sub>DD</sub> ) |  |  |  |  |  |

| 010                                                   | 0 (V <sub>SS</sub> ) | 1 (V <sub>DD</sub> ) | 0 (V <sub>SS</sub> ) |  |  |  |  |  |

| 011                                                   | 0 (V <sub>SS</sub> ) | 1 (V <sub>DD</sub> ) | 1 (V <sub>DD</sub> ) |  |  |  |  |  |

| 100                                                   | 1 (V <sub>DD</sub> ) | 0 (V <sub>SS</sub> ) | 0 (V <sub>SS</sub> ) |  |  |  |  |  |

| 101                                                   | 1 (V <sub>DD</sub> ) | 0 (V <sub>SS</sub> ) | 1 (V <sub>DD</sub> ) |  |  |  |  |  |

| 110                                                   | 1 (V <sub>DD</sub> ) | 1 (V <sub>DD</sub> ) | 0 (V <sub>SS</sub> ) |  |  |  |  |  |

| 111                                                   | 1 (V <sub>DD</sub> ) | 1 (V <sub>DD</sub> ) | 1 (V <sub>DD</sub> ) |  |  |  |  |  |

Table 1. Logical serial address according to A2. A1. A0

Write protection commands SWPn, CWP, and RPSn, and the SPD page address commands SPAn and RPA, do not use the select address A(n) or logical serial address (LSA), therefore all devices on the bus will act on these commands simultaneously. Since it is impossible to determine which device is responding to RPSn or RPA commands, for example, these functions are primarily used for external device programmers rather than insystem applications.

Serial communications STTS2004

Table 2. Device select code

| Function                                       | Symbol | Device Type Identifier (DTI) <sup>(1)</sup> |    |    |    | Logical Serial<br>Address (LSA) <sup>(2)(3)</sup> |         |        | R/W | A0 pin <sup>(4)</sup>   |

|------------------------------------------------|--------|---------------------------------------------|----|----|----|---------------------------------------------------|---------|--------|-----|-------------------------|

|                                                |        | b7                                          | b6 | b5 | b4 | b3                                                | b2      | b1     | b0  |                         |

| Read temperature registers                     | RTR    | 0                                           | 0  | 1  | 1  | A2                                                | A1      | A0     | 1   | 0 or 1                  |

| Write temperature registers                    | WTR    |                                             | O  | '  | '  | ^2                                                | _ ^ i   | Αυ     | 0   | 0 01 1                  |

| Read EE memory                                 | RSPD   | 1                                           | 0  | 1  | 0  | A2                                                | A1      | A0     | 1   | 0 or 1                  |

| Write EE memory                                | WSPD   | '                                           | U  | I  | "  | AZ                                                | A 1     | AU     | 0   | 0 01 1                  |

| Set write protection, block 0                  | SWP0   |                                             |    |    |    | 0                                                 | 0       | 1      | 0   | V <sub>HV</sub>         |

| Set write protection, block 1                  | SWP1   |                                             |    |    |    | 1                                                 | 0       | 0      | 0   | V <sub>HV</sub>         |

| Set write protection, block 2                  | SWP2   |                                             |    |    |    | 1                                                 | 0       | 1      | 0   | V <sub>HV</sub>         |

| Set write protection, block 3                  | SWP3   |                                             |    |    |    | 0                                                 | 0       | 0      | 0   | V <sub>HV</sub>         |

| Clear all write protection                     | CWP    |                                             |    |    |    | 0                                                 | 1       | 1      | 0   | V <sub>HV</sub>         |

| Read protection status, block 0 <sup>(5)</sup> | RPS0   |                                             | 1  | 1  | 0  | 0                                                 | 0       | 1      | 1   | 0, 1 or V <sub>HV</sub> |

| Read protection status, block 1 <sup>(5)</sup> | RPS1   | 0                                           | 1  | '  | 0  | 1                                                 | 0       | 0      | 1   | 0, 1 or V <sub>HV</sub> |

| Read protection status, block 2 <sup>(5)</sup> | RPS2   |                                             |    |    |    | 1                                                 | 0       | 1      | 1   | 0, 1 or V <sub>HV</sub> |

| Read protection status, block 3 <sup>(5)</sup> | RPS3   |                                             |    |    |    | 0                                                 | 0       | 0      | 1   | 0, 1 or V <sub>HV</sub> |

| Set EE page address to 0 <sup>(6)</sup>        | SPA0   |                                             |    |    |    | 1                                                 | 1       | 0      | 0   | 0, 1 or V <sub>HV</sub> |

| Set EE page address to 1 <sup>(6)</sup>        | SPA1   |                                             |    |    |    | 1                                                 | 1       | 1      | 0   | 0, 1 or V <sub>HV</sub> |

| Read EE page address <sup>(7)</sup>            | RPA    |                                             |    |    |    | 1                                                 | 1       | 0      | 1   | 0, 1 or V <sub>HV</sub> |

| Reserved                                       |        |                                             |    |    |    | All                                               | other e | ncodin | gs  |                         |

- 1. The most significant bit, b7, is sent first.

- 2. Logical Serial Addresses (LSA) are generated by the combination of inputs on the address pin (refer to Table 1)

- For backward compatibility with previous devices, the order of block select bits (b3 and b1) are not a simple binary encoding of the block number

- 4. A0 pin is driven to 0 =  $V_{SS}$ , 1 =  $V_{DD}$  or  $V_{HV}$ .

- Reading the block protection status results in Ack when the block is not write-protected, and results in NoAck when the block is write-protected.

- Setting the SPD (EEPROM) page address to 0 selects the lower 256 bytes of EEPROM, setting to 1 selects the upper 256 bytes of EEPROM. Subsequent Read EE or Write EE commands operate on the selected EE page.

- 7. Reading the EE page address results in ACK when the current page is 0 and NACK when the current page is 1.

STTS2004 Serial communications

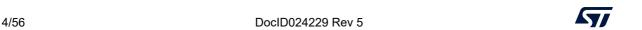

Figure 1. Logic diagram

1. SDA and  $\overline{\text{EVENT}}$  are open drain.

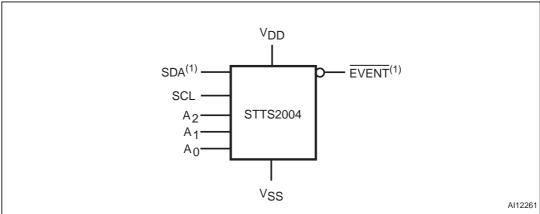

Table 3. Signal names

| Pin | Symbol               | Description                                                             | Direction    |

|-----|----------------------|-------------------------------------------------------------------------|--------------|

| 1   | A0                   | Serial bus address selection pin. Can be tied to $V_{SS}$ or $V_{DD}$ . | Input        |

| 2   | A1                   | Serial bus address selection pin. Can be tied to $V_{SS}$ or $V_{DD}$ . | Input        |

| 3   | A2                   | Serial bus address selection pin. Can be tied to $V_{SS}$ or $V_{DD}$ . | Input        |

| 4   | V <sub>SS</sub>      | Supply ground                                                           |              |

| 5   | SDA <sup>(1)</sup>   | Serial data                                                             | Input/output |

| 6   | SCL                  | Serial clock                                                            | Input        |

| 7   | EVENT <sup>(1)</sup> | Event output pin. Open drain and active-low.                            | Output       |

| 8   | $V_{DD}$             | Supply power (2.2 V to 3.6 V)                                           |              |

1. SDA and  $\overline{\text{EVENT}}$  are open drain.

Note: The STTS2004 also has a heat paddle, which is typically connected to the application ground plane, refer to Figure 23: Landing pattern - TDFN8 package (DN).

Figure 2. TDFN8 connections (top view)

1. SDA and  $\overline{\text{EVENT}}$  are open drain.

Serial communications STTS2004

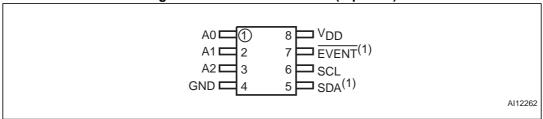

#### 2.2 Pin descriptions

#### 2.2.1 A0, A1, A2

A2, A1, and A0 are selectable address pins for the 3 LSBs of the I<sup>2</sup>C interface address. These inputs must be tied to V<sub>DD</sub> or GND as shown in Figure 3 to provide 8 unique address selections. These pins are internally connected to the A2, A1, A0 (slave address inputs) of the EEPROM.

$V_{DD}$  $V_{DD}$ STTS2004 STTS2004 A(n) A(n) **GND GND**

Figure 3. Device select code

#### V<sub>SS</sub> (ground) 2.2.2

This is the reference for the power supply. It must be connected to system ground.

#### 2.2.3 SDA (open drain)

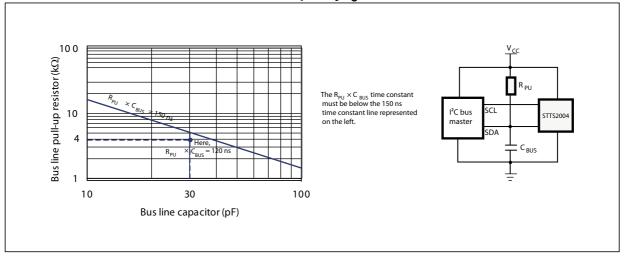

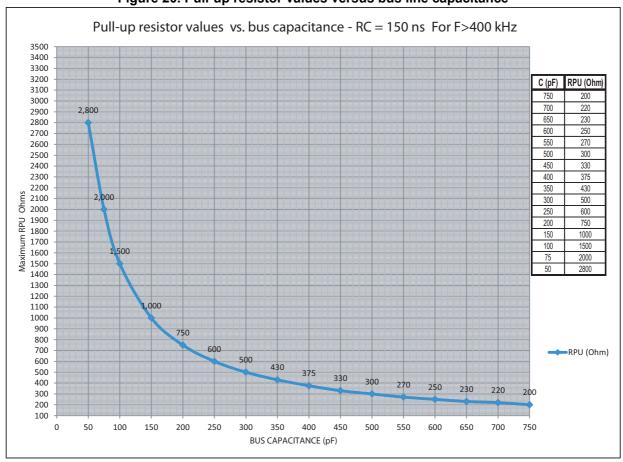

This is the serial data input/output pin. SDA(out) is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus. A pull-up resistor must be connected from Serial Data (SDA) to V<sub>DD</sub>. Figure 20 indicates how the value of the pull-up resistor can be calculated.

#### 2.2.4 SCL

This is the serial clock input pin.

#### **EVENT** (open drain) 2.2.5

This output pin is open drain and active-low. A pull-up resistor must be connected to this pin.

#### 2.2.6 V<sub>DD</sub> (power)

This is the supply voltage pin, and ranges from 2.2 V to 3.6 V.

DocID024229 Rev 5 12/56

STTS2004 Serial communications

Figure 4. Block diagram

# 3 Temperature sensor operation

The temperature sensor continuously monitors the ambient temperature and updates the temperature data register. Temperature data is latched internally by the device and may be read by software from the bus host at any time.

The I<sup>2</sup>C slave address selection pins allow up to 8 such devices to co-exist on the same bus. This means that up to 8 memory modules can be supported, given that each module has one such slave device address slot.

After initial power-on, the configuration registers are set to the default values. The software can write to the configuration register to set bits per the bit definitions in Section 3.1: I<sup>2</sup>C communications.

For details of operation and usage of 4 Kb SPD EEPROM, refer to Section 5: SPD EEPROM operation.

# 3.1 I<sup>2</sup>C communications

The registers in this device are selected by the pointer register. At power-up, the pointer register is set to "00", which is the capability register location. The pointer register latches the last location it was set to. Each data register falls into one of three types of user accessibility:

- Read-only

- 2. Write-only, and

- 3. WRITE/READ same address

A WRITE to this device will always include the address byte and the pointer byte. A WRITE to any register other than the pointer register, requires two data bytes.

Reading this device is achieved in one of two ways:

- If the location latched in the pointer register is correct (most of the time it is expected

that the pointer register will point to one of the read temperature registers because that

will be the data most frequently read), then the READ can simply consist of an address

byte, followed by retrieval of the two data bytes.

- If the pointer register needs to be set, then an address byte, pointer byte, repeat start, and another address byte will accomplish a READ.

The data byte transfers the MSB first. At the end of a READ, this device can accept either an acknowledge (ACK) or no acknowledge (No ACK) status from the master. The No ACK status is typically used as a signal for the slave that the master has read its last byte. This device subsequently takes up to 125 ms (max), 70 ms (typ) to measure the temperature for the default temperature resolution.

Note: The STTS2004 does not initiate clock stretching which is an optional I<sup>2</sup>C bus feature.

**T**

Figure 5. I<sup>2</sup>C write to pointer register

Figure 6. I<sup>2</sup>C write to pointer register, followed by a read data word

Figure 7. I<sup>2</sup>C write to pointer register, followed by a write data word

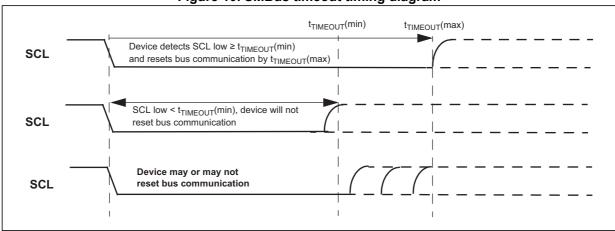

# 3.2 SMBus/I<sup>2</sup>C AC timing consideration

In order for this device to be both SMBus- and  $I^2C$ -compatible, it complies to a subset of each specification. The requirements which enable this device to co-exist with devices on either an SMBus or an  $I^2C$  bus include:

- The SMBus minimum clock frequency is required

- The SMBus timeout is maximum 35 ms

4

# 4 Temperature sensor registers

The temperature sensor component is comprised of various user-programmable registers. These registers are required to write their corresponding addresses to the pointer register. They can be accessed by writing to their respective addresses (see *Table 4*). Pointer register bits 7 - 4 must always be written to '0' (see *Table 5*). This must be maintained, as not setting these bits to '0' may keep the device from performing to specifications.

### The main registers include:

- Capability register (read-only)

- Configuration register (read/write)

- Temperature register (read-only)

- Temperature trip point registers (read/write), including

- Alarm temperature upper boundary

- Alarm temperature lower boundary

- Critical temperature

- Manufacturer ID register (read-only)

- Device ID and device revision ID register (read-only)

- Temperature resolution register (TRES) (read/write)

See *Table 6 on page 18* for pointer register selection bit details.

Table 4. Temperature sensor registers summary

| Address (hex)  | Register name                         | Power-on default |           |

|----------------|---------------------------------------|------------------|-----------|

| Not applicable | Address pointer                       | Undefined        |           |

| 00             | Capability                            | B-grade          | 0x00EF    |

| 01             | Configuration                         | 0x0000           |           |

| 02             | Alarm temperature upper boundary trip | 0x0000           |           |

| 03             | Alarm temperature lower boundary trip | 0x0000           |           |

| 04             | Critical temperature trip             |                  | 0x0000    |

| 05             | Temperature                           |                  | Undefined |

| 06             | Manufacturer's ID                     | 0x104A           |           |

| 07             | Device ID/revision                    | 0x2201           |           |

| 08             | Temperature resolution register       | 0x0001           |           |

Note:

Registers beyond the specified (00-08) are reserved for STMicroelectronics' internal use only, for device test modes in product manufacturing. The registers must NOT be accessed by the user (customer) in the system application or the device may not perform according to specifications.

Table 5. Pointer register format

| MSB  | MSB  |      |      |                              |      |      |      |  |

|------|------|------|------|------------------------------|------|------|------|--|

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3                         | Bit2 | Bit1 | Bit0 |  |

| 0    | 0    | 0    | 0    | P3                           | P2   | P1   | P0   |  |

|      |      |      |      | Pointer/register select bits |      |      |      |  |

Table 6. Pointer register select bits (type, width, and default values)

| Р3 | P2 | P1 | P0 | Name     | Register description            | Width<br>(bits) | Type<br>(R/W) | Default state<br>(POR) |       |

|----|----|----|----|----------|---------------------------------|-----------------|---------------|------------------------|-------|

| 0  | 0  | 0  | 0  | CAPA     | Thermal sensor capabilities     | B-grade only    | 16            | R                      | 00 EF |

| 0  | 0  | 0  | 1  | CONF     | Configuration                   |                 | 16            | R/W                    | 00 00 |

| 0  | 0  | 1  | 0  | UPPER    | Alarm temperature upper boundar | ту              | 16            | R/W                    | 00 00 |

| 0  | 0  | 1  | 1  | LOWER    | Alarm temperature lower boundar | у               | 16            | R/W                    | 00 00 |

| 0  | 1  | 0  | 0  | CRITICAL | Critical temperature            |                 | 16            | R/W                    | 00 00 |

| 0  | 1  | 0  | 1  | TEMP     | Temperature                     |                 | 16            | R                      | 00 00 |

| 0  | 1  | 1  | 0  | MANU     | Manufacturer ID                 |                 | 16            | R                      | 10 4A |

| 0  | 1  | 1  | 1  | ID       | Device ID/revision              |                 | 16            | R                      | 22 01 |

| 1  | 0  | 0  | 0  | TRES     | Temperature resolution register |                 | 8             | R/W                    | 01    |

# 4.1 Capability register (read-only)

This 16-bit register is read-only, and provides the TS capabilities which comply with the minimum JEDEC TSE2004av specifications (see *Table 7* and *Table 8 on page 19*). The STTS2004 resolution is programmable via writing to pointer 08 register. The power-on default value is 0.25 °C/LSB (10-bit).

Table 7. Capability register format

| Bit15 | Bit14 | Bit13           | Bit12 | Bit11 | Bit10          | Bit9             | Bit8                     |

|-------|-------|-----------------|-------|-------|----------------|------------------|--------------------------|

| RFU   | RFU   | RFU             | RFU   | RFU   | RFU            | RFU              | RFU                      |

|       |       |                 |       |       |                |                  |                          |

| Bit7  | Bit6  | Bit5            | Bit4  | Bit3  | Bit2           | Bit1             | Bit0                     |

| EVSD  | TMOUT | V <sub>HV</sub> | TRES1 | TRES0 | Wider<br>range | Higher precision | Alarm and critical trips |

Table 8. Capability register bit definitions

| Dit  | Position                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit  | Definition                                                                                                                                                                                                                                                                                                                                                                                                |

| 0    | Basic capability  - 0 = Alarm and critical trips turned OFF.  - 1 = Alarm and critical trips turned ON.                                                                                                                                                                                                                                                                                                   |

| 1    | Accuracy  — 1 = High accuracy ±1 °C over the active range and ±2 °C over the monitoring range (B-grade) (default).                                                                                                                                                                                                                                                                                        |

| 2    | Range width  - 0 = Values lower than 0 °C will be clamped and represented as binary value '0'.  - 1 = Temperatures below 0 °C can be read and the Sign bit will be set accordingly.                                                                                                                                                                                                                       |

| 4:3  | Temperature resolution  - 00 = 9 bit, 0.5 °C/LSB  - 01 = 10 bit, 0.25 °C/LSB - default resolution  - 10 = 11 bit, 0.125 °C/LSB  - 11 = 12 bit, 0.0625 °C/LSB                                                                                                                                                                                                                                              |

| 5    | (V <sub>HV</sub> ) high voltage support for <b>A0 (pin 1)</b> - 1 = STTS2004 supports a voltage up to 10 volts on the A0 pin - (default)                                                                                                                                                                                                                                                                  |

| 6    | TMOUT - bus timeout support - 1 = Default for STTS2004-SMBus compatible 25 ms - 35 ms                                                                                                                                                                                                                                                                                                                     |

| 7    | EVSD - EVENT behavior upon shutdown (default)  - 1 = The EVENT pin output is deasserted (not driven) when entering shutdown, and remains deasserted upon exit from shutdown until the next thermal sample is taken, or possibly sooner if EVENT is programmed for comparator mode. In interrupt mode, EVENT may or may not be asserted when exiting shutdown if a pending interrupt has not been cleared. |

| 15:8 | Reserved These values must be set to '0'.                                                                                                                                                                                                                                                                                                                                                                 |

# 4.2 Configuration register (read/write)

The 16-bit configuration register stores various configuration modes that are used to set up the sensor registers and configure according to application and JEDEC requirements (see *Table 9 on page 21* and *Table 10 on page 21*).

### 4.2.1 Event thresholds

All event thresholds use hysteresis as programmed in register address 0x01 (bits 10 through 9) to be set when they de-assert.

# 4.2.2 Interrupt mode

The interrupt mode allows an event to occur where software may write a '1' to the clear event bit (bit 5) to de-assert the event Interrupt output until the next trigger condition occurs.

# 4.2.3 Comparator mode

The comparator mode enables the device to be used as a thermostat. READs and WRITEs on the device registers will not affect the event output in comparator mode. The event signal will remain asserted until temperature drops outside the range or is re-programmed to make the current temperature "out of range".

### 4.2.4 Shutdown mode

The STTS2004 features a shutdown mode which disables all power-consuming activities (e.g. temperature sampling operations), and leaves the serial interface active. This is selected by setting the shutdown bit (bit 8) to '1'. In this mode, the devices consume the minimum current (I<sub>SHDN</sub>), as shown in *Table 30 on page 44*.

Note: Bit 8 cannot be set to '1' while bits 6 and 7 (the lock bits) are set to '1'.

The device may be enabled for continuous operation by clearing bit 8 to '0'. In shutdown mode, all registers may be read or written to. Power recycling will also clear this bit and return the device to continuous mode as well.

If the device is shut down while the  $\overline{\text{EVENT}}$  pin is asserted, then the Event output will be deasserted during shutdown. It will remain de-asserted until the device is enabled for normal operation. Once the device is enabled, it takes  $t_{\text{CONV}}$  before the device can re-assert the Event output.

Table 9. Configuration register format

| Bit15                | Bit14             | Bit13       | Bit12               | Bit11                  | Bit10               | Bit9           | Bit8             |

|----------------------|-------------------|-------------|---------------------|------------------------|---------------------|----------------|------------------|

| RFU                  | RFU               | RFU         | RFU                 | RFU Hysteresis Hystere |                     | Hysteresis     | Shutdown<br>mode |

|                      |                   |             |                     |                        |                     |                |                  |

| Bit7                 | Bit6              | Bit5        | Bit4                | Bit3                   | Bit2                | Bit1           | Bit0             |

| Critical lock<br>bit | Alarm lock<br>bit | Clear event | Event output status | Event output control   | Critical event only | Event polarity | Event<br>mode    |

The temperature sensor configuration register holds the control and status bits of the EVENT pin as well as general hysteresis on all limits. To avoid glitches on the EVENT output pin, users should disable EVENT or CRITICAL functions prior to programming or changing other device configuration settings.

Table 10. Configuration register bit definitions

| Bit | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Event mode  - 0 = Comparator output mode (this is the default).  - 1 = Interrupt mode; when either of the lock bits (bit6 or bit7) is set, this bit cannot be altered until it is unlocked.                                                                                                                                                                                                                                                                                  |

| 1   | Event polarity <sup>(1)</sup> The event polarity bit controls the active state of the EVENT pin. The EVENT pin is driven to this state when it is asserted.  - 0 = Active-low (this is the default). Requires a pull-up resistor to set the inactive state of the open-drain output. The power to the pull-up resistor should not be greater than V <sub>DD</sub> + 0.2 V. Active state is logical "0".  - 1 = Active-high. The active state of the pin is then logical "1". |

| 2   | Critical event only  - 0 = Event output on alarm or critical temperature event (this is the default).  - 1 = Event only if the temperature is above the value in the critical temperature register (T <sub>A</sub> > T <sub>CRIT</sub> ); when the alarm window lock bit (bit6) is set, this bit cannot be altered until it is unlocked.                                                                                                                                     |

| 3   | <ul> <li>Event output control</li> <li>0 = Event output disabled (this is the default).</li> <li>1 = Event output enabled; when either of the lock bits (bit6 or bit7) is set, this bit cannot be altered until it is unlocked.</li> </ul>                                                                                                                                                                                                                                   |

| 4   | Event status (read-only) <sup>(2)</sup> - 0 = Event output condition is not being asserted by this device 1 = Event output condition is being asserted by this device via the alarm window or critical trip event.                                                                                                                                                                                                                                                           |

| 5   | Clear event (write-only) <sup>(3)</sup> - 0 = No effect 1 = Clears the active event in interrupt mode. The pin is released and will not assert until a new interrupt condition occurs.                                                                                                                                                                                                                                                                                       |

Table 10. Configuration register bit definitions (continued)

| Bit   | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6     | Alarm window lock bit  - 0 = Alarm trips are not locked and can be altered (this is the default).  - 1 = Alarm trip register settings cannot be altered. This bit is initially cleared. When set, this bit returns a logic '1' and remains locked until cleared by an internal power-on reset. These bits can be written to with a single WRITE, and do not require double WRITEs.                                                                                                                                                                                                                                    |

| 7     | Critical trip lock bit  - 0 = Critical trip is not locked and can be altered (this is the default).  - 1 = Critical trip register settings cannot be altered. This bit is initially cleared. When set, this bit returns a logic '1' and remains locked until cleared by an internal power-on reset. These bits can be written to with a single WRITE, and do not require double WRITEs.                                                                                                                                                                                                                               |

| 8     | Shutdown mode  - 0 = TS is enabled, continuous conversion (this is the default).  - 1 = Shutdown TS when the shutdown, device, and A/D converter are disabled in order to save power. No event conditions will be asserted; when either of the lock bits (bit6 or bit7) is set, then this bit cannot be altered until it is unlocked. It can be cleared at any time.                                                                                                                                                                                                                                                  |

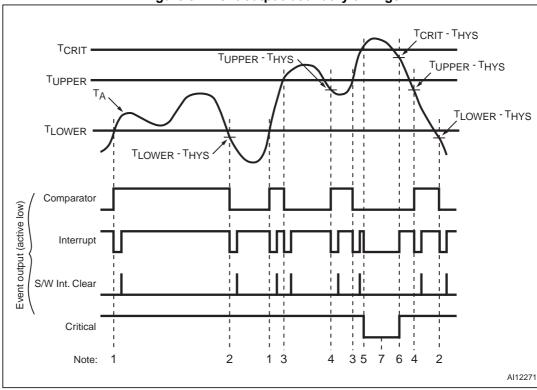

| 10:9  | Hysteresis enable (see <i>Figure 8</i> and <i>Table 11</i> )  - 00 = Hysteresis is disabled (default)  - 01 = Hysteresis is enabled at 1.5 °C  - 10 = Hysteresis is enabled at 3 °C  - 11 = Hysteresis is enabled at 6 °C  Hysteresis applies to all limits when the temperature is dropping below the threshold so that once the temperature is above a given threshold, it must drop below the threshold minus the hysteresis in order to be flagged as an interrupt event. Note that hysteresis is also applied to the EVENT pin functionality. When either of the lock bits is set, these bits cannot be altered. |

| 15:11 | Reserved for future use. These bits will always read '0' and writing to them will have no effect. For future compatibility, all RFU bits must be programmed as '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

As this device is used in DIMM (memory modules) applications, it is strongly recommended that only the active-low polarity (default) is used. This will provide full compatibility with the STTS2002. This is the recommended configuration for the STTS2004.

- 2. The actual incident causing the event can be determined from the read temperature register. Interrupt events can be cleared by writing to the clear event bit (writing to this bit will have no effect on overall device functioning).

- 3. Writing to this register has no effect on overall device functioning in comparator mode. When read, this bit will always return a logic '0' result.

AI12270

Tigure 6. Hysteresis

Figure 8. Hysteresis

- 1.  $T_H$  = Value stored in the alarm temperature upper boundary trip register

- 2.  $T_L$  = Value stored in the alarm temperature lower boundary trip register

- 3. HYS = Absolute value of selected hysteresis

Below Window bit

Above Window bit

Table 11. Hysteresis as applied to temperature movement

|        | Below alarm       | window bit               | Above alarm window bit |                      |  |  |  |

|--------|-------------------|--------------------------|------------------------|----------------------|--|--|--|

|        | Temperature slope | Temperature<br>threshold |                        |                      |  |  |  |

| Sets   | Falling           | T <sub>L</sub> - HYS     | Rising                 | T <sub>H</sub>       |  |  |  |

| Clears | Rising            | T <sub>L</sub>           | Falling                | T <sub>H</sub> - HYS |  |  |  |

# 4.2.5 Event output pin functionality

The STTS2004  $\overline{\text{EVENT}}$  pin is an open drain output that requires a pull-up to V<sub>DD</sub> on the system motherboard or integrated into the master controller.  $\overline{\text{EVENT}}$  has three operating modes, depending on configuration settings and any current out-of-limit conditions. These modes are interrupt, comparator or critical.

In interrupt mode the  $\overline{\text{EVENT}}$  pin will remain asserted until it is released by writing a '1' to the "Clear Event" bit in the status register. The value to write is independent of the EVENT polarity bit.

In comparator mode the  $\overline{\text{EVENT}}$  pin will clear itself when the error condition that caused the pin to be asserted is removed.

In the critical mode the  $\overline{\text{EVENT}}$  pin will only be asserted if the measured temperature exceeds the critical limit. Once the pin has been asserted, it will remain asserted until the temperature drops below the critical limit minus hysteresis. *Figure 9 on page 25* illustrates the operation of the different modes over time and temperature.

When the hysteresis bits (bits 10 and 9) are enabled, hysteresis may be used to sense temperature movement around trigger points. For example, when using the "above alarm window" bit (temperature register bit 14, see *Table 13 on page 26*) and hysteresis is set to 3 °C, as the temperature rises, bit 14 is set (bit 14 = 1). The temperature is above the alarm window and the temperature register contains a value that is greater than the value set in the alarm temperature upper boundary register (see *Table 17 on page 28*).

If the temperature decreases, bit 14 will remain set until the measured temperature is less than or equal to the value in the alarm temperature upper boundary register minus 3 °C (see *Figure 8 on page 23* and *Table 11 on page 23* for details.

Similarly, when using the "below alarm window" bit (temperature register bit 13, see *Table 13 on page 26*) will be set to '0'. The temperature is equal to or greater than the value set in the alarm temperature lower boundary register (see *Table 18 on page 28*). As the temperature decreases, bit 13 will be set to '1' when the value in the temperature register is less than the value in the alarm temperature lower boundary register minus 3 °C (see *Figure 8 on page 23* and *Table 11 on page 23* for details.

If the device enters the shutdown mode with the  $\overline{\text{EVENT}}$  output asserted, the output will be de-asserted.

Once the shutdown bit is cleared, the EVENT output will do the following, based on whether the device is configured for comparator or interrupt modes:

#### Comparator mode

The  $\overline{\text{EVENT}}$  output will remain de-asserted until after the first temperature conversion (t<sub>CONV</sub>) is completed. After this initial temperature conversion, T<sub>A</sub> must satisfy the T<sub>UPPER</sub> or T<sub>LOWER</sub> boundary conditions in order for the  $\overline{\text{EVENT}}$  output to be asserted.

#### Interrupt mode

The  $\overline{\text{EVENT}}$  output will remain de-asserted until after the first temperature conversion ( $t_{\text{CONV}}$ ) is completed. If the Clear event bit (bit 5 of configuration register) is never set, then the EVENT output will re-assert after the first temperature conversion.

Figure 9. Event output boundary timings

Table 12. Legend for Figure 9: Event output boundary timings

| Note | Event output boundary conditions                                                                         | Eve        |           | T <sub>A</sub> bits |      |       |      |

|------|----------------------------------------------------------------------------------------------------------|------------|-----------|---------------------|------|-------|------|

| Note | Event output boundary conditions                                                                         | Comparator | Interrupt | Critical            | 15   | 14    | 13   |

| 1    | $T_A \ge T_{LOWER}$                                                                                      | Н          | L         | Н                   | 0    | 0     | 0    |

| 2    | T <sub>A</sub> < T <sub>LOWER</sub> - T <sub>HYS</sub>                                                   | L          | L         | Н                   | 0    | 0     | 1    |

| 3    | T <sub>A</sub> > T <sub>UPPER</sub>                                                                      | L          | L         | Н                   | 0    | 1     | 0    |

| 4    | T <sub>A</sub> ≤ T <sub>UPPER -</sub> T <sub>HYS</sub>                                                   | Н          | L         | Н                   | 0    | 0     | 0    |

| 5    | T <sub>A</sub> ≥ T <sub>CRIT</sub>                                                                       | L          | L         | L                   | 1    | 0     | 0    |

| 6    | T <sub>A</sub> < T <sub>CRIT</sub> - T <sub>HYS</sub>                                                    | L          | Н         | Н                   | 0    | 1     | 0    |

| 7    | When $T_A \ge T_{CRIT}$ and $T_A < T_{CRIT}$ T <sub>HYS</sub> of the configuration register (interrupt m |            |           | nparator n          | node | and b | it 0 |

Systems that use the active high mode for Event output must be wired point-to-point between the STTS2004 and the sensing controller. Wire-OR configurations should not be used with active high Event output since any device pulling the Event output signal low will mask the other devices on the bus. Also note that the normal state of Event output in active high mode is a '0' which will constantly draw power through the pull-up resistor.

# 4.3 Temperature register (read-only)

This 16-bit, read-only register stores the temperature measured by the internal band gap TS as shown in *Table 13*. When reading this register, the MSBs (bit 15 to bit 8) are read first, and then the LSBs (bit 7 to bit 0) are read. The result is the current-sensed temperature. The data format is 2s complement with one LSB = 0.25 °C for the default resolution. The MSB has a 128 °C resolution.

The trip status bits represent the internal temperature trip detection, and are not affected by the status of the event or configuration bits (e.g. event output control or clear event). If neither of the above or below values are set (i.e. both are 0), then the temperature is exactly within the user-defined alarm window boundaries.

# 4.3.1 Temperature format

The 16-bit value used in the trip point set and temperature read-back registers is 2s complement, with the LSB equal to 0.0625 °C (see *Table 13*). For example:

- a value of 019C h represents 25.75 °C

- 2. a value of 07C0 h represents 124 °C, and

- 3. a value of 1E74 h represents -24.75 °C

All unused resolution bits are set to zero. The MSB will have a resolution of 128 °C. The STTS2004 supports programmable resolutions (9-12 bits) which is 0.5 to 0.0625 °C/LSB. The default is 0.25 °C/LSB (10 bits) programmable.

The upper 3 bits indicate trip status based on the current temperature, and are not affected by the event output status.

|                                     |                                         |                                         | Sign<br>MSB                                              |                                |           |          |          |          |          |          |          |          | LSB <sup>(1)</sup> |                         |                         |        |

|-------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------|--------------------------------|-----------|----------|----------|----------|----------|----------|----------|----------|--------------------|-------------------------|-------------------------|--------|

| Bit<br>15                           | Bit<br>14                               | Bit<br>13                               | Bit<br>12                                                | Bit<br>11                      | Bit<br>10 | Bit<br>9 | Bit<br>8 | Bit<br>7 | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3 | Bit<br>2           | Bit<br>1 <sup>(2)</sup> | Bit<br>0 <sup>(3)</sup> |        |

| Flag bit                            | Flag bit                                | Flag bit                                | Sign                                                     | 128                            | 64        | 32       | 16       | 8        | 4        | 2        | 1        | 0.5      | 0.25               | 0.125                   | 0.0625                  | °C/LSB |

| Above critical input <sup>(4)</sup> | Above<br>alarm<br>window <sup>(4)</sup> | Below<br>alarm<br>window <sup>(4)</sup> |                                                          | Temperature (default - 10 bit) |           |          |          |          |          |          |          |          | 0                  | 0                       |                         |        |

|                                     | Flag bits                               |                                         |                                                          |                                | Exar      | nple     | hex      | value    | of 0     | 7C0      | corre    | espo     | nds to 12          | 24 °C (1                | 0-bit)                  |        |

| 0                                   | 0                                       | 0                                       | 0                                                        | 0                              | 1         | 1        | 1        | 1        | 1        | 0        | 0        | 0        | 0                  | 0                       | 0                       | 07C0 h |

|                                     | Flag bits                               |                                         | Example hex value of 1EC0 corresponds to –20 °C (10-bit) |                                |           |          |          |          |          |          |          |          |                    |                         |                         |        |

| 0                                   | 0                                       | 0                                       | 1                                                        | 1                              | 1         | 1        | 0        | 1        | 1        | 0        | 0        | 0        | 0                  | 0                       | 0                       | 1EC0 h |

Table 13. Temperature register format

- 1. Bit 2 is LSB for default 10-bit mode.

- 2. Depending on status of the resolution register, bit 1 may display 0.125 °C value.

- 3. Depending on status of the resolution register, bit 0 may display 0.0625 °C value.

- 4. See *Table 15* for explanation.

A 0.25 °C minimum granularity is supported in all registers. Examples of valid settings and interpretation of temperature register bits for 10-bit (0.25 °C) default resolution are provided in *Table 14*.

Table 14. Temperature register coding examples (for 10 bits)

| B15:B0 (binary)     | Value  | Units |

|---------------------|--------|-------|

| xxx0 0000 0010 11xx | +2.75  | °C    |

| xxx0 0000 0001 00xx | +1.00  | °C    |

| xxx0 0000 0000 01xx | +0.25  | °C    |

| xxx0 0000 0000 00xx | 0      | °C    |

| xxx1 1111 1111 11xx | -0.25  | °C    |

| xxx1 1111 1110 00xx | -1.00  | °C    |

| xxx1 1111 1101 11xx | -2.25  | °C    |

| xxx1 1110 1100 00xx | -20.00 | °C    |

Table 15. Temperature register bit definitions

| Bit | Definition with hysteresis = 0                                                                                                                                       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | Below (temperature) alarm window  - 0 = Temperature is equal to or above the alarm window lower boundary temperature.  - 1 = Temperature is below the alarm window.  |

| 14  | Above (temperature) alarm window.  - 0 = Temperature is equal to or below the alarm window upper boundary temperature.  - 1 = Temperature is above the alarm window. |

| 15  | Above critical trip  - 0 = Temperature is below the critical temperature setting.  - 1 = Temperature is equal to or above the critical temperature setting.          |

# 4.4 Temperature trip point registers (read/write)

The STTS2004 alarm mode registers provide for 11-bit data in 2s compliment format. The data provides for one LSB = 0.25 °C. All unused bits in these registers are read as '0'.

The STTS2004 has three temperature trip point registers (see *Table 16*):

- Alarm temperature upper boundary threshold (*Table 17*)

- Alarm temperature lower boundary threshold (Table 18), and

- Critical temperature trip point value (*Table 19*)

Note:

If the upper or lower boundary threshold values are being altered in-system, all interrupts should be turned off until a known state can be obtained to avoid superfluous interrupt activity.

|    | rable to: temperature trip point register format |    |    |          |                                  |                 |               |                        |  |  |  |

|----|--------------------------------------------------|----|----|----------|----------------------------------|-----------------|---------------|------------------------|--|--|--|

| Р3 | P2                                               | P1 | P0 | Name     | Register description             | Width<br>(bits) | Type<br>(R/W) | Default state<br>(POR) |  |  |  |

| 0  | 0                                                | 1  | 0  | UPPER    | Alarm temperature upper boundary | 16              | R/W           | 00 00                  |  |  |  |

| 0  | 0                                                | 1  | 1  | LOWER    | Alarm temperature lower boundary | 16              | R/W           | 00 00                  |  |  |  |

| 0  | 1                                                | 0  | 0  | CRITICAL | Critical temperature             | 16              | R/W           | 00 00                  |  |  |  |

Table 16. Temperature trip point register format

# 4.4.1 Alarm window trip

The device provides a comparison window with an upper temperature trip point in the alarm upper boundary register, and a lower trip point in the alarm lower boundary register. When enabled, the event output will be triggered whenever entering or exiting (crossing above or below) the alarm window.

# 4.4.2 Critical trip

The device can be programmed in such a way that the event output is only triggered when the temperature exceeds the critical trip point. The critical temperature setting is programmed in the critical temperature register. When the temperature sensor reaches the critical temperature value in this register, the device is automatically placed in comparator mode, which means that the critical event output cannot be cleared by using software to set the clear event bit.

LSB<sup>(1)</sup> **MSB** Bit<sup>(3)</sup> Bit<sup>(2)</sup> Bit 0 0 0 0 Alarm window upper boundary temperature 0 0

Table 17. Alarm temperature upper boundary register format

- 1. Bit 2 is LSB for default 10-bit mode.

- 2. Depending on status of the resolution register, bit 1 may display 0.125 °C value.

- 3. Depending on status of the resolution register, bit 0 may display 0.0625  $^{\circ}\text{C}$  value.

Table 18. Alarm temperature lower boundary register format

|           |           |           | Sign<br>MSB |           |           |          |          |          |          |          |          |          | LSB <sup>(1)</sup> |                    |                         |

|-----------|-----------|-----------|-------------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|--------------------|--------------------|-------------------------|

| Bit<br>15 | Bit<br>14 | Bit<br>13 | Bit<br>12   | Bit<br>11 | Bit<br>10 | Bit<br>9 | Bit<br>8 | Bit<br>7 | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3 | Bit<br>2           | Bit <sup>(2)</sup> | Bit <sup>(3)</sup><br>0 |

| 0         | 0         | 0         |             |           | Alar      | m wind   | ow low   | er bour  | ndary te | empera   | ture     |          |                    | 0                  | 0                       |

- 1. Bit 2 is LSB for default 10-bit mode.

- 2. Depending on status of the resolution register, bit 1 may display 0.125 °C value.

- 3. Depending on status of the resolution register, bit 0 may display 0.0625 °C value.