# S1D13717 Mobile Graphics Engine with SD Card Support

# Hardware Functional Specification

Document Number: X57A-A-001-03.9

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2003-2018. All rights reserved.

### **Table of Contents**

| 1 | Introduction                                       |

|---|----------------------------------------------------|

|   | 1.1 Scope                                          |

|   | 1.2 General Description                            |

|   | 1.3 Internal Memory                                |

|   | 1.4 Host CPU Interface                             |

|   | 1.4.1 Direct Addressing Host Interfaces            |

|   | 1.4.2 Indirect Addressing Host Interfaces          |

|   | 1.4.3 Serial Port Interface for Serial LCD Control |

|   | 1.5 LCD Controller                                 |

|   | 1.5.1 RGB LCD Interface                            |

|   | 1.5.2 Parallel LCD Interface                       |

|   | 1.5.3 Serial LCD Interface                         |

|   | 1.6 Display Features                               |

|   | 1.7 Camera Interface                               |

|   | 1.8 Resizers and YUV/RGB Converter                 |

|   | 1.9 JPEG Encoder / Decoder                         |

|   | 1.9.1 Encoder                                      |

|   | 1.9.2 Decoder                                      |

|   | 1.10 2D BitBLT Engine                              |

| 2 | Features                                           |

|   | 2.1 Internal Memory                                |

|   | 2.2 Host CPU Interface                             |

|   | 2.3 Display Support                                |

|   | 2.4 Display Modes                                  |

|   | 2.5 Display Features                               |

|   | 2.6 Camera Interface                               |

|   | 2.7 Digital Video Features                         |

|   | 2.8 Picture Input / Output Functions               |

|   | 2.9 2D BitBLT Acceleration                         |

|   | 2.10 SD Memory Card Interface                      |

|   | 2.11 Clock                                         |

|   | 2.12 Power Save                                    |

|   | 2.13 Miscellaneous                                 |

| 3 | System Diagrams                                    |

| 4 | Block Diagram                                      |

| 5 | Pins                                               |

| _ |                                                    |

|   | 5.1 S1D   | 13717 Pinout Diagram (QFP21-176)                |

|---|-----------|-------------------------------------------------|

|   | 5.2 Pin l | Descriptions                                    |

|   | 5.2.1     | Unused Pins                                     |

|   | 5.2.2     | Host Interface                                  |

|   | 5.2.3     | LCD Interface                                   |

|   | 5.2.4     | Camera Interface                                |

|   | 5.2.5     | SD Memory Card Interface                        |

|   | 5.2.6     | Clock Input                                     |

|   | 5.2.7     | Miscellaneous                                   |

|   | 5.2.8     | Power And Ground                                |

|   | 5.3 Sum   | mary of Configuration Options                   |

|   | 5.4 Host  | Interface Pin Mapping                           |

|   | 5.5 LCD   | Interface Pin Mapping                           |

|   | 5.6 Cam   | era Interface Pin Mapping                       |

| 6 | D.C. Cha  | racteristics                                    |

| 7 | A.C. Cha  | racteristics                                    |

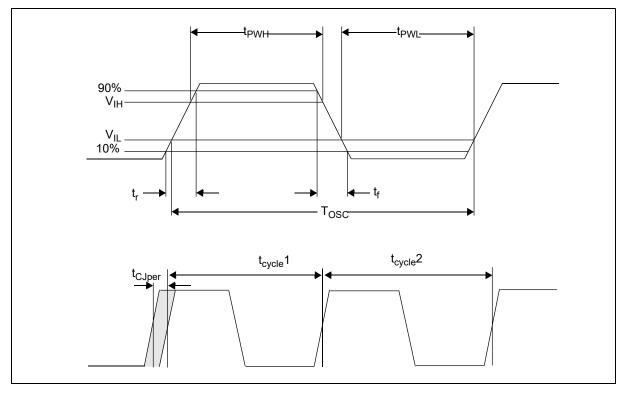

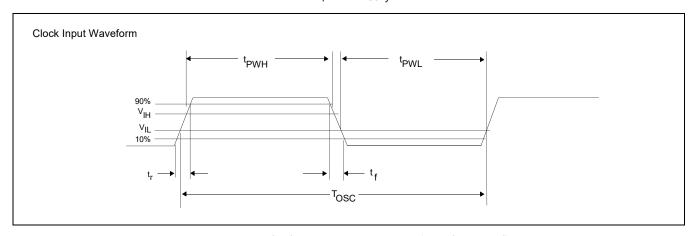

|   | 7.1 Cloc  | k Timing                                        |

|   | 7.1.1     | Input Clocks                                    |

|   | 7.1.2     | PLL Clock                                       |

|   | 7.1.3     | Internal Clocks                                 |

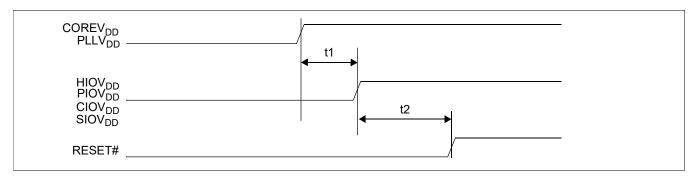

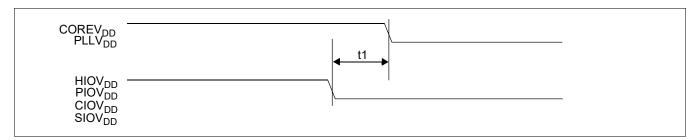

|   | 7.2 Pow   | er Supply Sequence                              |

|   | 7.2.1     | Power-On Sequence                               |

|   | 7.2.2     | Power-Off Sequence                              |

|   | 7.3 Host  | Interface Timing                                |

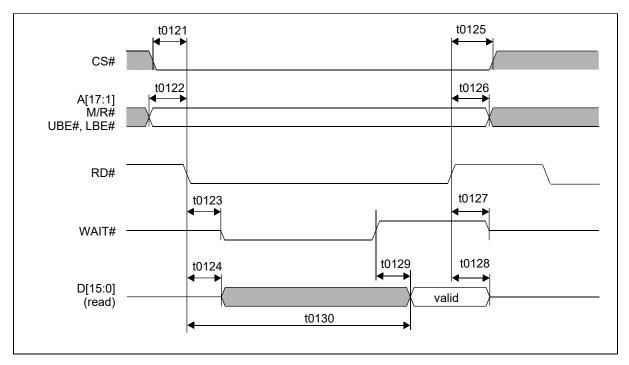

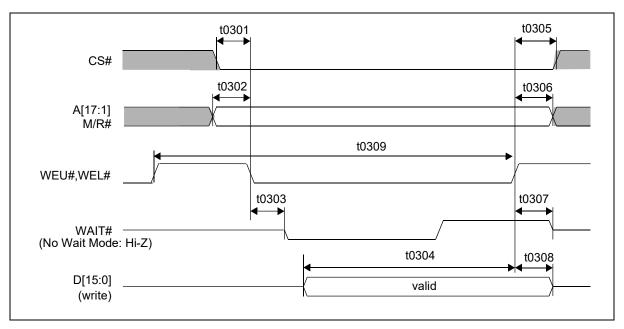

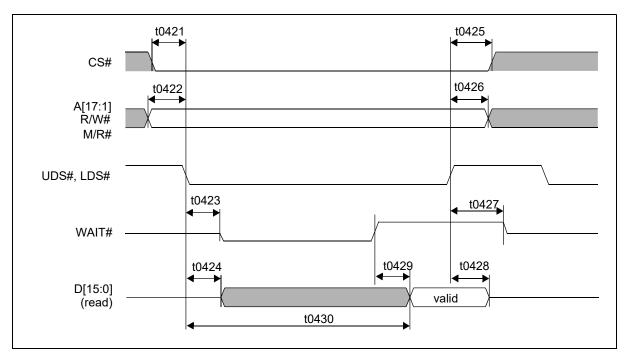

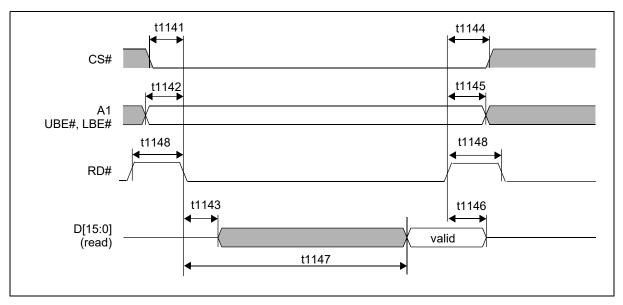

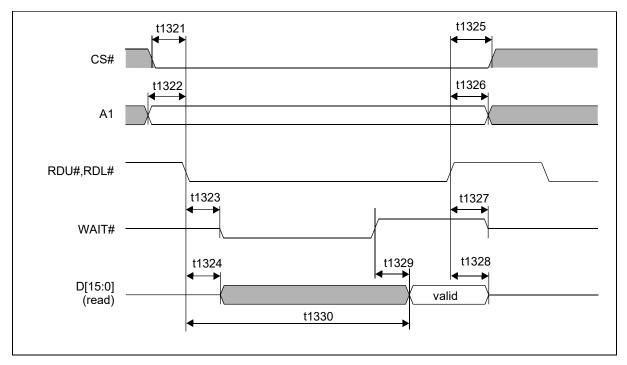

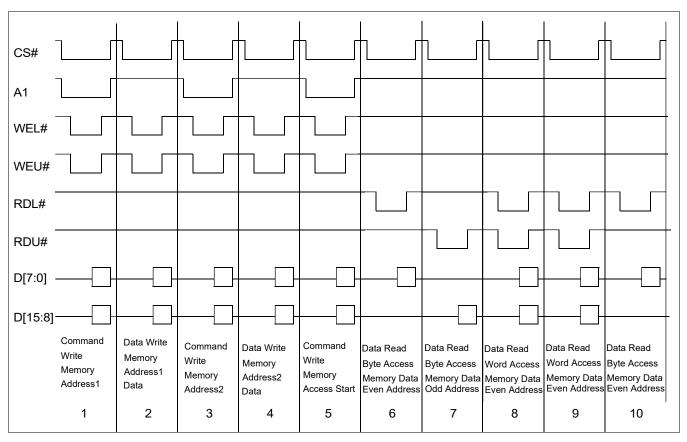

|   | 7.3.1     | Direct 80 Type 1                                |

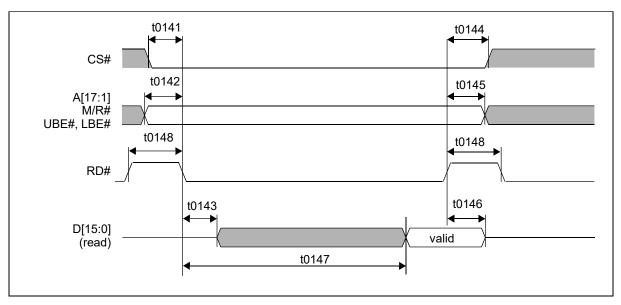

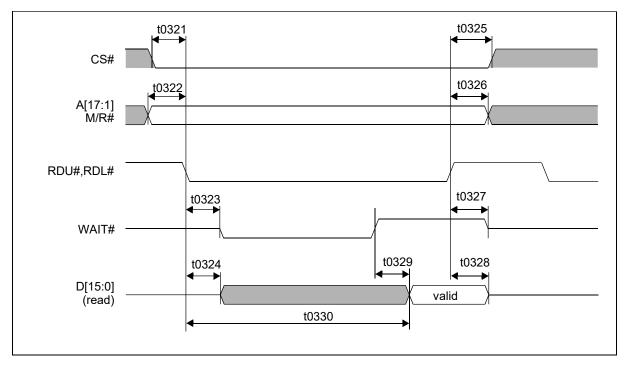

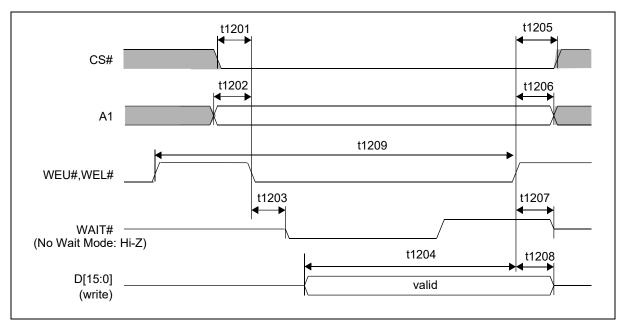

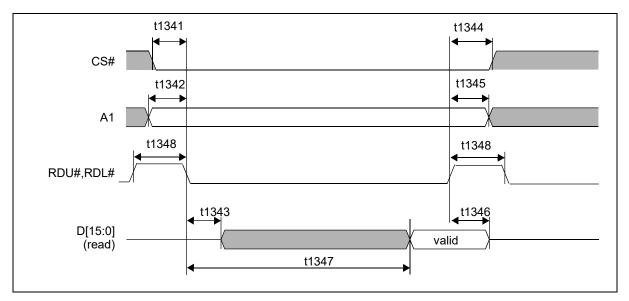

|   | 7.3.2     | Direct 80 Type 2                                |

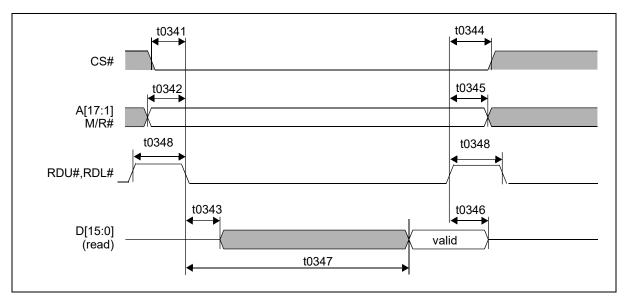

|   | 7.3.3     | Direct 80 Type 3                                |

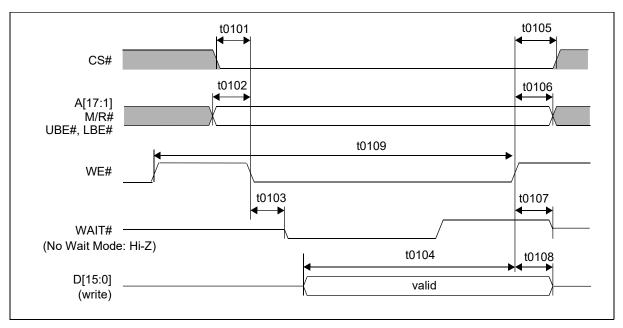

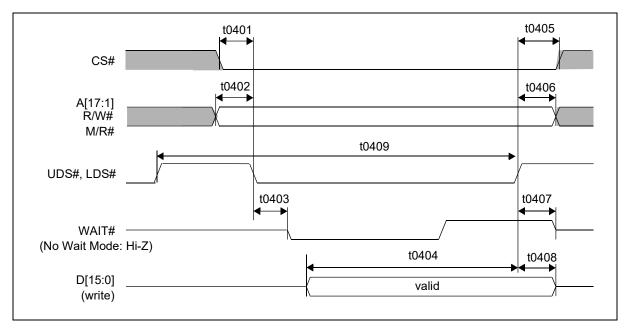

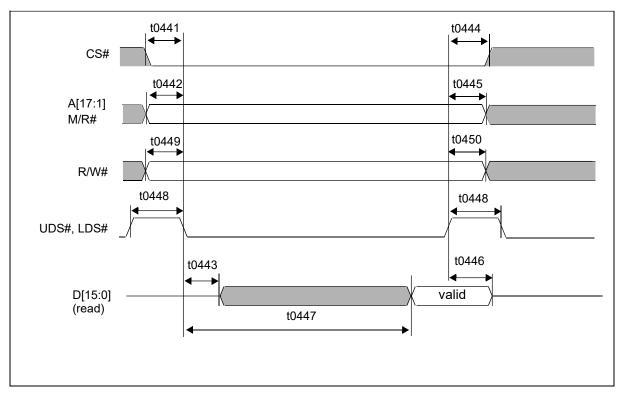

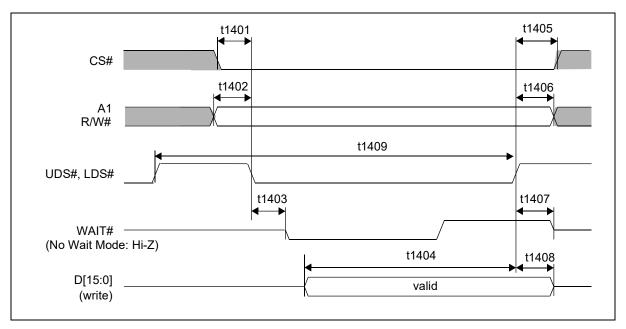

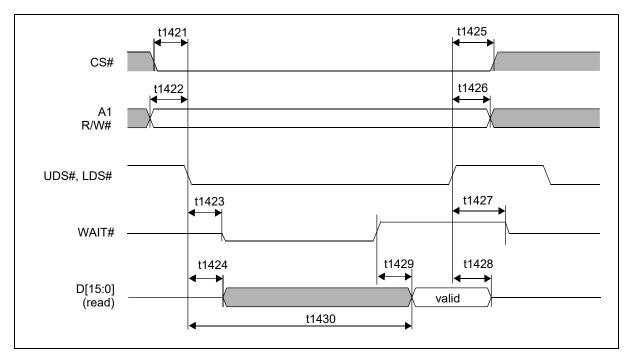

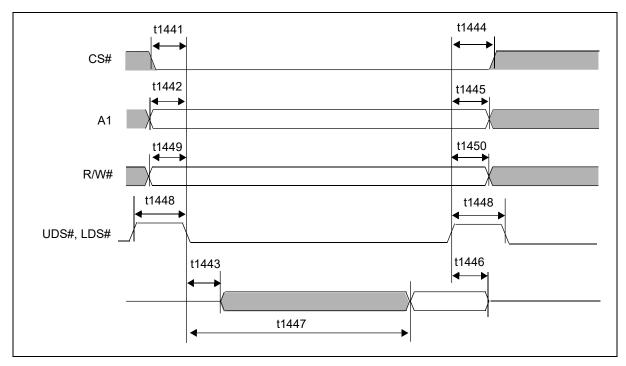

|   | 7.3.4     | Direct 68                                       |

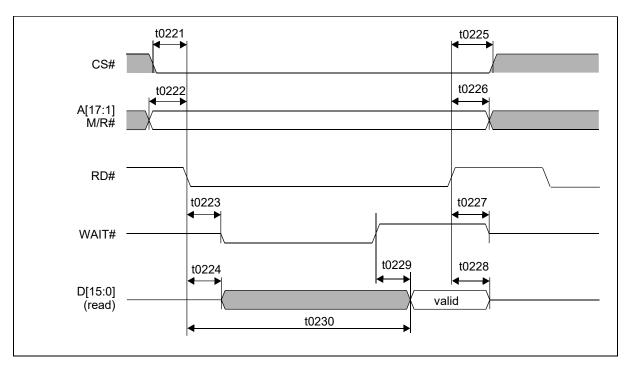

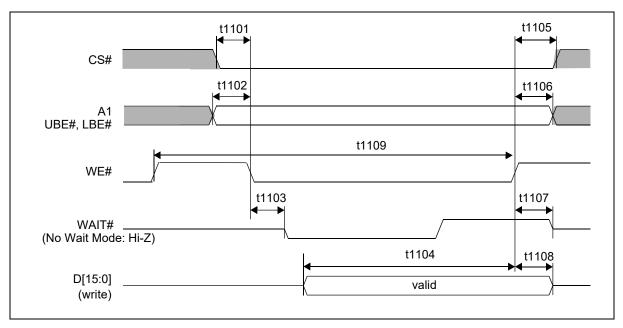

|   | 7.3.5     | Indirect 80 Type 1                              |

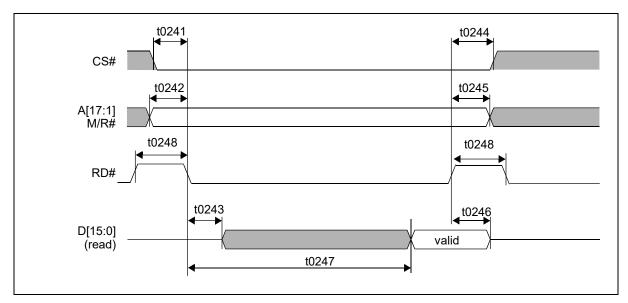

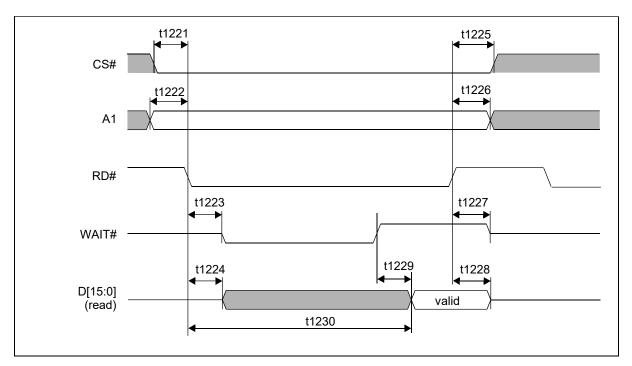

|   | 7.3.6     | Indirect 80 Type 2                              |

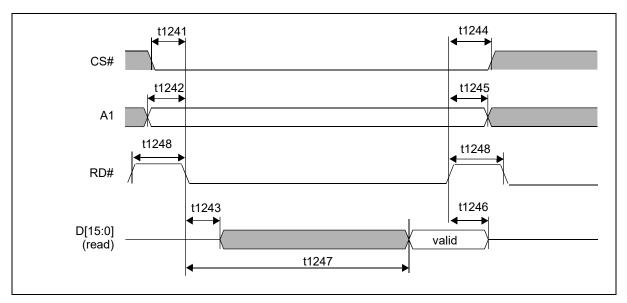

|   | 7.3.7     | Indirect 80 Type 3                              |

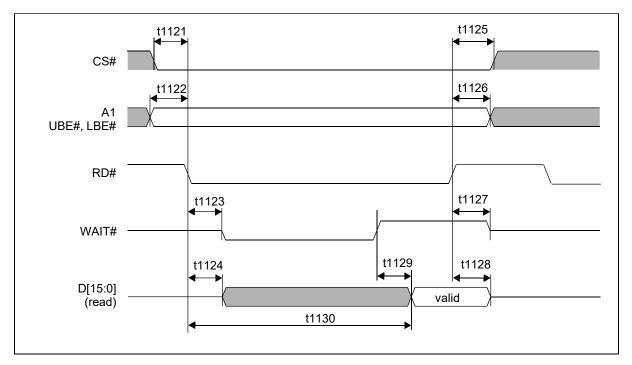

|   | 7.3.8     | Indirect 68                                     |

|   | 7.3.9     | WAIT Length                                     |

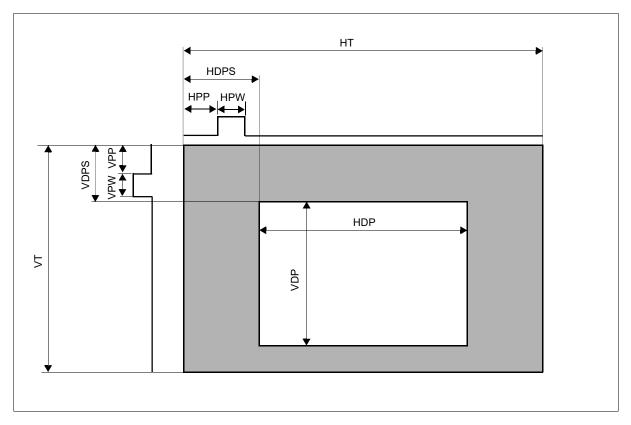

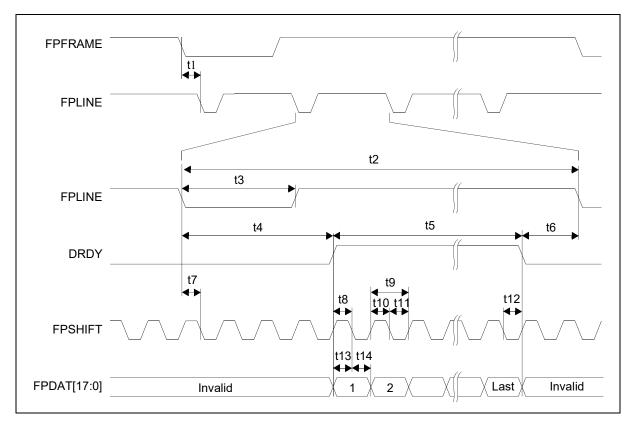

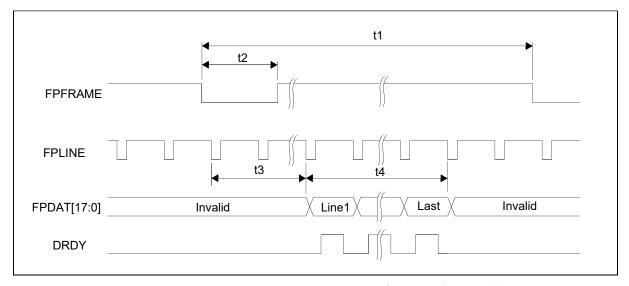

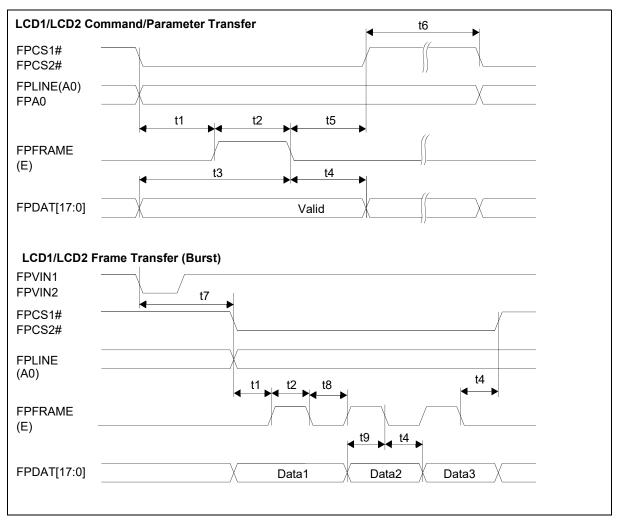

|   | 7.4 Pane  | el Interface Timing                             |

|   | 7.4.1     | Generic TFT Panel Timing                        |

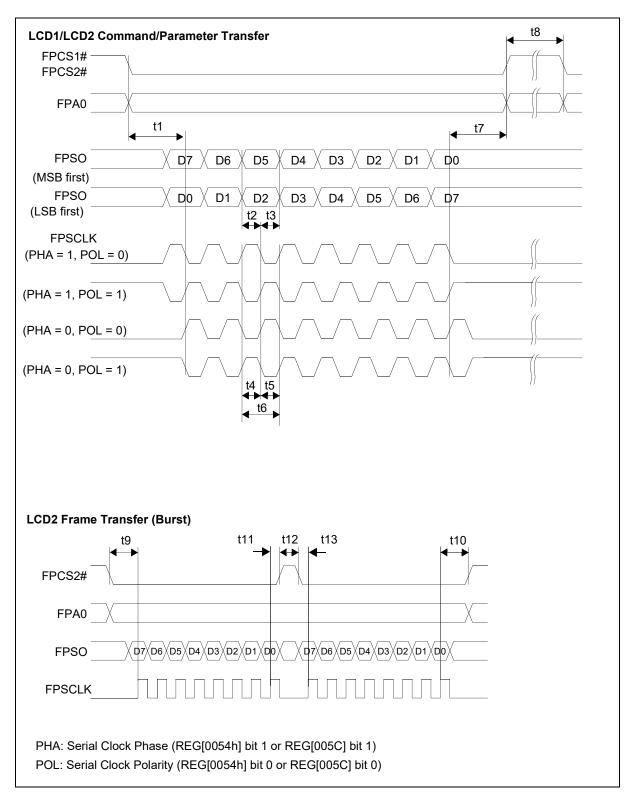

|   | 7.4.2     | LCD1 ND-TFD, LCD2 8-Bit Serial Interface Timing |

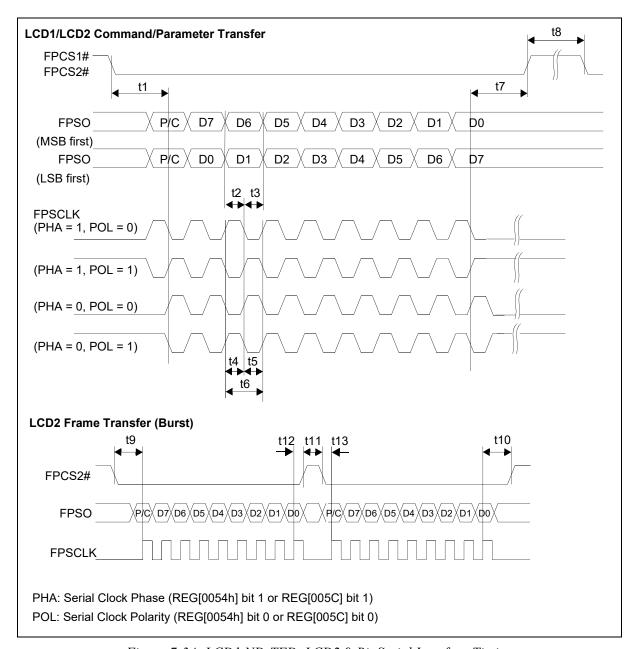

|   | 7.4.3     | LCD1 ND-TFD, LCD2 9-Bit Serial Interface Timing |

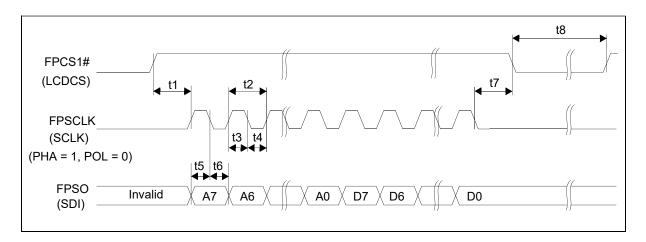

|   | 7.4.4     | LCD1 a-Si TFT Serial Interface Timing           |

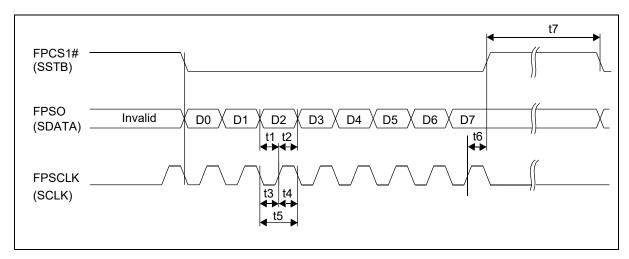

|   | 7.4.5     | LCD1 uWIRE Serial Interface Timing              |

4

|    |      | 7.4.6  | LCD1, LCD2 Parallel Interface Timing (80)      | . 97  |

|----|------|--------|------------------------------------------------|-------|

|    | ,    | 7.4.7  | LCD1, LCD2 Parallel Interface Timing (68)      | . 98  |

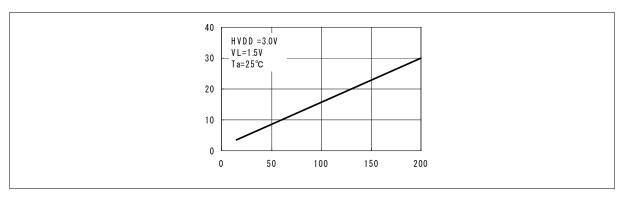

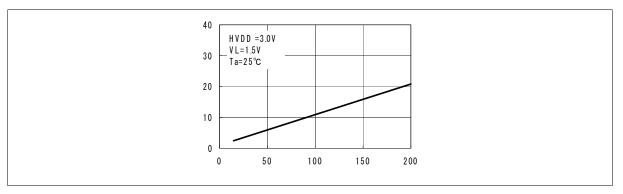

|    | 7.5  | Outp   | ut Buffer Rise/Fall Time v.s. Capacitance (CL) | . 99  |

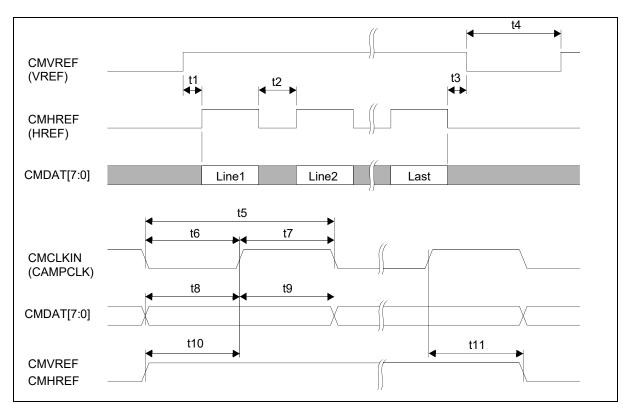

|    | 7.6  | Came   | era Interface Timing                           | . 100 |

|    | ,    | 7.6.1  | Camera Interface Timing                        | . 100 |

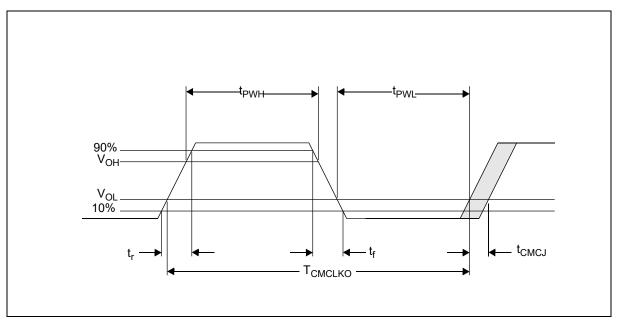

|    | •    | 7.6.2  | Camera Clock Output Timing                     | . 101 |

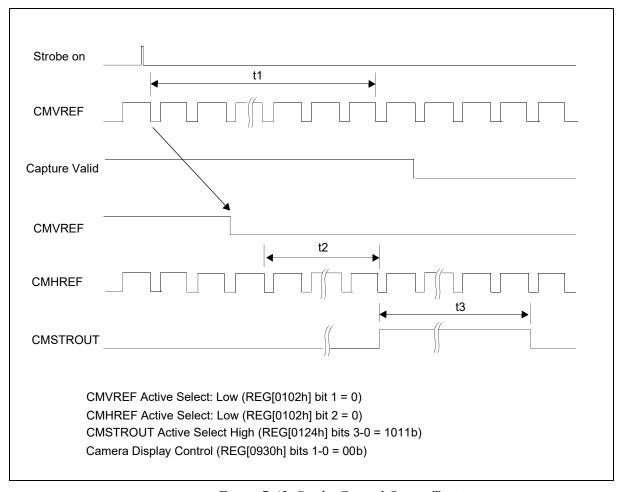

|    | ,    | 7.6.3  | Strobe Timing                                  | . 102 |

|    | 7.7  | SD M   | Iemory Card Interface                          |       |

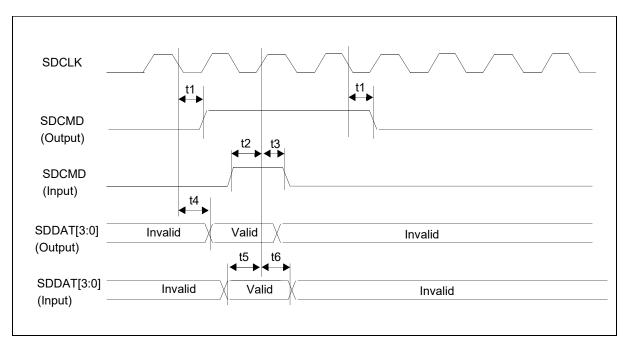

|    | •    | 7.7.1  | SD Memory Card Access                          | . 103 |

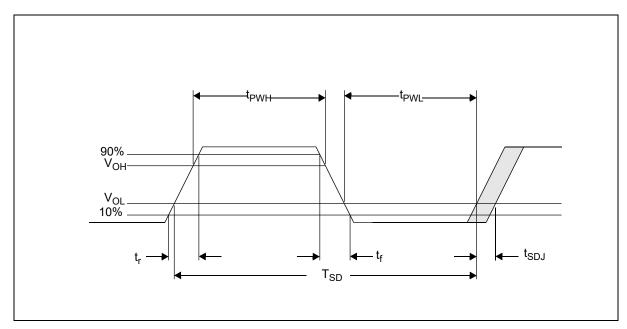

|    | ,    | 7.7.2  | SD Memory Card Clock Output                    | . 104 |

| 8  | Men  | nory A | Allocation                                     | 105   |

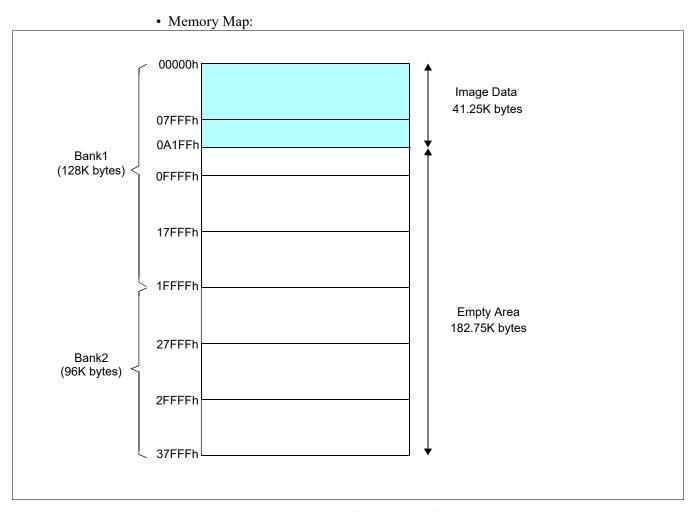

|    | 8.1  | Main   | Window Case 1                                  | . 105 |

|    | 8    | 8.1.1  | Environment                                    | . 105 |

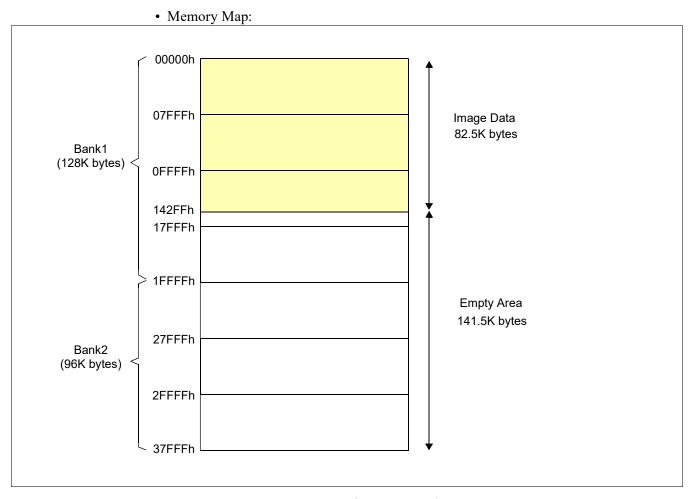

|    | 8.2  | Main   | Window Case 2                                  | . 107 |

|    | 8    | 8.2.1  | Environment                                    | . 107 |

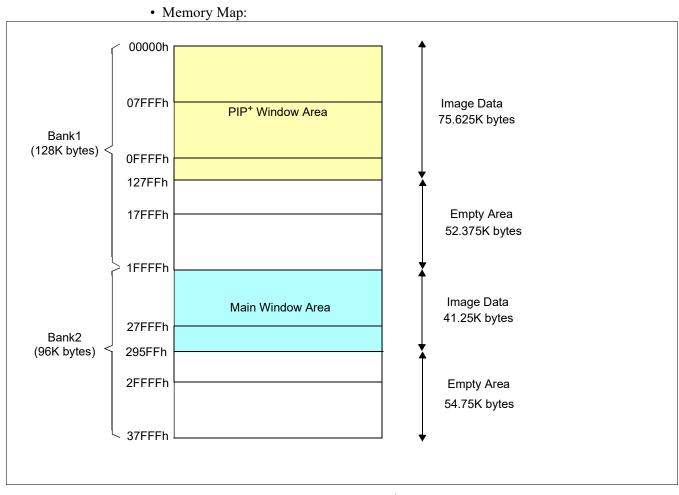

|    | 8.3  | Main   | Window, PIP+ Window, and Overlay Display       | . 109 |

|    | 8    | 8.3.1  | Environment                                    | . 109 |

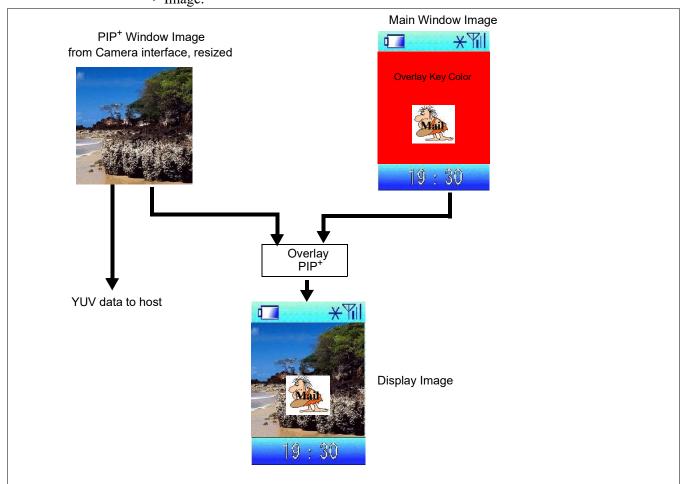

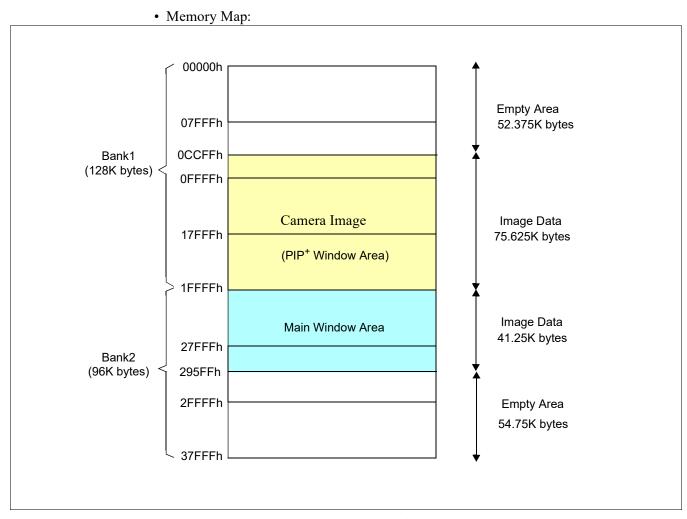

|    | 8.4  | Main   | Window, PIP+ Window, Overlay, and YUV          | . 111 |

|    | 8    | 8.4.1  | Environment                                    | . 111 |

|    | 8.5  | Main   | Window, PIP+ Window, Overlay, and JPEG         | . 113 |

|    | 8    | 8.5.1  | Environment                                    | . 113 |

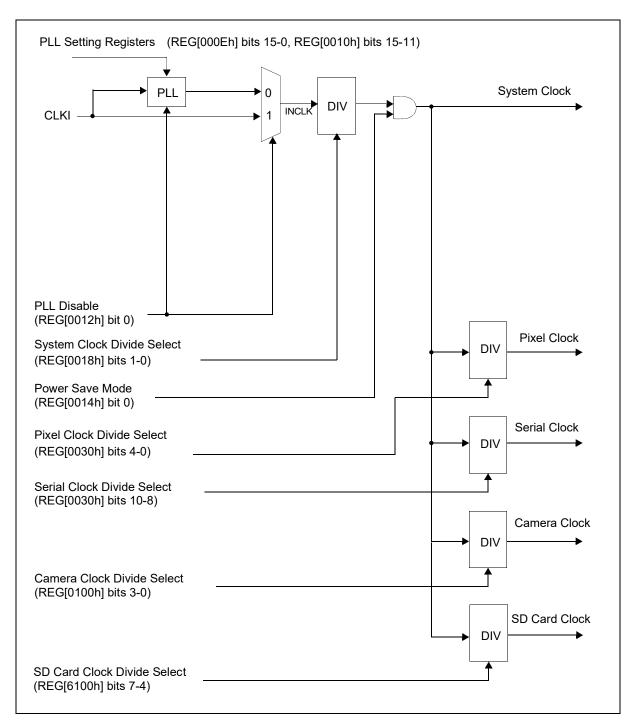

| 9  | Clo  | cks .  |                                                | 115   |

|    | 9.1  | Clock  | c Diagram                                      | . 115 |

|    | 9.2  | Clock  | cs                                             | . 116 |

|    | 9    | 9.2.1  | System Clock                                   | . 116 |

|    | 9    | 9.2.2  | Pixel Clock                                    | . 116 |

|    | Ģ    | 9.2.3  | Serial Clock                                   | . 116 |

|    | Ģ    | 9.2.4  | Camera Clock                                   | . 116 |

|    | Ģ    | 9.2.5  | SD Memory Card Clock                           | . 116 |

| 10 | Reg  | isters |                                                | 117   |

|    |      |        | ster Mapping                                   |       |

|    |      |        | ster Set                                       |       |

|    |      |        | ster Restrictions                              |       |

|    | 10.4 | Regis  | ster Description                               | . 123 |

|    |      | _      | System Configuration Registers                 |       |

|    |      |        | Clock Setting Registers                        |       |

|    |      |        | Indirect Interface Registers                   |       |

|    |      |        | LCD Panel Interface Generic Setting Registers  |       |

|    |      |        | LCD1 Setting Register                          | . 140 |

|    | 10.4.6 LCD2 Setting Registers                   | 147 |

|----|-------------------------------------------------|-----|

|    | 10.4.7 Camera Interface Setting Register        | 151 |

|    | 10.4.8 Display Mode Setting Register            | 162 |

|    | 10.4.9 GPIO Registers                           | 185 |

|    | 10.4.10 Overlay Registers                       | 187 |

|    | 10.4.11 LUT1 (Main Window) Registers            | 197 |

|    | 10.4.12 LUT2 (PIP+ Window) Registers            | 198 |

|    | 10.4.13 Resizer Operation Registers             | 199 |

|    | 10.4.14 JPEG Module Registers                   | 214 |

|    | 10.4.15 JPEG FIFO Setting Register              | 230 |

|    | 10.4.16 JPEG Line Buffer Setting Register       | 237 |

|    | 10.4.17 Interrupt Control Registers             | 242 |

|    | 10.4.18 JPEG Encode Performance Register        | 250 |

|    | 10.4.19 JPEG Codec Registers                    | 251 |

|    | 10.4.20 SD Memory Card Interface Registers      | 268 |

|    | 10.4.21 2D BitBLT Registers                     | 287 |

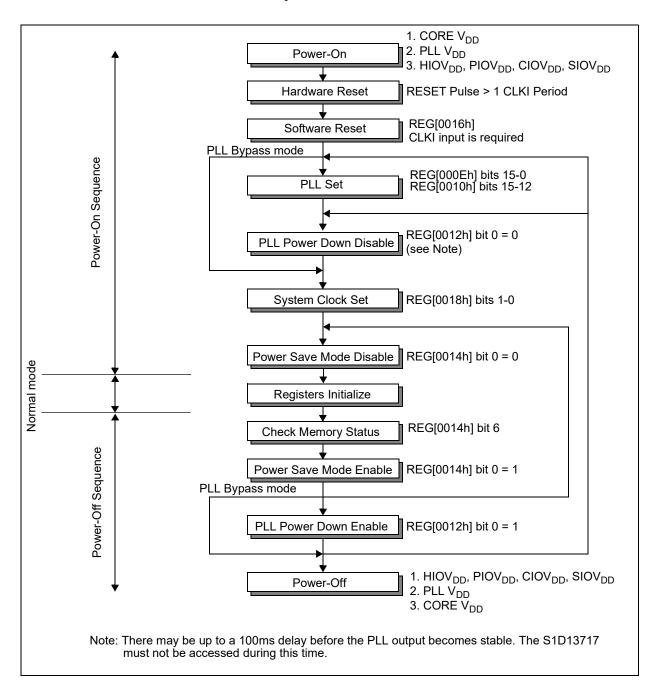

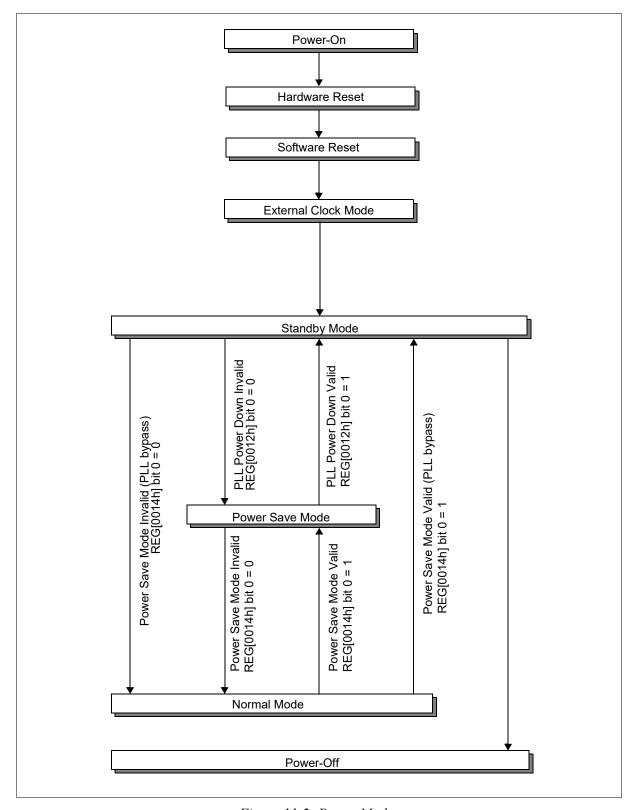

| 11 | Power Save Modes                                | 295 |

|    | 11.1 Power-On/Power-Off Sequence                | 295 |

|    | 11.1.1 Power-On                                 | 297 |

|    | 11.1.2 Reset                                    | 297 |

|    | 11.1.3 Standby Mode                             | 297 |

|    | 11.1.4 Power Save Mode                          | 297 |

|    | 11.1.5 Normal Mode                              | 298 |

|    | 11.1.6 Power-Off                                | 298 |

|    | 11.2 Power Save Mode Function                   | 298 |

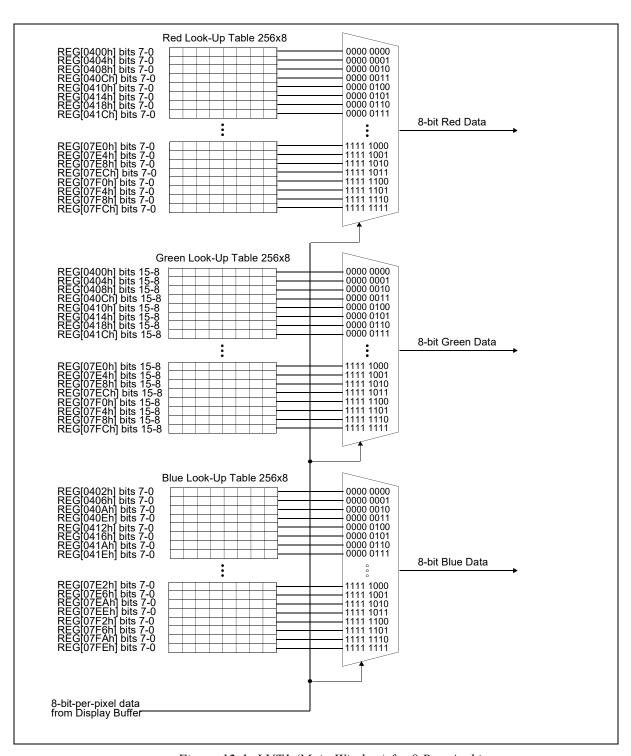

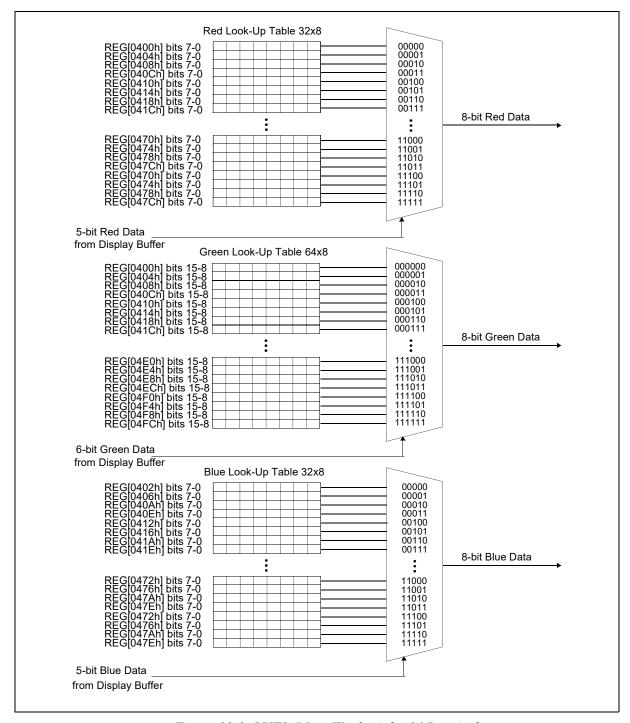

| 12 | LUT Architecture                                | 299 |

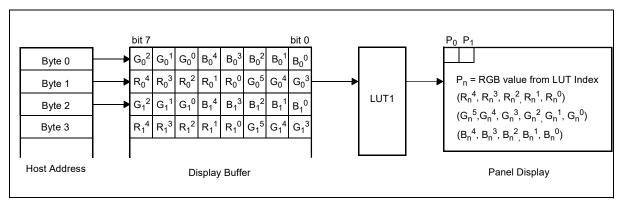

|    | 12.1 LUT1 (Main Window) for 8 bpp               | 299 |

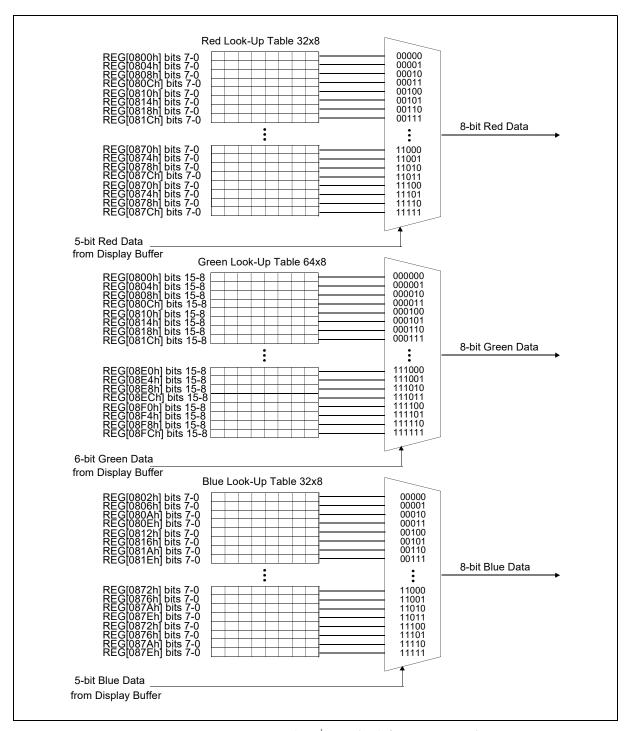

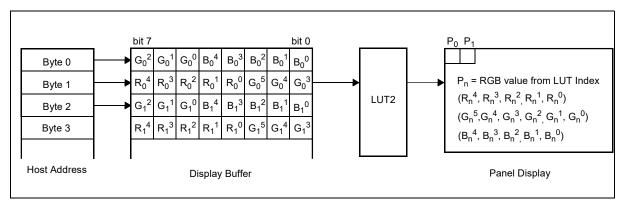

|    | 12.2 LUT2 (PIP+ Window) for 8 Bpp Architecture  | 300 |

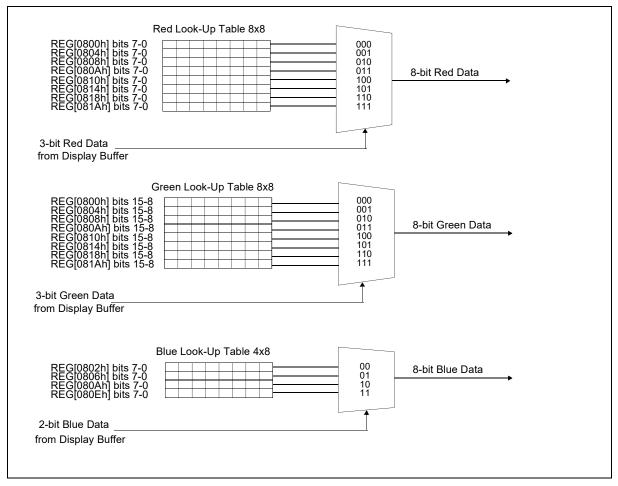

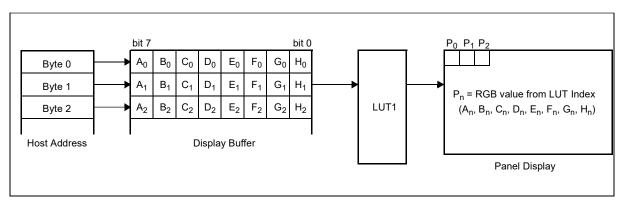

|    | 12.3 LUT1 (Main Window) for 16 Bpp Architecture | 301 |

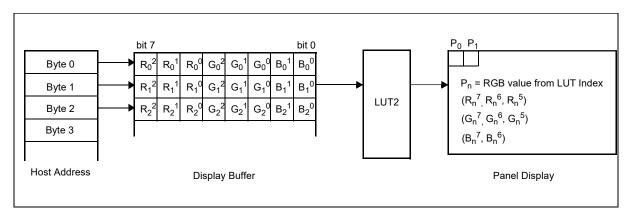

|    | 12.4 LUT2 (PIP+ Window) for 16 Bpp Architecture | 302 |

| 13 | Display Data Formats                            | 303 |

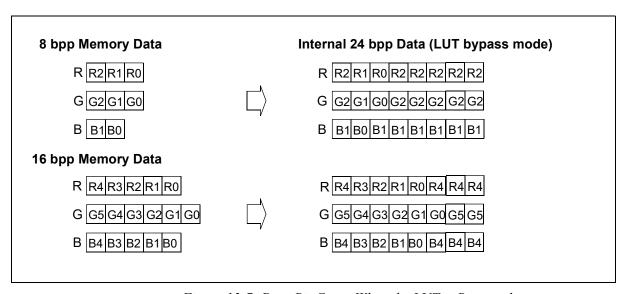

|    | 13.1 Display Data for LUT Mode                  |     |

|    | 13.1.1 8 Bpp Mode                               |     |

|    | 13.1.2 16 Bpp Mode                              |     |

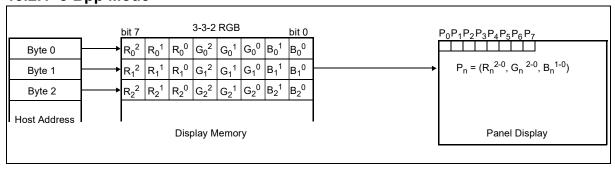

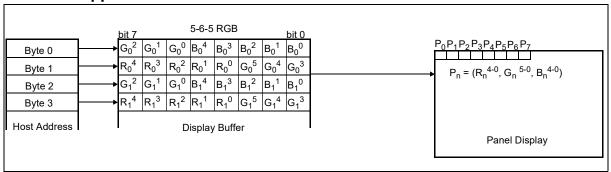

|    | 13.2 Display Data for LUT Bypass Mode           |     |

|    | 13.2.1 8 Bpp Mode                               |     |

|    | 13.2.2 16 Bpp Mode                              |     |

|    | 13.3 Display Data Flow                          |     |

|    | 13.3.1 Display Buffer Data                      |     |

|    | 13.3.2 Bit Cover When LUT Bypassed          | . 306 |

|----|---------------------------------------------|-------|

|    | 13.3.3 Overlay                              | . 306 |

|    | 13.4 Parallel Data Format                   | . 307 |

|    | 13.4.1 8-Bit Parallel, RGB=3:3:2            | . 307 |

|    | 13.4.2 8-Bit Parallel, RGB=4:4:4            | . 308 |

|    | 13.4.3 8-Bit Parallel, RGB=8:8:8            | . 308 |

|    | 13.4.4 16-Bit Parallel, RGB=4:4:4           | . 309 |

|    | 13.4.5 16-Bit Parallel, RGB=5:6:5           | .310  |

|    | 13.4.6 18-Bit Parallel, RGB=6:6:6           | . 311 |

|    | 13.4.7 16-Bit Parallel, RGB=8:8:8           | . 312 |

|    | 13.5 Serial Data Format                     | . 313 |

|    | 13.5.1 8-Bit Serial, RGB=3:3:2              | . 313 |

|    | 13.5.2 8-Bit Serial, RGB=4:4:4              | . 313 |

|    | 13.6 YUV Input / Output Data Format         | . 314 |

|    | 13.6.1 YUV 4:2:2 Data Input / Output Format | .314  |

|    | 13.6.2 YUV 4:2:0 Data Input / Output Format |       |

|    | 13.7 YUV/RGB Conversion                     | . 317 |

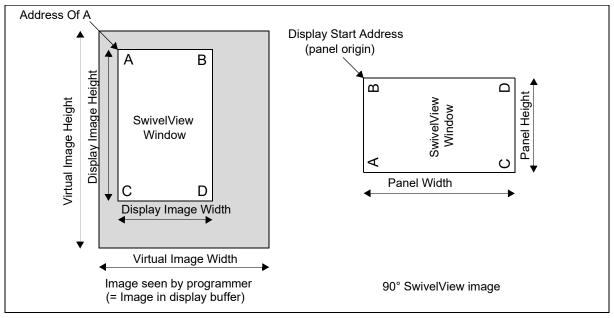

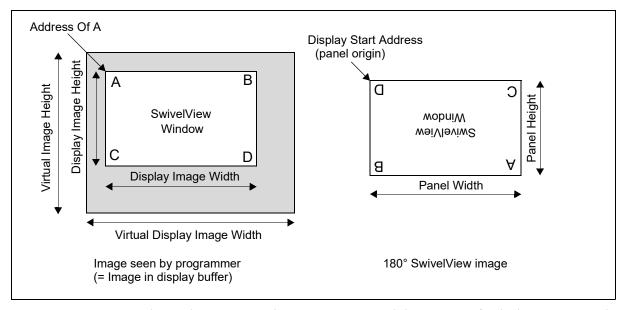

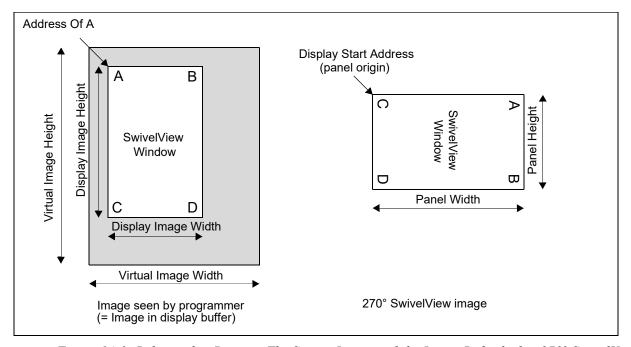

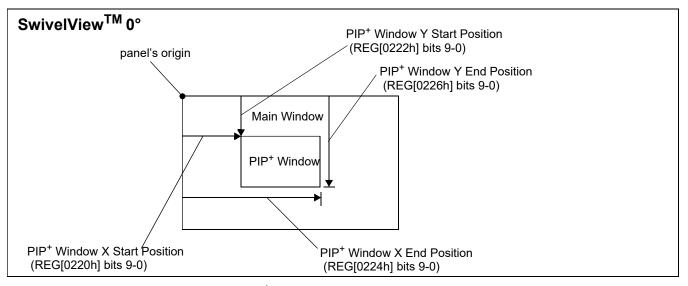

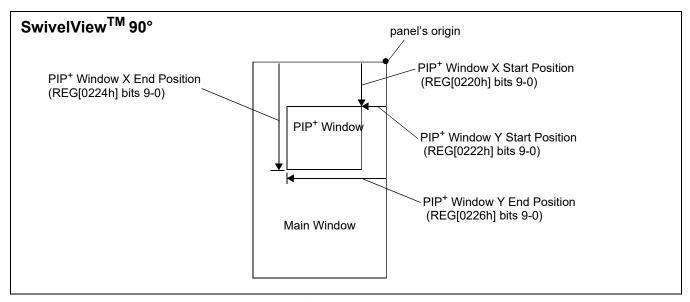

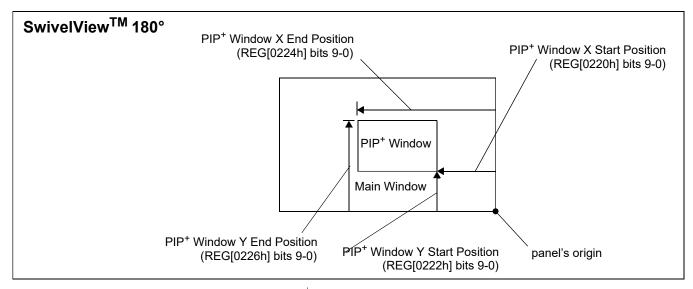

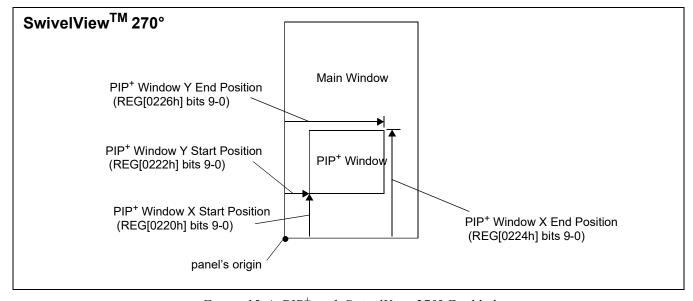

| 14 | SwivelView™                                 | 318   |

|    | 14.1 SwivelView Modes                       | . 319 |

|    | 14.1.1 90° SwivelView                       | .319  |

|    | 14.1.2 180° SwivelView                      | . 320 |

|    | 14.1.3 270° SwivelView                      | . 321 |

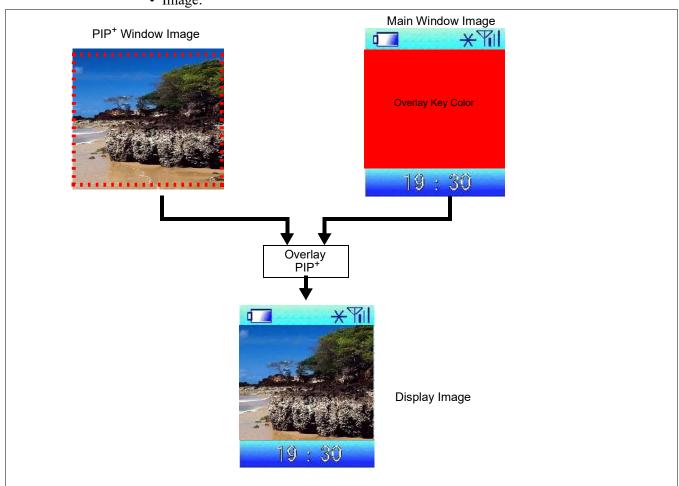

| 15 | Picture-in-Picture Plus (PIP+)              | 322   |

|    | 15.1 Overlay Display                        | . 324 |

|    | 15.1.1 Overlay Display Effects              | . 325 |

| 16 | 2D BitBLT Engine                            | 328   |

|    | 16.1 Overview                               |       |

|    | 16.2 BitBLTs                                | . 328 |

|    | 16.2.1 Read BitBLT                          | . 328 |

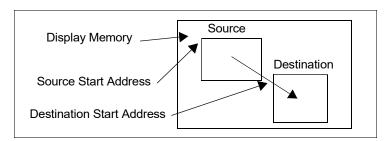

|    | 16.2.2 Move BitBLT                          | . 329 |

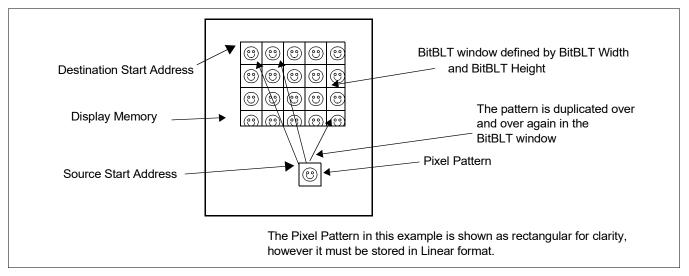

|    | 16.2.3 Pattern Fill BitBLT                  | . 330 |

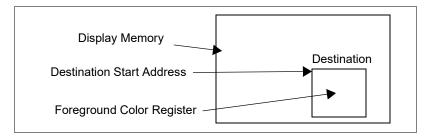

|    | 16.2.4 Solid Fill BitBLT                    | . 331 |

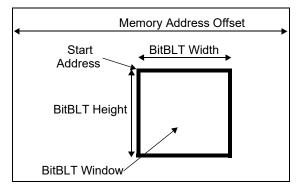

|    | 16.2.5 BitBLT Terms                         | . 332 |

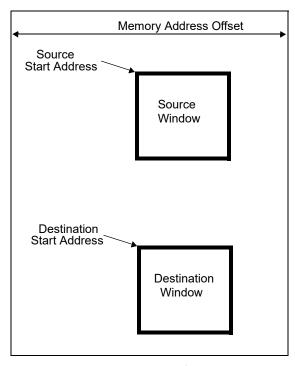

|    | 16.2.6 Source and Destination               | . 333 |

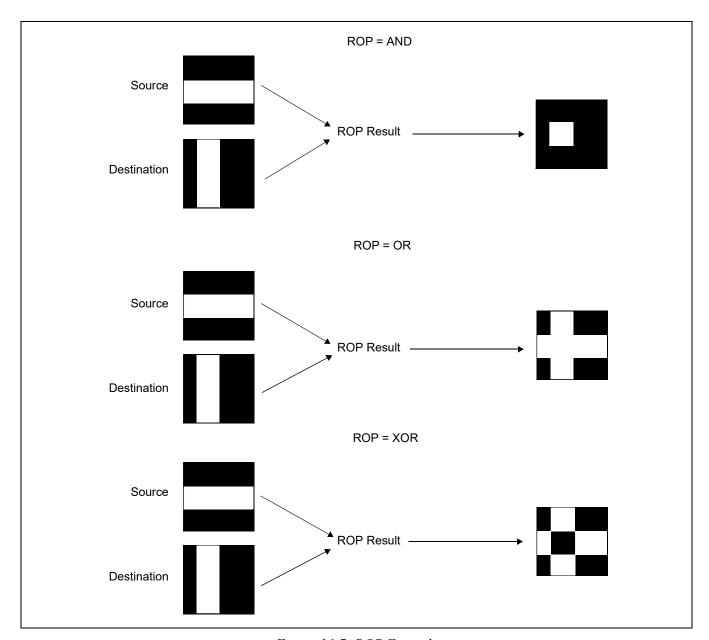

|    | 16.3 Data Functions                         | . 334 |

|    | 16.3.1 ROP                                  | . 335 |

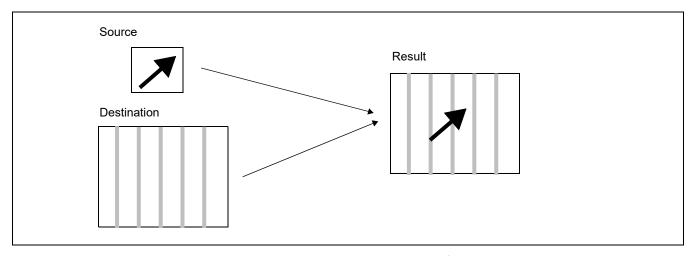

|    | 16.3.2 Transparency                         | . 336 |

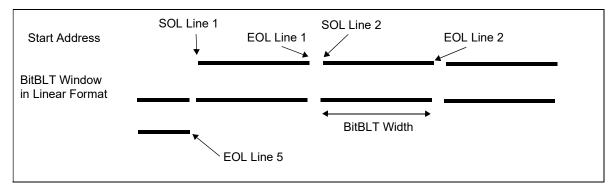

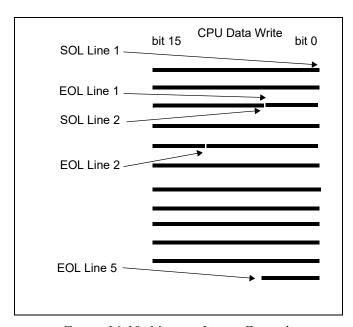

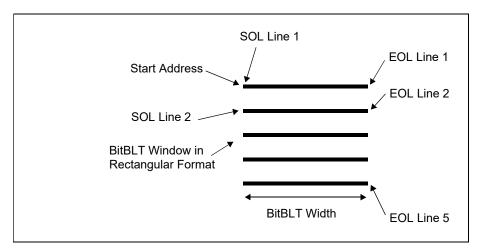

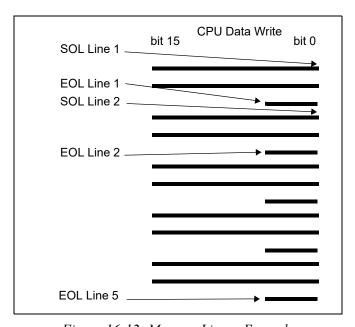

|    | 16.4 Linear / Rectangular                   | . 337 |

| 17 | Resizers                                    | 339   |

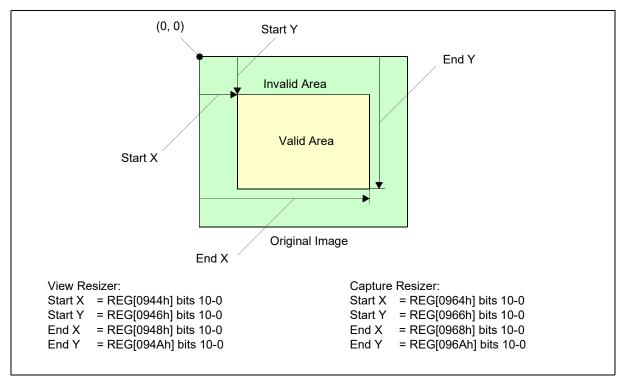

|    | 17.1 Trimming Function                            | . 339 |

|----|---------------------------------------------------|-------|

|    | 17.2 Scaling Function                             | . 341 |

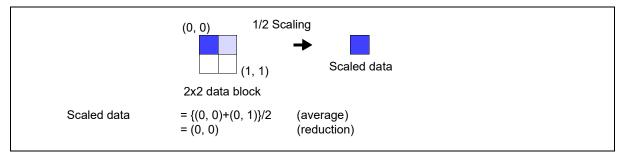

|    | 17.2.1 1/2 Scaling                                | .341  |

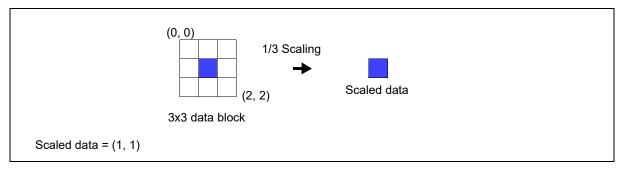

|    | 17.2.2 1/3 Scaling                                | .342  |

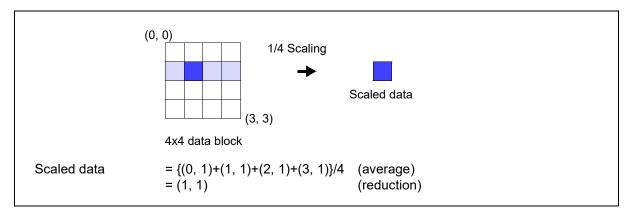

|    | 17.2.3 1/4 Scaling                                | .342  |

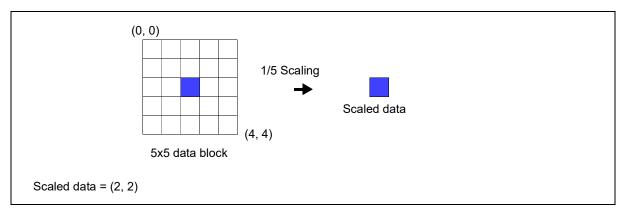

|    | 17.2.4 1/5 Scaling                                | .343  |

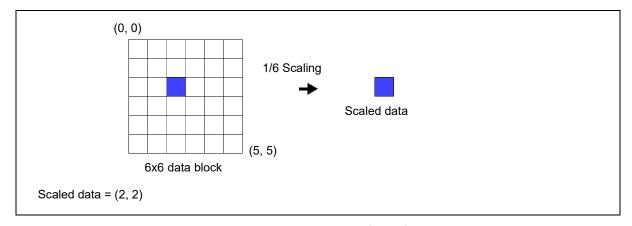

|    | 17.2.5 1/6 Scaling                                | .343  |

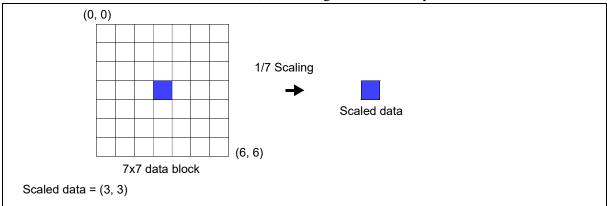

|    | 17.2.6 1/7 Scaling                                | .344  |

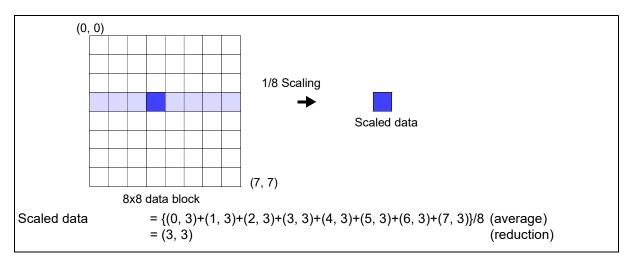

|    | 17.2.7 1/8 Scaling                                | .344  |

|    | 17.3 Resizer Restrictions                         | . 345 |

| 18 | Digital Video Functions                           | . 348 |

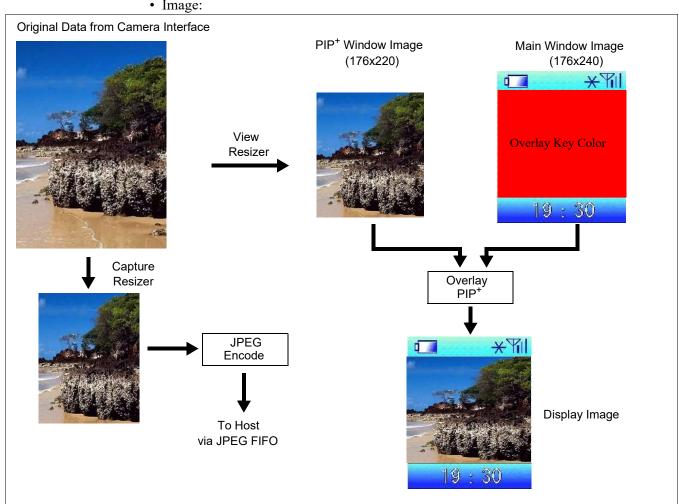

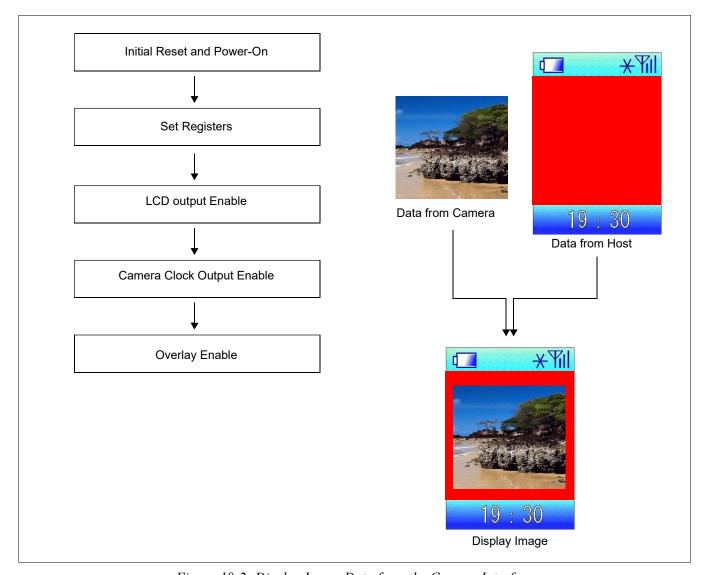

|    | 18.1 Display Image Data from the Camera Interface | . 349 |

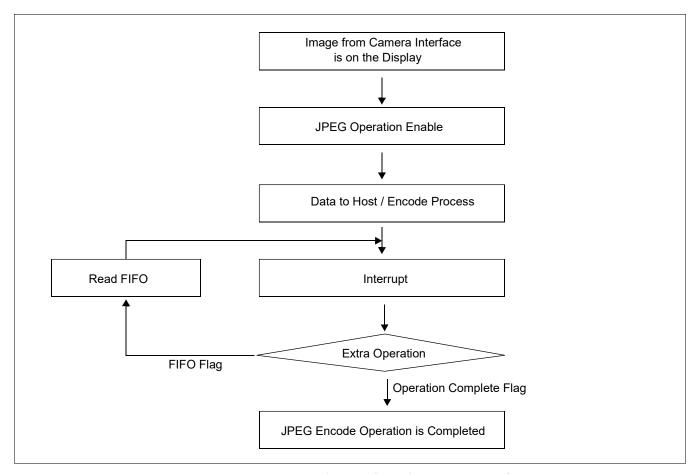

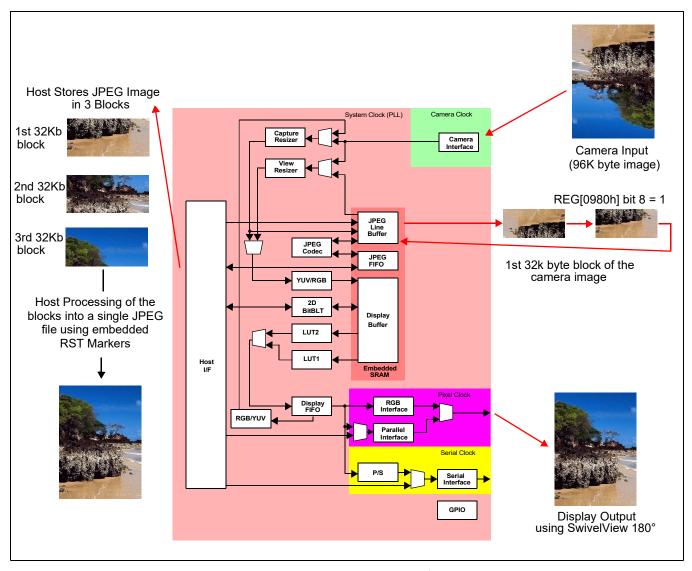

|    | 18.2 JPEG Encode and Camera Data to the Host      | . 350 |

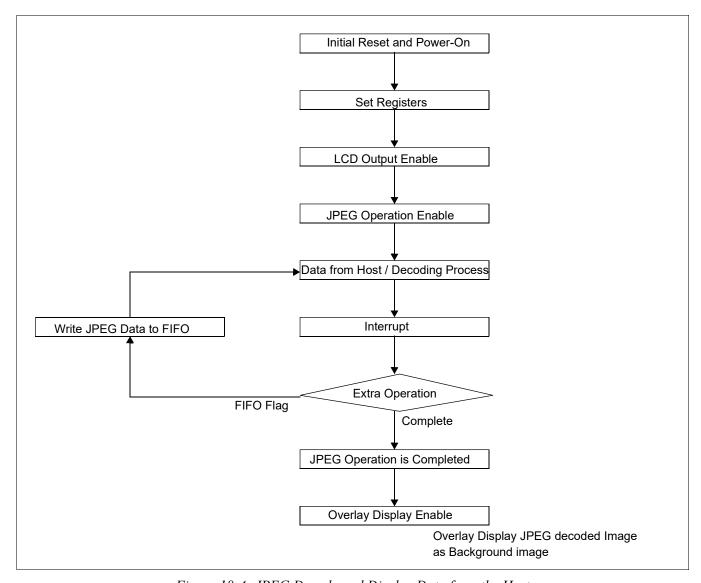

|    | 18.3 JPEG Decode and Display Data from the Host   | . 351 |

|    | 18.4 JPEG 180° Rotate Encode Diagram              | . 352 |

| 19 | JPEG Encode/Decode Operation                      | . 353 |

|    | 19.1 JPEG Features                                | . 353 |

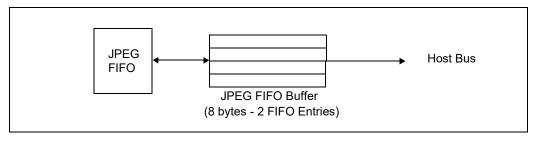

|    | 19.1.1 JPEG FIFO                                  | .353  |

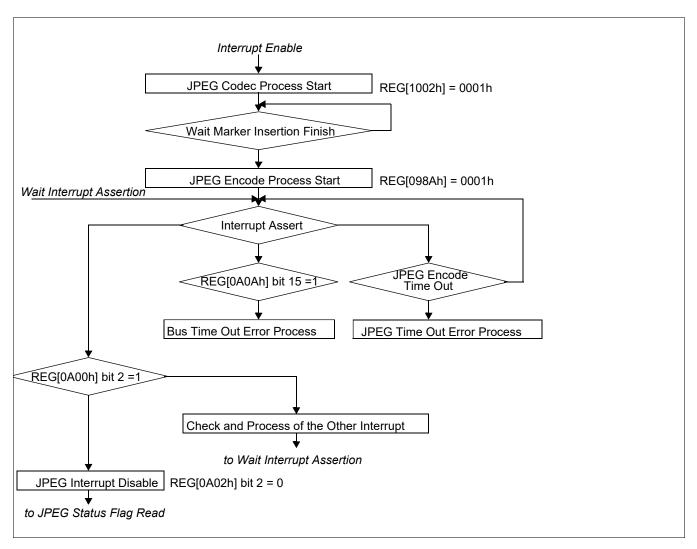

|    | 19.1.2 JPEG Codec Interrupts                      | .354  |

|    | 19.1.3 JPEG Bypass Modes                          | .355  |

|    | 19.2 Example Sequences                            | . 357 |

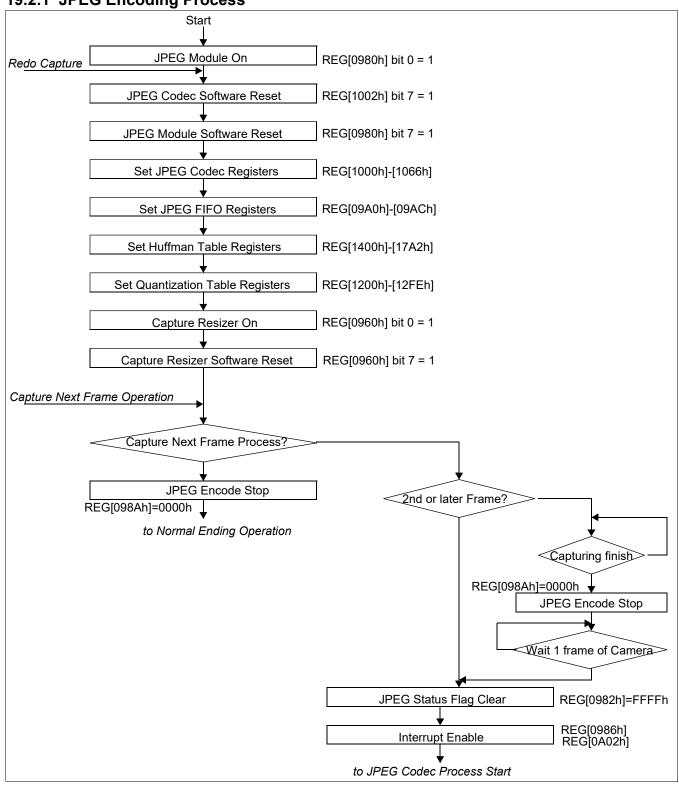

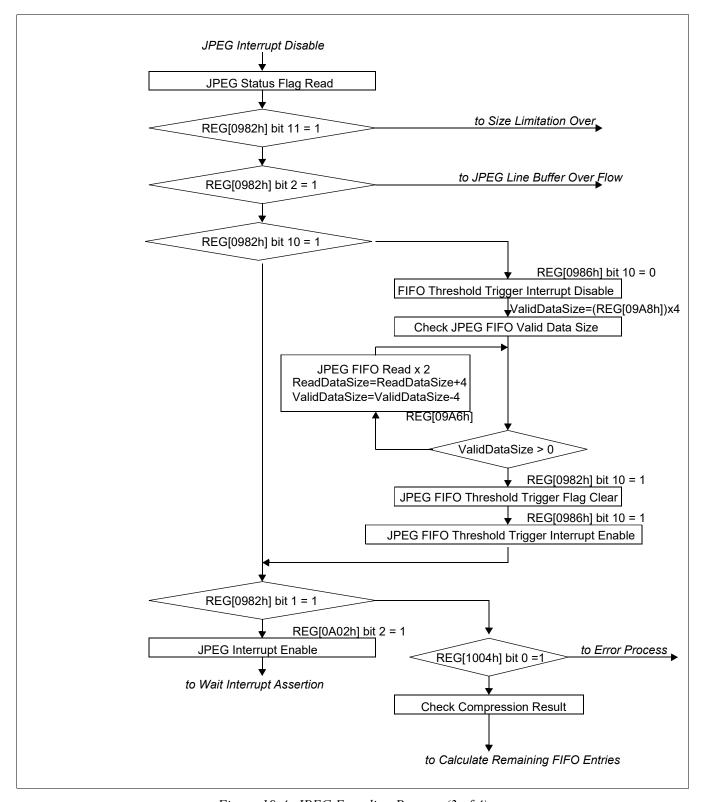

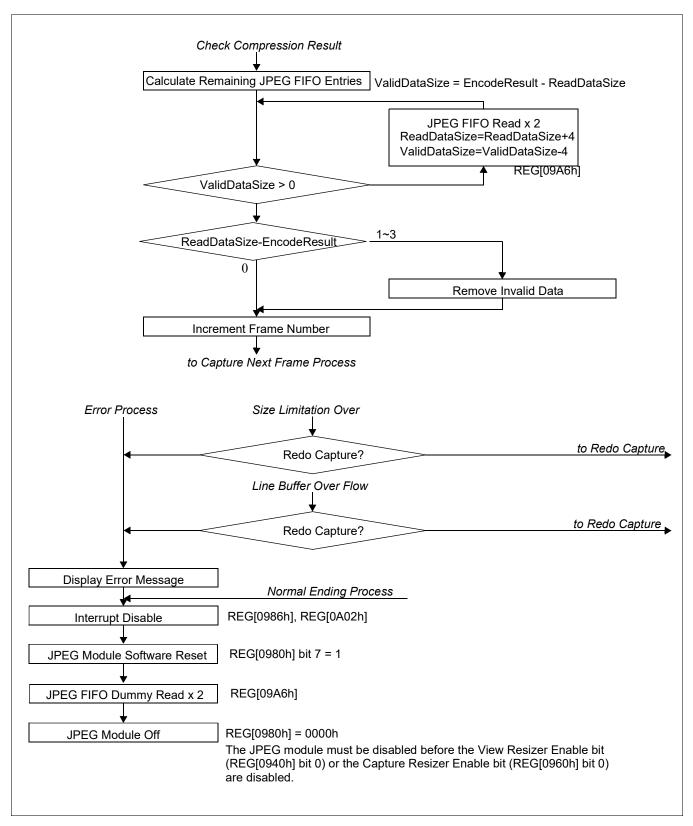

|    | 19.2.1 JPEG Encoding Process                      | .357  |

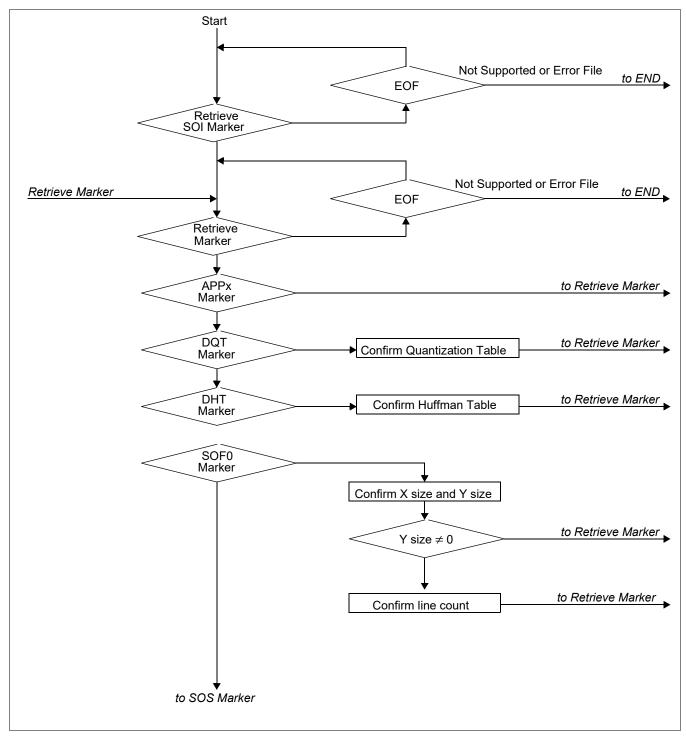

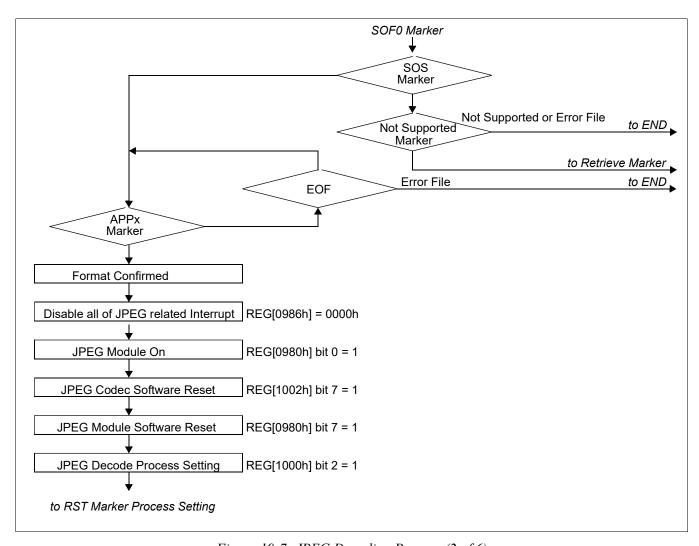

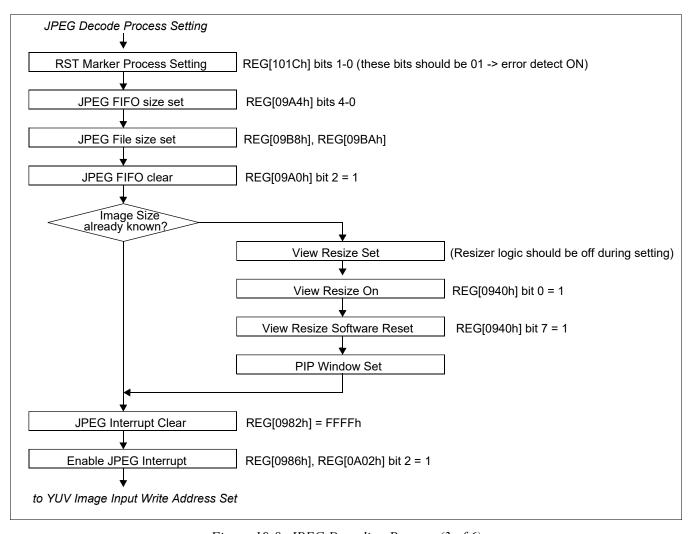

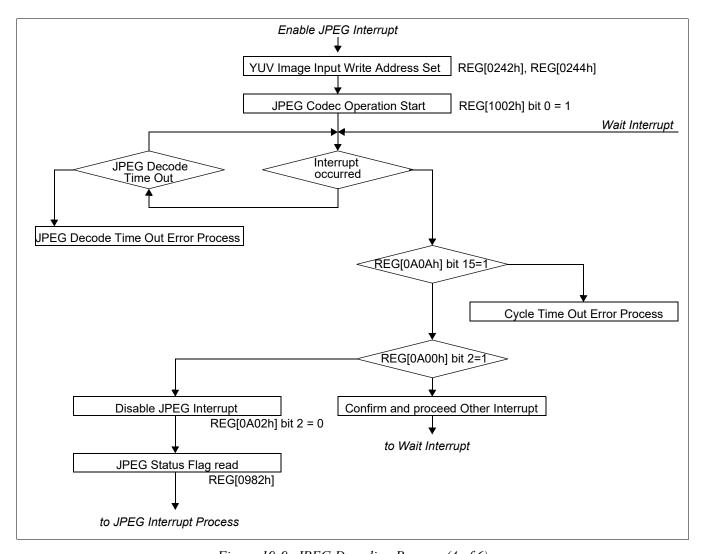

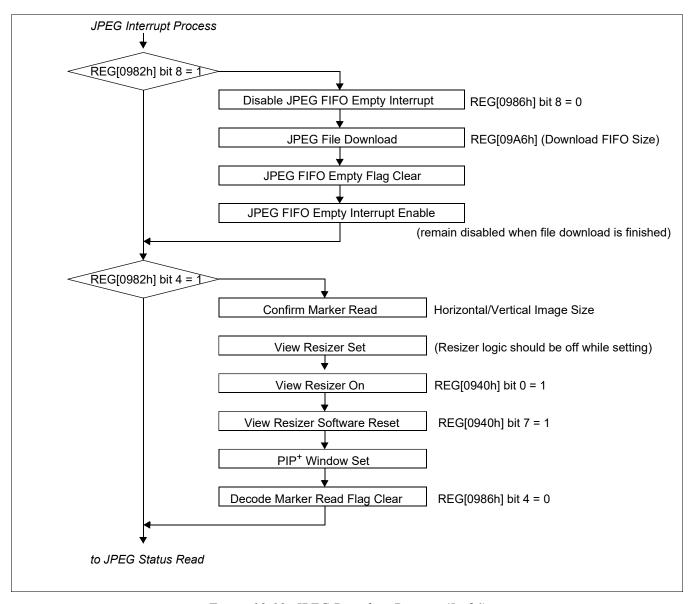

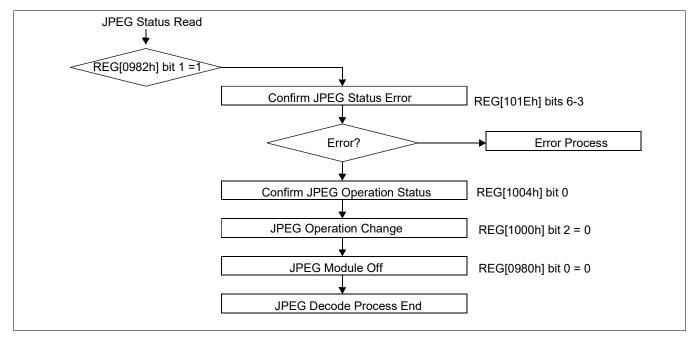

|    | 19.2.2 JPEG Decoding Process                      | .364  |

|    | 19.2.3 YUV Data Capture                           | .371  |

|    | 19.2.4 YUV Data Display                           | .372  |

|    | 19.2.5 Exit Sequence                              | .373  |

| 20 | Camera Interface                                  | . 374 |

|    | 20.1 Type 1 Camera                                | . 374 |

|    | 20.2 Strobe Control Signal                        | . 375 |

|    | 20.2.1 Generating a Strobe Pulse                  | .375  |

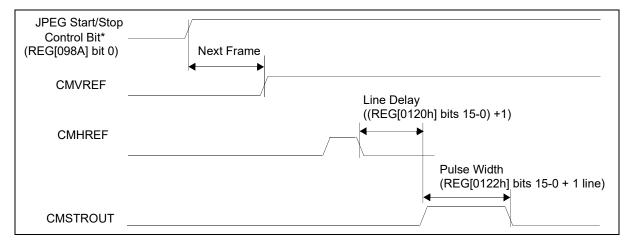

|    | 20.2.2 Strobe Timing                              | .376  |

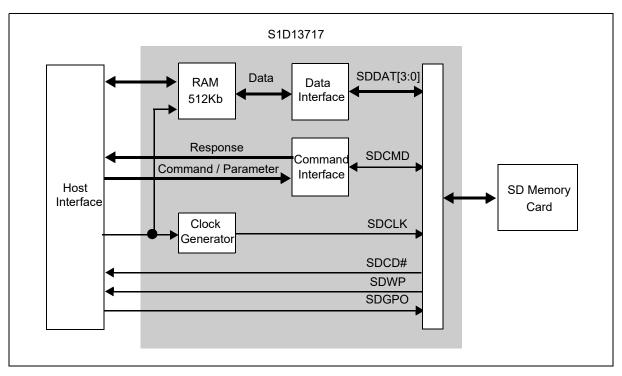

| 21 | SD Memory Card Interface                          | . 377 |

|    | 21.1 Interface Commands                           | . 378 |

|    | 21.2 Pin Functions                                | . 379 |

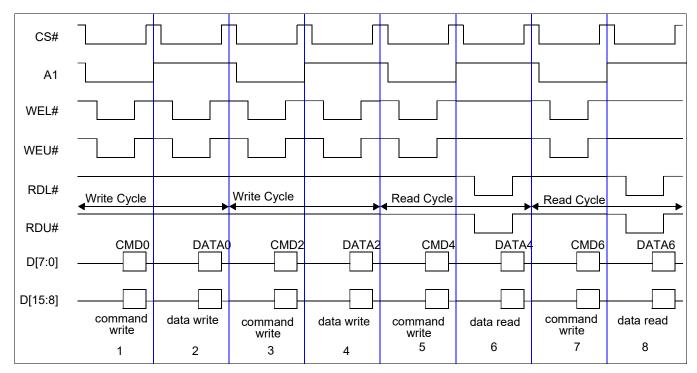

| 22 | Indirect Interface                                | . 380 |

|    | 22.1 Using the Indirect Interface                 |       |

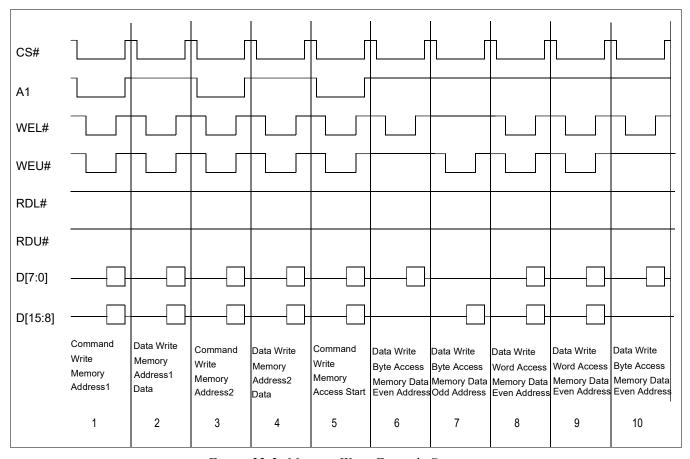

|    | 22.2 Example Sequences                            |       |

|    | 22.2.1 Register Read/Write Example Sequence       |       |

|    | 22.2.2 Memory Write Example Sequence              | .382  |

|    | 22.2.3 Memory Read Example Sequence | . 384 |

|----|-------------------------------------|-------|

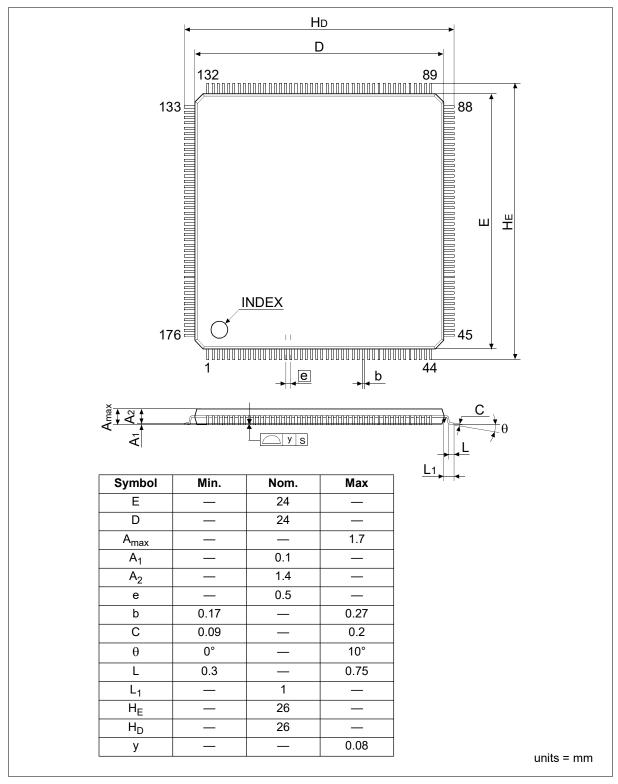

| 23 | Mechanical Data                     | . 387 |

| 24 | Change Record                       | . 388 |

| 25 | Sales and Technical Support         | . 398 |

#### 1 Introduction

#### 1.1 Scope

This is the Hardware Functional Specification for the S1D13717 Mobile Graphics Engine. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at vdc.epson.com.

We appreciate your comments on our documentation. Please contact us via email at vdc-documentation@ea.epson.com.

#### 1.2 General Description

The S1D13717 is an Mobile Graphics Engine solution designed with support for the digital video revolution in mobile products. The S1D13717 contains an integrated camera interface, hardware JPEG encoder/decoder and SD Memory Card interface. Seamlessly connecting to both direct and indirect CPU interfaces, it provides support for up to two LCD panels. The Mobile Graphics Engine supports all standard TFT panel types, eliminating the need for an external timing control IC. The S1D13717, with it's 224K bytes of embedded SRAM and rich feature set, provides a low cost, low power, single chip solution to meet the demands of embedded markets requiring Digital Video, such as Mobile Communications devices and Palm-size PDAs.

Additionally, products requiring a rotated display can take advantage of the SwivelView<sup>TM</sup> feature which provides hardware rotation of the display memory, transparent to the software application. The S1D13717 also provides support for "Picture-in-Picture Plus" (a variable size window with overlay functions). Higher performance is provided by the Hardware Acceleration Engine which provides 2D BitBLT functions.

The S1D13717 provides impressive support for cellular and other mobile solutions requiring Digital Video support. However, its impartiality to CPU type or operating system makes it an ideal display solution for a wide variety of applications.

#### 1.3 Internal Memory

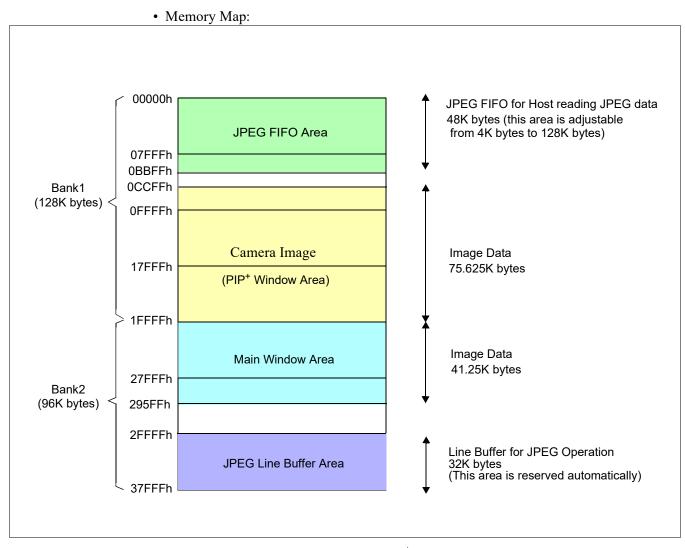

The S1D13717 contains 224K bytes of internal SRAM memory. This internal memory is divided into two physical SRAM banks that contain independent arbitration logic. The boundaries between the memory banks are transparent to the user. Memory Bank1 is 128K bytes and Bank2 is 96K bytes.

The internal memory can be used in 5 distinct ways:

- 1. **Main Window Display Only**: 224K bytes available. If the JPEG functions and the PIP<sup>+</sup> window are not required (therefore disabled), the entire 224K bytes of memory is available for main window image storage. In this case, the image written to the main display window can either come from the Host (RGB data) over the host interface, and/or input by the camera (YUV or RGB data) through the camera interface. The Main Window Display Start Address registers (REG[0212h]-[0214h]) determines where the main window image is stored in memory. Additionally, if the main window image is being updated by a camera, the YUV/RGB Converter Write Start Address registers (REG[0242h]-[0244h]) determines where the camera data is written and typically equals the address of the Main Window Display Start Address.

- 2. **Main Window and PIP**<sup>+</sup> **Window Display Only**: 224K bytes available. If the JPEG functions are not required (therefore disabled), the entire 224K bytes of memory is available for image storage and must be shared between the Main Window Display Image and the PIP<sup>+</sup> Window Display Image. It is recommended that the Main Window and the PIP<sup>+</sup> Window be located in different memory banks for improved performance. Since the PIP<sup>+</sup> Window is typically smaller than the Main Window, it is recommended that the PIP<sup>+</sup> Window Display Image be set to Bank2 using the PIP<sup>+</sup> Display Start Address registers (REG[0218h]-[021Ah]), and the Main Window Display Image be set to Bank1 using the Main Window Display Start Address registers (REG[0212h]-[0214h]). As in option 1, the image data for either of these windows can come from the Host or from the camera. Typically, in this setup the camera will input image data to the PIP+ Window and the YUV/RGB Converter Write Start Address registers (REG[0242h]-[0244h]) will equal the PIP<sup>+</sup> Display Start Address.

- 3. **JPEG Functions Enabled**: 192K bytes JPEG FIFO size available. If either the JPEG Encoder or Decoder is used, segments of Bank1 and Bank2 are automatically reserved for JPEG use only. The JPEG FIFO uses Bank1 and its size is configurable from 4K bytes to 128K bytes using the JPEG FIFO Size bits (REG[09A4h] bits 4-0). The JPEG FIFO starts at address 0 of Bank1 and is accessed using the JPEG FIFO Read/Write register (REG[09A6h]). The JPEG FIFO is used as an interface between the JPEG module and the HOST. When the S1D13717 is encoding a JPEG image, the JPEG FIFO stores JPEG data for the HOST to read. When the S1D13717 is decoding a JPEG file, the JPEG FIFO stores incoming JPEG data from the HOST. The size of the JPEG FIFO should be set to optimize performance based on the HOST operating speed, S1D13717 operating speed, and the size of the JPEG image. The JPEG Line Buffer uses the upper 32K bytes of Bank2, from 2FFFFh 37FFFh. During an encode operation, the JPEG Line Buffer is used to organize incoming YUV data from the

camera and send it to the JPEG Encoder. During a decode operation, the JPEG Line Buffer organizes the YUV data output of the JPEG decoder to be sent to the View Resizer and YUV/RGB Converter for display on the LCD panel.

- 4. YUV Data Output: 192K bytes JPEG FIFO size available. If YUV data from the camera is directly sent to the HOST, the JPEG Codec is bypassed, however the JPEG FIFO and JPEG Line Buffer are still utilized. The JPEG FIFO and JPEG Line Buffer are used as described for the decode operation in option 3 (JPEG Functions Enabled).

- 5. YUV Data Input: 192K bytes available. If YUV data from the Host is sent directly to the S1D13717, the JPEG Codec and JPEG FIFO are bypassed. YUV data is written directly to the JPEG Line Buffer. In this mode, the JPEG Line Buffer is accessed using the JPEG Line Buffer Write Port register (REG[09E0h]). The JPEG Line Buffer then sends the YUV data to the View Resizer and the YUV/RGB Converter for display on the LCD panel.

All data stored in the internal memory that is intended for display on the LCD panel, must be stored in RGB format. YUV data from the camera interface or from the HOST must be converted to RGB by the YUV/RGB Converter. Color depth data formats of 8/16/32 bit-per-pixel are supported.

#### 1.4 Host CPU Interface

The S1D13717 supports four CPU Host interfaces with 16-bit wide data buses. Each interface can support little or big endian data formats, direct or indirect addressing, and the option to use a wait signal or not. See Section 5.3, "Summary of Configuration Options" on page 41 for a description on how to configure the S1D13717 for these various options. In addition to these four CPU Host interfaces, the S1D13717 also has a serial CPU port which allows the CPU Host to directly control a serial LCD panel connected to the S1D13717.

The Host CPU that is connected to the S1D13717 must meet all specified timing parameters for the Host interface being used, as shown in Section 7.3, "Host Interface Timing" on page 55.

It is recommended that the WAIT# signal be used for all host interfaces as this will ensure that the highest performance is achieved when accessing the S1D13717. When this mode is selected, the WAIT# signal is only asserted when needed (i.e. the S1D13717 cannot accept or present data immediately). If the WAIT# signal is not used, the CPU must guarantee that all cycles meet the maximum cycle length as shown in Table 7-46: "Wait Length," on page 87.

#### 1.4.1 Direct Addressing Host Interfaces

The direct addressing host interfaces (Direct 80 Type 1, Direct 80 Type 2, Direct 80 Type 3, and Direct 68) are generic asynchronous CPU interfaces that provide addressing along with the data in one transfer. These interfaces only differ in the signals used to interpret the read/write and byte enable command signals. Typically, these interfaces are used to connect to the external memory bus of the host CPU and offer the highest performance when accessing the S1D13717.

The direct addressing host interfaces also have the ability to combine the S1D13717 registers and internal memory into one contiguous memory segment or into separate memory segments. In the contiguous mode (1 CS# mode), only one chip select is used to select the S1D13717 on the host bus. Memory and register accesses are differentiated by the M/R# pin which is typically connected to address pin A19 of the host CPU bus. In the separate memory mode (2 CS# mode), two chip selects select the S1D13717. One chip select is used for memory accesses and the other is used for register accesses. In this mode, the host CPU can be programmed to assign different memory spaces for the memory and registers of the S1D13717.

#### 1.4.2 Indirect Addressing Host Interfaces

The indirect addressing host interfaces (Indirect 80 Type 1, Indirect 80 Type 2, Indirect 80 Type 3, and Indirect 68) are generic asynchronous CPU interfaces that provide addressing and data in two separate transfers. These interfaces only differ in the signals used to interpret the read/write and byte enable command signals. Typically, these interfaces are used when the address and data lines of the host CPU are multiplexed together and two transfers are needed to complete a data transfer.

#### 1.4.3 Serial Port Interface for Serial LCD Control

The S1D13717 also supports a Serial Host Interface that is used to directly control a serial LCD panel connected to the S1D13717. This bypass mode is controlled by the Serial Port Bypass Enable bit (REG[0032h] bit 8). Typically, this interface is used when the S1D13717 is in power save mode and a serial LCD panel is required to show an image such as a status display.

#### 1.5 LCD Controller

The S1D13717 Mobile Graphics Engine contains a versatile LCD controller which supports many LCD panel types and offers a rich feature set. The S1D13717 has four LCD interface modes where either one or two LCD panels (referred to as LCD1 and LCD2) can be connected to the S1D13717. These modes are selected using the Panel Interface bits (REG[0032h] bits 1-0). LCD1 and LCD2 each have their own vertical and horizontal LCD panel size setting and other specific features, in order to easily switch from the LCD1 panel display to the LCD2 panel display or vice versa.

In Mode 1, LCD1 is defined as a TFT RGB type LCD panel. LCD2 is defined as a serial interface type LCD panel with integrated RAM to store the image data.

In Mode 2, LCD1 is defined as a parallel interface LCD panel with integrated RAM to store the image data. LCD2 is defined as a serial interface type LCD panel with integrated RAM to store the image data.

In Mode 3, LCD1 and LCD2 are both defined as parallel interface LCD panels with integrated RAM to store the image data.

In Mode 4, LCD1 is defined as a TFT RGB type LCD panel. LCD2 is defined as a parallel interface LCD panel with integrated RAM to store the image data.

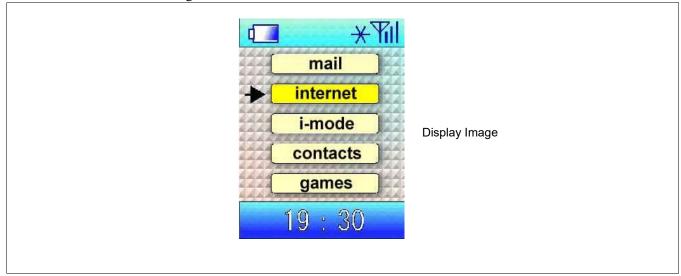

In each mode, only one display at a time (LCD1 or LCD2) can be the active display. A typical application for using two separate LCD panels would be a clamshell type cellular phone where there is a main display and a smaller status display on the outside of the phone. LCD1 would be the main display and LCD2 would be the small status display, typically a serial interface LCD panel. Two images would be stored in the internal memory of the S1D13717 for each LCD display. When each display is selected as active, (LCD1 when the cellular phone is open and LCD2 when the cellular phone is closed) the correct image to be displayed is selected using the Main Window Display Start Address registers (REG[0210h]-[0212h]).

For LCD Interface Pin Mapping refer to Table 5-12: "LCD Interface Pin Mapping," on page 45.

#### 1.5.1 RGB LCD Interface

The RGB LCD interface supports a wide range of generic TFT panels. TFT panels that can be programmed via various serial type interface are supported and are selected with the LCD1 Serial Data Type bits (REG[0054h] bits 7-5).

The RGB LCD panel data bus width is selectable to support 9/12/16/18-bit panels using the RGB Interface Panel Data Bus Width bits (REG[0032h] bits 6-4). Other configurable options include non-display period times and polarity, width, and position of control signals.

#### 1.5.2 Parallel LCD Interface

The Parallel LCD Interface supports multiple output data formats, providing the flexibility to support various RAM integrated Parallel Interface LCD panels. If a parallel panel is connected to LCD1, the LCD1 Parallel Data Format bits (REG[0056h] bits 2-0) are used to program the output data format, otherwise the LCD2 Parallel Data Format bits (REG[005Eh] bits 2-0) are used.

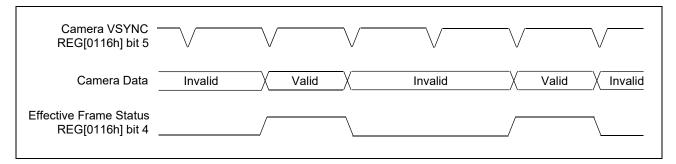

The LCD panel image can be updated in three different ways. Manual Transfer is accomplished by setting REG[003Ah] bit 1 = 1 which sends one frame of panel data to the Parallel LCD panel. LCD Module VSYNC Manual Transfer mode synchronizes a manual frame transfer to an external VSYNC signal sent by the parallel LCD panel. The VSYNC Input Enable bit for either LCD1 or LCD2 (REG[0056h] bit 7 or REG[005Eh] bit 7) must be set to enable this mode. The last transfer method is Automatic Transfer which sends frames to the LCD panel whenever a camera vertical sync signal is detected. If the VYSNC Input mode is also enabled, an external LCD panel VSYNC must also be detected. Automatic Transfer mode is enabled by setting REG[003Ch] bit 1 = 1. Automatic Transfer mode is intended for displaying a camera image on a serial or parallel interface LCD panel without the need to manually update the panel display.

#### 1.5.3 Serial LCD Interface

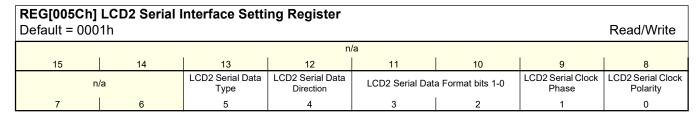

The Serial LCD Interface supports serial type LCD panels only on LCD2. Serial Data Type, Data Direction, Data Format, and Serial Clock Phase and Polarity are all selectable and are controlled in the LCD2 Serial Interface Setting register (REG[005Ch]). Serial Interface Panels are updated with image data as described in Section 1.5.2, "Parallel LCD Interface" on page 16.

#### 1.6 Display Features

The S1D13717 contains display features that enhance the functionality of the Mobile Graphics Engine. These features are Picture-in-Picture Plus (PIP<sup>+</sup>), Overlay, SwivelView, Mirror, and Pixel Doubling.

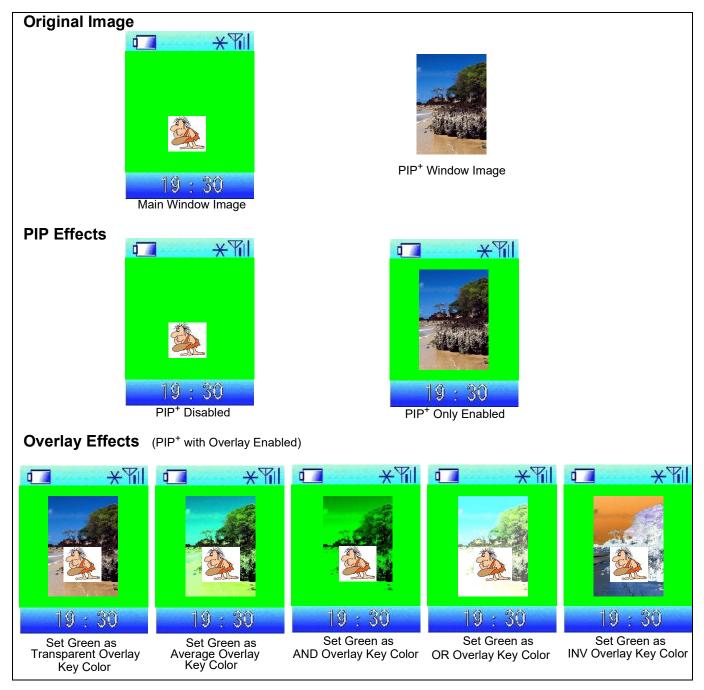

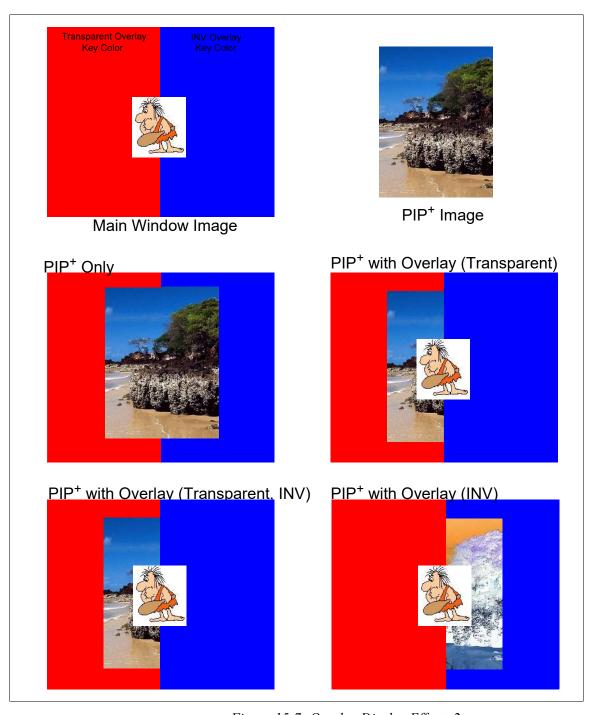

PIP<sup>+</sup> is a sub-window within the Main Window and typically is used to display the camera image or a decoded JPEG image. PIP<sup>+</sup> can be used with the overlay functions so that only the part of the PIP<sup>+</sup> window that overlaps the overlay color in the Main Window is displayed (according to the overlay function selected). Various overlay functions can be employed such as transparency, averaging, ANDing, ORing, and Inverting. Multiple overlay functions can be enabled, but only the overlay function with the highest priority is processed.

SwivelView is a hardware rotation of the display image by either 90, 180, or 270 degrees. By processing the rotation of the image in hardware, SwivelView offers a performance advantage over software rotation. SwivelView can be used to support portrait sized panels mounted in a landscape orientation or vice versa.

Mirror can be used to mirror the image in either the PIP<sup>+</sup> window display, Main Window display, or both. A typical application for mirroring is to support swivelling on a clamshell phone. When the large display is on the outside of the phone and the camera is pointing at the user, mirroring allows the camera image to be displayed properly.

Pixel Doubling is a feature that can be used to double the size of an image in either the PIP<sup>+</sup> window display, Main Window display or both. Typical applications for pixel doubling include increasing the displayed size of a decoded JPEG image or using a larger panel size than is supported natively by an operating system. For example, if a 320x320 resolution panel is used with an OS that supports only a main display of 160x160 (such as in many PDAs), pixel doubling can be enabled to utilize the whole display.

#### 1.7 Camera Interface

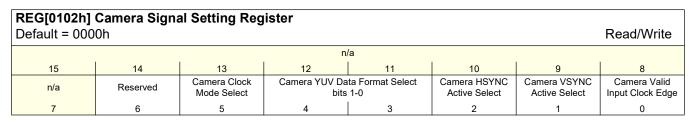

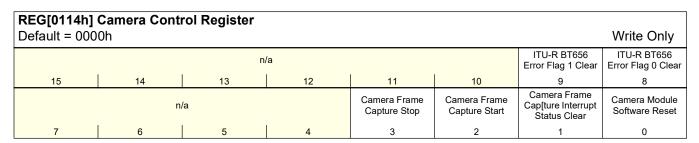

The S1D13717 supports an 8-bit parallel Camera Interface. The input data format supported is YUV 4:2:2. Embedded sync signals, as defined by the ITU-R BT656 standard, are also supported. A clock is supplied to the camera from the camera interface (CMCLKOUT) and the camera in turn outputs YUV data, horizontal and vertical sync signals, and a pixel clock that the S1D13717 camera interface uses to sample the incoming YUV data. The CMCLKOUT frequencies are controlled by the Camera Clock Divide Select bits (REG[0100h] bits 3-0). The camera interface supports various types of YUV cameras by allowing the selection of different formats of YUV 4:2:2 signals. Features such as YUV Data Format, YUV Data Range, HSYNC and VSYNC polarity, and Camera Pixel Clock Input Polarity are all selectable.

Since the Camera Pixel Clock can be, at most, 1/3 the S1D13715 System Clock, the frames per second of the camera image displayed on the LCD display is dependant on the internal speed of the S1D13717. For example, a setting of 54MHz for the System Clock results in the camera returning a Pixel Clock of 6.5MHz when the S1D13717 Camera Clock Out Divide is set to a divide of 4 (typical cameras use a divide by 2 of the input clock to generate the pixel clock). For CIF resolutions (352x288), this translates into 29 fps. For a Camera Clock Out Divide of 2 and VGA resolutions (640x480), 21 fps is achieved.

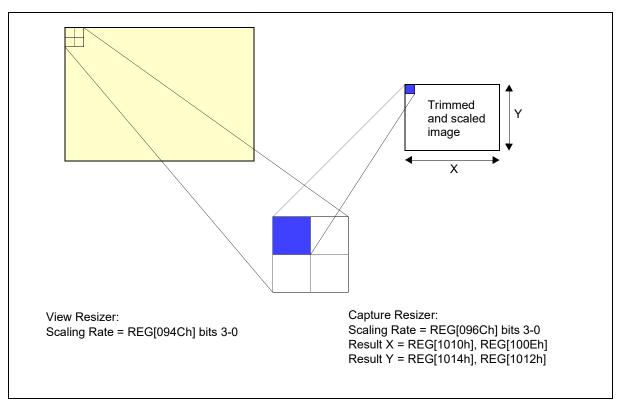

#### 1.8 Resizers and YUV/RGB Converter

There are two resizers in the S1D13717: the view resizer and the capture resizer. Both resizers can be used to resize (crop) and/or scale incoming YUV data from the camera interface, from the JPEG Decoder, or from the Host CPU in YUV bypass mode. Once the YUV data has been resized and scaled, it gets converted to RGB data by the YUV/RGB Converter (YRC), so that it can be displayed on the LCD panel. The location in memory where the YRC writes the RGB data is defined by the YUV/RGB Converter Write Start Address registers (REG[0242h]-[0244h]). The output bpp of the YRC must match either the Main Window color depth (bpp) or the PIP<sup>+</sup> Window color depth (bpp) setting, depending on which window the image is being displayed in. The YRC color depth (bpp) output is controlled by the YRC Output Bpp Select bits (REG[0240h] bits 11-10). The resizers can support a maximum image size up to 2048 x 2048 pixels.

Although each resizer can be configured to be the source for the YRC using the Output Source Select bit (REG[0940h] bit 3), typically the view resizer is set as the source since only the capture resizer can be the source for the JPEG Encoder or for YUV bypass mode to the Host CPU. A typical application has the view resizer resizing the camera data and has the YRC converting it for display on the LCD panel, while the capture resizer is used to send camera YUV data for JPEG encoding or for raw storage by the Host CPU. When the desired viewed camera image is the same dimensions as the desired captured JPEG or YUV image, only the capture resizer needs to be used.

#### Note

Only the view resizer can be used to resize YUV data from the JPEG Decoder or from the Host CPU.

#### 1.9 JPEG Encoder / Decoder

The S1D13717 contains a full JPEG Codec capable of encoding an incoming camera data stream or decoding a JPEG image sent from the Host CPU.

#### 1.9.1 Encoder

Either the YUV data stream from the camera interface or the display buffer memory via the RGB to YUV Converter or YUV data from the host can be encoded into a JPEG image. The YUV data from the capture resizer is organized into 8 x 8 blocks in the JPEG Line Buffer, as required for JPEG processing, and then sent to the JPEG Encoder. As the JPEG Encoder is encoding the YUV data, it starts filling up the JPEG FIFO with JPEG data. This data must be read by the Host CPU before the JPEG FIFO overflows. Status flags and interrupts can be used to determine how full the JPEG FIFO is becoming. The JPEG FIFO is accessed through the JPEG FIFO Read/Write register (REG[09A6h]). The JPEG FIFO can be set as large as 128K bytes and typically this will be large enough to contain the whole JPEG image. A smaller JPEG file size can be achieved using the capture resizer's trimming and scaling functions or a higher JPEG compression ratio can be achieved by using different Quantization and Huffman Tables.

As mentioned in Section 1.3, "Internal Memory" on page 12, when the JPEG functions are enabled, 32K bytes of the internal memory is used for the JPEG Line Buffer and from 4K bytes to 64K bytes is used for the JPEG FIFO. The JPEG Encoder can encode YUV 4:2:2, YUV 4:2:0, and YUV 4:1:1 data formats and will convert the incoming YUV data to the desired format. This encoding option is set by the YUV Format Select bits (REG[1000h] bits 1-0). The JPEG file size can be reduced if a smaller UV:Y ratio format is used.

The intended use of the JPEG Encoder is to "take a snapshot" of the currently viewed camera image or display image, or to encode YUV data sent by the Host CPU. This JPEG image is then downloaded to the Host CPU through the JPEG FIFO and stored as a JPEG file.

#### 1.9.2 Decoder

The S1D13717 contains a JPEG Decoder which allows the Host CPU to send a JPEG image file for conversion and display on the LCD panel, or to send the resulting YUV decoded data back to the Host CPU. The incoming JPEG data is written to the JPEP FIFO and then goes to the JPEG Decoder for decoding into YUV format. The YUV format output is based on the original format the JPEG file was encoded from and is reported in the YUV Format Select bits (REG[1000h] bits 1-0). The output of the JPEG Decoder goes to the JPEG Line Buffer which then organizes the 8 x 8 blocks of YUV data into the correct YUV format and sends this data to the view resizer. The view resizer can trim and scale the image and then it is converted by the YRC to be displayed on the LCD panel or sent to the Host CPU.

While writing the JPEG data to the JPEG FIFO, the Host CPU may be interrupted. When this happens, the JPEG Decoder completes decoding the data stored in the JPEG FIFO and the waits for more data from the Host CPU. The decode operation will continue until the JPEG Decoder detects the End-of-File Marker. The JPEG FIFO must not be overflowed by the Host CPU. Status flags and interrupts can be used to determine how full the JPEG FIFO is becoming. The JPEG FIFO is accessed through the JPEG FIFO Read/Write register (REG[09A6h]).

As mentioned in Section 1.3, "Internal Memory" on page 12, when the JPEG functions are enabled, 32K bytes of the internal memory is used for the JPEG Line Buffer and from 4K bytes to 64K bytes is used for the JPEG FIFO. The JPEG Decoder can decode YUV 4:4:4, YUV 4:2:2, YUV 4:2:0, and YUV 4:1:1 data formats.

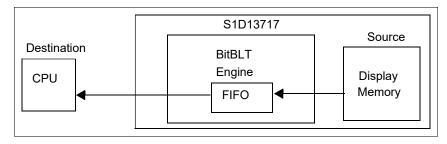

#### 1.10 2D BitBLT Engine

The purpose of the 2D BitBLT Engine is to improve the overall system performance by off-loading the work of the Host CPU in moving display data between the CPU and display memory. There are five BitBLTs (Bit Block Load Transfer) that can move display data from one location to another. Additionally, data functions can be performed that manipulate the source and/or destination data. For more information on the 2D BitBLT Engine, see Section 16, "2D BitBLT Engine" on page 328.

#### 2 Features

#### 2.1 Internal Memory

- Embedded 224K byte SRAM memory used for:

- Display Buffer

- JPEG FIFO

- JPEG Line Buffer

#### 2.2 Host CPU Interface

- Four generic asynchronous CPU interfaces

- 16-bit data bus

- 16-bit register and FIFO access

- 8/16-bit display buffer access

- Direct / Indirect addressing

- Little / Big endian support

- · Registers are memory-mapped

- M/R# input selects between memory and register address space

- M/R# and CS# inputs select between memory and register address space in 2 CS# mode

- CPU serial port for direct control of a serial LCD

- CPU parallel port for direct control of a parallel LCD

#### 2.3 Display Support

- Active Matrix TFT displays: 9/12/18-bit interface

- TFT with u-Wire interface

- · a-Si TFT interface

- Epson ND-TFD interface

- 8/9-bit serial interface LCDs with integrated RAM

- 8/16/18-bit MPU parallel interface LCDs with integrated RAM

- Supports a maximum of 2 panels (LCD1 and LCD2 can't be refreshed simultaneously)

#### 2.4 Display Modes

- Supports three panel interface modes which each allow two LCDs (LCD1 and LCD2) to be connected to the S1D13717. Only one LCD can be active at a time.

- Mode 1:

- LCD1: RGB type panel

- LCD2: Serial interface panel

- Mode 2:

- LCD1: Parallel interface panel

- LCD2: Serial interface panel

- Mode 3:

- LCD1: Parallel interface panel

- LCD2: Parallel interface panel

- Mode 4:

- LCD1: RGB type panel

- LCD2: Parallel interface panel

- Host CPU can directly control serial interface panels on LCD2

- Host CPU can directly control parallel interface panels on LCD1 or LCD2

- 8/16/32 bit-per-pixel (bpp) color depths

- Separate Look-up Tables (LUTs) for the Main Window and the PIP<sup>+</sup> Window

- LUTs can be bypassed

#### 2.5 Display Features

- · Overlay functions

- SwivelView<sup>TM</sup>: 90°, 180°, 270° counter-clockwise hardware rotation of display image

- Mirror Display: provides a "mirror" image of the display

- Virtual display support: displays images larger than the panel size through the use of panning and scrolling

- Picture-in-Picture Plus (PIP<sup>+</sup>): displays a variable size window overlaid over background image

- Pixel Doubling

- Video Invert: Data output to the LCD is inverted

#### 2.6 Camera Interface

- 8-bit Camera Interface (YUV Multi Out)

- Supports YUV 4:2:2 format

- Supports ITU-R BT.656 format

- MPU type interface camera support on Camera interface

- Strobe control function

#### 2.7 Digital Video Features

- · Hardware JPEG codec based on the JPEG baseline standard

- JPEG Encode supports YUV 4:2:2, YUV 4:2:0, YUV4:1:1 formats

- JPEG Decode supports YUV 4:4:4, YUV 4:2:2, YUV 4:2:0, YUV4:1:1 formats

- Arithmetic accuracy satisfies the compatibility test of JPEG Part-2

- Software control of image size

- Maximum horizontal image size for JPEG encoding (YUV 4:2:2 format: up to 2880 pixels)

- Two resizers: View resizer receives YUV data from the camera interface, or from the JPEG decoder, or from the Host CPU. Capture resizer receives YUV data only from the camera interface.

- YUV Data can be resized (trimmed and scaled) then:

- Converted to RGB data for display on the LCD

- Converted to JPEG data and read by the CPU Host via the JPEG FIFO

- Read by the Host CPU directly (YUV format)

- YUV to RGB Converter (YRC): YUV data from the View Resizer or Capture Resizer is converted to RGB format to be displayed on the LCD.

#### 2.8 Picture Input / Output Functions

- The YUV data from Camera Interface can be:

- Stored in the display buffer after resizing and conversion to RGB format.

- Transferred to the Host CPU via the JPEG FIFO after resizing and encoding to JPEG format.

- Transferred to the Host CPU via the JPEG FIFO after resizing and conversion to YUV format (4:2:2, 4:2:0).

- The JPEG file downloaded from the Host CPU can be:

- Decoded by the internal JPEG decoder, resized, scaled, converted to RGB and stored in the display buffer memory for display on the LCD.

- Decoded by the internal JPEG decoder, resized, scaled, and downloaded to the Host CPU via the JPEG FIFO.

- YUV data (format 4:2:2 or 4:2:0) downloaded from the Host CPU can be:

- Resized, scaled, converted to RGB and stored in the display buffer memory for display on the LCD.

- Encoded by the internal JPEG encoder, resized, scaled, and downloaded to the Host CPU via the JPEG FIFO.

- RGB data in the display buffer can be:

- Converted to YUV, then transferred to the Host CPU via the JPEG FIFO after resizing and encoding to JPEG format.

#### 2.9 2D BitBLT Acceleration

• 2D BitBLT engine including: (this function does not support 32 bpp modes)

Move BitBLT Transparent Move BitBLT

Solid Fill BitBLT Read BitBLT

Pattern Fill BitBLT Move BitBLT with Color Expansion

#### 2.10 SD Memory Card Interface

- SD Memory Card interface compatible with the SD Memory Card Physical Layer version 1.0 specification

- 4-bit or 1-bit interface (SPI mode is not supported)

- No security functions

- Card Detect and Write Protect inputs

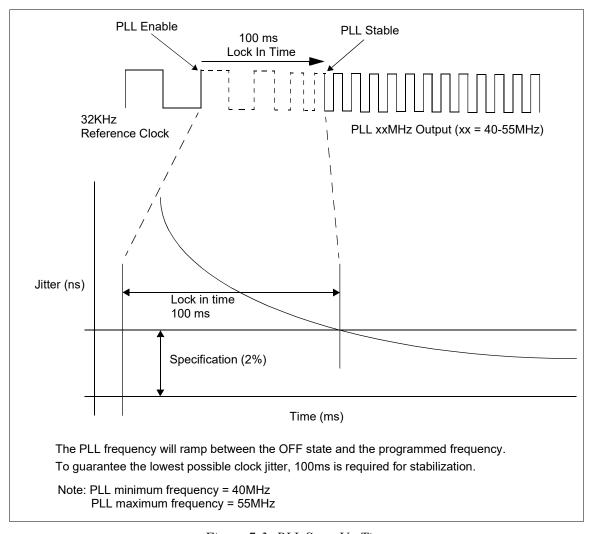

#### **2.11 Clock**

- Internal PLL driven by a single external reference clock, 32.768KHz

- 40 55MHz PLL output

- PLL bypass mode for external clock input

#### 2.12 Power Save

- Software initiated power save mode

- Software initiated display blank

#### 2.13 Miscellaneous

- General Purpose Input/Output pins are available

- S1D13717F00A QFP21-176-pin package

# 3 System Diagrams

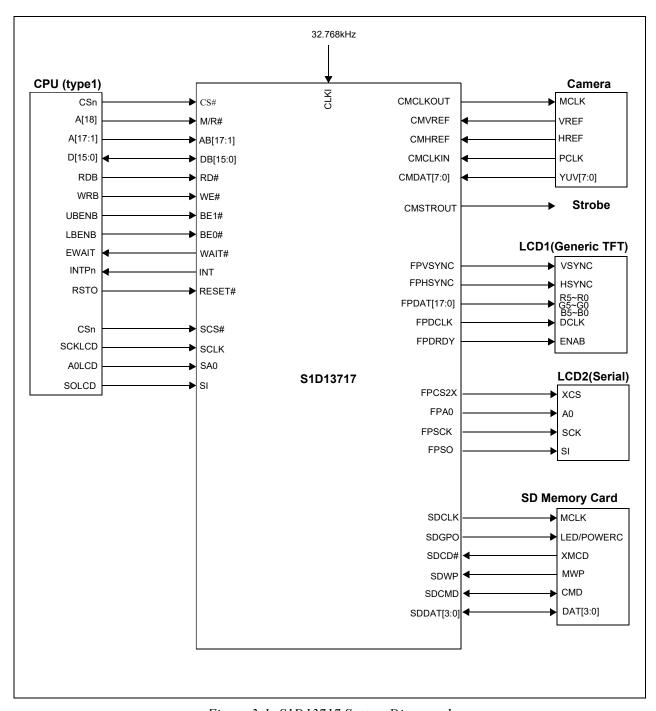

Figure 3-1: S1D13717 System Diagram 1

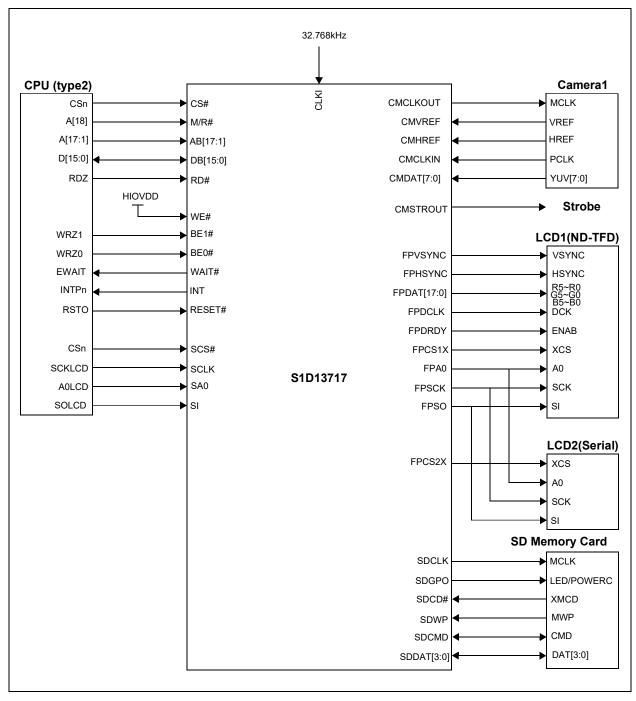

Figure 3-2: S1D13717 System Diagram 2

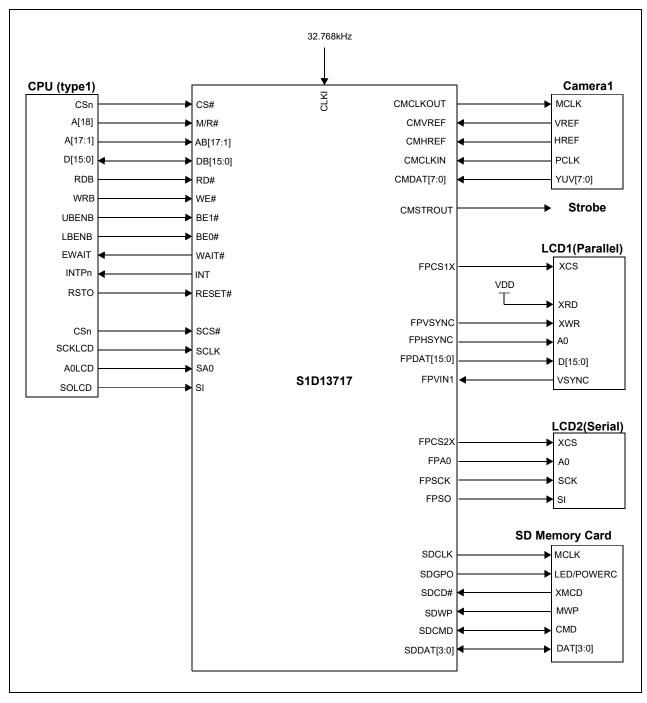

Figure 3-3: S1D13717 System Diagram 3

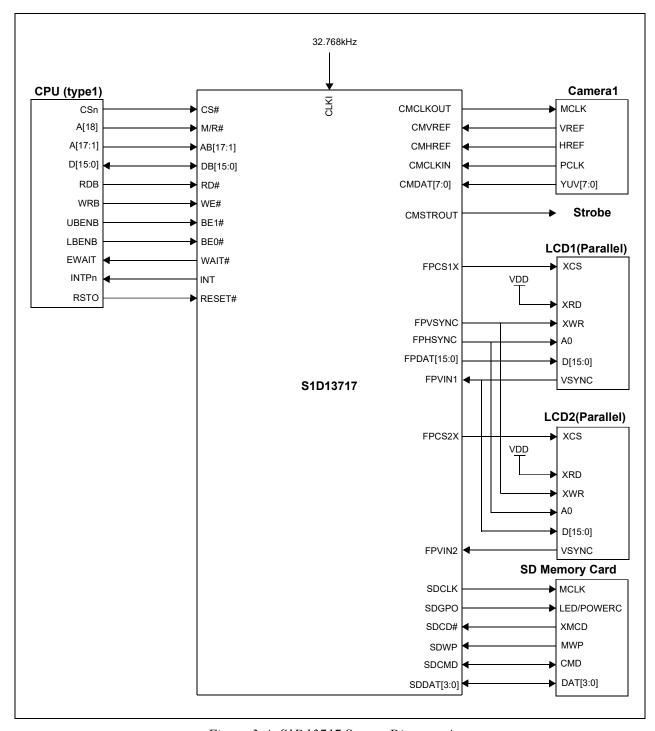

Figure 3-4: S1D13717 System Diagram 4

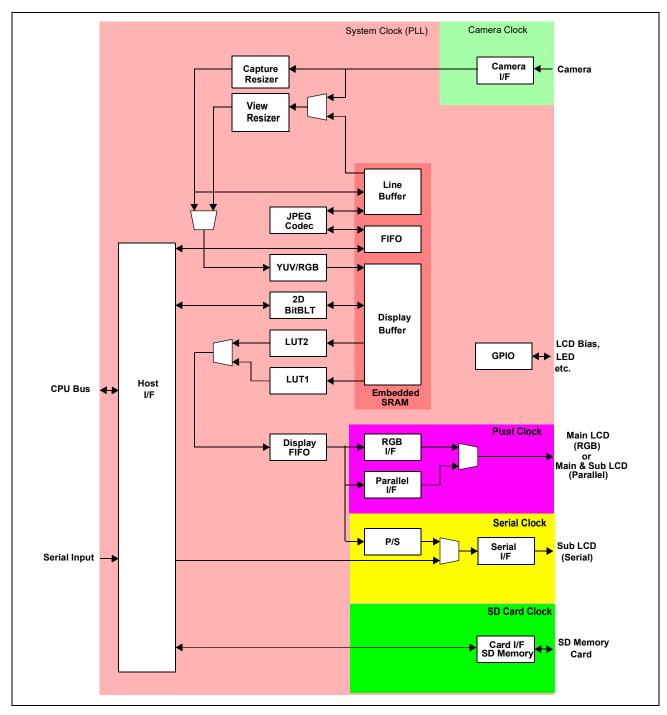

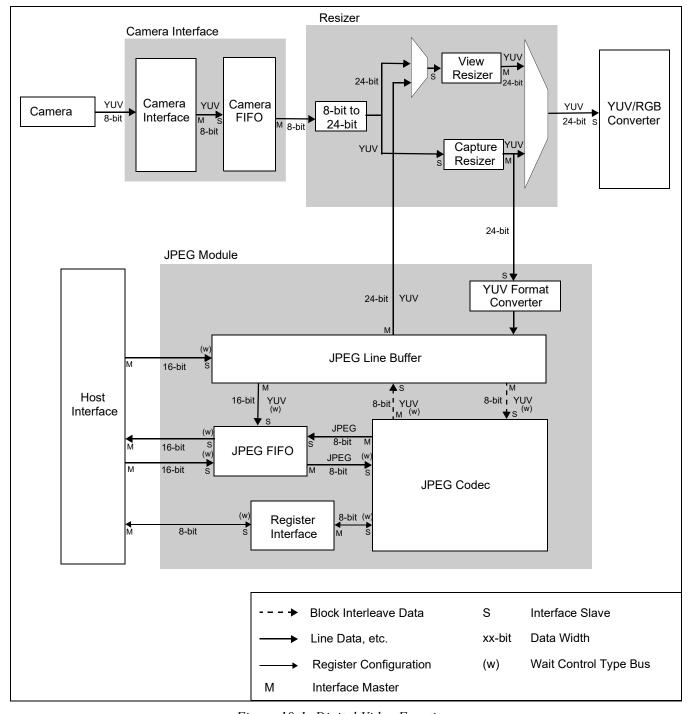

# 4 Block Diagram

Figure 4-1: S1D13717 Block Diagram

#### 5 Pins

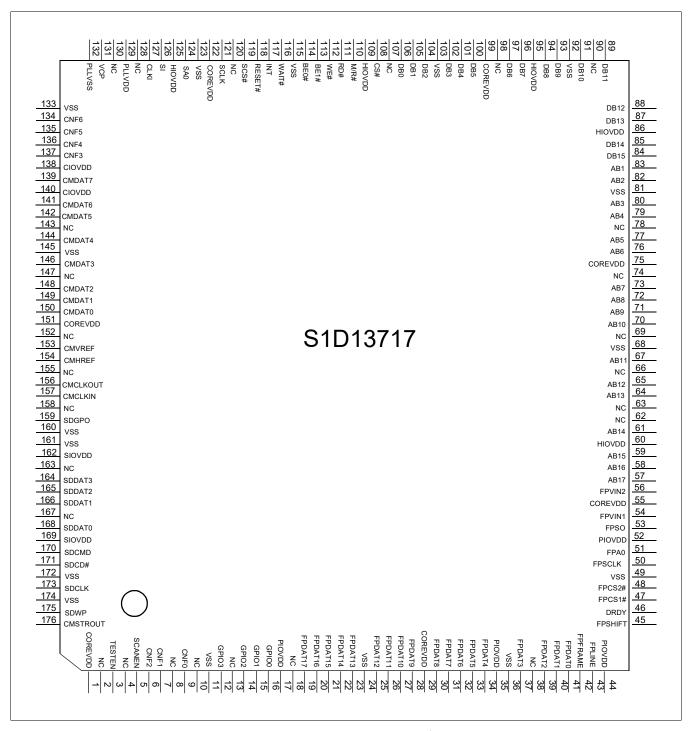

#### 5.1 S1D13717 Pinout Diagram (QFP21-176)

Figure 5-1: S1D13717 QFP21 176-Pin Package - Top View

#### 5.2 Pin Descriptions

#### Key:

Τ Input 0 = Output Ю Bi-Directional (Input/Output) Р Power pin High Impedance Ζ L Low level output High level output Н 0 Pull-down control on input Pull-up control on input

Table 5-1: Cell Descriptions

| Item     | Description                                                                                         |  |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| IC       | LVCMOS <sup>1</sup> input                                                                           |  |  |  |  |  |  |

| ICU      | LVCMOS input with pull-up resistor (60KΩ@3.0V)                                                      |  |  |  |  |  |  |

| ICD      | LVCMOS input with pull-down resistor (60KΩ@3.0V)                                                    |  |  |  |  |  |  |

| IHCS     | H System LVCMOS level Schmitt input                                                                 |  |  |  |  |  |  |

| ILCS     | L System LVCMOS level Schmitt input                                                                 |  |  |  |  |  |  |

| OLN35    | Low noise output buffer (3.5mA/-3.5mA@3.0V)                                                         |  |  |  |  |  |  |

| OLN35T   | Low noise Tri-state output buffer (3.5mA/-3.5mA@3.0V)                                               |  |  |  |  |  |  |

| BLNC35   | Low noise LVCMOS IO buffer (3.5mA/-3.5mA@3.0V)                                                      |  |  |  |  |  |  |

| BLNC35D  | Low noise LVCMOS IO buffer (3.5mA/-3.5mA@3.0V) with pull-down resistor (60K $\Omega$ @3.0V)         |  |  |  |  |  |  |

| BLNC35DS | Low noise LVCMOS Schmitt IO buffer (3.5mA/-3.5mA@3.0V) with pull-down resistor (60K $\Omega$ @3.0V) |  |  |  |  |  |  |

| ITD      | Test mode control input with pull-down resistor (60KΩ@3.0V)                                         |  |  |  |  |  |  |

| ILTR     | Low Voltage Transparent Input                                                                       |  |  |  |  |  |  |

| IHTR     | High Voltage Transparent Input                                                                      |  |  |  |  |  |  |

| OHTR     | High Voltage Transparent Output                                                                     |  |  |  |  |  |  |

1. LVCMOS is Low Voltage CMOS (see Section 6, "D.C. Characteristics" on page 48).

#### 5.2.1 Unused Pins

All unused input pins should be connected to their inactive state if an internal pull-down resistor is not present.

All unused output pins should be left unconnected.

All unused bi-directional pins should be connected to a  $100 \mathrm{K}\Omega$  pull-down/up resistor if an internal pull-down resistor is not present.

#### 5.2.2 Host Interface

Many of the host interface pins have different functions depending on the selection of the host bus interface (see configuration of CNF[4:2] pins in Table 5-9: "Summary of Power-On/Reset Options," on page 41). For a summary of host interface pins, see Table 5-10: "Host Interface Pin Mapping (1 CS# mode)," on page 43 and Table 5-11: "Host Interface Pin Mapping (2 CS# mode)," on page 44.

Table 5-2: Host Interface Pin Descriptions

| Pin Name | Туре | QFP21<br>Pin#                                                                 | Cell   | Power  | RESET#<br>State                                                                                                                                                                                                                                | Description                                                                                                      |

|----------|------|-------------------------------------------------------------------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| AB[17:2] | I    | 57,58,59,<br>61,64,65,<br>67,70,71,<br>72,73,76,<br>77,79,80,<br>82           | IC     | HIOVDD | Z                                                                                                                                                                                                                                              | System address bits 17:2.  • For Indirect Host Bus Interfaces, these pins must be connected to V <sub>SS</sub> . |

|          |      |                                                                               |        |        |                                                                                                                                                                                                                                                | System address bit 1.                                                                                            |

| AB1      | I    | 83                                                                            | IC     | HIOVDD | Z                                                                                                                                                                                                                                              | <ul> <li>For Indirect Host Bus Interfaces, this pin is the<br/>command/data signal.</li> </ul>                   |

| DB[15:0] | Ю    | 84,85,87,<br>88,89,91,<br>93,94,96,<br>97,100,<br>101,102,<br>104,105,<br>106 | BLNC35 | HIOVDD | Z                                                                                                                                                                                                                                              | System data bus.                                                                                                 |

|          | I    | l 108                                                                         | IC     | HIOVDD | Z                                                                                                                                                                                                                                              | This input pin has multiple functions.                                                                           |

| CS#      |      |                                                                               |        |        |                                                                                                                                                                                                                                                | <ul> <li>For 1 CS# mode, this pin inputs the chip select<br/>signal (CS#).</li> </ul>                            |

|          |      |                                                                               |        |        |                                                                                                                                                                                                                                                | <ul> <li>For 2 CS# mode, this pin inputs the memory<br/>chip select signal (CSM#).</li> </ul>                    |

|          |      |                                                                               |        |        |                                                                                                                                                                                                                                                | This input pin has multiple functions.                                                                           |

| M/R#     | ı    | I 110 IC I                                                                    | HIOVDD | Z      | <ul> <li>For 1 CS# mode, this pin selects between the<br/>display buffer and register address spaces.</li> <li>When M/R# is set high, the display buffer is<br/>accessed and when M/R# is set low the regis-<br/>ters are accessed.</li> </ul> |                                                                                                                  |

|          |      |                                                                               |        |        |                                                                                                                                                                                                                                                | <ul> <li>For 2 CS# mode, this pin inputs the register<br/>chip select (CSR#).</li> </ul>                         |

|          |      |                                                                               |        |        |                                                                                                                                                                                                                                                | <ul> <li>For Indirect Host Bus Interfaces, this pin must<br/>be connected to V<sub>SS</sub>.</li> </ul>          |

Table 5-2: Host Interface Pin Descriptions (Continued)

| Pin Name | Туре | QFP21<br>Pin# | Cell   | Power  | RESET#<br>State | Description                                                                                                                                                                                                                                                                                      |

|----------|------|---------------|--------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |               |        |        |                 | This input pin has multiple functions.                                                                                                                                                                                                                                                           |

|          |      |               |        |        |                 | <ul> <li>For Indirect and Direct 68, this pin must be<br/>connected to HIOV<sub>DD</sub>.</li> </ul>                                                                                                                                                                                             |

| RD#      | I    | 111           | IC     | HIOVDD | Z               | <ul> <li>For Indirect and Direct 80 Type 1 and Type 2,<br/>this pin is the read enable signal (RD#).</li> </ul>                                                                                                                                                                                  |

|          |      |               |        |        |                 | For Indirect and Direct 80 Type 3, this pin is the DB[7:0] lower byte read enable signal (RDL#).                                                                                                                                                                                                 |

|          |      |               |        |        |                 | This input pin has multiple functions.                                                                                                                                                                                                                                                           |

|          |      |               |        |        |                 | <ul> <li>For Indirect and Direct 68, this pin is the<br/>read/write signal (R/W#).</li> </ul>                                                                                                                                                                                                    |

| WE#      | ı    | 112           | IC     | HIOVDD | Z               | <ul> <li>For Indirect and Direct 80 Type 1, this pin is the<br/>write enable signal (WE#).</li> </ul>                                                                                                                                                                                            |

|          |      |               |        |        |                 | <ul> <li>For Indirect and Direct 80 Type 2, this pin must<br/>be connected to HIOV<sub>DD</sub>.</li> </ul>                                                                                                                                                                                      |

|          |      |               |        |        |                 | <ul> <li>For Indirect and Direct 80 Type 3, this pin is the<br/>DB[7:0] lower byte write enable signal (WEL#).</li> </ul>                                                                                                                                                                        |

|          | I    |               | IC     | HIOVDD | Z               | This input pin has multiple functions.                                                                                                                                                                                                                                                           |

|          |      | I 113         |        |        |                 | <ul> <li>For Indirect and Direct 68, this pin is the<br/>D[15:8] upper data strobe (UDS#).</li> </ul>                                                                                                                                                                                            |

|          |      |               |        |        |                 | For Indirect and Direct 80 Type 1, this pin is the D[15:8] upper byte enable signal (UBE#).                                                                                                                                                                                                      |

| BE1#     |      |               |        |        |                 | For Indirect and Direct 80 Type 2, this pin is the DB[15:8] upper byte write enable signal (WEU#).                                                                                                                                                                                               |

|          |      |               |        |        |                 | For Indirect and Direct 80 Type 3, this pin is the DB[15:8] upper byte read enable signal (RDU#).                                                                                                                                                                                                |

|          |      |               |        | HIOVDD | Z               | This input pin has multiple functions.                                                                                                                                                                                                                                                           |

|          |      |               | IC     |        |                 | <ul> <li>For Indirect and Direct 68, this pin is the D[7:0]<br/>lower data strobe (LDS#).</li> </ul>                                                                                                                                                                                             |

| BE0#     |      | 114           |        |        |                 | <ul> <li>For Indirect and Direct 80 Type 1, this pin is the<br/>D[7:0] lower byte enable signal (LBE#).</li> </ul>                                                                                                                                                                               |

| BLon     | ·    |               |        |        | _               | <ul> <li>For Indirect and Direct 80 Type 2, this pin is the<br/>DB[7:0] lower byte write enable signal (WEL#).</li> </ul>                                                                                                                                                                        |

|          |      |               |        |        |                 | For Indirect and Direct 80 Type 3, this pin is the DB[15:8] upper byte write enable signal (WEU#).                                                                                                                                                                                               |

| WAIT#    | 0    | 116           | OLN35T | HIOVDD | Z               | During a data transfer, WAIT# is driven active (low) to force the system to insert wait states. It is driven inactive to indicate the completion of a data transfer. WAIT# is released to a high impedance state after the data transfer is complete. This pin can be masked using the CNF0 pin. |

Table 5-2: Host Interface Pin Descriptions (Continued)

| Туре | QFP21<br>Pin#                         | Cell  | Power  | RESET#<br>State                                         | Description                                                                                                                                                                                                                                  |

|------|---------------------------------------|-------|--------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 117                                   | OLN35 | HIOVDD | L                                                       | Interrupt output. When an internal interrupt occurs, this output pin is driven high. If the Host CPU clears the internal interrupt, this pin is driven low.                                                                                  |

| ı    | 118                                   | IHCS  | HIOVDD | Z                                                       | This active low input sets all internal registers to their default state and forces all signals to their inactive states.                                                                                                                    |

|      |                                       |       |        |                                                         | This input pin has multiple functions.                                                                                                                                                                                                       |

| I    | 119                                   | ICU   | HIOVDD | 1                                                       | <ul> <li>For Serial Bypass Mode, this pin is the serial<br/>chip select input for the Host CPU serial<br/>interface. When Serial Bypass Mode is enabled,<br/>the Host CPU can directly control the LCD2<br/>serial interface LCD.</li> </ul> |

|      |                                       |       |        |                                                         | This input pin has multiple functions.                                                                                                                                                                                                       |

| ı    | 121                                   | ICD   | HIOVDD | 0                                                       | For Serial Bypass Mode, this pin is the serial clock input for the Host CPU serial interface. When Serial Bypass Mode is enabled, the Host CPU can directly control the LCD2 serial interface LCD.                                           |

|      |                                       |       |        |                                                         | This input pin has multiple functions.                                                                                                                                                                                                       |

| I    | 124                                   | ICD   | HIOVDD | 0                                                       | For Serial Bypass Mode, this pin is the serial A0 command input for the Host CPU serial interface. When Serial Bypass Mode is enabled, the Host CPU can directly control the LCD2 serial interface LCD.                                      |

|      |                                       |       |        |                                                         | This input pin has multiple functions.                                                                                                                                                                                                       |

| ı    | 126                                   | ICD   | HIOVDD | 0                                                       | For Serial Bypass Mode, this pin is the serial data input for the Host CPU serial interface.     When Serial Bypass Mode is enabled, the Host CPU can directly control the LCD2 serial interface LCD.                                        |

|      | 0   1   1   1   1   1   1   1   1   1 | Name  | O      | O 117 OLN35 HIOVDD  I 118 IHCS HIOVDD  I 121 ICD HIOVDD | Type Pin# Cell Power State  O 117 OLN35 HIOVDD L  I 118 IHCS HIOVDD Z  I 119 ICU HIOVDD 1  I 121 ICD HIOVDD 0                                                                                                                                |

#### 5.2.3 LCD Interface

Many of the LCD Interface pins have different functions depending on the configured panel interface mode. See Table 5-12: "LCD Interface Pin Mapping," on page 45 for more details on the pin functions.

Mode 1 is LCD1: RGB, LCD2: SerialMode 2 is LCD1: Parallel, LCD2: Serial

• Mode 3 is LCD1: Parallel, LCD2: Parallel

• Mode 4 is LCD1: RGB, LCD2: Parallel

For further information on the three panel interface modes, see the bit description for REG[0032h] bits 1-0.

Table 5-3: LCD Interface Pin Descriptions

| Pin Name    | Туре | QFP21<br>Pin#                                                             | Cell  | Power  | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|------|---------------------------------------------------------------------------|-------|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPDAT[17:0] | 0    | 19,20,21,<br>22,23,25,<br>26,27,28,<br>30,31,32,<br>33,34,37,<br>39,40,41 | OLN35 | PIOVDD | L               | <ul> <li>These output pins have multiple functions.</li> <li>For Mode 1 and Mode 4 RGB interfaces, these pins are the LCD1 RGB data outputs.</li> <li>For Mode 2, Mode 3 and Mode 4 parallel interfaces, FPDAT[17:0] are the parallel interface data outputs.</li> <li>When REG[0056h] bit 13 = 1 or REG[005Eh] bit 13 = 1, these pins are controlled with tri-state.</li> <li>For Parallel Bypass Mode, these pins output the Host CPU data. See Table 5-13: "Serial Bypass Pin Mapping," on page 46.</li> </ul> |

| FPFRAME     | 0    | 42                                                                        | OLN35 | PIOVDD | L (H)           | <ul> <li>This output pin has multiple functions.</li> <li>For Mode 1 and Mode 4 RGB interfaces, this pin is the LCD1 frame pulse output.</li> <li>For Mode 2, Mode 3 and Mode 4 parallel interfaces, this pin is the write command output.</li> <li>For Parallel Bypass Mode, this pin outputs the Host CPU XWR signal.</li> </ul>                                                                                                                                                                                |

| FPLINE      | 0    | 43                                                                        | OLN35 | PIOVDD | L               | <ul> <li>This output pin has multiple functions.</li> <li>For Mode 1 and Mode 4 RGB interfaces, this pin is the LCD1 line pulse output.</li> <li>For Mode 2, Mode 3 and Mode 4 parallel interfaces, this pin is the A0 output.</li> <li>For Parallel Bypass Mode, this pin outputs the Host CPU A0 signal.</li> </ul>                                                                                                                                                                                             |

| FPSHIFT     | 0    | 45                                                                        | OLN35 | PIOVDD | L               | This output pin has multiple functions.  • For Mode 1 and Mode 4, this pin is the LCD1 pixel clock output.  • For all other cases, this pin is not used.                                                                                                                                                                                                                                                                                                                                                          |

Table 5-3: LCD Interface Pin Descriptions (Continued)

| Pin Name | Туре | QFP21<br>Pin# | Cell  | Power  | RESET#<br>State      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|---------------|-------|--------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRDY     | 0    | 46            | OLN35 | PIOVDD | L                    | This output pin has multiple functions.  For Mode 1 and Mode 4, this pin is the LCD1 DRDY output.  For all other cases, this pin is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

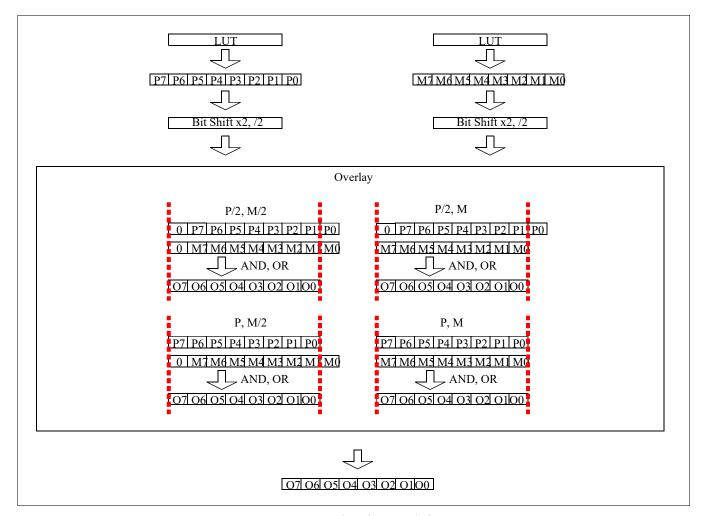

| FPCS1#   | 0    | 47            | OLN35 | PIOVDD | L (H)                | <ul> <li>This output pin has multiple functions.</li> <li>For Mode 1 and Mode 4, this pin is the LCD1 serial interface chip select output.</li> <li>For Mode 2 and Mode 3, this pin is the LCD1 parallel interface chip select output.</li> <li>For Parallel Bypass Mode, this pin outputs the Host CPU NCS1 signal.</li> </ul>                                                                                                                                                                                                                                                                                                                    |