## **Quasi-Resonant Current-Mode Controller for High-Power Universal Off-Line Supplies**

The NCP1380 hosts a high-performance circuitry aimed to powering quasi-resonant converters. Capitalizing on a proprietary valley-lockout system, the controller shifts gears and reduces the switching frequency as the power loading becomes lighter. This results in a stable operation despite switching events always occurring in the drain-source valley. This system works down to the 4<sup>th</sup> valley and toggles to a variable frequency mode beyond, ensuring an excellent standby power performance.

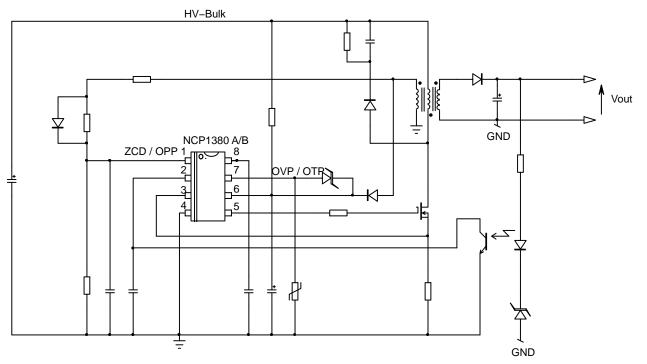

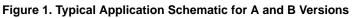

To improve the safety in overload situations, the controller includes an Over Power Protection (OPP) circuit which clamps the delivered power at high-line. Safety-wise, a fixed internal timer relies on the feedback voltage to detect a fault. Once the timer elapses, the controller stops and stays latched for option A and C or enters auto-recovery mode for option B and D.

Particularly well suited for adapter applications, the controller features a pin to implement either a combined overvoltage / overtemperature protection (Version A and B) or a combined brown-out/overvoltage protection (Version C and D).

## Features

- Quasi-Resonant Peak Current-Mode Control Operation

- Valley Switching Operation with Valley–Lockout for Noise–Immune Operation

- Frequency Foldback at Light Load to Improve the Light Load Efficiency

- Adjustable Over Power Protection

- Auto-Recovery or Latched Internal Output Short-Circuit Protection

- Fixed Internal 80 ms Timer for Short-Circuit Protection

- Combined Overvoltage and Overtemperature Protection (A and B Versions)

- Combined Overvoltage Protection and Brown-Out (C and D Versions)

- +500 mA/-800 mA Peak Current Source/Sink Capability

- Internal Temperature Shutdown

- Direct Optocoupler Connection

- Extended V<sub>CC</sub> Range Operation Up to 28 V

- Extremely Low No-Load Standby Power

- SO-8 Package

- These Devices are Pb-Free and are RoHS Compliant

## **Typical Applications**

- High Power ac-dc Converters for TVs, Set-Top Boxes etc.

- Offline Adapters for Notebooks

## **ON Semiconductor®**

www.onsemi.com

## QUASI-RESONANT PWM **CONTROLLER FOR HIGH POW-**ER AC-DC WALL ADAPTERS

#### MARKING DIAGRAMS

| 1380x | = Specific Device Code          |

|-------|---------------------------------|

| х     | = Device Option (A, B, C, or D) |

| А     | = Assembly Location             |

| L     | = Wafer Lot                     |

| Y     | = Year                          |

- = Year

- W = Work Week

- = Pb-Free Package

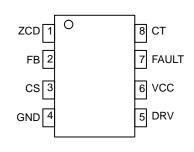

## **PIN CONNECTIONS**

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 25 of this data sheet.

## TYPICAL APPLICATION EXAMPLE

## PIN FUNCTION DESCRIPTION

| Pin N° | Pin Name        | Function                                                                                                                          | Pin Description                                                                                                                                                                                                                                                                      |

|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | ZCD             | Zero Crossing Detection<br>Adjust the over power protection                                                                       | Connected to the auxiliary winding, this pin detects the core<br>reset event.<br>Also, injecting a negative voltage smaller than 0.3 V on this<br>pin will perform over power protection.                                                                                            |

| 2      | FB              | Feedback pin                                                                                                                      | Hooking an optocoupler collector to this pin will allow regulation.                                                                                                                                                                                                                  |

| 3      | CS              | Current sense                                                                                                                     | This pin monitors the primary peak.                                                                                                                                                                                                                                                  |

| 4      | GND             | -                                                                                                                                 | The controller ground                                                                                                                                                                                                                                                                |

| 5      | DRV             | Driver output                                                                                                                     | The driver's output to an external MOSFET                                                                                                                                                                                                                                            |

| 6      | V <sub>CC</sub> | Supplies the controller                                                                                                           | This pin is connected to an external auxiliary voltage.                                                                                                                                                                                                                              |

| 7      | Fault           | Over voltage and Over temperature<br>protection (A and B versions)<br>Over-voltage and Brown-out<br>protection (C and D versions) | <ul><li>Pulling this pin down with an NTC or up with a zener diode allows to latch the controller.</li><li>This pin observes the HV rail and protects the circuit in case of low main conditions. It also offers a way to latch the circuit in case of over voltage event.</li></ul> |

| 8      | C <sub>T</sub>  | Timing capacitor                                                                                                                  | A capacitor connected to this pin acts as the timing capacitor in foldback mode.                                                                                                                                                                                                     |

## NCP1380 OPTIONS

|             | ОТР | OVP | Brown-Out | Auto–Recovery<br>Overcurrent<br>Protection | Latched<br>Overcurrent<br>Protection |

|-------------|-----|-----|-----------|--------------------------------------------|--------------------------------------|

| NCP1380 / A | Yes | Yes |           |                                            | Yes                                  |

| NCP1380 / B | Yes | Yes |           | Yes                                        |                                      |

| NCP1380 / C |     | Yes | Yes       |                                            | Yes                                  |

| NCP1380 / D |     | Yes | Yes       | Yes                                        |                                      |

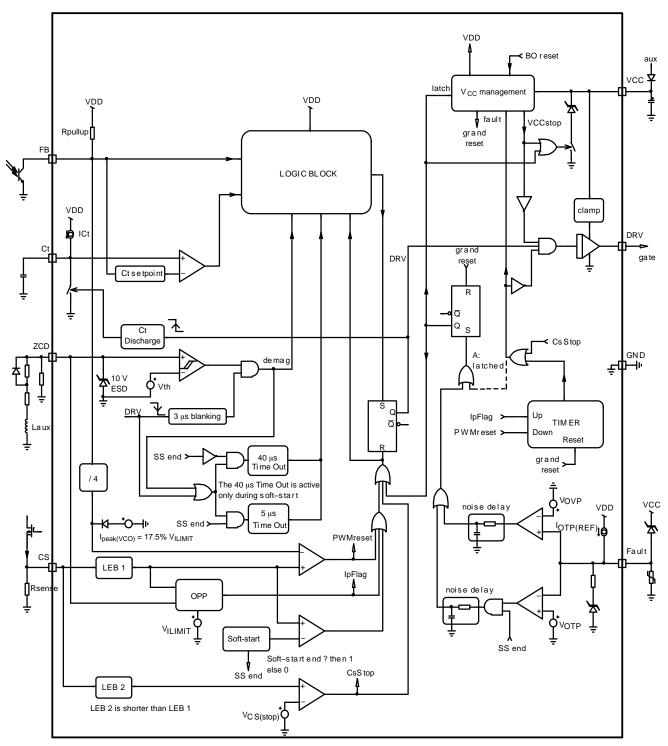

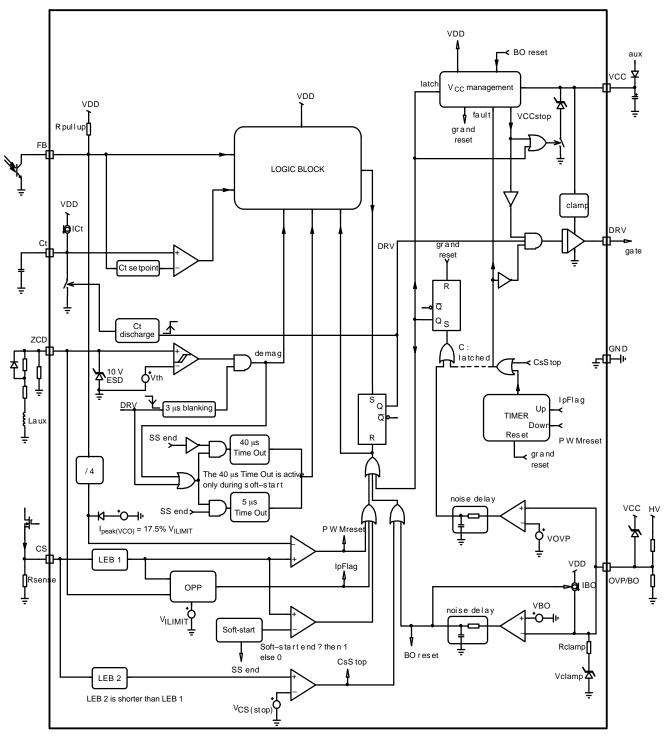

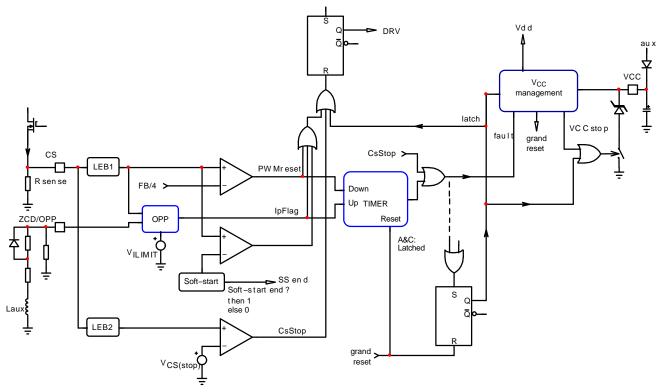

## INTERNAL CIRCUIT ARCHITECTURE

Figure 3. Internal Circuit Architecture for Versions A and B

Figure 4. Internal Circuit Architecture for Versions C and D

## MAXIMUM RATINGS

| Symbol                                         | Rating                                                                                                                                                | Value               | Unit    |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|

| V <sub>CC(MAX)</sub><br>I <sub>CC(MAX)</sub>   | Maximum Power Supply voltage, $V_{CC}$ pin, continuous voltage Maximum current for $V_{CC}$ pin                                                       | -0.3 to 28<br>±30   | V<br>mA |

| V <sub>DRV(MAX)</sub><br>I <sub>DRV(MAX)</sub> | Maximum driver pin voltage, DRV pin, continuous voltage<br>Maximum current for DRV pin                                                                | -0.3 to 20<br>±1000 | V<br>mA |

| V <sub>MAX</sub><br>I <sub>MAX</sub>           | Maximum voltage on low power pins (except pins DRV and V <sub>CC</sub> ) Current range for low power pins (except pins ZCD, DRV and V <sub>CC</sub> ) | −0.3 to 10<br>±10   | V<br>mA |

| I <sub>ZCD(MAX)</sub>                          | Maximum current for ZCD pin                                                                                                                           | +3 / -2             | mA      |

| $R_{\thetaJA}$                                 | Thermal Resistance Junction-to-Air                                                                                                                    | 120                 | °C/W    |

| T <sub>J(MAX)</sub>                            | Maximum Junction Temperature                                                                                                                          | 150                 | °C      |

|                                                | Operating Temperature Range                                                                                                                           | -40 to +125         | °C      |

|                                                | Storage Temperature Range                                                                                                                             | -60 to +150         | °C      |

|                                                | ESD Capability, HBM Model (Note 1)                                                                                                                    | 4                   | kV      |

|                                                | ESD Capability, MM Model (Note 1)                                                                                                                     | 200                 | V       |

|                                                | ESD Capability, CDM Model (Note 1)                                                                                                                    | 2                   | kV      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

This device series contains ESD protection and exceeds the following tests: Human Body Model 4000 V per JEDEC Standard JESD22, Method A114E Machine Model 200 V per JEDEC Standard JESD22, Method A115A Charged Device Model 2000 V per JEDEC Standard JESD22–C101D.

2. This device contains latchup protection and exceeds 100 mA per JEDEC Standard JESD78.

**ELECTRICAL CHARACTERISTICS** (Unless otherwise noted: For typical values  $T_J = 25^{\circ}C$ ,  $V_{CC} = 12$  V,  $V_{ZCD} = 0$  V,  $V_{FB} = 3$  V,  $V_{CS} = 0$  V,  $V_{fault} = 1.5$  V,  $C_T = 680$  pF) For min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , Max  $T_J = 150^{\circ}C$ ,  $V_{CC} = 12$  V)

| Symbol     |                                    | Condition | Min | Тур | Max | Unit |

|------------|------------------------------------|-----------|-----|-----|-----|------|

| SUPPLY SEC | TION – STARTUP AND SUPPLY CIRCUITS |           |     |     |     |      |

| SUFFLI SEC                                                                                                                   | SUFFLY SECTION - STARTUP AND SUFFLY CIRCUITS                                                                                                                                                      |                                                                                                                                                                                               |                              |                            |                              |    |  |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------|------------------------------|----|--|

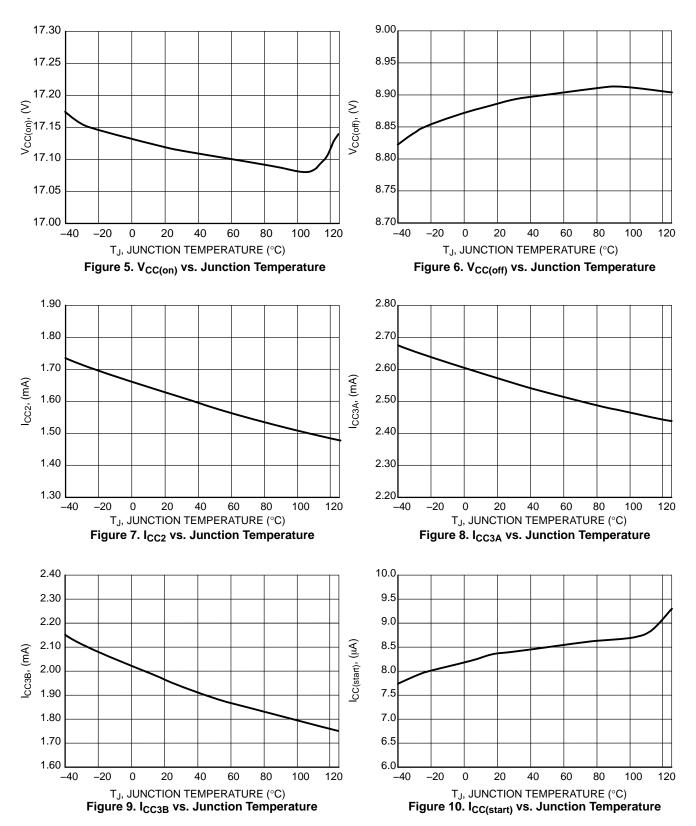

| V <sub>CC</sub> (on)<br>V <sub>CC</sub> (off)<br>V <sub>CC</sub> (HYS)<br>V <sub>CC</sub> (latch)<br>V <sub>CC</sub> (reset) | $\begin{array}{l} Supply Voltage \\ Startup Threshold \\ Minimum Operating Voltage \\ Hysteresis V_{CC(on)} - V_{CC(off)} \\ Clamped V_{CC} when latched-off \\ Internal logic reset \end{array}$ | $V_{CC}$ increasing<br>$V_{CC}$ decreasing<br>$V_{CC}$ decreasing, $I_{CC}$ = 30 $\mu$ A                                                                                                      | 16<br>8.3<br>7.2<br>6.2<br>6 | 17<br>9<br>8.0<br>7.2<br>7 | 18<br>9.4<br>9.2<br>8.2<br>8 | V  |  |

| t <sub>VCC(off)</sub><br>t <sub>VCC(reset)</sub>                                                                             | $V_{CC(off)}$ noise filter $V_{CC(reset)}$ noise filter                                                                                                                                           |                                                                                                                                                                                               |                              | 5<br>20                    |                              | μs |  |

| I <sub>CC(start)</sub>                                                                                                       | Startup current                                                                                                                                                                                   | FB pin open<br>V <sub>CC</sub> = V <sub>CC(on)</sub> $- 0.5$ V                                                                                                                                | -                            | 10                         | 20                           | μΑ |  |

| I <sub>CC(disch)</sub>                                                                                                       | Current that discharges $V_{CC}$ when the controller gets latched                                                                                                                                 | V <sub>CC</sub> = 12 V                                                                                                                                                                        | 3.0                          | 4.0                        | 5.0                          | mA |  |

| I <sub>CC(latch)</sub>                                                                                                       | Current into $V_{CC}$ that keeps the controller latched (Note 3)                                                                                                                                  | $V_{CC} = V_{CC(latch)}$                                                                                                                                                                      | 30                           | -                          | -                            | μΑ |  |

| ICC1<br>ICC2<br>ICC3A<br>ICC3B                                                                                               | Supply Current<br>Device Disabled/Fault (Note 3) B, C, and D only<br>Device Enabled/No output load on pin 5<br>Device Switching (F <sub>SW</sub> = 65 kHz)<br>Device Switching VCO mode           | $\begin{array}{l} V_{CC} > V_{CC(off)} \\ F_{sw} = 10 \ \text{kHz} \\ C_{DRV} = 1 \ \text{nF}, \ F_{SW} = 65 \ \text{kHz} \\ C_{DRV} = 1 \ \text{nF}, \ V_{FB} = 1.25 \ \text{V} \end{array}$ | -<br>-<br>-                  | 1.7<br>1.7<br>2.65<br>2.0  | 2.0<br>2.0<br>3.0<br>-       | mA |  |

#### **CURRENT COMPARATOR – CURRENT SENSE**

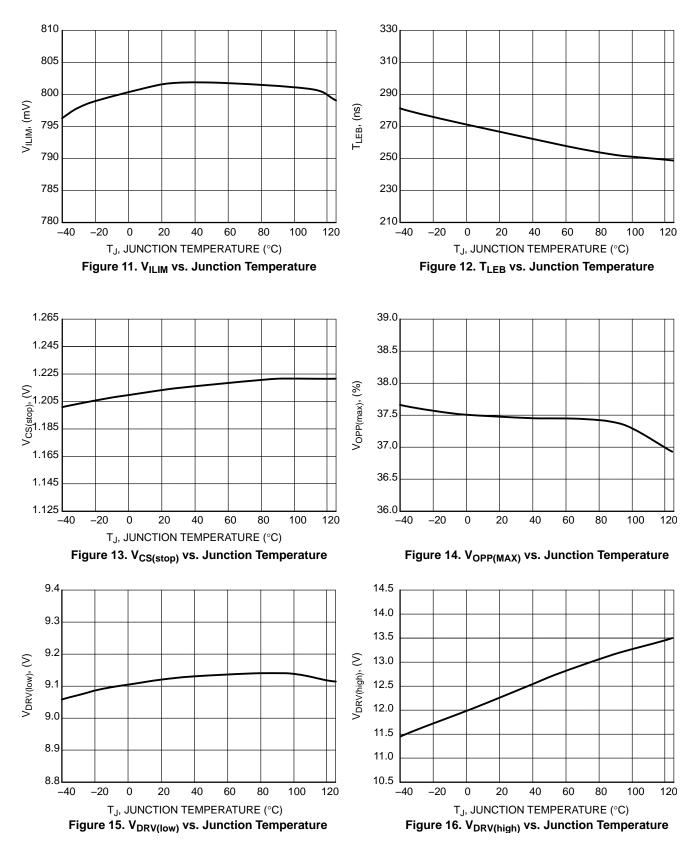

| VILIM                  | Current Sense Voltage Threshold                                           | $V_{FB}$ = 4 V, $V_{CS}$ increasing     | 0.76 | 0.8  | 0.84 | V  |

|------------------------|---------------------------------------------------------------------------|-----------------------------------------|------|------|------|----|

| t <sub>LEB</sub>       | Leading Edge Blanking Duration for VILIM                                  | Minimum on time minus t <sub>ILIM</sub> | 210  | 275  | 330  | ns |

| I <sub>bias</sub>      | Input Bias Current (Note 3)                                               | DRV high                                | -2   | -    | 2    | μΑ |

| t <sub>ILIM</sub>      | Propagation Delay                                                         | $V_{CS} > V_{ILIM}$ to DRV turn–off     | -    | 125  | 175  | ns |

| I <sub>peak(VCO)</sub> | Percentage of maximum peak current level at which VCO takes over (Note 4) | $V_{FB}$ = 0.4 V, $V_{CS}$ increasing   | 15.4 | 17.5 | 19.6 | %  |

| <b>ELECTRICAL CHARACTERISTICS</b> (continued) (Unless otherwise noted: For typical values T <sub>J</sub> = 25°C, V <sub>CC</sub> = 12 V, V <sub>ZCD</sub> = 0 V, |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{FB}$ = 3 V, $V_{CS}$ = 0 V, $V_{fault}$ = 1.5 V, $C_T$ = 680 pF) For min/max values $T_J$ = -40°C to +125°C, Max $T_J$ = 150°C, $V_{CC}$ = 12 V)             |

| Symbol                             |                                                            | Condition                                                            | Min   | Тур   | Max   | Unit |  |  |

|------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------|-------|-------|-------|------|--|--|

| CURRENT COMPARATOR – CURRENT SENSE |                                                            |                                                                      |       |       |       |      |  |  |

| V <sub>OPP(MAX)</sub>              | Setpoint decrease for $V_{ZCD} = -300 \text{ mV}$ (Note 5) | $V_{ZCD} = -300 \text{ mV}, V_{FB} = 4 \text{ V}, V_{CS}$ increasing | 35    | 37.5  | 40    | %    |  |  |

| V <sub>CS(stop)</sub>              | Threshold for immediate fault protection activation        |                                                                      | 1.125 | 1.200 | 1.275 | V    |  |  |

| t <sub>BCS</sub>                   | Leading Edge Blanking Duration for $V_{CS(stop)}$          |                                                                      | -     | 120   | -     | ns   |  |  |

## DRIVE OUTPUT – GATE DRIVE

| R <sub>SNK</sub><br>R <sub>SRC</sub> | Drive Resistance<br>DRV Sink<br>DRV Source         | V <sub>DRV</sub> = 10 V<br>V <sub>DRV</sub> = 2 V                                         |      | 12.5<br>20 | -<br>- | Ω  |

|--------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|------|------------|--------|----|

| I <sub>SNK</sub><br>I <sub>SRC</sub> | Drive current capability<br>DRV Sink<br>DRV Source | V <sub>DRV</sub> = 10 V<br>V <sub>DRV</sub> = 2 V                                         | -    | 800<br>500 | -      | mA |

| t <sub>r</sub>                       | Rise Time (10% to 90%)                             | $C_{DRV} = 1 \text{ nF}, V_{DRV} \text{ from 0 to}$<br>12 V                               | -    | 40         | 75     | ns |

| t <sub>f</sub>                       | Fall Time (90% to 10%)                             | $C_{DRV}$ = 1 nF, $V_{DRV}$ from 0 to 12 V                                                | -    | 25         | 60     | ns |

| V <sub>DRV(low)</sub>                | DRV Low Voltage                                    | $V_{CC} = V_{CC(off)} + 0.2 V$<br>$C_{DRV} = 1 \text{ nF, } R_{DRV} = 33 \text{ k}\Omega$ | 8.4  | 9.1        | -      | V  |

| V <sub>DRV(high)</sub>               | DRV High Voltage (Note 6)                          | $V_{CC} = V_{CC(MAX)}$<br>$C_{DRV} = 1 \text{ nF}$                                        | 10.5 | 13.0       | 15.5   | V  |

#### DEMAGNETIZATION INPUT - ZERO VOLTAGE DETECTION CIRCUIT

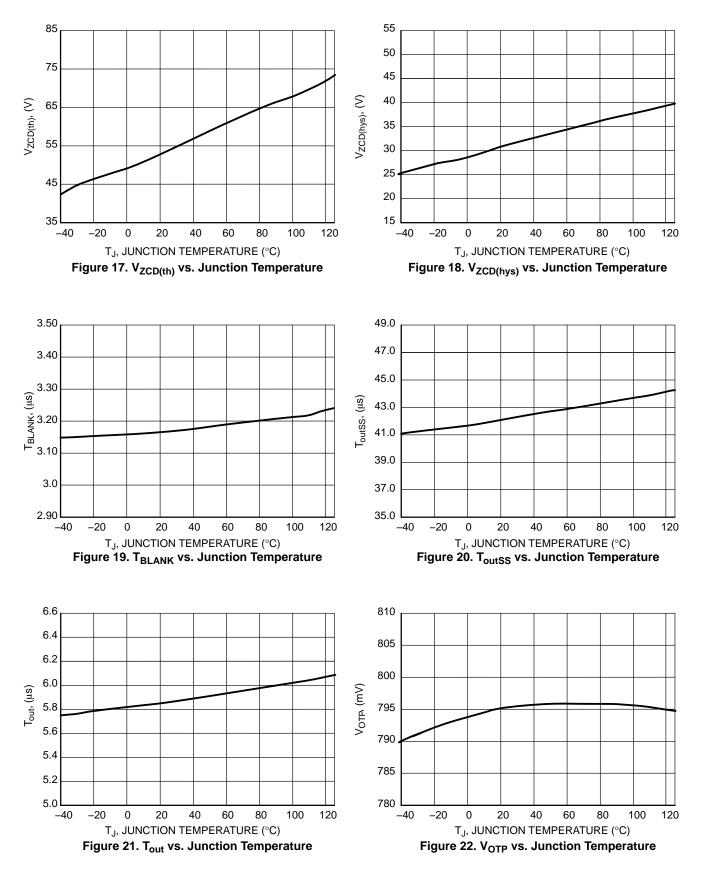

| V <sub>ZCD(TH)</sub>                   | ZCD threshold voltage                          | V <sub>ZCD</sub> decreasing                               | 35        | 55         | 90         | mV |

|----------------------------------------|------------------------------------------------|-----------------------------------------------------------|-----------|------------|------------|----|

| V <sub>ZCD(HYS)</sub>                  | ZCD hysteresis                                 | V <sub>ZCD</sub> increasing                               | 15        | 35         | 55         | mV |

| V <sub>CH</sub><br>V <sub>CL</sub>     | Input clamp voltage<br>High state<br>Low state | l <sub>pin1</sub> = 3.0 mA<br>l <sub>pin1</sub> = -2.0 mA | 8<br>-0.9 | 10<br>-0.7 | 12<br>-0.3 | V  |

| t <sub>DEM</sub>                       | Propagation Delay                              | V <sub>ZCD</sub> decreasing from 4 V to<br>-0.3 V         | -         | 150        | 250        | ns |

| C <sub>PAR</sub>                       | Internal input capacitance                     |                                                           | -         | 10         | -          | pF |

| t <sub>BLANK</sub>                     | Blanking delay after on-time                   |                                                           | 2.30      | 3.15       | 4.00       | μs |

| t <sub>outSS</sub><br>t <sub>out</sub> | Timeout after last demag transition            | During soft-start<br>After the end of soft-start          | 28<br>5.0 | 41<br>5.9  | 54<br>6.7  | μs |

| R <sub>ZCD(pdown)</sub>                | Pulldown resistor (Note 3)                     |                                                           | 140       | 320        | 700        | kΩ |

TIMING CAPACITOR

| V <sub>CT(MAX)</sub> | Maximum voltage on C <sub>T</sub> pin                      | $V_{FB} < V_{FB(TH)}$ | 5.15 | 5.40 | 5.65 | V  |  |

|----------------------|------------------------------------------------------------|-----------------------|------|------|------|----|--|

| I <sub>CT</sub>      | Source current                                             | V <sub>CT</sub> = 0 V | 18   | 20   | 22   | μΑ |  |

| V <sub>CT(MIN)</sub> | Minimum voltage on $C_{T}$ pin, discharge switch activated |                       | -    | -    | 90   | mV |  |

| CT                   | Recommended timing capacitor value                         |                       |      | 220  |      | pF |  |

|                      |                                                            |                       |      |      |      |    |  |

#### FEEDBACK SECTION

| R <sub>FB(pullup)</sub> | Internal pullup resistor                                         | 15   | 18  | 22   | kΩ |

|-------------------------|------------------------------------------------------------------|------|-----|------|----|

| I <sub>ratio</sub>      | Pin FB to current setpoint division ratio                        | 3.8  | 4.0 | 4.2  |    |

| V <sub>FB(TH)</sub>     | FB pin threshold under which $C_{T}$ is clamped to $V_{CT(MAX)}$ | 0.26 | 0.3 | 0.34 | V  |

| Symbol                                                                                                                                            | Condition                                                          | Min        | Tun                  | Max | Unit |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------|----------------------|-----|------|--|--|

| $V_{FB}$ = 3 V, $V_{CS}$ = 0 V, $V_{fault}$ = 1.5 V, $C_T$ = 680 pF) For min/max value                                                            | s T <sub>J</sub> = $-40^{\circ}$ C to +125°C, Max T <sub>J</sub> = | = 150°C, ' | V <sub>CC</sub> = 12 | V)  |      |  |  |

| <b>ELECTRICAL CHARACTERISTICS</b> (continued) (Unless otherwise noted: For typical values $T_J = 25^{\circ}C$ , $V_{CC} = 12$ V, $V_{ZCD} = 0$ V, |                                                                    |            |                      |     |      |  |  |

| Symbol             |                                                                                             | Condition                 | Min   | Тур | Max   | Unit |  |

|--------------------|---------------------------------------------------------------------------------------------|---------------------------|-------|-----|-------|------|--|

| FEEDBACK SECTION   |                                                                                             |                           |       |     |       |      |  |

|                    | Valley threshold                                                                            |                           |       |     |       | V    |  |

| V <sub>H2D</sub>   | FB voltage where 1 <sup>st</sup> valley ends and 2 <sup>nd</sup> valley starts              | V <sub>FB</sub> decreases | 1.316 | 1.4 | 1.484 |      |  |

| V <sub>H3D</sub>   | FB voltage where 2 <sup>nd</sup> valley ends and 3 <sup>rd</sup> valley starts              | V <sub>FB</sub> decreases | 1.128 | 1.2 | 1.272 |      |  |

| V <sub>H4D</sub>   | FB voltage where 3 <sup>rd</sup> valley ends and 4 <sup>th</sup> valley                     | V <sub>FB</sub> decreases | 0.846 | 0.9 | 0.954 |      |  |

| V <sub>HVCOD</sub> | starts<br>FB voltage where 4 <sup>th</sup> valley ends and VCO starts                       | V <sub>FB</sub> decreases | 0.732 | 0.8 | 0.828 |      |  |

| V <sub>HVCOI</sub> | FB voltage where VCO ends and 4 <sup>th</sup> valley starts                                 | V <sub>FB</sub> increases | 1.316 | 1.4 | 1.484 |      |  |

| V <sub>H4I</sub>   | FB voltage where 4 <sup>th</sup> valley ends and 3 <sup>rd</sup> valley                     | V <sub>FB</sub> increases | 1.504 | 1.6 | 1.696 |      |  |

| V <sub>H3I</sub>   | starts<br>FB voltage where 3 <sup>rd</sup> valley ends and 2 <sup>nd</sup> valley           | V <sub>FB</sub> increases | 1.692 | 1.8 | 1.908 |      |  |

| V <sub>H2I</sub>   | starts<br>FB voltage where 2 <sup>nd</sup> valley ends and 1 <sup>st</sup> valley<br>starts | V <sub>FB</sub> increases | 1.880 | 2.0 | 2.120 |      |  |

## FAULT PROTECTION (ALL VERSIONS)

| T <sub>SHDN</sub>         | Thermal Shutdown                | Device switching (F <sub>SW</sub><br>around 65 kHz)                                                                                                                                                                                 | 140  | -    | 170  | °C |

|---------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| T <sub>SHDN(HYS)</sub>    | Thermal Shutdown Hysteresis     |                                                                                                                                                                                                                                     | -    | 40   | -    | °C |

| t <sub>OVLD</sub>         | Overload Timer                  | $V_{FB} = 4 V, V_{CS} > V_{ILIM}$                                                                                                                                                                                                   | 75   | 85   | 95   | ms |

| <sup>t</sup> sstart       | Soft-start duration             | $\label{eq:VFB} \begin{array}{l} V_{FB} = 4 \ \text{V}, \ \text{V}_{CS} \ \text{ramping up}, \\ \text{measured from 1}^{\text{st}} \ \text{DRV} \\ \text{pulse to } V_{CS(\text{peak})} = 90\% \ \text{of} \\ V_{ILIM} \end{array}$ | 2.8  | 3.8  | 4.8  | ms |

| R <sub>Fault(clamp)</sub> | Clamp series resistor           |                                                                                                                                                                                                                                     | 1.3  | 1.55 | 1.8  | kΩ |

| V <sub>OVP</sub>          | Fault detection level for OVP   | V <sub>Fault</sub> increasing                                                                                                                                                                                                       | 2.35 | 2.5  | 2.65 | V  |

| t <sub>latch(delay)</sub> | Delay before latch confirmation |                                                                                                                                                                                                                                     | 22.5 | 30   | 37.5 | μS |

## FAULT PROTECTION A & B VERSIONS

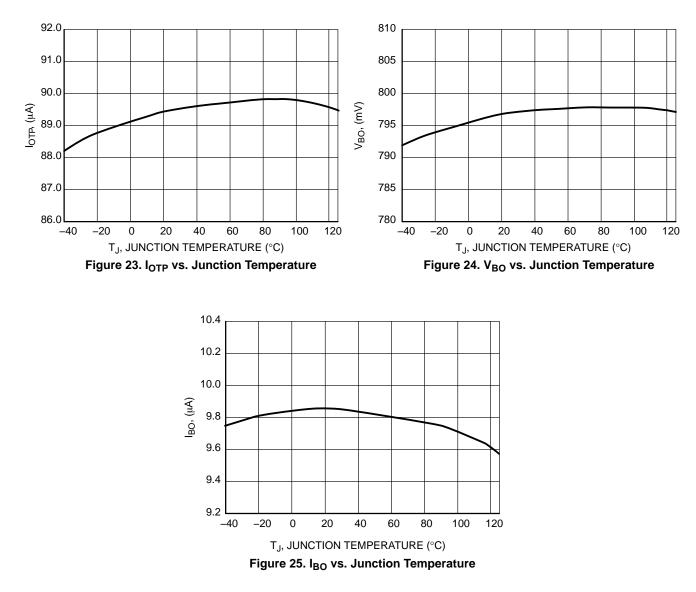

| I <sub>OTP(REF)</sub>     | Reference current for direct connection of an NTC (Note 7) | V <sub>Fault</sub> = V <sub>OTP</sub> + 0.2 V | 85    | 91   | 97    | μΑ |

|---------------------------|------------------------------------------------------------|-----------------------------------------------|-------|------|-------|----|

| V <sub>OTP</sub>          | Fault detection level for OTP                              | V <sub>Fault</sub> decreasing                 | 0.744 | 0.8  | 0.856 | V  |

| V <sub>Fault(clamp)</sub> | Clamped voltage (Fault pin left open)                      | Fault pin open                                | 1.13  | 1.35 | 1.57  | V  |

#### FAULT PROTECTION C & D VERSIONS

| V <sub>BO</sub>           | Brown–Out level                                 | V <sub>Fault</sub> decreasing                | 0.744 | 0.8 | 0.856 | V  |

|---------------------------|-------------------------------------------------|----------------------------------------------|-------|-----|-------|----|

| I <sub>BO</sub>           | Sourced hysteresis current $V_{Fault} > V_{BO}$ | V <sub>Fault</sub> = V <sub>BO</sub> + 0.2 V | 9     | 10  | 11    | μΑ |

| t <sub>BO(delay)</sub>    | Delay before entering and exiting Brown-out     |                                              | 22.5  | 30  | 37.5  | μs |

| V <sub>Fault(clamp)</sub> | Clamped voltage (Fault pin left open)           | Fault pin open                               | 1.0   | 1.2 | 1.4   | V  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Guaranteed by design.

The peak current setpoint goes down as the load decreases. It is frozen below I<sub>peak(VCO)</sub> (I<sub>peak</sub> = cst)

If negative voltage in excess to -300 mV is applied to ZCD pin, the current setpoint decrease is no longer guaranteed to be linear 6. Minimum value for  $T_J = 125^{\circ}C$ 7. NTC with  $R_{110} = 8.8 \text{ k}\Omega$ .

## **APPLICATION INFORMATION**

The NCP1380 implements a standard current-mode architecture operating in quasi-resonant mode. Due to a proprietary circuitry, the controller prevents valley-jumping instability and steadily locks out in selected valley as the power demand goes down. Once the fourth valley is reached, the controller continues to reduce the frequency further down, offering excellent efficiency over a wide operating range. Thanks to a fault timer combined to an OPP circuitry, the controller is able to efficiently limit the output power at high-line.

- Quasi-Resonance Current-mode operation: implementing quasi-resonance operation in peak current-mode control, the NCP1380 optimizes the efficiency by switching in the valley of the MOSFET drain-source voltage. Thanks to a proprietary circuitry, the controller locks-out in a selected valley and remains locked until the output loading significantly changes. When the load becomes lighter, the controller jumps into the next valley. It can go down to the 4<sup>th</sup> valley if necessary. Beyond this point, the controller reduces its switching frequency by freezing the peak current setpoint. During quasi-resonance operation, in case of very damped valleys, a 5.5 µs timer emulates the missing valleys.

- **Frequency reduction in light–load conditions**: when the 4<sup>th</sup> valley is left, the controller reduces the switching frequency which naturally improves the standby power by a reduction of all switching losses.

- Overpower protection (OPP): When the voltage on ZCD pin swings in flyback polarity, a direct image if the input voltage is applied on ZCD pin. We can thus reduce the peak current depending of V<sub>ZCD</sub> during the on-time.

- **Internal soft-start**: A soft-start precludes the main power switch from being stressed upon startup. Its duration is fixed and equal to 4 ms.

- Fault input (A and B versions): By combining a dual threshold on the Fault pin, the controller allows the direct connection of an NTC to ground plus a zener diode to a monitored voltage. In case the pin is brought below the OTP threshold by the NTC or above the OVP threshold by the zener diode, the circuit permanently latches–off and V<sub>CC</sub> is clamped to 7.2 V.

- Fault input (C and D versions): The C and D versions of NCP1380 include a brown–out circuit which safely stops the controller in case the input voltage is too low. Restart occurs via a complete startup sequence (latch reset and soft–start). During normal operation, the voltage on this pin is clamped to V<sub>clamp</sub> to give enough room for OVP detection. If the voltage on this pin increases above 2.5 V, the part latches–off.

- Short-circuit protection: Short-circuit and especially over-load protections are difficult to implement when a strong leakage inductance between auxiliary and power windings affects the transformer (where the auxiliary winding level does not properly collapse in presence of an output short). Here, when the internal 0.8 V maximum peak current limit is activated, the timer starts counting up. If the fault disappears, the timer counts down. If the timer reaches completion while the error flag is still present, the controller stops the pulses. This protection is latched on A and C version (the user must unplug and re-plug the power supply to restart the controller) and auto-recovery on B and D versions (if the fault disappears, the SMPS automatically resumes operation). In addition, all versions feature a winding short-circuit protection, that senses the CS signal and stops the controller if V<sub>CS</sub> reaches 1.5 x V<sub>ILIM</sub> (after a reduced LEB of t<sub>BCS</sub>). This additional comparator is enabled only during the main LEB duration t<sub>LEB</sub>, for noise immunity reason.

## NCP1380 OPERATING MODES

NCP1380 has two operating mode: quasi-resonant operation and VCO operation for the frequency foldback.

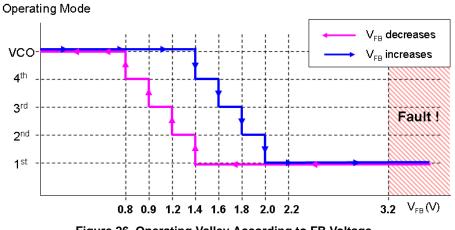

The operating mode is fixed by the FB voltage as portrayed by Figure 26:

- Quasi-resonant operation occurs for FB voltage higher than 0.8 V (FB decreasing) or higher than 1.4 V (FB increasing) which correspond to high output power and medium output power. The peak current is variable and is set by the FB voltage divided by 4.

- Frequency foldback or VCO mode occurs for FB voltage lower than 0.8 V (FB decreasing) or lower than 1.4 V (FB increasing). This corresponds to low output

#### power.

During VCO mode, the peak current decreases down to 17.5% of its maximum value and is then frozen. The switching frequency is variable and decreases as the output load decreases.

The switching frequency is set by the end of charge of the capacitor connected to the  $C_T$  pin. This capacitor is charged with a constant current source and the capacitor voltage is compared to an internal threshold fixed by FB voltage. When this capacitor voltage reaches the threshold the capacitor is rapidly discharged down to 0 V and a new period start.

Figure 26. Operating Valley According to FB Voltage

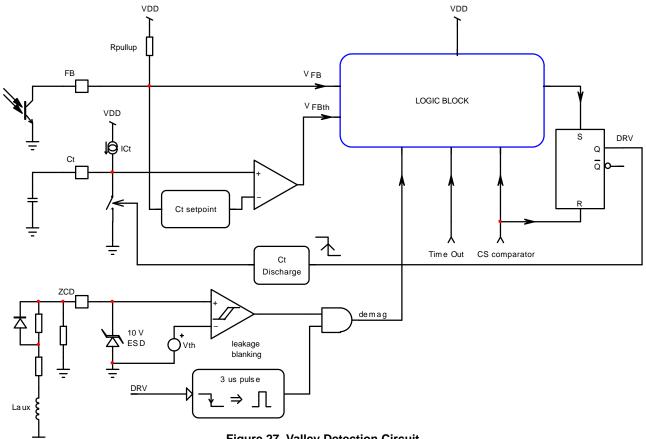

## VALLEY DETECTION AND SELECTION

The valley detection is done by monitoring the voltage of the auxiliary winding of the transformer. A valley is detected when the voltage on pin 1 crosses down the 55 mV internal

threshold. When a valley is detected, an internal counter is incremented. The operating valley (1st, 2nd, 3rd or 4th) is determined by the FB voltage as shown by Figure 26.

Figure 27. Valley Detection Circuit

As the output load decreases (FB voltage decreases), the valleys are incremented from the first to the fourth. When the fourth valley is reached, if FB voltage further decreases below 0.8 V, the controller enters VCO mode.

During VCO operation, the peak current continues to decrease until it reaches 17.5% of the maximum peak current: the switching frequency expands to deliver the

necessary output power. This allows achieving very low standby power consumption.

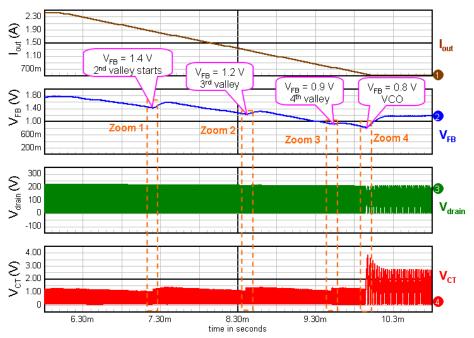

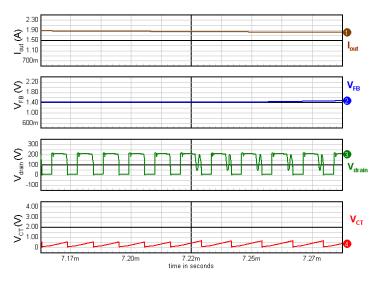

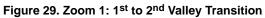

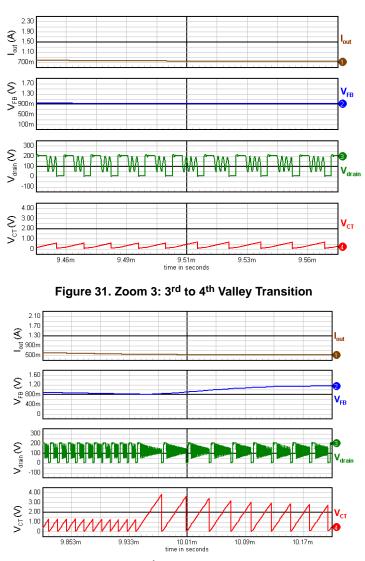

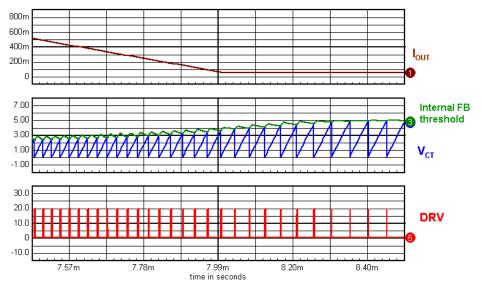

The Figure 28 shows a simulation case where the output current of a 19 V, 60 W adapter decreases from 2.8 A to 0.1 A. No instability is seen during the valley transitions (Figures 29, 30, 31 and 32)

Figure 28. Output Load is Decreased from 2.8 A Down to 100 mA at 120 Vdc Input Voltage

Figure 30. Zoom 2: 2<sup>nd</sup> to 3<sup>rd</sup> Valley Transition

Figure 32. Zoom 4: 4<sup>th</sup> Valley to VCO Mode Transition

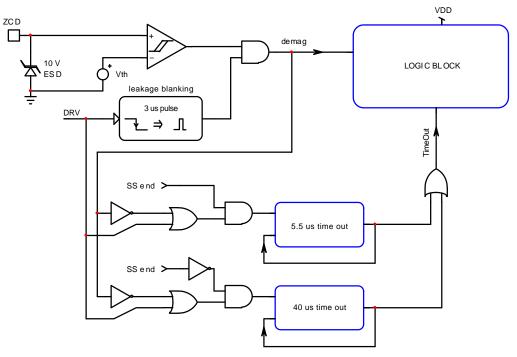

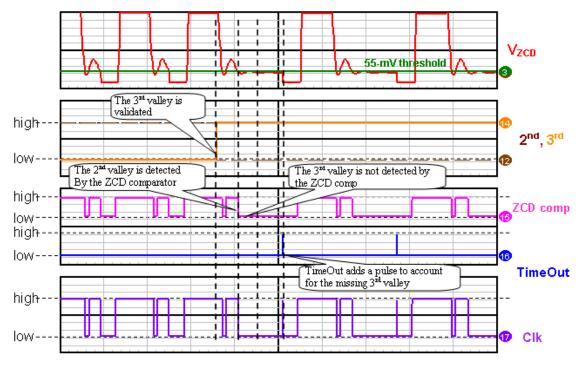

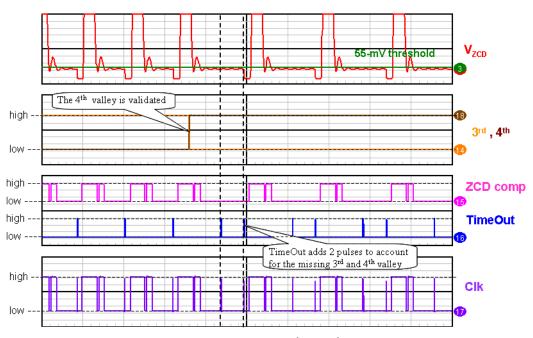

#### Time Out

In case of extremely damped free oscillations, the ZCD comparator can be unable to detect the valleys. To avoid such situation, NCP1380 integrates a Time Out function that acts as a substitute clock for the decimal counter inside the logic bloc. The controller thus continues its normal operation. To avoid having a too big step in frequency, the time out duration is set to  $5.5 \,\mu$ s. Figures 34 and 35 detail the time out operation.

The NCP1380 also features an extended time out during the soft-start.

Indeed, at startup, the output voltage reflected on the auxiliary winding is low. Because of the voltage drop

introduced by the Over Power Compensation diode (Figure 40), the voltage on the ZCD pin is very low and the ZCD comparator might be unable to detect the valleys. In this condition, setting the DRV Latch with the 5.5  $\mu$ s time–out can lead to a continuous conduction mode operation (CCM) at the beginning of the soft–start. This CCM operation only last a few cycles until the voltage on ZCD pin becomes high enough to be detected by the ZCD comparator. To avoid this, the time–out duration is extended to 40  $\mu$ s during the soft–start in order to ensure that the transformer is fully demagnetized before the MOSFET is turned–on.

Figure 33. Time Out Circuit

Figure 34. Time Out Case n°1: the 3<sup>rd</sup> Valley is Missing

Figure 35. Time Out Case n°2: the 3<sup>rd</sup> and 4<sup>th</sup> Valley are Missing

## VCO MODE OR FREQUENCY FOLDBACK

VCO operation occurs for FB voltage lower than 0.8 V (FB decreasing), or lower than 1.4 V (FB increasing). This corresponds to low output power.

During VCO operation, the peak current is fixed to 17.5% of his maximum value and the frequency is variable and expands as the output power decreases.

The frequency is set by the end of charge of the capacitor connected to the  $C_T$  pin. This capacitor is charged with a constant current source and its voltage is compared to an internal threshold (V<sub>FBth</sub>) fixed by FB voltage (see

Figure 27). When this capacitor voltage reaches the threshold, the capacitor is rapidly discharged down to 0 V and a new period start. The internal threshold is inversely proportional to FB voltage. The relationship between  $V_{FB}$  and  $V_{FBth}$  is given by Equation 1.

$$V_{FBth} = 6.5 - (10/3)V_{FB}$$

(eq. 1)

When  $V_{FB}$  is lower than 0.3 V,  $V_{CT}$  is clamped to  $V_{CT(MAX)}$  which is typically 5.5 V. Figure 36 shows the VCO mode at works.

Figure 36. In VCO Mode, as the Power Output Decreases, the Frequency Expands

#### SHORT-CIRCUIT OR OVERLOAD MODE

Figure 37 shows the implementation of the fault timer.

Figure 37. Overload Detection Schematic

When the current in the MOSFET is higher than  $V_{ILIM} / R_{sense}$ , "Max Ip" comparator trips and the digital timer starts counting: the timer count is incremented each 10 ms. When the current comes back within safe limits, "Max Ip" comparator becomes silent and the timer count down: the timer count is decremented each 10 ms. In normal overload conditions the timer reaches its completion when it has counted up 8 times 10 ms.

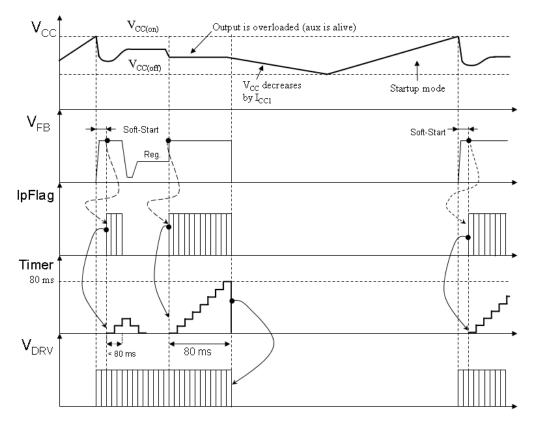

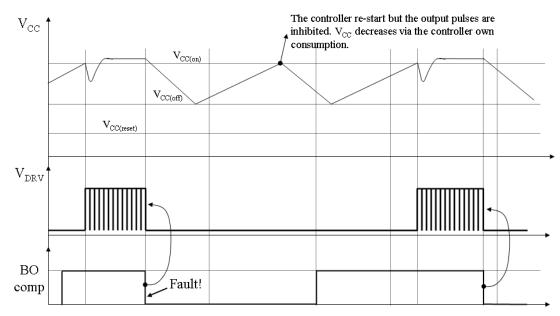

On B and D version, when the timers reaches its completion, the circuit enter auto-recovery mode: the circuit stops all operations and  $V_{CC}$  decreases via the circuit own consumption (I<sub>CC1</sub>). When  $V_{CC}$  reaches  $V_{CC(off)}$ , the circuit goes in startup mode and restart switching. (see Figure 38) This ensures a low duty-cycle burst operation in fault mode.

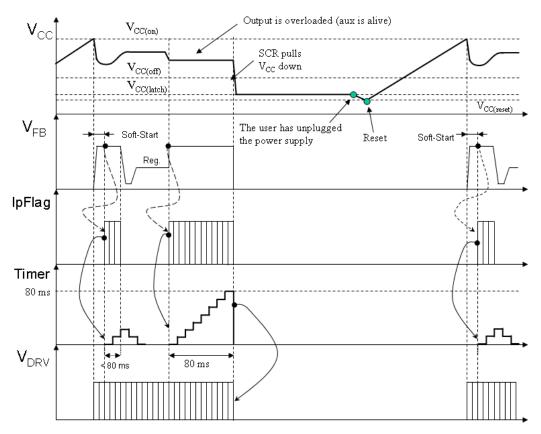

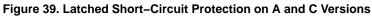

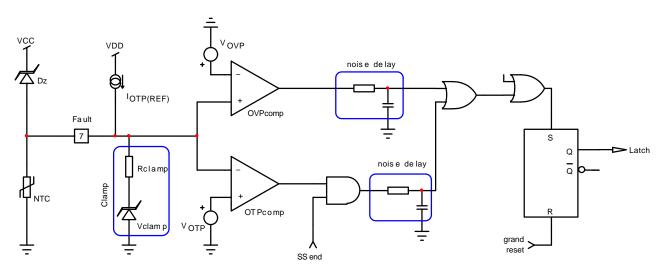

On A and C versions, when the timers finishes counting 80 ms, the circuit goes in latch mode (Figure 39): the DRV pulses stop and  $V_{CC}$  is pulled down to  $V_{CC(latch)}$  which is 7.2 V typically. The circuit un–latches when the current circulating in  $V_{CC}$  pin drops below  $I_{CC(latch)}$ .

In parallel to the cycle–by–cycle sensing of the CS pin, another comparator with a reduced LEB ( $t_{BCS}$ ) and a threshold of 1.2 V is able to sense winding short–circuit and immediately shut down the controller. Depending on the version, this additional protection is either latched or auto–recovery, according to the overload protection behavior.

Figure 38. Auto-Recovery Short-Circuit Protection on B and D Versions

#### OVER POWER COMPENSATION

The over power compensation is achieved by monitoring the signal on ZCD pin (pin 1). Indeed, a negative voltage applied on this pin directly affects the internal voltage reference setting the maximum peak current (Figure 40).

When the power MOSFET is turned-on, the auxiliary winding voltage becomes a negative voltage proportional to

Rz cd Ropu ZCD/OPP OPP IpFlag 1 ESD protection Ropl Demag Vth leakage blanking Tblank DRV ⇒

Figure 40. Over Power Compensation Circuit

To ensure optimal zero–crossing detection, a diode is needed to bypass  $R_{opu}$  during the off–time.

If we apply the resistor divider law on the pin 1 during the on–time, we obtain the following relationship:

$$\frac{R_{ZCD} + R_{opu}}{R_{opl}} = -\frac{N_{p,aux}V_{in} - V_{OPP}}{V_{OPP}} \qquad (eq. 2)$$

Where:

$N_{p,aux}$  is the auxiliary to primary turn ration:  $N_{p,aux} = N_{aux} \ / \ N_p$

V<sub>in</sub> is the DC input voltage

V<sub>OPP</sub> is the negative OPP voltage

By selecting a value for  $R_{opl}$ , we can easily deduce  $R_{opu}$ using Equation 2. While selecting the value for  $R_{opl}$ , we must be careful not choosing a too low value for this resistor in order to have enough voltage for zero–crossing detection during the off–time. We recommend having at least 8 V on ZCD pin, the maximum voltage being 10 V.

During the off-time, ZCD pin voltage can be expressed as follows:

$$V_{ZCD} = \frac{R_{opl}}{R_{ZCD} + R_{opl}} (V_{aux} - V_d)$$

(eq. 3)

We can thus deduce the relationship between  $R_{opl}$  and  $R_{ZCD}$ :

$$\frac{\mathsf{R}_{\mathsf{ZCD}}}{\mathsf{R}_{\mathsf{opl}}} = \frac{\mathsf{V}_{\mathsf{aux}} - \mathsf{V}_{\mathsf{d}} - \mathsf{V}_{\mathsf{ZCD}}}{\mathsf{V}_{\mathsf{ZCD}}} \tag{eq. 4}$$

$$\begin{split} V_{aux} &= 18 \text{ V} \\ V_d &= 0.6 \text{ V} \\ N_{p,aux} &= 0.18 \end{split}$$

Design example:

over power compensation.

If we want at least 8 V on ZCD pin, we have:

$$\frac{R_{ZCD}}{R_{opl}} = \frac{V_{aux} - V_{d} - V_{ZCD}}{V_{ZCD}}$$

$$= \frac{18 - 0.6 - 8}{8} \approx 1.2$$

(eq. 5)

We can choose:  $R_{ZCD} = 1 \text{ k}\Omega$  and  $R_{opl} = 1 \text{ k}\Omega$ .

For the over power compensation, we need to decrease the peak current by 37.5% at high line (370 Vdc). The corresponding OPP voltage is:

the input voltage. As the auxiliary winding is already

connected to ZCD pin for the valley detection, by selecting

the right values for  $R_{opu}$  and  $R_{opl}$ , we can easily perform

$$V_{OPP} = 0.375 \times V_{ILIM} = -300 \text{ mV}$$

(eq. 6)

Using Equation 2, we have:

$$\frac{R_{ZCD} + R_{opu}}{R_{opt}} = -\frac{N_{p,aux}V_{lin} - V_{OPP}}{V_{OPP}}$$

$$= \frac{-0.18 \times 370 - (-0.3)}{(-0.3)} = 221$$

(eq. 7)

Thus,

$$R_{opu} = 221_{Ropl} - R_{ZCD} = 221 \times 1k - 1k = 220 k\Omega$$

(eq. 8)

#### OVERVOLTAGE/OVERTEMPERATURE DETECTION (A AND B VERSIONS)

Overvoltage and overtemperature detection is achieved by reading the voltage on pin 7 (See Figure 41).

Figure 41. OVP/OTP Circuitry

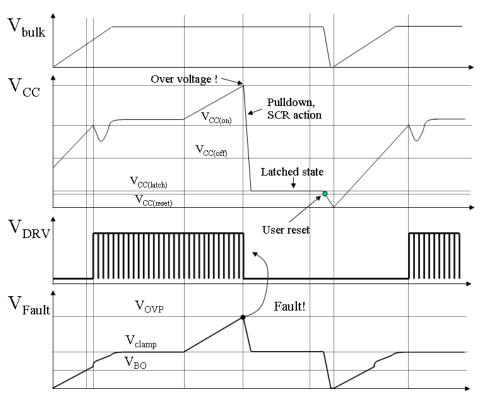

The I<sub>OTP(REF)</sub> current (91  $\mu$ A typ.) biases the Negative Temperature Coefficient sensor (NTC), naturally imposing a dc voltage on the OTP pin. An internal clamp limit the pin 7 voltage to 1.2 V when the NTC resistance is high (For example, at 25°C, R<sub>NTC</sub> > 100 k $\Omega$ ). When the temperature increases, the NTC's resistance reduces bringing the pin 7 voltage down until it reaches a typical value of 0.8 V: the comparator trips and latches–off the controller (see Figure 42). In case of overvoltage, the zener diode starts to conduct and inject current inside the internal clamp resistor  $R_{clamp}$ thus causing the pin 7 voltage to increase. When this voltage reaches the OVP threshold (2.5 V typ), the controller is latched–off: all the DRV pulses stops and V<sub>CC</sub> is pulled–down to V<sub>CC(latch)</sub> (7.2 V typ). The circuit un–latches when the current circulating in V<sub>CC</sub> pin drops below I<sub>CC(latch)</sub>, thus the user must unplug and replug the power supply.

Figure 42. Overvoltage and Overtemperature Chronograms

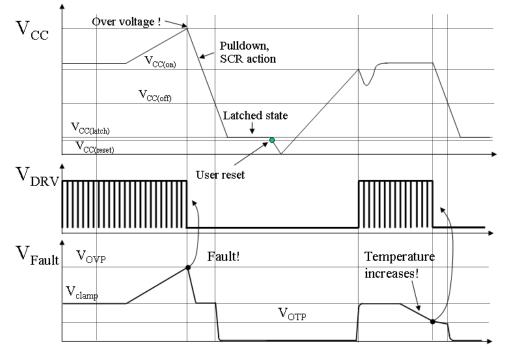

#### OVERVOLTAGE PROTECTION/BROWN-OUT (C AND D VERSIONS)

The C and D versions of NCP1380 combine brown–out and overvoltage detection on pin 7.

Figure 43. Brown-out and Overvoltage Protection

In order to protect the power supply against low input voltage condition, the pin 7 permanently monitors a fraction of the bulk voltage through a voltage divider. When this image of bulk voltage is below the  $V_{BO}$  threshold, the controller stops switching. When the bulk voltage comes back within safe limits, the circuit will restart pulsing only

when V<sub>CC</sub> reaches V<sub>CC(on)</sub> (Figure 44): this ensures a clean startup sequence with soft–start. The hysteresis for the brown–out function is implemented with a high side current source sinking 10  $\mu$ A when the brown–out comparator is high (V<sub>bulk</sub> < V<sub>bulk(on)</sub>)

Figure 44. Brown-out Operating Chronograms

In order to avoid having a too high voltage on pin 7 if the bulk voltage is high, an internal clamp limits the voltage.

In case of overvoltage, the zener diode will start to conduct and inject current inside the internal clamp resistor

$R_{clamp}$  thus causing pin 7 voltage to increase. When this voltage reaches  $V_{OVP}$ , the controller latches–off and stays latched until the user cycles down the power supply (Figure 45).

Figure 45. Operating Chronograms in Case of Overvoltage

The following equations show how to calculate the brownout resistors.

First of all, select the bulk voltage value at which the controller must start switching  $(V_{bulk(on)})$  and the bulk voltage for shutdown  $(V_{bulk(off)})$ . Then use the following equation to calculate  $R_{bou}$  and  $R_{bol}$ .

$$R_{bol} = \frac{V_{BO} \Big( V_{bulk(on)} - V_{bulk(off)} \Big)}{I_{BO} \Big( V_{bulk(on)} - V_{BO} \Big)}$$

(eq. 9)

$$R_{bou} = \frac{R_{bol} (V_{bulk(on)} - V_{BO})}{V_{BO}}$$

(eq. 10)

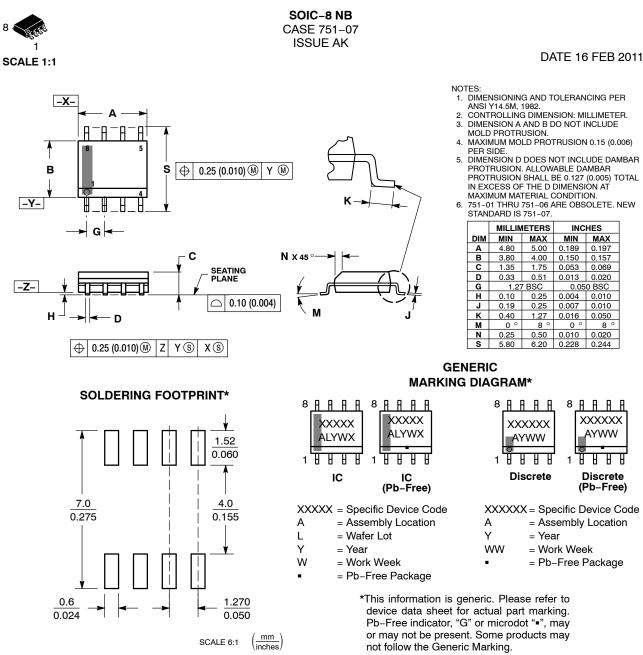

## **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCP1380ADR2G | SOIC–8<br>(Pb–Free) | 2500 / Tape & Reel    |

| NCP1380BDR2G | SOIC–8<br>(Pb–Free) | 2500 / Tape & Reel    |

| NCP1380CDR2G | SOIC–8<br>(Pb–Free) | 2500 / Tape & Reel    |

| NCP1380DDR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# onsemí

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                     | 98ASB42564B                                                                                                | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                     |                           |  |  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|

| DESCRIPTION: SOIC-8 NB PAGE 1 OF 2                                                   |                                                                                                            |                                                                                                                                                                                                                                                                                                       |                           |  |  |

| the right to make changes without furth<br>purpose, nor does <b>onsemi</b> assume ar | er notice to any products herein. <b>onsemi</b> make<br>ny liability arising out of the application or use | LLC dba <b>onsemi</b> or its subsidiaries in the United States and/or other courses no warranty, representation or guarantee regarding the suitability of its proof any product or circuit, and specifically disclaims any and all liability, incle under its patent rights nor the rights of others. | oducts for any particular |  |  |

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. 3. COLLECTOR 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT IOUT 6. IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4 SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5.

6.

7.

8 GATE 1

SOURCE 1/DRAIN 2

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. З. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 MIRROR 1 8. STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT OVI O 2 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 З. BASE #2 COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6 DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER: | 98ASB42564B | 564B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                          | PAGE 2 OF 2 |  |  |  |

|                  |             |                                                                                                                                                                                          |             |  |  |  |

onsem and of isor in are trademarks or semiconductor compension instructions, the do onsem or its subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced stat purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative