## 19VIN, 3.5/5.5A 1-Cell Li+ Battery Charger with Smart Power Selector and OTG for USBC PD

#### **General Description**

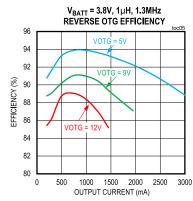

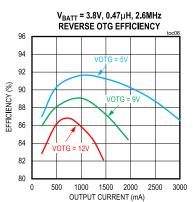

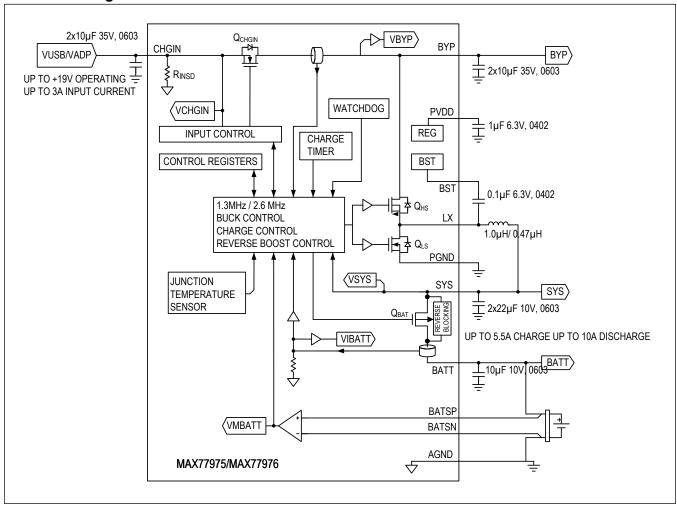

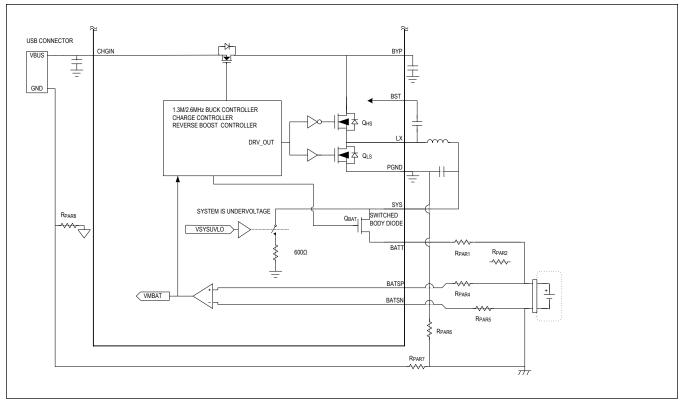

The MAX77975/MAX77976 is a high-performance high-input 3.5/5.5A fast charger with Smart Power Selector<sup>TM</sup>. The IC can operate as a reverse boost without an additional inductor, allowing the battery to share its power through the charging port and is voltage programmable from 5V to 12V. The device features fully integrated low-loss power switches to provide small solution size and high-efficiency, even at high input voltage and high charging current. Its high switching frequency allows the use of a smaller sized inductor. The IC features true load disconnection in reverse boost mode and has an adjustable output current protection limit. The device is highly flexible and programmable through I<sup>2</sup>C configuration.

The battery charger includes a Smart Power Selector to accommodate a wide range of battery sizes and system loads. The Smart Power Selector allows the system to start-up gracefully as soon as an input source is available, even when the battery is deeply discharged (dead battery) or missing. It can be configured so that when power is applied to the charger input, the battery charging can automatically start.

### **Applications**

- Gaming Devices

- VR Applications

- mPOS

- Tablet PCs

#### **Benefits and Features**

- High-Efficiency Single-Cell Switching Charger

- Up to 5.5A Charging with MAX77976

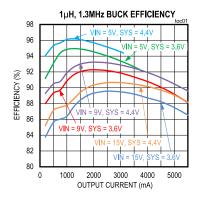

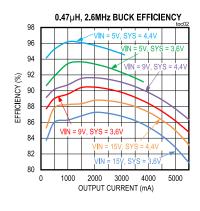

- 91.2% Buck Efficiency at 4A, 12V Input

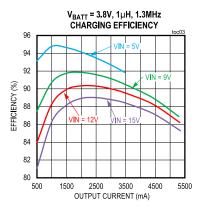

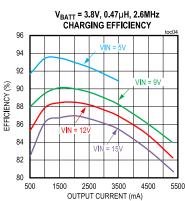

- 90.5% Charging Efficiency at 3.5A, 9V Input

- Optimized for High Voltage Input Operation

- Accelerate Charge Time by Monitoring Kelvin Sensing Battery Voltage

- Up to 3.2A Input Current Limit with AICL

- +28V Absolute Maximum Input Voltage Rating

- 4.7V to 19V Input Operating Voltage Range

- Reverse Boost with Programmable Output Voltage Options up to 12V

- Up to 18W for MAX77976

- Up to 12W for MAX77975

- Integrated Battery True-Disconnect FET

- $R_{DSON} = 7.7 \text{m}\Omega$

- Discharge Current up to 10A

- Support Shipping Mode and Low Battery Leakage Current

- 1.3MHz/2.6MHz Switching Frequency with 1μH/ 0.47μH Inductor

- Disconnect Input (DISQBAT)

- Safety

- Battery Temperature Sensing and Charge Safety Timer

- JEITA Guideline Compliant

- Thermal Regulation and Thermal Shutdown

- System Voltage OVLO/UVLO

- Charge Status Output for LED

- Push-Button Input for Exiting from Ship Mode

- External Discharge FET Enable Output

- Dedicated Input for Suspend Mode (SUSPND)

- I<sup>2</sup>C Interface

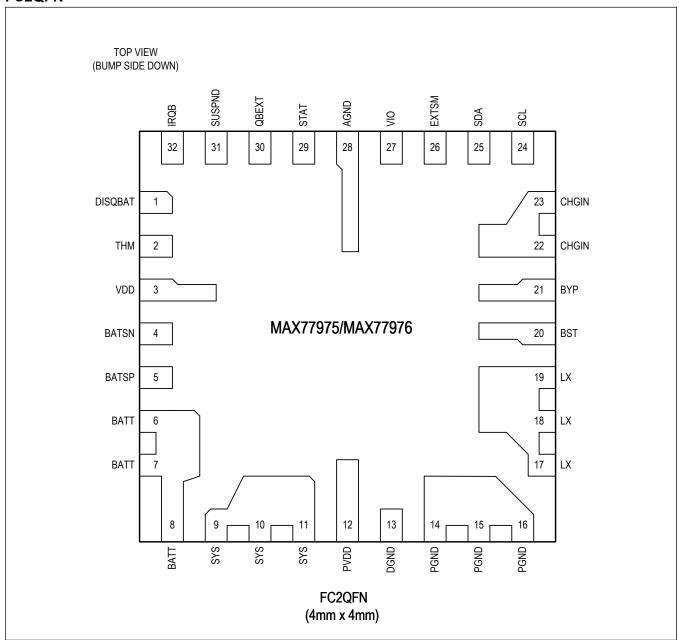

- 4mm x 4mm FC2QFN

Ordering Information appears at end of data sheet.

Smart Power Selector is a trademark of Maxim Integrated Products, Inc. USB Type-C is a registered trademark of USB Implementers Forum. PowerPath is a trademark of Linear Technology Corporation.

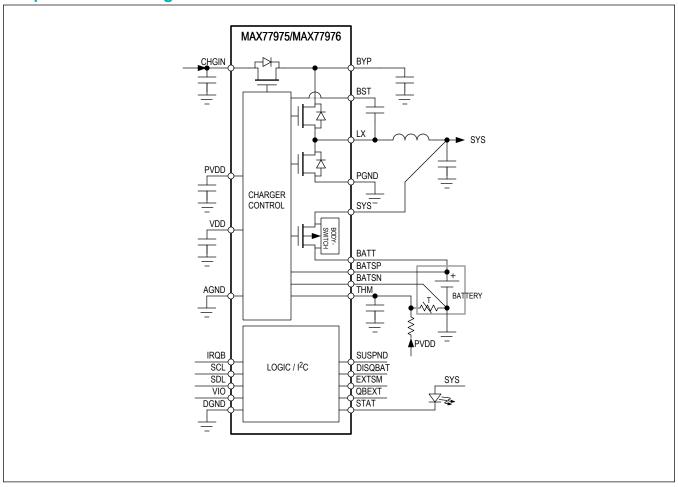

## **Simplified Block Diagram**

#### **TABLE OF CONTENTS**

| india of contants                       |      |

|-----------------------------------------|------|

| General Description                     | 1    |

| Applications                            | 1    |

| Benefits and Features                   | 1    |

| Simplified Block Diagram                | 2    |

| Absolute Maximum Ratings                | 7    |

| Package Information                     | 7    |

| FCQFN                                   | 7    |

| Electrical Characteristics              | . 11 |

| Typical Operating Characteristics       | . 21 |

| Pin Configuration                       | . 22 |

| FC2QFN                                  | . 22 |

| Pin Description                         | . 22 |

| Functional Diagram                      | . 24 |

| Functional Diagram                      |      |

| Detailed Description                    | . 25 |

| Switching Mode Charger                  | . 25 |

| Features                                | . 25 |

| Detailed Description                    | . 25 |

| Smart Power Selector (SPS)              |      |

| Input Validation                        |      |

| Input Current Limit                     | . 27 |

| Input Voltage Regulation Loop           | . 27 |

| System Self-Discharge with No Power     |      |

| Power States                            |      |

| Charger States                          |      |

| No Input Power or Charge Idle State     |      |

| Precharge State                         | . 33 |

| Trickle Charge State                    |      |

| Fast-Charge Constant Current (CC) State |      |

| Fast-Charge Constant Voltage (CV) State |      |

| Top-Off State                           |      |

| Done State                              | . 35 |

| Timer Fault State                       |      |

| Watchdog Timer                          |      |

| Thermal Shutdown State                  | . 36 |

| Charger Interrupt Debounce Time         | . 36 |

| Battery Differential Voltage Sense      | . 36 |

| Reverse Boost Mode                      | . 36 |

| Battery Overcurrent Protection          | . 37 |

## TABLE OF CONTENTS (CONTINUED)

| Battery to SYS Q <sub>BATT</sub> Switch Control (DISIBS) | 37 |

|----------------------------------------------------------|----|

| HW Control of Battery to SYS QBATT Switch—DISQBAT        | 38 |

| Thermal Management                                       | 38 |

| Thermal Foldback                                         | 38 |

| Thermistor Input (THM)                                   | 39 |

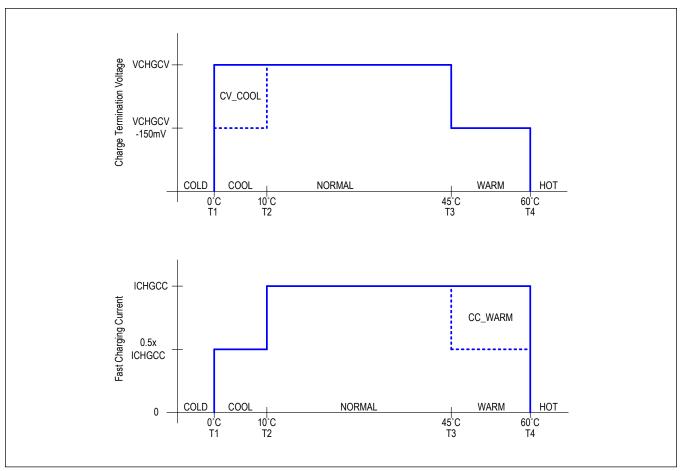

| JEITA Controlled Charging                                | 41 |

| Analog Low-Noise Power PVDD and VDD                      | 42 |

| Factory-Ship Mode                                        | 42 |

| External Q <sub>BATT</sub> Control I/O                   | 43 |

| Charge Status LED Indication                             | 43 |

| Design Considerations to Protect Against Hot Plug Event  | 43 |

| Top System Management                                    | 44 |

| Overview                                                 | 44 |

| Main Bias                                                | 44 |

| System Faults                                            | 44 |

| System Faults Debounce Time                              | 45 |

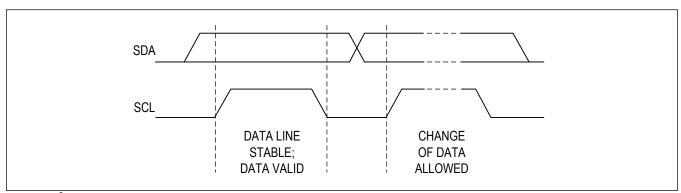

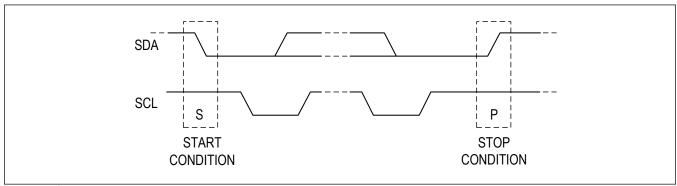

| I <sup>2</sup> C Interface Description                   | 45 |

| Register Map                                             | 49 |

| TOP                                                      | 49 |

| Register Details                                         | 49 |

| CHARGER                                                  | 52 |

| Register Details                                         | 53 |

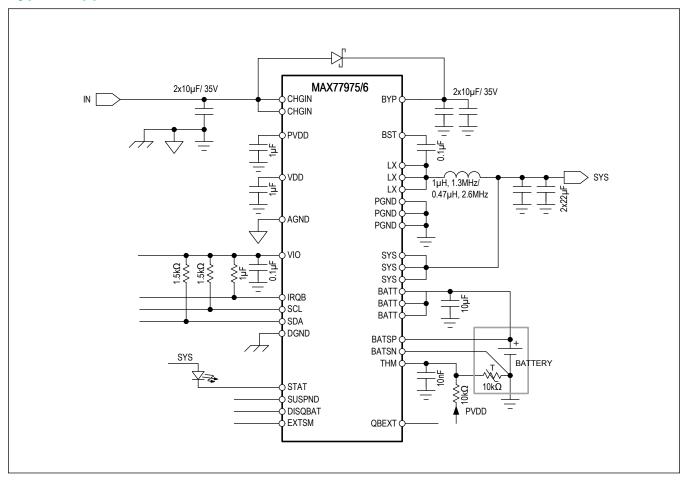

| Typical Application Circuits                             | 74 |

| Ordering Information                                     | 75 |

| Revision History                                         | 76 |

# 19VIN, 3.5/5.5A 1-Cell Li+ Battery Charger with Smart Power Selector and OTG for USBC PD

## LIST OF FIGURES

| Figure 1. System Self-Discharge Circuit                                 | 29 |

|-------------------------------------------------------------------------|----|

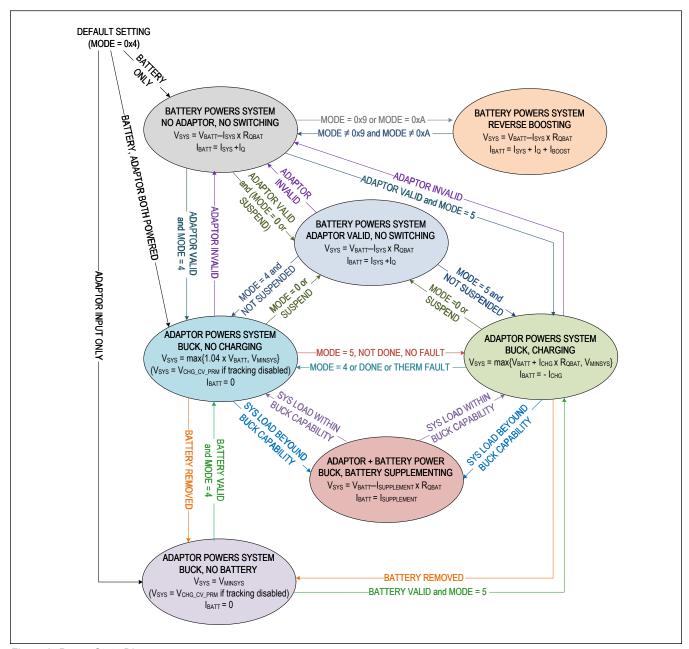

| Figure 2. Power State Diagram                                           | 30 |

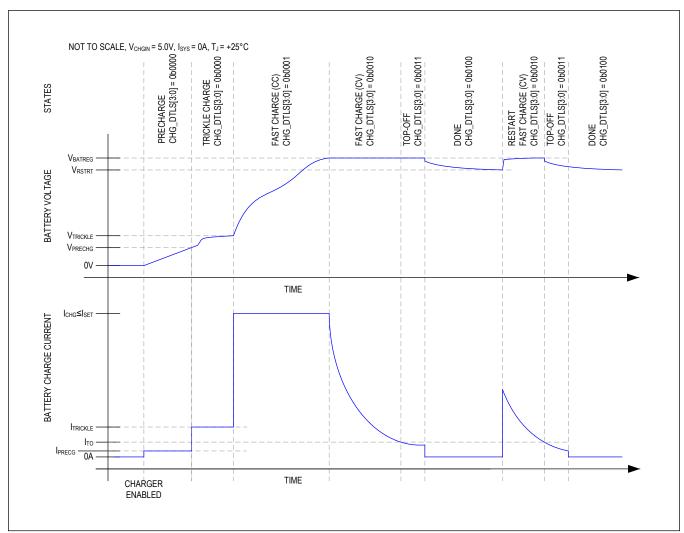

| Figure 3. Li+/Li-Poly Charge Profile                                    | 32 |

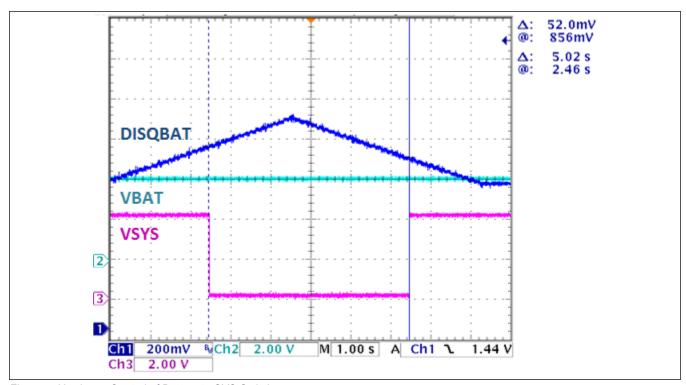

| Figure 4. Hardware Control of Battery to SYS Switch                     | 38 |

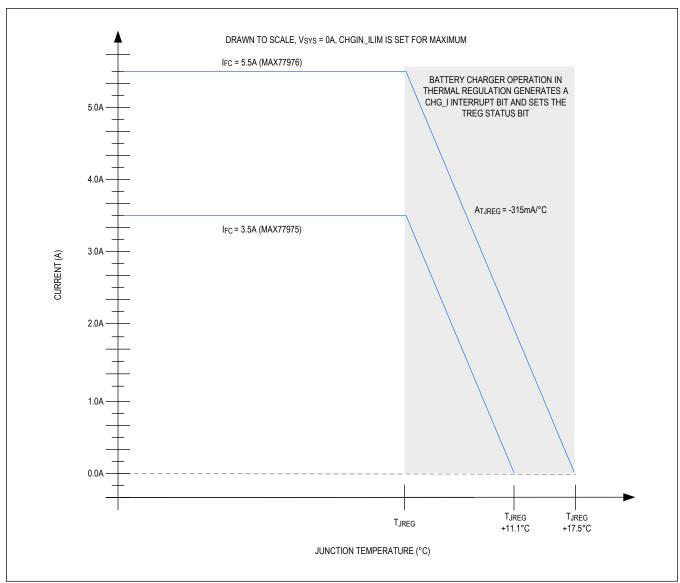

| Figure 5. Charge Currents vs. Junction Temperature                      | 39 |

| Figure 6. JEITA Controlled Charging                                     | 42 |

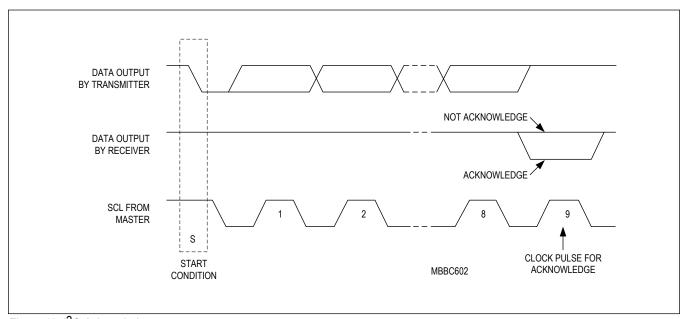

| Figure 7. I <sup>2</sup> C Bit Transfer                                 | 45 |

| Figure 8. I <sup>2</sup> C Start and Stop                               | 46 |

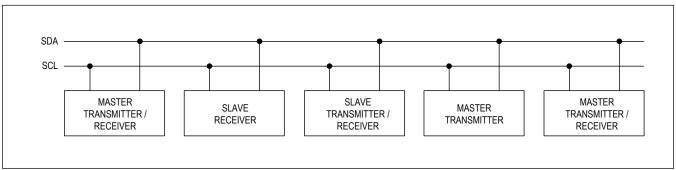

| Figure 9. System Configurations                                         | 46 |

| Figure 10. I <sup>2</sup> C Acknowledge                                 | 47 |

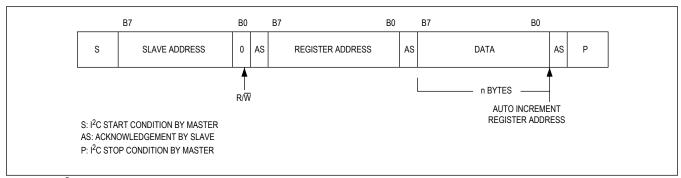

| Figure 11. I <sup>2</sup> C Master Transmits                            | 47 |

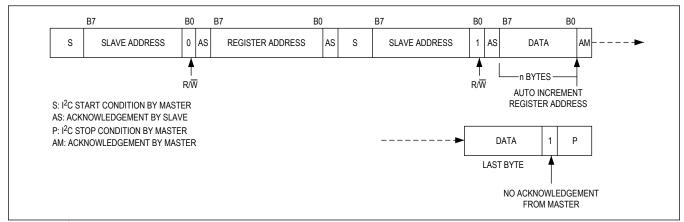

| Figure 12. I <sup>2</sup> C Master Reads After Setting Register Address | 48 |

| Figure 13. I <sup>2</sup> C Master Block Read                           | 48 |

# 19VIN, 3.5/5.5A 1-Cell Li+ Battery Charger with Smart Power Selector and OTG for USBC PD

| LIST OF TABLES                                       |    |

|------------------------------------------------------|----|

| Fable 1. Charger Interrupt Debounce Time             | 36 |

| Table 2. Trip Temperatures for Different Thermistors | 40 |

| Table 3. QBEXT Output in Different System Modes      | 43 |

| Гable 4. STAT_MODE = 0x0                             | 43 |

| Гable 5. STAT_MODE = 0x1                             | 43 |

| Fable 6. System Faults Debounce Time Summary         | 4  |

## **Absolute Maximum Ratings**

| CHGIN to PGND | -0.3V to +28V                   | VIO to AGND                             | -0.3V to +6.0V                     |

|---------------|---------------------------------|-----------------------------------------|------------------------------------|

| BYP to PGND   |                                 | DISQBAT, SUSPEND, QBEXT to AGND         |                                    |

| BYP to CHGIN  |                                 | EXTSM to AGND                           |                                    |

| BYP to LX     |                                 | IRQB, STAT to AGND                      |                                    |

| LX to PGND    | 0.3V to +22V                    | THM to AGND                             |                                    |

| BST to PVDD   | 0.3V to +22V                    | SDA, SCL to AGND                        | 0.3V to +6.0V                      |

| BST to LX     | 0.3V to +2.2V                   | CHGIN, BYP Continuous Current           | 3.4A <sub>RMS</sub>                |

| SYS to AGND   |                                 | LX, PGND Continuous Current             |                                    |

| BATT to AGND  | 0.3V to +6.0V                   | SYS, BATT Continuous Current            |                                    |

| BATSP to AGND | 0.3V to V <sub>BATT</sub> +0.3V | Continuous Power Dissipation (Multilaye | er Board) ( $T_A = +70^{\circ}C$ , |

| BATSP to BATT | 0.3V to +0.3V                   | deration is 35.34mW/°C above +70°C)     | mW to 2826.86mW                    |

| BATSN to AGND | 0.3V to +0.3V                   | Operating Temperature Range             | 40°C to +85°C                      |

| PGND to AGND  | 0.3V to +0.3V                   | Junction Temperature                    | +150°C                             |

| DGND to AGND  | 0.3V to +0.3V                   | Storage Temperature Range               | 65°C to +150°C                     |

| PVDD to PGND  | 0.3V to +2.2V                   | Soldering Temperature (reflow)          | +260°C                             |

| VDD to AGND   | 0.3V to +2.2V                   |                                         |                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

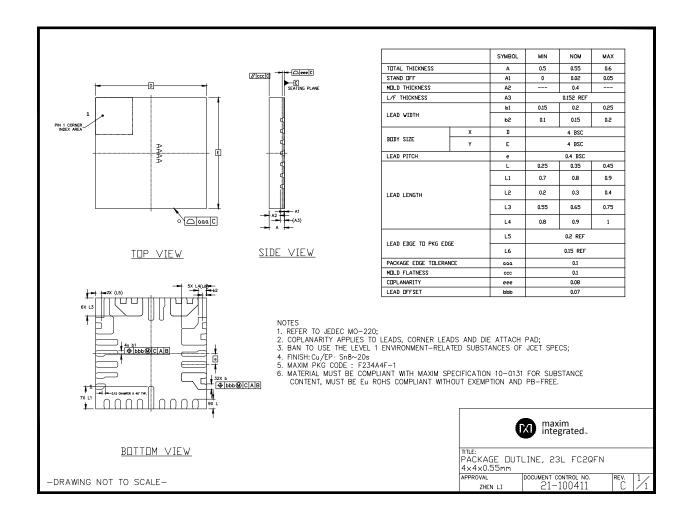

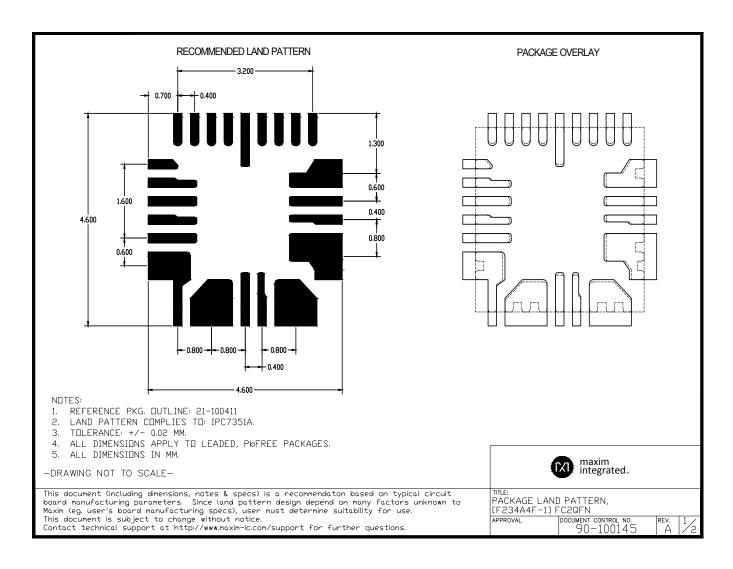

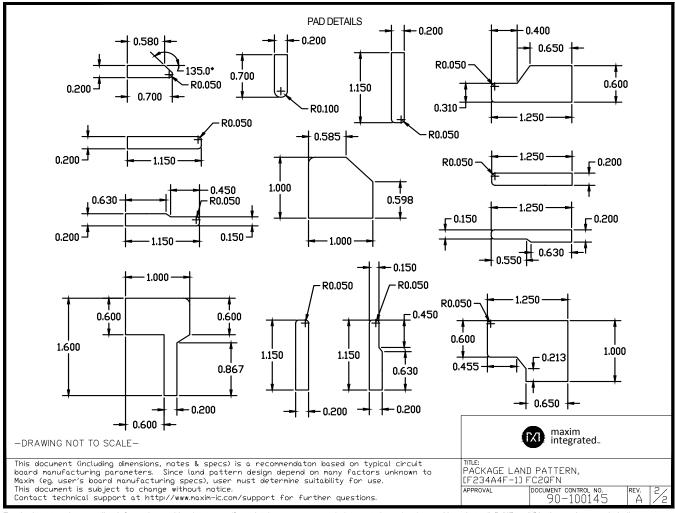

## **Package Information**

#### **FCQFN**

| Package Code                           | F234A4F+1        |

|----------------------------------------|------------------|

| Outline Number                         | <u>21-100411</u> |

| Land Pattern Number                    | <u>90-100145</u> |

| Thermal Resistance, Four-Layer Board:  |                  |

| Junction to Ambient (θ <sub>JA</sub> ) | 28.30°C/W        |

| Junction to Case (θ <sub>JC</sub> )    | 6.65°C/W         |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T_A = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                                  | SYMBOL                          | CONDITIONS                                                                                                                                                                                  | MIN                          | TYP                        | MAX                          | UNITS |

|--------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------|------------------------------|-------|

| GENERAL ELECTRICAL                         | CHARACTERIS                     | TICS                                                                                                                                                                                        |                              |                            |                              |       |

|                                            |                                 | V <sub>CHGIN</sub> = 5.0V, SUSPEND pin digital high or MODE = 0, DEEP_SUSP_DIS = 1                                                                                                          |                              | 0.19                       | 0.38                         | mA    |

| CHGIN Quiescent<br>Current                 | I <sub>CHGIN</sub>              | V <sub>CHGIN</sub> = 5.0V, SUSPEND pin digital high or MODE = 0, DEEP_SUSP_DIS = 0                                                                                                          |                              | 85                         |                              | μΑ    |

|                                            |                                 | $V_{CHGIN} = 5.0V$ , $V_{BATT} = 4.2V$ , MODE = 5, DONE state ( $V_{SYS} = 4.35V$ ), $I_{SYS} = 0A$                                                                                         |                              | 2.35                       |                              | mA    |

| Input Undervoltage<br>Supply Current       | I <sub>IN</sub>                 | V <sub>CHGIN</sub> = 2.4V, the input is undervoltage                                                                                                                                        |                              | 0.035                      |                              | mA    |

| BAT Quiescent Current                      | I <sub>BAT</sub>                | $V_{CHGIN}$ = 0V, $V_{BATT}$ = 3.6V, $Q_{BATT}$ FET is on, LPM = 0, $I_{SYS}$ = 0A                                                                                                          |                              | 29                         |                              | μΑ    |

| BAT Quiescent Current in Low-Power Mode    | I <sub>BAT</sub>                | $V_{CHGIN}$ = 0V, $V_{BATT}$ = 3.6V, $Q_{BATT}$ FET is on, LPM = 1, $I_{SYS}$ = 0A                                                                                                          |                              | 22                         |                              | μΑ    |

| BAT Quiescent Current in Factory-Ship Mode | I <sub>BAT</sub>                | $V_{CHGIN}$ = 0V, $V_{BATT}$ = 3.6V, $Q_{BATT}$ FET is off, $V_{SYS}$ = $V_{VDD}$ = 0V, factory-ship mode                                                                                   |                              | 3                          |                              | μΑ    |

| BAT Quiescent Current in Done State        | I <sub>MBDN</sub>               | $V_{CHGIN}$ = 5V, $I_{BYP}$ = 0A, $V_{BATT}$ = 4.2V, $I_{SYS}$ = 0A, $Q_{BATT}$ FET is off, MODE = 5, done state                                                                            |                              | 7.5                        | 10.5                         | μΑ    |

| SYS Operating Voltage                      | V <sub>SYS</sub>                | Guaranteed by V <sub>SYS_UVLO_R</sub> and V <sub>SYS_OVLO_R</sub>                                                                                                                           | V <sub>SYS_U</sub><br>VLO_R  |                            | V <sub>SYS_O</sub><br>VLO_R  | V     |

| VIO Voltage Range                          | V <sub>VIO</sub>                |                                                                                                                                                                                             | 1.62                         |                            | 5.5                          | V     |

| SCL, SDA Input Low<br>Level                | V <sub>SCL_SDA_IN_</sub>        | T <sub>A</sub> = +25°C                                                                                                                                                                      |                              |                            | 0.3 x<br>V <sub>VIO</sub>    | V     |

| SCL, SDA Input High<br>Level               | V <sub>SCL_SDA_IN_</sub>        | T <sub>A</sub> = +25°C                                                                                                                                                                      | 0.7 x<br>V <sub>VIO</sub>    |                            |                              | V     |

| SCL, SDA Input<br>Hysteresis               | V <sub>SCL_SDA_HY</sub><br>S    | T <sub>A</sub> = +25°C                                                                                                                                                                      |                              | 0.05 x<br>V <sub>VIO</sub> |                              | V     |

| SCL, SDA Logic Input<br>Current            | I <sub>SCL_SDA</sub>            | V <sub>SCL</sub> = V <sub>SDA</sub> = V <sub>VIO</sub> = 1.9V                                                                                                                               | -10                          |                            | +10                          | μΑ    |

| SDA Output Low<br>Voltage                  | V <sub>SDA_OUT_L</sub>          | I <sub>SDA</sub> = 20mA sinking                                                                                                                                                             |                              |                            | 0.4                          | V     |

| IRQB Output Low<br>Voltage                 | V <sub>IRQB_OUT_L</sub>         | I <sub>IRQB</sub> = 1mA sinking                                                                                                                                                             |                              |                            | 0.4                          | V     |

| IRQB Output High                           | I <sub>IRQB_H</sub>             | V <sub>IRQB</sub> = 5.5V, T <sub>A</sub> = 2+5°C                                                                                                                                            | -1                           | 0                          | +1                           | μA    |

| Leakage                                    |                                 | V <sub>IRQB</sub> = 5.5V, T <sub>A</sub> = +85°C                                                                                                                                            |                              | 0.1                        |                              | •     |

| CHGIN INPUT LIMITER                        | I                               | M                                                                                                                                                                                           |                              |                            | 1                            |       |

| CHGIN Operating<br>Voltage Range           | V <sub>CHGIN</sub>              | V <sub>CHGIN</sub> must be less than V <sub>CHGIN</sub> _OVLO and greater than both V <sub>CHGIN</sub> _UVLO and (V <sub>SYS</sub> + V <sub>CHGIN2SYS</sub> _TH) for the charger to turn-on | V <sub>CHGIN</sub> _<br>UVLO |                            | V <sub>CHGIN</sub> _<br>OVLO | V     |

| CHGIN Overvoltage<br>Threshold             | V <sub>CHGIN</sub> _OVLO        | V <sub>CHGIN</sub> rising                                                                                                                                                                   | 19                           | 19.5                       | 20                           | V     |

| CHGIN Overvoltage<br>Threshold Hysteresis  | V <sub>CHGIN_OVLO</sub><br>_HYS |                                                                                                                                                                                             |                              | 500                        |                              | mV    |

## **Electrical Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T_A = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                                                          | SYMBOL                         | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                             | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| CHGIN Undervoltage<br>Threshold Setting<br>Range                   | V <sub>CHGIN_UVLO</sub>        | V <sub>CHGIN</sub> rising, 20% hysteresis, programmable at 4.7V, 4.8V, 4.9V, 5.05V                                                                                                                                                                                                                                                                                                                     | 4.7  |      | 5.05 | V     |

| CHGIN Undervoltage<br>Threshold Accuracy                           | V <sub>CHGIN_UVLO</sub>        | V <sub>CHGIN</sub> rising, 4.7V setting                                                                                                                                                                                                                                                                                                                                                                | 4.6  | 4.7  | 4.8  | V     |

| CHGIN to SYS<br>Undervoltage Threshold<br>Rising                   | V <sub>CHGIN2SYS</sub> _<br>TH | V <sub>CHGIN</sub> - V <sub>SYS</sub> , rising                                                                                                                                                                                                                                                                                                                                                         | 0.12 | 0.20 | 0.28 | V     |

| CHGIN Turn-On<br>Threshold Validation<br>Delay                     | t <sub>D-UVLO</sub>            | Delay from V <sub>CHGIN</sub> > V <sub>CHGIN_UVLO</sub> to Q <sub>CHGIN</sub> FET enable                                                                                                                                                                                                                                                                                                               |      | 8    |      | ms    |

| CHGIN Switching Start<br>Delay                                     | <sup>t</sup> START             | Delay from Input Validation to LX switching (if charge or buck mode is selected and charger is not suspended); see the <i>Input Validation</i> section for input validation conditions                                                                                                                                                                                                                 |      | 150  |      | ms    |

| CHGIN Adaptive<br>Voltage Regulation<br>Threshold Setting<br>Range | V <sub>C</sub> HGIN_REG        | Programmable at 4.5V, 4.6V, 4.7V, 4.85V. The input voltage regulation loop decreases the input current to regulate V <sub>CHGIN</sub> at V <sub>CHGIN</sub> <sub>REG</sub> under weak input source conditions. If the input current is decreased to I <sub>IULO</sub> <sub>DET</sub> and the input voltage is equal or below V <sub>CHGIN</sub> <sub>REG</sub> , then the charger input is turned off. | 4.5  |      | 4.85 | V     |

| CHGIN Adaptive<br>Voltage Regulation<br>Threshold Accuracy         | V <sub>CHGIN_REG_</sub>        | 4.5V setting                                                                                                                                                                                                                                                                                                                                                                                           | 4.4  | 4.5  | 4.6  | V     |

| CHGIN Input Current<br>Limit Setting Range                         | I <sub>INLIMIT</sub>           | Programmable, 500mA default, 50mA step, production tested at 100mA, 500mA, 1000mA, 1800mA, and 3200mA settings only                                                                                                                                                                                                                                                                                    | 0.1  |      | 3.2  | A     |

|                                                                    |                                | Charger enabled, 500mA input current limit setting                                                                                                                                                                                                                                                                                                                                                     | 440  | 470  | 500  |       |

| CHGIN Input Current                                                |                                | Charger enabled, 1000mA input current limit setting                                                                                                                                                                                                                                                                                                                                                    | 880  | 940  | 1000 |       |

| Limit Accuracy                                                     | INLIMIT                        | Charger enabled, 1800mA input current limit setting                                                                                                                                                                                                                                                                                                                                                    | 1584 | 1692 | 1800 | mA    |

|                                                                    |                                | Charger enabled, 3200mA input current limit setting                                                                                                                                                                                                                                                                                                                                                    | 2816 | 3008 | 3200 |       |

| CHGIN Input Current<br>Low Threshold                               | lulo_det                       | Charger enabled, 3200mA input current limit setting                                                                                                                                                                                                                                                                                                                                                    |      | 60   |      | mA    |

| SYSTEM BUCK                                                        |                                |                                                                                                                                                                                                                                                                                                                                                                                                        | •    |      |      | •     |

| Buck Output Voltage<br>Setting Range (Tracking<br>Disabled)        | V <sub>SYSREG</sub>            | Programmable 4.15V to 4.46V in 10mV steps (5-bits). Production tested at 4.2V only.                                                                                                                                                                                                                                                                                                                    | 4.15 |      | 4.46 | V     |

## **Electrical Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T_A = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                                              | SYMBOL                          | CONDITIONS                                                                                                                                                          | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Buck Output Voltage<br>Accuracy (Tracking<br>Disabled) | V <sub>SYSREG_</sub> AC<br>C    | Buck only, charging disabled                                                                                                                                        | -3   |      | +3   | %     |

| Ruck Output Voltage                                    | V <sub>SYSREG_TR</sub><br>K_MIN | MODE = 4, SYS Tracking mode enabled, VBATT < VSYS_MIN/1.04                                                                                                          | 3.48 | 3.60 | 3.72 | V     |

| Buck Output Voltage<br>(Tracking Enabled)              | V <sub>SYSREG_TR</sub>          | MODE = 4, SYS Tracking mode enabled,<br>V <sub>BATT</sub> ≥ V <sub>SYS_MIN</sub> /1.04, V <sub>SYSREG_TRK</sub><br>represented as a percentage of V <sub>BATT</sub> |      | 104  |      | %     |

| Buck Inductor Current                                  | I <sub>HSILIM</sub>             | For MAX77976                                                                                                                                                        | 8.5  | 9.5  | 10.5 | ^     |

| Limit                                                  | I <sub>HSILIM</sub>             | For MAX77975                                                                                                                                                        | 5.95 | 7.00 | 8.05 | Α     |

| Buck Minimum On Time                                   | t <sub>ON-MIN</sub>             | Measured on LX                                                                                                                                                      |      | 100  |      | ns    |

| Buck Minimum Off Time                                  | t <sub>OFF-MIN</sub>            | Measured on LX                                                                                                                                                      |      | 100  |      | ns    |

| System Power-Up<br>Current (from BYP)                  | ISYSPU_BYP                      | Charger present, V <sub>SYS</sub> < V <sub>SYS_UVLO_R</sub>                                                                                                         | 50   | 75   | 100  | mA    |

| System Power-Up Time-<br>Out (from BYP)                | tsyspu_byp                      |                                                                                                                                                                     |      | 150  |      | ms    |

| CHARGER                                                | •                               |                                                                                                                                                                     |      |      |      |       |

| Precharge Charge<br>Current                            | IPRECHG                         | V <sub>BATT</sub> < V <sub>PRECHG</sub>                                                                                                                             | 40   | 55   | 80   | mA    |

| Precharge Voltage<br>Threshold                         | V <sub>PRECHG</sub>             | V <sub>BATT</sub> rising                                                                                                                                            | 2.4  | 2.5  | 2.6  | V     |

| Precharge Voltage<br>Threshold Hysteresis              | V <sub>PRECHG_HY</sub><br>S     |                                                                                                                                                                     |      | 500  |      | mV    |

| Trickle Charge Current                                 | ITRICKLE                        | TKEN = 1 by default, V <sub>PRECHG</sub> < V <sub>BATT</sub> < V <sub>TRICKLE</sub>                                                                                 | 270  | 300  | 330  | mA    |

| Trickle Charge Voltage<br>Threshold                    | V <sub>TRICKLE</sub>            | V <sub>BATT</sub> rising, TKEN = 1 by default                                                                                                                       | 3.0  | 3.1  | 3.2  | V     |

| Trickle Charge Voltage<br>Threshold Hysteresis         | V <sub>TRICKLE_HY</sub><br>S    | TKEN = 1 by default                                                                                                                                                 |      | 100  |      | mV    |

| Prequalification Time                                  | t <sub>PQ</sub>                 | Applies to the total time of precharge and trickle charge mode                                                                                                      |      | 30   |      | min   |

| Fast-Charge Current                                    | I <sub>FC</sub>                 | 100mA to 5500mA in 50mA steps;<br>production tested at 500mA, 1000mA,<br>3000mA, and 5000mA settings<br>(MAX77976 only)                                             | 0.1  |      | 5.5  | A     |

| Setting Range                                          |                                 | 100mA to 3500mA in 50mA steps;<br>production tested at 500mA, 1000mA,<br>and 3000mA settings (MAX77975 only)                                                        | 0.1  |      | 3.5  |       |

|                                                        |                                 | Programmed $I_{FC} \ge 500$ mA, $V_{BATT} > V_{SYSMIN}$ , $T_A = +25$ °C                                                                                            | -3.5 |      | +3.5 |       |

| Fast-Charge Current<br>Accuracy                        | I <sub>FC_ACC</sub>             | Programmed $I_{FC} \ge 500$ mA, $V_{BATT} > V_{SYSMIN}$ , $T_A = 0$ °C to +85°C                                                                                     | -6   |      | +6   | %     |

| . iourus,                                              |                                 | Programmed I <sub>FC</sub> ≥ 500mA, V <sub>TRICKLE</sub> < V <sub>BATT</sub> < V <sub>SYSMIN</sub> (LDO mode), T <sub>A</sub> = -5°C to +85°C                       | -10  |      | +10  |       |

## **Electrical Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T_A = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                                                         | SYMBOL                  | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Fast-Charge Current<br>Thermal Regulation<br>Setting Range        | T <sub>REG</sub>        | Junction temperature when charge current starts to reduce for thermal regulation; programmable from +85°C to +130°C in 5°C steps; default value is +115°C                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85    |      | 130   | °C    |

| Fast-Charge Current<br>Thermal Regulation<br>Gain                 | A <sub>TJRE</sub> G     | The charge current is decreased 5.73% of the fast-charge current full-scale for every degree that the junction temperature exceeds the thermal regulation temperature. This slope ensures that the full-scale current of 5.5A is reduced to 0A by the time the junction temperature is +17.5°C above the programmed loop set point. For lower programmed charge currents such as 480mA, this slope is valid for charge current reductions down to 80mA; below 100mA the slope becomes shallower but the charge current is reduced to 0A if the junction temperature is +20°C above the programmed loop set point. |       | -315 |       | mA/°C |

| Fast-Charge<br>Termination Voltage<br>Setting Range               | V <sub>BATTREG</sub>    | Programmable from 4.15V to 4.46V in 10mV steps (5-bits); production tested at 4.2V and 4.35V only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.15  |      | 4.46  | V     |

| Fast-Charge Termination Voltage Accuracy at Room Temp             | VBATTREG_AC             | V <sub>BATTREG</sub> = 4.35V setting, represented as percentage of V <sub>BATTREG</sub> ; T <sub>A</sub> = +25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.6  | -0.3 | +0.0  | %     |

| Fast-Charge<br>Termination Voltage<br>Accuracy                    | V <sub>BATTREG_AC</sub> | $V_{BATTREG}$ = 4.35V setting, represented as percentage of $V_{BATTREG}$ ; $T_A$ = -5°C to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -0.8  | -0.3 | +0.2  | %     |

| Fast-Charge<br>Termination Debounce<br>Time                       | t <sub>TERM</sub>       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | 30   |       | ms    |

| Fast-Charge Constant<br>Current + Constant<br>Voltage Safety Time | t <sub>FC</sub>         | Adjustable from 3hrs, 4hrs, 5hrs, 6hrs, 7hrs, 8hrs including a disable setting; 5hrs default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 5    |       | hrs   |

| Top-Off Current Setting<br>Range                                  | Іто                     | Programmable from 150mA to 850mA with 50mA in 16 steps; production tested at 150mA, 200mA, 500mA, and 850mA settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 150   |      | 850   | mA    |

|                                                                   |                         | 150mA setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 122.5 |      | 177.5 |       |

| Top-Off Current                                                   | lto .co                 | 200mA setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 170   |      | 230   | mA    |

| Accuracy                                                          | I <sub>TO_ACC</sub>     | 500mA setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 455   |      | 545   |       |

|                                                                   |                         | 850mA setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 787.5 |      | 912.5 |       |

| Top-Off Time                                                      | t <sub>TO</sub>         | Adjustable from 30sec to 70min in 10min steps; default setting is 30min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | 30   |       | min   |

## **Electrical Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T_A = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                                                | SYMBOL                 | CONDITIONS                                                                                                                                              | MIN   | TYP   | MAX   | UNITS |

|----------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Charge Restart<br>Threshold Setting<br>Range             | V <sub>RSTRT</sub>     | Adjustable at 100mV, 150mV, and 200mV; it can also be disabled                                                                                          | 100   | 150   | 200   | mV    |

| Charge Restart<br>Debounce Time                          | <sup>t</sup> CRDG      |                                                                                                                                                         |       | 130   |       | ms    |

| Charge State Change<br>Interrupt Debounce<br>Time        | tscidg                 | Excludes transition to timer fault state, watchdog timer state                                                                                          |       | 30    |       | ms    |

| Charge Watchdog Time                                     | $t_{WD}$               |                                                                                                                                                         |       | 80    |       | s     |

| Charge Timers<br>Accuracy                                | <sup>t</sup> ACC       |                                                                                                                                                         | -20   |       | +20   | %     |

| Charge-Overvoltage<br>Threshold                          | V <sub>COV</sub>       | V <sub>BAT_SP</sub> - V <sub>BAT_SN</sub> , relative to V <sub>CHG_CV_PRM</sub>                                                                         |       | 200   |       | mV    |

| Remote Sense BAT_SP<br>Input Current in<br>Charging Mode | IBAT_SP_CHG            | $V_{\text{BATT\_SP}} = V_{\text{BATT}} = 3.8V, \text{ MODE} = 5,$<br>$T_{\text{A}} = +\overline{2}5^{\circ}\text{C}$                                    |       | 14    |       | μA    |

| Remote Sense BAT_SN<br>Input Current in<br>Charging Mode | IBAT_SN_CHG            | V <sub>BATT_SN</sub> = 0, MODE = 5, T <sub>A</sub> = +25°C                                                                                              |       | 10    |       | μA    |

| SMART POWER SELECT                                       | TOR                    |                                                                                                                                                         |       |       |       | 1     |

| System Regulation                                        | V <sub>SYSMIN</sub>    | Charging enabled, V <sub>BATT</sub> < V <sub>SYSMIN</sub> - V <sub>SYSTRK</sub>                                                                         | 3.492 | 3.600 | 3.708 |       |

| Voltage (Charging<br>Enabled, Low Battery)               | V <sub>SYSTRK</sub>    | Charging enabled, V <sub>SYSMIN</sub> - V <sub>SYSTRK</sub> < V <sub>BATT</sub> < V <sub>SYSMIN</sub> , measure of V <sub>SYS</sub> - V <sub>BATT</sub> |       | 0.45  |       | V     |

| BATT to SYS Reverse<br>Regulation Voltage                | V <sub>BSREG</sub>     | Measure of V <sub>SYS</sub> - V <sub>BATT</sub> ; production tested at 10mA and 2A                                                                      |       | -100  |       | mV    |

| SYS Self-Discharge<br>Resistor                           | R <sub>SYSSD</sub>     | Switching is disabled, Q <sub>BATT</sub> FET is off, V <sub>SYS</sub> < V <sub>SYS</sub> UVLO_F                                                         |       | 600   |       | Ω     |

| SYSTEM POWER-UP                                          |                        |                                                                                                                                                         |       |       |       |       |

| System Power-Up<br>Current (from BATT)                   | ISYSPU_BAT             | V <sub>CHGIN</sub> = 0V                                                                                                                                 | 35    | 50    | 80    | mA    |

| System Power-Up<br>Voltage (from BATT)                   | V <sub>SYSPU_BAT</sub> | V <sub>SYS</sub> rising, 100mV hysteresis                                                                                                               | 1.9   | 2.0   | 2.1   | V     |

| System Power-Up Time-<br>Out (from BATT)                 | tsyspu_bat             |                                                                                                                                                         |       | 150   |       | ms    |

| REVERSE BOOST                                            |                        |                                                                                                                                                         |       |       |       |       |

| Reverse Boost<br>Quiescent Current                       |                        | V <sub>BYP</sub> = 5.1V, V <sub>BATT</sub> = 3.8V, MODE = 0x0A, V <sub>BYPSET</sub> = 0x1                                                               |       | 2.5   |       | mA    |

| Reverse Boost Output<br>Voltage Setting Range            | V <sub>BYP_OTG</sub>   | Measured on BYP pin, 2.5V < V <sub>BATT</sub> < 4.5V; adjustable from 5V to 12V with 0.1V step; production tested at 5V and 12V                         | 5     |       | 12    | V     |

| Reverse Boost Output<br>Voltage Accuracy                 | V <sub>BYP_ACC</sub>   | Measured on BYP, MODE = 0x0A,<br>V <sub>BYPSET</sub> = 0x1                                                                                              | 4.95  | 5.10  | 5.25  | V     |

## **Electrical Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                                               | SYMBOL                           | CONDITIONS                                                                                         | MIN  | TYP  | MAX   | UNITS |

|---------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------|------|------|-------|-------|

| Reverse Boost Inductor                                  | I <sub>LSILIM</sub>              | For MAX77976                                                                                       | 8.5  | 9.5  | 10.5  | ^     |

| Current Limit                                           | I <sub>LSILIM</sub>              | For MAX77975                                                                                       | 5.95 | 7.00 | 8.05  | A     |

| CHGIN OUTPUT LIMITE                                     | R                                |                                                                                                    |      |      |       |       |

| OTG Output Current<br>Limit Setting Range<br>(MAX77975) | ICHGIN_OTG_L<br>IM               | Configurable from 500mA to 2400mA in 100mA steps. Clamped to 12W power limit                       | 500  |      | 2400  | mA    |

| OTG Output Current<br>Limit Setting Range<br>(MAX77976) | ICHGIN_OTG_L<br>IM               | Configurable from 500mA to 3100mA in 100mA steps. Clamped to 18W power limit                       | 500  |      | 3100  | mA    |

|                                                         |                                  | 3.4V < V <sub>BATT</sub> < 4.5V, OTG_ILIM = 0x00                                                   | 500  | 537  | 575   |       |

|                                                         |                                  | 3.4V < V <sub>BATT</sub> < 4.5V, OTG_ILIM = 0x04                                                   | 900  | 967  | 1035  | 1     |

| OTG Output Current                                      | louoni oto i                     | 3.4V < V <sub>BATT</sub> < 4.5V, OTG_ILIM = 0x0A                                                   | 1500 | 1612 | 1725  |       |

| Limit                                                   | ICHGIN_OTG_L<br>IM               | 3.4V < V <sub>BATT</sub> < 4.5V, OTG_ILIM = 0x19<br>(MAX77975 only)                                | 2400 | 2580 | 2760  | mA    |

|                                                         |                                  | 3.4V < V <sub>BATT</sub> < 4.5V, OTG_ILIM = 0x19<br>(MAX77976 only)                                | 3000 | 3225 | 3450  |       |

| OTG Output Current<br>Limit Alarm Time                  | tOTG_ALARM                       | Delay from OTG overcurrent event to BYP_I interrupt generated                                      |      | 20   |       | ms    |

| OTG Output Current<br>Limit Fault Time                  | tOTG_FAULT                       | Delay from OTG overcurrent event to QCHGIN FET opening                                             |      | 30   |       | ms    |

| OTG Output Current<br>Limit Retry Time                  | totg_retry                       | Delay from Q <sub>CHGIN</sub> FET opening to Q <sub>CHGIN</sub> FET closing again (OTG_REC_EN = 1) |      | 300  |       | ms    |

| SWITCHE IMPEDANCES                                      | AND LEAKAGE                      | CURRENTS                                                                                           |      |      |       |       |

| CHGIN to BYP On<br>Resistance at Room<br>Temp           | R <sub>CHGIN2BYP</sub> _<br>ROOM | CHGIN pin to BYP pin, T <sub>A</sub> = +25°C                                                       |      | 13.0 | 16.9  | mΩ    |

| CHGIN to BYP On<br>Resistance                           | R <sub>CHGIN2BYP</sub>           | CHGIN pin to BYP pin, T <sub>A</sub> = -40°C to +85°C                                              |      | 13.0 | 20.0  | mΩ    |

| LX High-Side On<br>Resistance at Room<br>Temp           | R <sub>HS_ROOM</sub>             | BYP pin to LX pin, T <sub>A</sub> = +25°C                                                          |      | 31.0 | 43.4  | mΩ    |

| LX High-Side On<br>Resistance                           | R <sub>HS</sub>                  | BYP pin to LX pin, T <sub>A</sub> = -40°C to +85°C                                                 |      | 31.0 | 54.3  | mΩ    |

| LX Low-Side On<br>Resistance at Room<br>Temp            | R <sub>LS_ROOM</sub>             | LX pin to PGND pin, T <sub>A</sub> = +25°C                                                         |      | 16.0 | 22.4  | mΩ    |

| LX Low-Side On<br>Resistance                            | R <sub>LS</sub>                  | LX pin to PGND pin, T <sub>A</sub> = -40°C to +85°C                                                |      | 16.0 | 28.0  | mΩ    |

| BATT to SYS On<br>Resistance at Room<br>Temp            | R <sub>BAT2SYS_RO</sub><br>OM    | BATT pin to SYS pin, V <sub>BATT</sub> = 4.4V, T <sub>A</sub> = +25°C                              |      | 7.70 | 11.05 | mΩ    |

| BATT to SYS On<br>Resistance                            | R <sub>BAT2SYS</sub>             | BATT pin to SYS pin, V <sub>BATT</sub> = 4.4V, T <sub>A</sub> = -40°C to +85°C                     |      | 7.70 | 12.75 | mΩ    |

## **Electrical Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                              | SYMBOL                | CONDITIONS                                                                                           | MIN                        | TYP  | MAX                        | UNITS |

|----------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------|----------------------------|------|----------------------------|-------|

| LVI ookogo Current                     | 1                     | V <sub>LX</sub> = V <sub>PGND</sub> or V <sub>BYP</sub> , T <sub>A</sub> = +25°C                     |                            | 0.01 | 10                         |       |

| LX Leakage Current                     | ILX_LEAK              | V <sub>LX</sub> = V <sub>PGND</sub> or V <sub>BYP</sub> , T <sub>A</sub> = +85°C                     |                            | 1    |                            | μA    |

| BST Leakage Current                    | l                     | V <sub>BST</sub> - V <sub>LX</sub> = 1.8V, T <sub>A</sub> = +25°C                                    |                            | 0.01 | 10                         |       |

|                                        | <sup>I</sup> BST_LEAK | V <sub>BST</sub> - V <sub>LX</sub> = 1.8V, T <sub>A</sub> = +85°C                                    |                            | 1    |                            | μΑ    |

| BYP Leakage Current                    | I <sub>BYP_LEAK</sub> | $V_{BYP}$ = 5.5V, $V_{CHGIN}$ = 0V, $V_{LX}$ = 0V, charger disabled, $T_A$ = +25°C                   |                            | 0.01 | 10                         |       |

|                                        |                       | $V_{BYP}$ = 5.5V, $V_{CHGIN}$ = 0V, $V_{LX}$ = 0V, charger disabled, $T_A$ = +85°C                   |                            | 1    |                            | μA    |

| BATSP Input Current<br>Leakage         | I <sub>BATSP</sub>    | Charger disabled, V <sub>BATSP</sub> = V <sub>BATT</sub> , T <sub>A</sub> = +25°C                    |                            | ±1   |                            | μΑ    |

| BATSN Input Current<br>Leakage         | I <sub>BATSN</sub>    | Charger disabled, V <sub>BATSN</sub> = V <sub>AGND</sub> , T <sub>A</sub> = +25°C                    |                            | ±1   |                            | μΑ    |

| LOGIC AND CONTROL I                    | /Os                   |                                                                                                      |                            |      |                            |       |

|                                        |                       | SUSPND, DISQBAT, T <sub>A</sub> = +25°C                                                              |                            |      | 0.4                        |       |

| Input Low Level                        | V <sub>IL</sub>       | EXTSM, T <sub>A</sub> = +25°C                                                                        |                            |      | 0.3 x<br>V <sub>BATT</sub> | V     |

|                                        |                       | SUSPND, DISQBAT, T <sub>A</sub> = +25°C                                                              | 1.4                        |      |                            | V     |

| Input High Level                       | V <sub>IH</sub>       | EXTSM, T <sub>A</sub> = +25°C                                                                        | 0.7 x<br>V <sub>BATT</sub> |      |                            |       |

| Input Leakage Current                  | I <sub>LK</sub>       | SUSPND, DISQBAT, EXTSM pin, at 5.5V (including current through pulldown resistor)                    |                            | 24   | 60                         | μΑ    |

| Output Low Voltage<br>QBEXT            | V <sub>OLQBEXT</sub>  | Sourcing 1mA, T <sub>A</sub> = +25°C                                                                 |                            |      | 0.4                        | V     |

| Output High Leakage                    | l                     | V <sub>SYS</sub> = 5.5V, T <sub>A</sub> = +25°C                                                      | -1                         | 0    | +1                         |       |

| QBEXT                                  | ILQBEXT               | V <sub>SYS</sub> = 5.5V, T <sub>A</sub> = +85°C                                                      |                            | 0.1  |                            | μΑ    |

| SUSPND Internal<br>Pulldown Resistor   | R <sub>SUSPND</sub>   |                                                                                                      |                            | 235  |                            | kΩ    |

| DISQBAT Internal<br>Pulldown Resistor  | R <sub>DISQBAT</sub>  |                                                                                                      |                            | 235  |                            | kΩ    |

| EXTSM Internal<br>Pulldown Resistor    | R <sub>EXTSM</sub>    |                                                                                                      |                            | 235  |                            | kΩ    |

| EXTSM Debounce Time                    | textsm_deb            | V <sub>BATT</sub> in 3.3V to 4.5V range, EXTSM_T<br>= 0                                              |                            | 10   |                            |       |

|                                        |                       | V <sub>BATT</sub> in 3.3V to 4.5V range, EXTSM_T<br>= 1                                              |                            | 0.1  |                            | - ms  |

| CHARGE STATUS INDIC                    | ATOR                  |                                                                                                      |                            |      |                            |       |

| Charge Status Current<br>Setting Range | I <sub>STAT_RNG</sub> | 5mA to 20mA in 5mA steps; production tested at V <sub>STAT</sub> - V <sub>AGND</sub> = 1.0V and 5.0V | 5                          |      | 20                         | mA    |

| Charge Status Current<br>Accuracy      | ISTAT_ACC             | Production tested at 5mA and 20mA                                                                    | -30                        |      | +30                        | %     |

## **Electrical Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                                               | SYMBOL                  | CONDITIONS                                                                                              | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|-------|

| THERMISTOR MONITOR                                      |                         |                                                                                                         |      |      |      |       |

| THM Threshold, COLD                                     | THM_COLD                | V <sub>THM</sub> /V <sub>PVDD</sub> rising, 1% hysteresis (thermistor temperature falling)              | 73.8 | 75.0 | 76.2 | %     |

| THM Threshold, COOL                                     | THM_COOL                | V <sub>THM</sub> /V <sub>PVDD</sub> rising, 1% hysteresis (thermistor temperature falling)              | 64.3 | 65.5 | 66.7 | %     |

| THM Threshold, WARM                                     | THM_WARM                | V <sub>THM</sub> /V <sub>PVDD</sub> falling, 1% hysteresis (thermistor temperature rising)              | 30.8 | 32.0 | 33.2 | %     |

| THM Threshold, HOT                                      | тнм_нот                 | V <sub>THM</sub> /V <sub>PVDD</sub> falling, 1% hysteresis (thermistor temperature rising)              | 20.8 | 22.0 | 23.2 | %     |

| THM Threshold,<br>Disabled                              | THM_DIS                 | V <sub>THM</sub> /V <sub>PVDD</sub> falling, 1% hysteresis, THM function is disabled below this voltage | 4.8  | 6.0  | 7.2  | %     |

| THM Threshold, Battery Removal Detection                | THM_RM                  | V <sub>THM</sub> /V <sub>PVDD</sub> rising, 1% hysteresis, battery removal                              | 85   | 87   | 89   | %     |

| THM Input Leakage                                       | 1, 1,27, 13,4           | $V_{THM} = V_{AGND}$ or $V_{PVDD}$ , charger disabled, $T_A = +25$ °C                                   |      | 0.1  | 1    | μΑ    |

| Current                                                 | I <sub>LKTHM</sub>      | $V_{THM} = V_{AGND}$ or $V_{PVDD}$ , charger disabled, $T_A = +85$ °C                                   |      | 0.1  |      | μΛ    |

| SUPPLIES AND MONITO                                     | RING                    |                                                                                                         |      |      |      |       |

| VDD Output Voltage                                      | V <sub>VDD_1P8</sub>    | $V_{SYS}$ or $V_{BATT}$ = 3.8V, $I_{VDD}$ = 20mA                                                        | 1.71 | 1.80 | 1.89 | V     |

| SYS Undervoltage-<br>Lockout Threshold (SYS<br>Rising)  | V <sub>SYS_UVLO_R</sub> |                                                                                                         | 2.74 | 2.80 | 2.86 | V     |

| SYS Undervoltage-<br>Lockout Threshold (SYS<br>Falling) | V <sub>SYS_UVLO_F</sub> |                                                                                                         | 2.55 | 2.60 | 2.65 | V     |

| SYS Undervoltage-<br>Lockout Hysteresis                 | V <sub>SYS_UVLO_H</sub> |                                                                                                         |      | 200  |      | mV    |

| SYS Overvoltage-<br>Lockout Threshold (SYS<br>Rising)   | V <sub>SYS_OVLO_R</sub> | SYS rising                                                                                              | 5.2  | 5.35 | 5.5  | V     |

| SYS Overvoltage-<br>Lockout Threshold (SYS<br>Falling)  | V <sub>SYS_OVLO_F</sub> | SYS falling                                                                                             | 5    | 5.15 | 5.3  | V     |

| SYS Overvoltage-<br>Lockout Hysteresis                  | V <sub>SYS_OVLO_H</sub> |                                                                                                         |      | 200  |      | mV    |

| Thermal Shutdown<br>Threshold                           | T <sub>SHDN_R</sub>     | T <sub>j</sub> rising                                                                                   |      | 155  |      | °C    |

| Thermal Shutdown<br>Threshold Hysteresis                | T <sub>SHDN_H</sub>     |                                                                                                         |      | 15   |      | °C    |

| PVDD Output Voltage                                     | V <sub>PVDD_1P8</sub>   | $V_{SYS}$ = 3.8V, $I_{PVDD}$ = 20mA                                                                     | 1.71 | 1.80 | 1.89 | V     |

| I <sup>2</sup> C-COMPATIBLE INTER                       |                         | OR STANDARD, FAST, AND FAST-MODE                                                                        | PLUS |      |      |       |

| Clock Frequency                                         | f <sub>SCL</sub>        |                                                                                                         |      |      | 1000 | kHz   |

| Hold Time (Repeated)<br>START Condition                 | t <sub>HD;STA</sub>     |                                                                                                         | 0.26 |      |      | μs    |

| CLK Low Period                                          | t <sub>LOW</sub>        |                                                                                                         | 0.5  |      |      | μs    |

## **Electrical Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{BATT} = 3.8V, V_{VIO} = 1.8V, V_{CHGIN} = 5V, unless otherwise specified. Limits are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                                                                  | SYMBOL              | CONDITIONS              | MIN  | TYP | MAX  | UNITS |

|----------------------------------------------------------------------------|---------------------|-------------------------|------|-----|------|-------|

| CLK High Period                                                            | tHIGH               |                         | 0.26 |     |      | μs    |

| Set-Up Time Repeated START Condition                                       | tsu;sta             |                         | 0.26 |     |      | μs    |

| DATA Hold Time                                                             | t <sub>HD:DAT</sub> |                         | 0    |     |      | μs    |

| DATA Valid Time                                                            | t <sub>VD:DAT</sub> |                         |      |     | 0.45 | μs    |

| DATA Valid<br>Acknowledge Time                                             | t <sub>VD:ACK</sub> |                         |      |     | 0.45 | μs    |

| DATA Set-Up time                                                           | t <sub>SU;DAT</sub> |                         | 50   |     |      | ns    |

| Set-Up Time for STOP<br>Condition                                          | tsu;sto             |                         | 0.26 |     |      | μs    |

| Bus-Free Time Between STOP and START                                       | t <sub>BUF</sub>    |                         | 0.5  |     |      | μs    |

| Pulse Width of Spikes<br>that must be<br>Suppressed by the Input<br>Filter | t <sub>SP</sub>     |                         |      | 50  |      | ns    |

| I <sup>2</sup> C-COMPATIBLE INTER                                          | FACE TIMING FO      | OR HS-MODE (CB = 100pF) |      |     |      |       |

| Clock Frequency                                                            | f <sub>SCL</sub>    |                         |      |     | 3.4  | MHz   |

| Set-Up Time Repeated START Condition                                       | tsu;sta             |                         | 160  |     |      | ns    |

| Hold Time (Repeated)<br>START Condition                                    | t <sub>HD;STA</sub> |                         | 160  |     |      | ns    |

| CLK Low Period                                                             | t <sub>LOW</sub>    |                         | 160  |     |      | ns    |

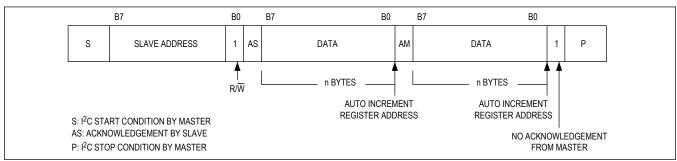

| CLK High Period                                                            | <sup>t</sup> HIGH   |                         | 60   |     |      | ns    |