# 32K x 32 CacheRAM™ 3.3V Synchronous SRAM Burst Counter Single Cycle Deselect

### IDT71V432 OBSOLETE PART

#### **Features**

- 32K x 32 memory configuration

- Supports high-performance system speed: Commercial and Industrial:

- 5ns Clock-to-Data Access (100MHz)

- 6ns Clock-to-Data Access (83MHz)

- Single-cycle deselect functionality (Compatible with Micron Part # MT58LC32K32D7LG-XX)

- **LBO** input selects interleaved or linear burst mode

- Self-timed write cycle with global write control (GW), byte write enable (BWE), and byte writes (BWx)

- Power down controlled by ZZ input

- Operates with a single 3.3V power supply (+10/-5%)

- Packaged in a JEDEC Standard 100-pin rectangular plastic thin quad flatpack (TQFP)

- Green parts available, see ordering information

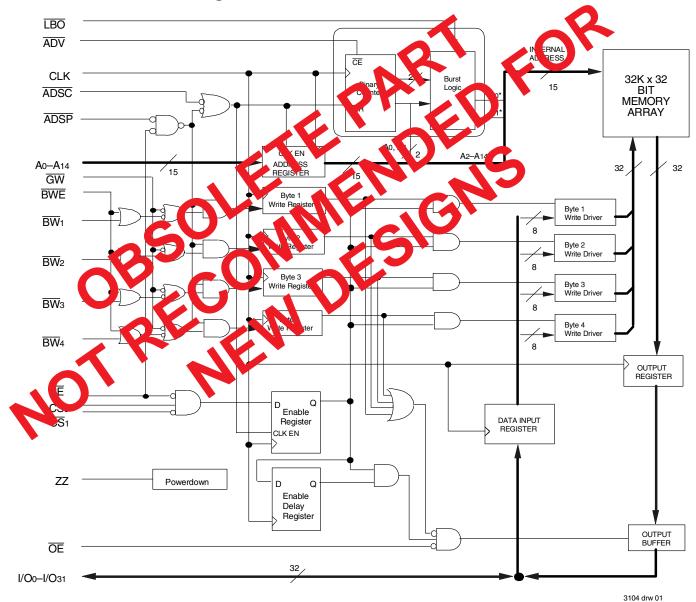

## Functional Block Diagram

OCTOBER 2014

## Description

The IDT71V432 is a 3.3V high-speed 1,048,576-bit CacheRAM organized as 32K x 32 with full support of the Pentium™ and PowerPC™ processor interfaces. The pipelined burst architecture provides cost-effective 3-1-1-1 secondary cache performance for processors up to 100 MHz.

The IDT71V432 CacheRAM contains write, data, address, and control registers. Internal logic allows the CacheRAM to generate a self-timed write based upon a decision which can be left until the extreme end of the write cycle.

The burst mode feature offers the highest level of performance to the system designer, as the IDT71V432 can provide four cycles of data for a single address presented to the

CacheRAM. An internal burst address counter accepts the first cycle address from the processor, initiating the access sequence. The first cycle of output data will be pipelined for one cycle before it is available on the next rising clock edge. If burst mode operation is selected  $(\overline{ADV}=LOW)$ , the subsequent three cycles of output data will be available to the user on the next three rising clock edges. The order of these three addresses will be defined by the internal burst counter and the  $\overline{LBO}$  input pin.

The IDT71V432 CacheRAM utilizes high-performance, high-volume 3.3V CMOS process, and is packaged in a JEDEC Standard 14mm x 20mm 100-pin thin plastic quad flatpack (TQFP) for optimum board density in both desktop and notebook applications.

## Pin Description Summary

| A0-A14               | Address Inputs                    | Input  | Synchronous  |

|----------------------|-----------------------------------|--------|--------------|

| CE                   | Chip Enable                       | Input  | Synchronous  |

| CSo, <del>CS</del> 1 | Chips Selects                     | Input  | Synchronous  |

| ŌĒ                   | Output Enable                     | Input  | Asynchronous |

| GW                   | Global Write Enable               | Input  | Synchronous  |

| BWE                  | Byte Write Enable                 | Input  | Synchronous  |

| BW1, BW2, BW3, BW4   | Individual Byte Write Selects     | Input  | Synchronous  |

| CLK                  | Clock                             | Input  | N/A          |

| ĀDV                  | Burst Address Advance             | Input  | Synchronous  |

| ADSC                 | Address Status (Cache Controller) | Input  | Synchronous  |

| ADSP                 | Address Status (Processor)        | Input  | Synchronous  |

| ĪBO                  | Linear / Interleaved Burst Order  | Input  | DC           |

| ZZ                   | Sleep Mode                        | Input  | Asynchronous |

| I/O0-I/O31           | Data Input/Output                 | I/O    | Synchronous  |

| VDD                  | 3.3V Power                        | Power  | DC           |

| Vss                  | Ground                            | Ground | DC           |

## Pin Definitions<sup>(1)</sup>

| Symbol                                | Pin Function                         | I/O | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------|--------------------------------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A14                                | Address Inputs                       | I   | N/A    | Synchronous Address inputs. The address register is triggered by a combination of the rising edge of CLK and ADSC Low or ADSP Low and CE Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADSC                                  | Address Status<br>(Cache Controller) | -   | LOW    | Synchronous Address Status from Cache Controller. ADSC is an active LOW input that is used to load the address registers with new addresses. ADSC is NOT GATED by CE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ĀDSP                                  | Address Status<br>(Processor)        | I   | LOW    | Synchronous Address Status from Processor. ADSP is an active LOW input that is used to load the address registers with new addresses. ADSP is gated by CE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ĀDV                                   | Burst Address Advance                | _   | LOW    | Synchronous Address Advance. $\overline{\text{ADV}}$ is an active LOW input that is used to advance the internal burst counter, controlling burst access after the initial address is loaded. When this input is HIGH the burst counter is not incremented; that is, there is no address advance.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BWE                                   | Byte Write Enable                    | _   | LOW    | Synchronous byte write enable gates the byte write inputs $\overline{BW}_1-\overline{BW}_4$ . If $\overline{BWE}$ is LOW at the rising edge of CLK then $\overline{BW}_1$ inputs are passed to the next stage in the circuit. A byte write can still be blocked if $\overline{ADSP}$ is LOW at the rising edge of CLK. If $\overline{ADSP}$ is HIGH and $\overline{BW}_1$ is LOW at the rising edge of CLK then data will be written to the SRAM. If $\overline{BWE}$ is HIGH then the byte write inputs are blocked and only $\overline{GW}$ can initiate a write cycle.                                                                                                                                                            |

| $\overline{BW}_1$ - $\overline{BW}_4$ | Individual Byte<br>Write Enables     | _   | LOW    | Synchronous byte write enables. $\overline{BW}_1$ controls $VO(7:0)$ , $\overline{BW}_2$ controls $VO(15:8)$ , etc. Any active byte write causes all outputs to be disabled. $\overline{ADSP}$ LOW disables all byte writes. $\overline{BW}_1$ - $\overline{BW}_4$ must meet specified setup and hold times with respect to CLK.                                                                                                                                                                                                                                                                                                                                                                                                     |

| CE                                    | Chip Enable                          | I   | LOW    | Synchronous chip enable. $\overline{CE}$ is used with CSo and $\overline{CS}$ 1 to enable the IDT71V432. $\overline{CE}$ also gates $\overline{ADSP}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CLK                                   | Clock                                | I   | N/A    | This is the clock input to the IDT71V432. All timing references for the device are made with respect to this input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CS <sub>0</sub>                       | Chip Select 0                        | I   | HIGH   | Synchronous active HIGH chip select. CSo is used with $\overline{CE}$ and $\overline{CS}$ 1 to enable the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ŪS₁                                   | Chip Select 1                        | I   | LOW    | Synchronous active LOW chip select. $\overline{CS}_1$ is used with $\overline{CE}$ and CSo to enable the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GW                                    | Global Write Enable                  | I   | LOW    | Synchronous global write enable. This input will write all four 8-bit data bytes when LOW on the rising edge of CLK. GW supercedes individual byte write enables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I/O0-I/O31                            | Data Input/Output                    | I/O | N/A    | Synchronous data input/output (I/O) pins. Both the data input path and data output path are registered and triggered by the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LBO                                   | Linear Burst Order                   | I   | LOW    | Asynchronous burst order selection DC input. When $\overline{\text{LBO}}$ is HIGH the Interleaved (Intel) burst sequence is selected. When $\overline{\text{LBO}}$ is LOW the Linear (PowerPC) burst sequence is selected. $\overline{\text{LBO}}$ is a static DC input and must not change state while the device is operating.                                                                                                                                                                                                                                                                                                                                                                                                     |

| ŌĒ                                    | Output Enable                        | I   | LOW    | Asynchronous output enable. When $\overline{OE}$ is LOW the data output drivers are enabled on the I/O pins. $\overline{OE}$ is gated internally by a delay circuit driven by $\overline{CE}$ , CSo, and $\overline{CS}$ 1. In dual-bank mode, when the user is utilizing two banks of IDT71V432 and toggling back and forth between them using $\overline{CE}$ , the internal delay circuit delays the $\overline{OE}$ activation of the data output drivers by one cycle to prevent bus contention between the banks. When used in single bank mode $\overline{CE}$ , CSo, and $\overline{CS}$ 1 are all tied active and there is no output enable delay. When $\overline{OE}$ is HIGH the I/O pins are in a high-impedence state. |

| VDD                                   | Power Supply                         | N/A | N/A    | 3.3V power supply inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Vss                                   | Ground                               | N/A | N/A    | Ground pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ZZ                                    | Sleep Mode                           | I   | HIGH   | Asynchronous sleep mode input. ZZ HIGH will gate the CLK internally and power down the IDT71V432 to its lowest power consumption level. Data retention is guaranteed in Sleep Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

NOTE:

<sup>1.</sup> All synchronous inputs must meet specified setup and hold times with respect to CLK.

## Absolute Maximum Ratings(1)

| Symbol               | Rating                               | Value           | Unit |

|----------------------|--------------------------------------|-----------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage with Respect to GND | -0.5 to +4.6    | V    |

| VTERM <sup>(3)</sup> | Terminal Voltage with Respect to GND | -0.5 to VDD+0.5 | V    |

| Та                   | Operating Temperature                | 0 to +70        | °C   |

| TBIAS                | Temperature Under Bias               | -55 to +125     | °C   |

| Tstg                 | Storage Temperature                  | -55 to +125     | °C   |

| Рт                   | Power Dissipation                    | 1.0             | W    |

| Гоит                 | DC Output Current                    | 50              | mA   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. VDD and Input terminals only.

- 3. I/O terminals.

## Recommended Operating Temperature and Supply Voltage

| Grade Temperature |                | Vss | <b>V</b> DD |

|-------------------|----------------|-----|-------------|

| Commercial        | 0°C to +70°C   | 0V  | 3.3V+10/-5% |

| Industrial        | –40°C to +85°C | 0V  | 3.3V+10/-5% |

3104 tbl 03

## Recommended DC Operating Conditions

| Symbol | Parameter                   | Min.                | Тур. | Max.               | Unit |

|--------|-----------------------------|---------------------|------|--------------------|------|

| VDD    | Supply Voltage              | 3.135               | 3.3  | 3.63               | V    |

| Vss    | Ground                      | 0                   | 0    | 0                  | V    |

| V⊪     | Input High Voltage — Inputs | 2.0                 | -    | 4.6 <sup>(2)</sup> | V    |

| V⊪     | Input High Voltage — I/O    | 2.0                 | _    | VDD+0.3            | V    |

| VIL    | Input Low Voltage           | -0.5 <sup>(1)</sup> | _    | 0.8                | V    |

#### 3104 tbl 04

#### NOTES:

- 1.  $V_{IL}$  (min) = -1.0V for pulse width less than tcyc/2, once per cycle.

- 2. Vih (max) = 6.0V for pulse width less than tcyc/2, once per cycle.

### Capacitance

$(TA = +25^{\circ}C, f = 1.0MHz, TQFP package)$

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| CIN    | Input Capacitance        | VIN = 3dV  | 6    | pF   |

| Ci/o   | I/O Capacitance          | Vout = 3dV | 7    | pF   |

#### 3104 tbl 06

3104 tbl 05

This parameter is guaranteed by device characterization, but not production tested.

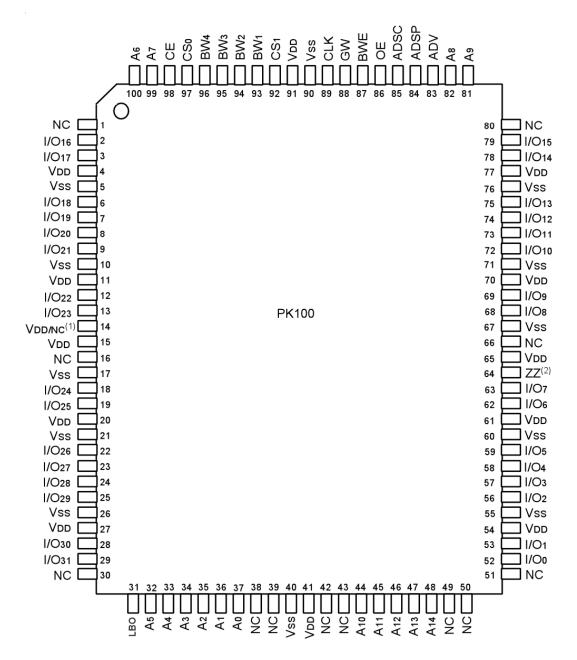

## Pin Configuration

3104 drw 02

## Top View TQFP

#### NOTES:

- 1. Pin 14 can either be directly connected to VDD or not connected.

- 2. Pin 64 can be left unconnected and the device will always remain in active mode.

## Synchronous Truth Table<sup>(1,2)</sup>

| Operation                    | Address<br>Used | CE | CS <sub>0</sub> | <del>CS</del> 1 | ADSP | ADSC | ADV | Ū₩ | BWE | <b>BW</b> x | ŌĒ <sup>(3)</sup> | CLK        | I/O  |

|------------------------------|-----------------|----|-----------------|-----------------|------|------|-----|----|-----|-------------|-------------------|------------|------|

| Deselected Cycle, Power Down | None            | Н  | Χ               | Χ               | Χ    | L    | Χ   | Χ  | Χ   | Χ           | Χ                 | 1          | Hi-Z |

| Deselected Cycle, Power Down | None            | L  | Χ               | Н               | L    | Χ    | Χ   | Χ  | Χ   | Х           | Χ                 | 1          | Hi-Z |

| Deselected Cycle, Power Down | None            | L  | L               | Χ               | L    | Χ    | Х   | Χ  | Χ   | Х           | Χ                 | 1          | Hi-Z |

| Deselected Cycle, Power Down | None            | L  | Х               | Н               | Х    | L    | Х   | Χ  | Χ   | Х           | Х                 | 1          | Hi-Z |

| Deselected Cycle, Power Down | None            | L  | L               | Χ               | Χ    | L    | Х   | Χ  | Χ   | Х           | Χ                 | 1          | Hi-Z |

| Read Cycle, Begin Burst      | External        | L  | Н               | L               | L    | Χ    | Х   | Χ  | Χ   | Х           | L                 | 1          | Dout |

| Read Cycle, Begin Burst      | External        | L  | Н               | L               | L    | Χ    | Х   | Х  | Х   | Х           | Н                 | 1          | Hi-Z |

| Read Cycle, Begin Burst      | External        | L  | Н               | L               | Н    | L    | Х   | Н  | Н   | Х           | L                 | 1          | Dout |

| Read Cycle, Begin Burst      | External        | L  | Н               | L               | Н    | L    | Х   | Н  | L   | Н           | L                 | 1          | Dout |

| Read Cycle, Begin Burst      | External        | L  | Н               | L               | Н    | L    | Χ   | Н  | L   | Н           | Н                 | 1          | Hi-Z |

| Write Cycle, Begin Burst     | External        | L  | Н               | L               | Н    | L    | Χ   | Н  | L   | L           | Χ                 | 1          | Din  |

| Write Cycle, Begin Burst     | External        | L  | Н               | L               | Н    | L    | Х   | L  | Х   | Х           | Х                 | <b>↑</b>   | DIN  |

| Read Cycle, Continue Burst   | Next            | Χ  | Х               | Χ               | Н    | Н    | L   | Н  | Н   | Х           | L                 | <b>↑</b>   | Dout |

| Read Cycle, Continue Burst   | Next            | Χ  | Χ               | Χ               | Н    | Ι    | L   | Ι  | Ι   | Х           | Н                 | $\uparrow$ | Hi-Z |

| Read Cycle, Continue Burst   | Next            | Χ  | Х               | Χ               | Н    | Η    | L   | Ι  | Χ   | Н           | L                 | $\uparrow$ | Dout |

| Read Cycle, Continue Burst   | Next            | Χ  | Х               | Χ               | Н    | Η    | L   | Η  | Χ   | Н           | Н                 | <b>↑</b>   | Hi-Z |

| Read Cycle, Continue Burst   | Next            | Н  | Х               | Х               | Х    | Η    | L   | Η  | Н   | Х           | L                 | $\uparrow$ | Dout |

| Read Cycle, Continue Burst   | Next            | Н  | Х               | Х               | Х    | Η    | L   | Η  | Н   | Х           | Н                 | <b>↑</b>   | Hi-Z |

| Read Cycle, Continue Burst   | Next            | Н  | Χ               | Χ               | Χ    | Н    | L   | Н  | Χ   | Н           | L                 | <b>↑</b>   | Dout |

| Read Cycle, Continue Burst   | Next            | Н  | Χ               | Х               | Χ    | Н    | L   | Н  | Χ   | Н           | Н                 | <b>↑</b>   | Hi-Z |

| Write Cycle, Continue Burst  | Next            | Χ  | Χ               | Χ               | Н    | Н    | L   | Н  | L   | L           | Χ                 | 1          | Din  |

| Write Cycle, Continue Burst  | Next            | Χ  | Χ               | Χ               | Н    | Н    | L   | L  | Χ   | Χ           | Χ                 | 1          | DIN  |

| Write Cycle, Continue Burst  | Next            | Н  | Χ               | Χ               | Χ    | Н    | L   | Н  | L   | L           | Χ                 | 1          | DIN  |

| Write Cycle, Continue Burst  | Next            | Н  | Χ               | Χ               | Χ    | Н    | L   | L  | Χ   | Х           | Χ                 | 1          | Din  |

| Read Cycle, Suspend Burst    | Current         | Χ  | Χ               | Χ               | Н    | Н    | Н   | Н  | Н   | Х           | L                 | 1          | Dout |

| Read Cycle, Suspend Burst    | Current         | Χ  | Χ               | Χ               | Н    | Н    | Н   | Н  | Н   | Х           | Н                 | 1          | Hi-Z |

| Read Cycle, Suspend Burst    | Current         | Χ  | Χ               | Χ               | Н    | Н    | Н   | Н  | Χ   | Н           | L                 | 1          | Dout |

| Read Cycle, Suspend Burst    | Current         | Χ  | Χ               | Χ               | Н    | Н    | Н   | Н  | Χ   | Н           | Н                 | 1          | Hi-Z |

| Read Cycle, Suspend Burst    | Current         | Н  | Χ               | Χ               | Χ    | Н    | Н   | Н  | Н   | Χ           | L                 | 1          | Dout |

| Read Cycle, Suspend Burst    | Current         | Н  | Χ               | Χ               | Χ    | Н    | Н   | Н  | Н   | Х           | Н                 | 1          | Hi-Z |

| Read Cycle, Suspend Burst    | Current         | Н  | Х               | Х               | Χ    | Η    | Н   | Н  | Χ   | Н           | L                 | <b>↑</b>   | Dout |

| Read Cycle, Suspend Burst    | Current         | Н  | Х               | Х               | Х    | Н    | Н   | Н  | Χ   | Н           | Н                 | 1          | Hi-Z |

| Write Cycle, Suspend Burst   | Current         | Х  | Х               | Х               | Н    | Η    | Н   | Н  | L   | L           | Χ                 | <b>↑</b>   | DIN  |

| Write Cycle, Suspend Burst   | Current         | Χ  | Χ               | Χ               | Н    | Н    | Н   | L  | Χ   | Х           | Χ                 | <b>↑</b>   | DIN  |

| Write Cycle, Suspend Burst   | Current         | Н  | Х               | Χ               | Χ    | Η    | Н   | Н  | L   | L           | Χ                 | <b>↑</b>   | Din  |

| Write Cycle, Suspend Burst   | Current         | Н  | Χ               | Χ               | Χ    | Н    | Н   | ┙  | Х   | Х           | Х                 | $\uparrow$ | DIN  |

#### NOTES:

1. L = VIL, H = VIH, X = Don't Care.

2. ZZ = LOW for this table.

3.  $\overline{\text{OE}}$  is an asynchronous input.

## Synchronous Write Function Truth Table<sup>(1)</sup>

| Operation                   | GW | BWE | <b>BW</b> ₁ | BW₂ | <b>BW</b> ₃ | BW <sub>4</sub> |

|-----------------------------|----|-----|-------------|-----|-------------|-----------------|

| Read                        | Н  | Н   | Х           | Х   | Х           | Х               |

| Read                        | Н  | L   | Н           | Н   | Н           | Н               |

| Write all Bytes             | L  | Х   | Х           | Х   | Х           | Х               |

| Write all Bytes             | Н  | L   | L           | L   | L           | L               |

| Write Byte 1 <sup>(2)</sup> | Н  | L   | L           | Н   | Н           | Н               |

| Write Byte 2 <sup>(2)</sup> | Н  | L   | Н           | L   | Н           | Н               |

| Write Byte 3 <sup>(2)</sup> | Н  | L   | Н           | Н   | L           | Н               |

| Write Byte 4 <sup>(2)</sup> | Н  | L   | Н           | Н   | Н           | L               |

NOTES:

3104 tbl 08

- 1. L = VIL, H = VIH, X = Don't Care.

- 2. Multiple bytes may be selected during the same cycle.

## Asynchronous Truth Table<sup>(1)</sup>

| Operation <sup>(2)</sup> |   | I/O Status | Power                                                    |         |

|--------------------------|---|------------|----------------------------------------------------------|---------|

| Read                     | L | L,         | Data Out (I/Oo - I/O31)                                  | Active  |

| Read                     | Н | L          | High-Z                                                   | Active  |

| Write                    | Х | L,         | High-Z — Data In (I/O <sub>0</sub> - I/O <sub>31</sub> ) | Active  |

| Deselected               | Х | L,         | High-Z                                                   | Standby |

| Sleep                    | Х | Н          | High-Z                                                   | Sleep   |

NOTES: 3104 tbl 09

- 1. L = VIL, H = VIH, X = Don't Care.

- 2. Synchronous function pins must be biased appropriately to satisfy operation requirements.

## Interleaved Burst Sequence Table (**LBO**=VDD)

|                               | Sequence 1 | Sequence 2 | Sequence 3 | Sequence 4 |

|-------------------------------|------------|------------|------------|------------|

|                               | A1 A0      | A1 A0      | A1 A0      | A1 A0      |

| First Address                 | 0 0        | 0 1        | 1 0        | 1 1        |

| Second Address                | 0 1        | 0 0        | 1 1        | 1 0        |

| Third Address                 | 1 0        | 1 1        | 0 0        | 0 1        |

| Fourth Address <sup>(1)</sup> | 1 1        | 1 0        | 0 1        | 0 0        |

NOTE

3104 tbl 10

## Linear Burst Sequence Table (**LBO**=Vss)

|                               | Sequence 1 |    | Sequ | Sequence 2 |    | Sequence 3 |    | ence 4 |

|-------------------------------|------------|----|------|------------|----|------------|----|--------|

|                               | A1         | A0 | A1   | A0         | A1 | A0         | A1 | A0     |

| First Address                 | 0          | 0  | 0    | 1          | 1  | 0          | 1  | 1      |

| Second Address                | 0          | 1  | 1    | 0          | 1  | 1          | 0  | 0      |

| Third Address                 | 1          | 0  | 1    | 1          | 0  | 0          | 0  | 1      |

| Fourth Address <sup>(1)</sup> | 1          | 1  | 0    | 0          | 0  | 1          | 1  | 0      |

NOTE:

<sup>1.</sup> Upon completion of the Burst sequence the counter wraps around to its initial state.

<sup>1.</sup> Upon completion of the Burst sequence the counter wraps around to its initial state.

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 3.3V +10/-5%, Commercial and Industrial Temperature Ranges)

| Symbol | Parameter                                       | Test Conditions                                                                                                            | Min. | Max. | Unit |

|--------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Iu     | Input Leakage Current                           | VDD = Max., VIN = 0V to VDD                                                                                                |      | 5    | μΑ   |

| ILI    | ZZ and LBO Input Leakage Current <sup>(1)</sup> | VDD = Max., VIN = 0V to VDD                                                                                                |      | 30   | μΑ   |

| ILO    | Output Leakage Current                          | $\overline{\text{CE}} \ge \text{Vih or } \overline{\text{OE}} \ge \text{Vih, Vout} = 0 \text{V to Vdd, Vdd} = \text{Max.}$ | ĺ    | 5    | μΑ   |

| Vol    | Output Low Voltage (I/O1-I/O31)                 | IOL = 5mA, VDD = Min.                                                                                                      |      | 0.4  | V    |

| Vон    | Output High Voltage (I/O1-I/O31)                | IOH = -5mA, VDD = Min.                                                                                                     | 2.4  | _    | V    |

#### NOTE:

3104 tbl 12

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1)</sup> (VDD = 3.3V +10/-5%, VHD = VDD-0.2V, VLD = 0.2V)

|        |                                                                                                                         |                                                                                             | IDT71V432S5 |      | IDT71V432S6 |      |      |

|--------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------|------|-------------|------|------|

| Symbol | Parameter                                                                                                               | Test Conditions                                                                             | Com'l.      | Ind. | Com'l.      | Ind. | Unit |

| IDD    | Operating Power Supply Current                                                                                          | Device Selected, Outputs Open, VDD = Max., VIN $\geq$ VIH or $\leq$ VIL, f = fMAX $^{(2)}$  | 200         | 200  | 180         | 180  | mA   |

| Isb    | Standby Power Supply Current                                                                                            | Device Deselected, Outputs Open, $VDD = Max$ ., $VIN \ge VIH Or \le VIL$ , $f = fMAX^{(2)}$ | 65          | 65   | 60          | 60   | mA   |

| ISB1   | Full Standby Power Supply Current Device Deselected, Outputs Open, VDD = Max $VIN \ge VHD$ or $\le VLD$ , $f = 0^{(2)}$ |                                                                                             | 15          | 15   | 15          | 15   | mA   |

| Izz    | Full Sleep Mode Power Supply Current                                                                                    | $ZZ \ge VHD$ , $VDD = Max$ .                                                                | 10          | 10   | 10          | 10   | mA   |

#### NOTES:

3104 tbl 13a

- 1. All values are maximum guaranteed values.

- 2. At f = fmax, inputs are cycling at the maximum frequency of read cycles of 1/tcvc while ADSC = LOW; f=0 means no input lines are changing.

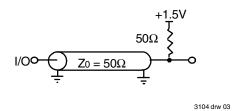

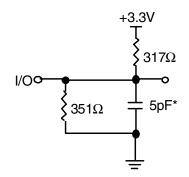

#### **AC Test Loads**

Figure 1. AC Test Load

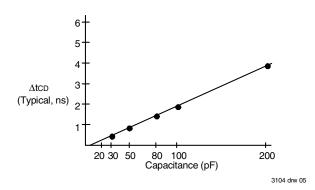

Figure 3. Lumped Capacitive Load, Typical Derating

\* Including scope and jig capacitance.

3104 drw 04

Figure 2. AC Test Load (for tohz, tchz, tolz, and toc1)

#### AC Test Conditions

| 7.6 1631 661141116113          |                     |  |  |  |

|--------------------------------|---------------------|--|--|--|

| Input Pulse Levels             | 0 to 3.0V           |  |  |  |

| Input Rise/Fall Times          | 2ns                 |  |  |  |

| Input Timing Reference Levels  | 1.5V                |  |  |  |

| Output Timing Reference Levels | 1.5V                |  |  |  |

| AC Test Load                   | See Figures 1 and 2 |  |  |  |

<sup>1.</sup> The LBO pin will be internally pulled to Vpp if it is not actively driven in the application and the ZZ pin will be internally pulled to Vps if not actively driven.

AC Electrical Characteristics (VDD = 3.3V +10/-5%, Commercial and Industrial Temperature Ranges)

| (VDD = 3.3 V                    | / +10/-5%, Commercial and Industr | 71V432S5 71V432S6 |          |          |      |      |

|---------------------------------|-----------------------------------|-------------------|----------|----------|------|------|

| Symbol                          | Parameter                         | Min.              | Max.     | Min.     | Max. | Unit |

| CLOCK PARAN                     | <br>IETERS                        | <u>I</u>          | <u> </u> | <u> </u> |      |      |

| tcyc                            | Clock Cycle Time                  | 10                | _        | 12       |      | ns   |

| tcH <sup>(1)</sup>              | Clock High Pulse Width            | 4                 | _        | 4.5      | _    | ns   |

| tcL <sup>(1)</sup>              | Clock Low Pulse Width             | 4                 | _        | 4.5      |      | ns   |

| OUTPUT PARA                     | METERS                            | •                 | •        | •        |      | •    |

| tcD                             | Clock High to Valid Data          |                   | 5        |          | 6    | ns   |

| tcdc                            | Clock High to Data Change         | 1.5               | _        | 2        |      | ns   |

| tclz <sup>(2)</sup>             | Clock High to Output Active       | 0                 | _        | 0        |      | ns   |

| tснz <sup>(2)</sup>             | Clock High to Data High-Z         | 1.5               | 5        | 2        | 5    | ns   |

| toe                             | Output Enable Access Time         |                   | 5        |          | 5    | ns   |

| tolz <sup>(2)</sup>             | Output Enable Low to Data Active  | 0                 | _        | 0        |      | ns   |

| tонz <sup>(2)</sup>             | Output Enable High to Data High-Z |                   | 4        |          | 5    | ns   |

| SETUP TIMES                     | •                                 |                   |          |          |      |      |

| tsa                             | Address Setup Time                | 2.5               | _        | 2.5      | _    | ns   |

| tss                             | Address Status Setup Time         | 2.5               | _        | 2.5      | _    | ns   |

| tsd                             | Data in Setup Time                | 2.5               | _        | 2.5      | _    | ns   |

| tsw                             | Write Setup Time                  | 2.5               | _        | 2.5      | _    | ns   |

| tsav                            | Address Advance Setup Time        |                   | _        | 2.5      | _    | ns   |

| tsc                             | Chip Enable/Select Setup Time     |                   | _        | 2.5      |      | ns   |

| HOLD TIMES                      |                                   |                   |          |          |      |      |

| tна                             | Address Hold Time                 | 0.5               | _        | 0.5      | _    | ns   |

| ths                             | Address Status Hold Time          | 0.5               | _        | 0.5      | _    | ns   |

| thd                             | Data In Hold Time                 | 0.5               | _        | 0.5      | _    | ns   |

| thw                             | Write Hold Time                   | 0.5               | _        | 0.5      | _    | ns   |

| THAV                            | Address Advance Hold Time         | 0.5               | _        | 0.5      | _    | ns   |

| HC Chip Enable/Select Hold Time |                                   | 0.5               | _        | 0.5      | _    | ns   |

| SLEEP MODE A                    | AND CONFIGURATION PARAMETERS      |                   |          |          |      |      |

| tzzpw                           | ZZ Pulse Width                    | 100               | _        | 100      | _    | ns   |

| tzzr <sup>(3)</sup>             | ZZ Recovery Time                  | 100               | _        | 100      |      | ns   |

| tcfg <sup>(4)</sup>             | Configuration Set-up Time         | 40                | _        | 50       |      | ns   |

3104 tbl 15a

#### NOTES:

- 1. Measured as HIGH above 2.0V and LOW below 0.8V.

- 2. Transition is measured  $\pm 200 \text{mV}$  from steady-state.

- 3. Device must be deselected when powered-up from sleep mode.

- 4. tcrs is the minimum time required to configure the device based on the  $\overline{LBO}$  input.  $\overline{LBO}$  is a static input and must not change during normal operation.

3104 drw 06

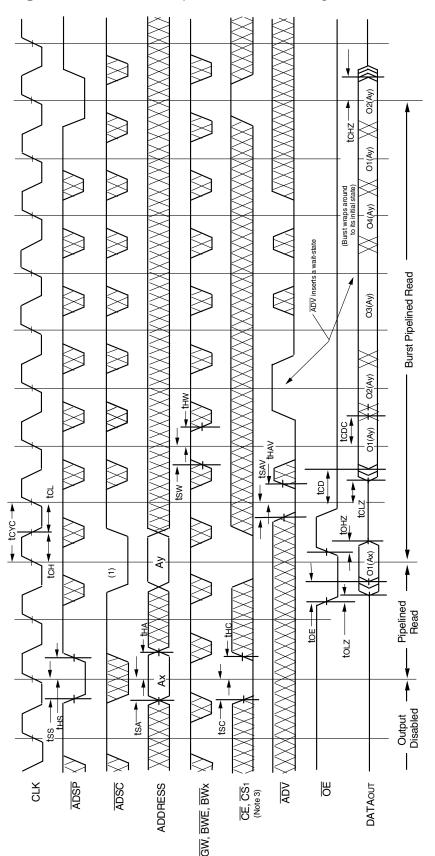

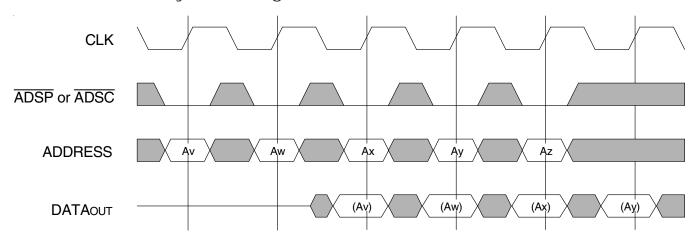

## Timing Waveform of Pipelined Read Cycle<sup>(1,2)</sup>

- 1. O1 (Ax) represents the first output from the external address Ax. O1 (Ay) represents the first output from the external address Ay; O2 (Ay) represents the next output data in the burst sequence of the base address Ay, etc. where Ao and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input.

2. ZZ input is LOW and LBO is Don't Care for this cycle.

3. CSO timing transitions are identical but inverted to the CE and CS1 signals. For example, when CE and CS1 are LOW on this waveform, CS0 is HIGH.

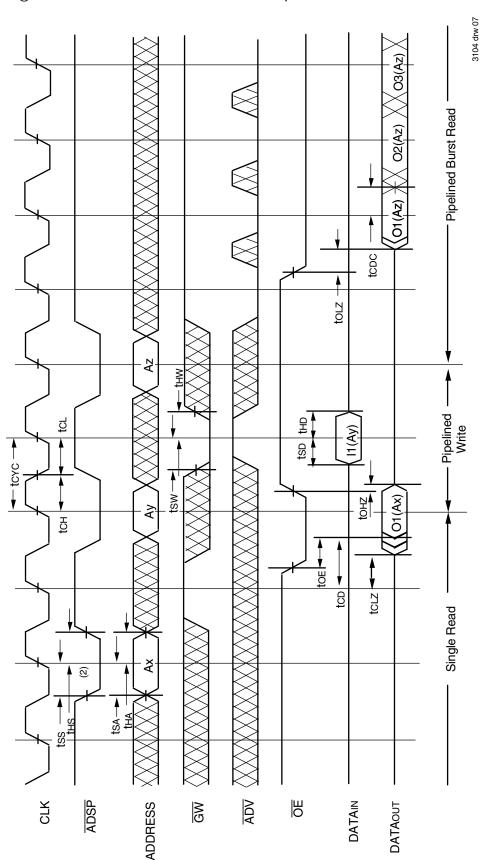

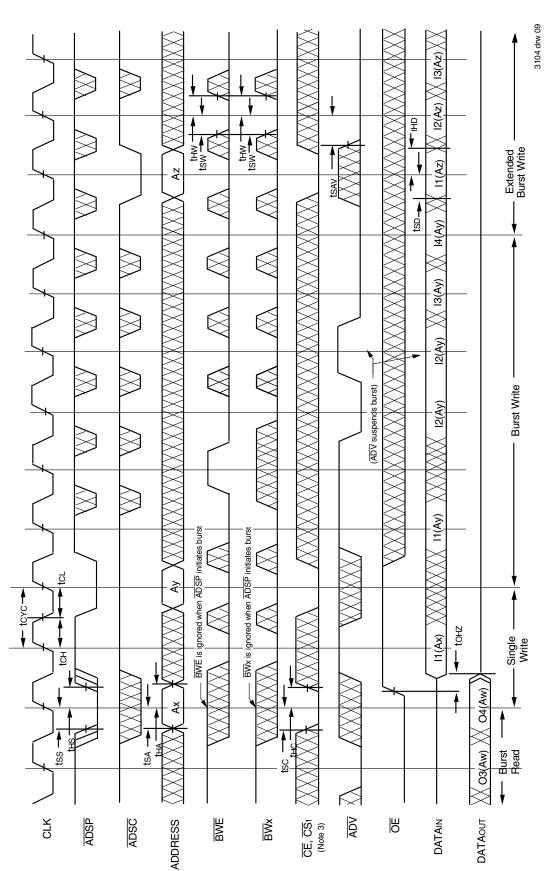

## Timing Waveform of Combined Pipelined Read and Write Cycles (1,2,3)

1. Device is selected through entire cycle: <u>OE</u> and <u>OS</u>1 are LOW, CS0 is HIGH.

2. ZZ input is LOW and <u>LBO</u> is Don't Care for this cycle.

3. O1(Ax) represents the first output from the external address Ax. I1 (Ax) represents the first input from the external address Az, O2(Az) represents the next output data in the burst sequence of the base address Az, etc. where Ao and A1 are advancing for the four word burst in the sequence defined by the state of the <u>LBO</u> input.

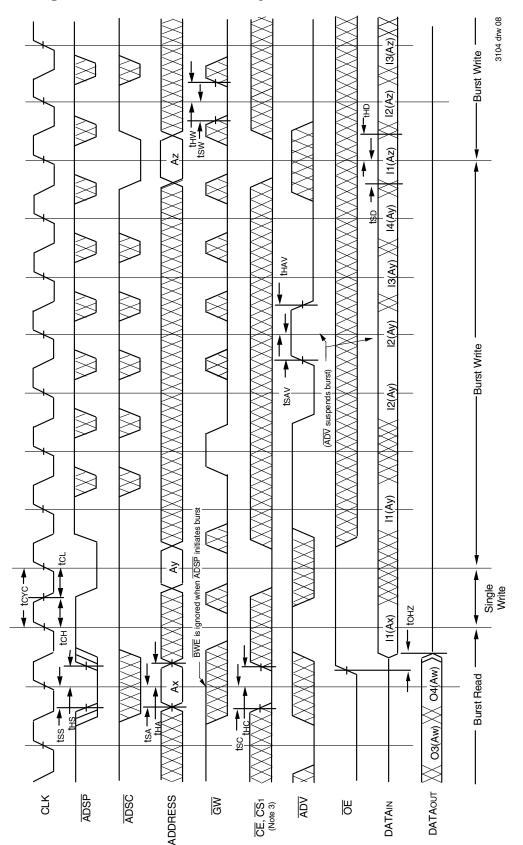

## Timing Waveform of Write Cycle No. 1 — $\overline{\textbf{GW}}$ Controlled<sup>(1,2,3)</sup>

NOTES:

- 1. ZZ input is LOW, BWE is HIGH, and LBO is Don't Care for this cycle.

- O4(Aw) represents the final output data in the burst sequence of the base address Aw. 11(Ax) represents the first input from the external address Ax. 11(Ay) represents the first input from the external address Ay; I2(Ay) represents the next input data in the burst sequence of the base address Ay, etc. where A0 and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input. In the case of input I2(Ay) this data is valid for two cycles because ADV is high and has suspended the burst.

CSo timing transitions are identical but inverted to the CE and CS1 signals. For example, when CE and CS1 are LOW on this waveform, CS0 is HIGH.

- 3

## Timing Waveform of Write Cycle No. 2 — Byte Controlled<sup>(1,2,3)</sup>

- ZZ input is LOW, GW is HIGH, and LBO is Don't Care for this cycle.

O4(Aw) represents the final output data in the burst sequence of the base address Aw. I1(Ax) represents the first input from the external address Ax. I1(Ay) represents the next input data in the burst sequence of the base address Ay, etc. where Ao and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input. In the case of input I2(Ay) this data is valid for two cycles because ADV is high and has suspended the burst.

CSO timing transitions are identical but inverted to the CE and CS1 signals. For example, when CE and CS1 are LOW on this waveform, CS0 is HIGH.

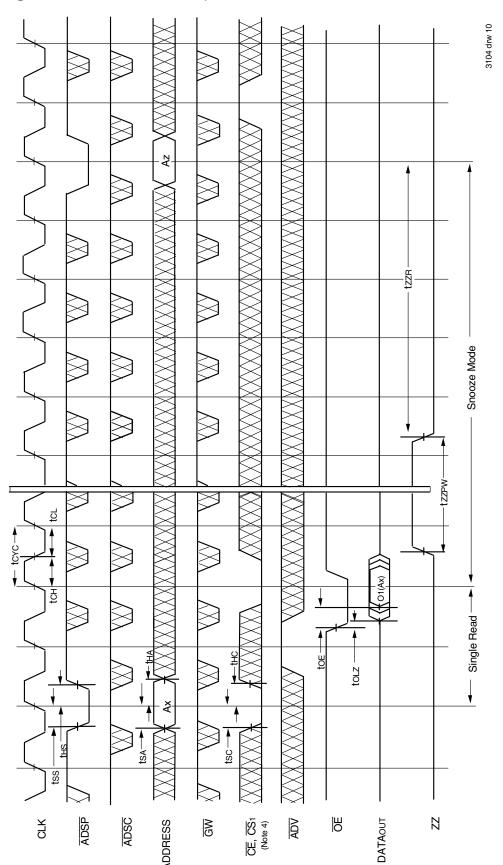

## Timing Waveform of Sleep (ZZ) and Power-Down Modes (1,2,3)

Device must power up in deselected Mode.

LBO input is Don't Care for this cycle.

It is not necessary to retain the state of the input registers throughout the Power-down cycle.

CS0 timing transitions are identical but inverted to the \(\overline{\text{CE}}\) and \(\overline{\text{SS}}\) and \(\overline{\text{CS}}\) are LOW on this waveform, CS0 is HIGH.

## Non-Burst Read Cycle Timing Waveform (1,2,3,4)

3104 drw 11

#### NOTES:

- 1. ZZ,  $\overline{CE}$ ,  $\overline{CS}_1$ , and  $\overline{OE}$  are LOW for this cycle.

- 2.  $\overline{ADV}$ ,  $\overline{GW}$ ,  $\overline{BWE}$ ,  $\overline{BWx}$ , and CSo are HIGH for this cycle.

- 3. (Ax) represents the data for address Ax, etc.

- 4. For read cycles, ADSP and ADSC function identically and are therefore interchangeable.

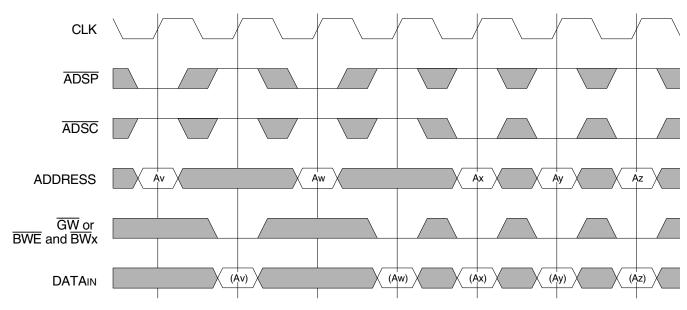

## Non-Burst Write Cycle Timing Waveform (1,2,3,4)

3104 drw 12

#### NOTES:

- 1. ZZ,  $\overline{\text{CE}}$  and  $\overline{\text{CS}}_1$  are LOW for this cycle.

- 2. ADV, OE and CSo are HIGH for this cycle.

- 3. (Ax) represents the data for address Ax, etc.

- 4. For write cycles, ADSP and ADSC have different limitations.

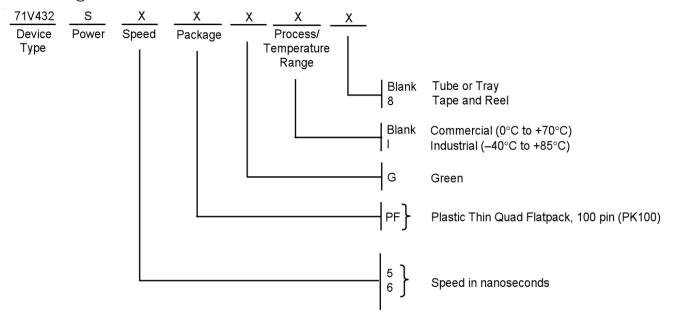

## Ordering Information

| PART NUMBER | SPEED IN MEGAHERTZ | tcd PARAMETER | CLOCK CYCLE TIME |

|-------------|--------------------|---------------|------------------|

| 71V432S5PF  | 100 MHz            | 5 ns          | 10 ns            |

| 71V432S6PF  | 83 MHz             | 6 ns          | 12 ns            |

3104 drw 13

## **Datasheet Document History**

| 9/10/99  |                    | Updated to new format                                                                            |

|----------|--------------------|--------------------------------------------------------------------------------------------------|

|          | Pg. 3-5            | Adjusted page layout, added extra page                                                           |

|          | Pg. 5              | Added notes to pin configuration                                                                 |

|          | Pg. 11–14          | Revised notes                                                                                    |

|          | Pg. 17             | Added Datasheet Document History                                                                 |

| 03/09/00 | Pg. 1, 4, 8, 9, 16 | Added Industrial temperature range offerings                                                     |

| 04/04/00 | Pg. 16             | Added 100pinTQFP package Diagram Outline                                                         |

| 08/09/00 |                    | Added "Not recommended for new designs"                                                          |

| 08/17/01 |                    | Removed "Not recommended for new designs" from the background on the datasheet                   |

| 03/31/05 | Pg. 17             | Added RoHS "Restricted Hazardous Substance Device" to ordering information                       |

| 08/01/14 | Pg. 1-3            | Moved the FBD, the pin description and pin definition tables to pages 1 - 3 respectively to      |

|          |                    | align the datasheet reading flow to that of our other established datasheets                     |

|          | Pg. 17             | In the Ordering Information, Tape & Reel added & RoHS designation changed to Green               |

| 10/03/14 | Pg. 1              | Removed 7ns Clock-to-Data Access (66MHz). and added green availability in Features               |

|          | Pg. 1-2            | Moved notes regarding IDT's use of the CacheRAM, the Pentium processor & the PowerPC terminology |

|          | Pg. 2              | Removed the reference to IDT with regards to the CMOS process                                    |

|          | Pg. 5              | The package code PK100-1 changed to PK100 to match standard package codes                        |

|          | Pg. 8              | Removed IDT71V432S7 speed grade offering in the DC Chars table                                   |

|          | Pg. 9              | Removed 71V432S7 speed grade offering in the AC Chars table                                      |

|          | Pg. 16             | Removed TQFP Package Diagram Outline                                                             |

|          | <b>J</b>           | In the Ordering Information, PK100-1 package code changed to PK100 and 7ns speed                 |

|          |                    | grade was removed                                                                                |

|          | Pg. 17             | Updated Customer's SRAM Tech Support phone number and email address                              |

| 03/16/22 | 5                  | 71V432 Datasheet changed to Obsolete status                                                      |

|          |                    |                                                                                                  |

CORPORATE HEADQUARTERS 6024 Silver Creek Valley Road San Jose, CA 95138 for SALES: 800-345-7015 or 408-284-8200 fax: 408-284-277

408-284-4532 sramhelp@idt.com

for Tech Support:

fax: 408-284-2775 www.idt.com

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/