ASNT5012-PQC is available on two evaluation boards: one with negative supply and one with positive supply. Application notes for these two evaluation boards are presented in order of:

- Negative supply on ASNT05\_12

- Positive supply on ASNT05\_11

By default, ADSANTEC will ship the positive supply evaluation board. Please send us a message through the DigiKey marketplace website if you would like to receive the negative supply version.

The datasheet for ASNT5012-PQC can be accessed through the following LINK.

Rev. 1.0.1 1 September 2020

# ASNT5012-PQC on ASNT05\_12 Evaluation Board DC-17Gbps High Sensitivity D-Type Flip-Flop Application Note

### **Part Description**

The ASNT5012-PQC high sensitivity D-type flip-flop accepts a broadband data signal at its differential input port dp/dn and delivers a retimed version of it to its differential output port outp/outn. Retiming of the input data is accomplished by applying a full rate input clock signal to the differential input port cp/cn.

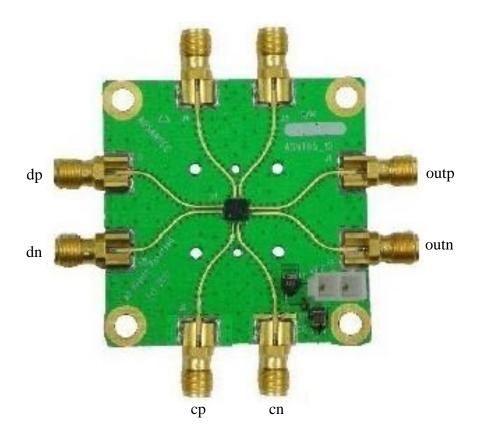

The part is mounted on an ASNT05\_12 evaluation board with 50*Ohm* transmission lines to transfer signals to/from the chip to 6 high-speed edge-mount female connectors (Southwest or similar) as shown in Fig. 1. The board has a MOLEX connector for the power supply, as well as signal filters, supply filters, and decoupling networks. The board measures approximately 2.0x2.0 inches, without connectors.

Fig. 1. Layout of ASNT05\_12 PCB

The signal and power connectors are described in Table 1 and Table 2 below.

Table 1. Signal Connectors

| Name   | Name    | Signal description                                              | Signal   | I/O type |

|--------|---------|-----------------------------------------------------------------|----------|----------|

| on PCB | on Chip |                                                                 | polarity |          |

| J7     | dp      | Differential data inputs with internal SE 50 <i>Ohm</i>         | Direct   | CML      |

| J8     | dn      | termination to VCC                                              | Inverted | input    |

| J1     | outp    | Differential outputs with internal SE 50 <i>Ohm</i> termination | Direct   | CML      |

| J2     | outn    | to VCC; require external SE 50 <i>Ohm</i> termination to VCC    | Inverted | output   |

| J6     | ср      | Differential clock inputs with internal SE 50 <i>Ohm</i>        | Direct   | CML      |

| J5     | cn      | termination to VCC                                              | Inverted | input    |

Table 2. Power Supply Connectors

| Name on PCB | Name on Chip | Supply type                | Supply voltage, V |

|-------------|--------------|----------------------------|-------------------|

| GND         | vcc          | External ground            | 0                 |

| VEE         | vee          | Main negative power supply | -3.3              |

### **Initial Setup and Basic Functionality**

- 1. The part is static sensitive. Please observe anti-static protection procedures!

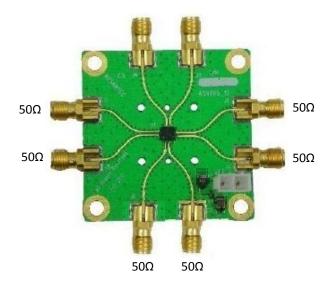

- 2. Measure the resistance of all connector pins to VCC, including the power supply, while making sure the board is grounded. All I/O ports should measure 50*Ohms* while on the power supply connector, VEE should be high impedance and GND should be a short. Fig. 2 shows the resistance values of the described I/O connectors.

Fig. 2. Impedance of I/O Connectors

Rev. 1.0.1 3 September 2020

- 3. Switch on the first external power supply unit and set it to a negative supply voltage with a value of 0.0V (positive output pin of the unit must be shorted to ground).

- 4. Connect the supply unit's output pins to the PCB's Molex connector marked VEE GND so that the negative output pin is connected to VEE connector pin.

- 5. Gradually increase the negative supply voltage to -3.3V.

- 6. Monitor the supply current in accordance with the part's specifications. Current should be approximately 140mA.

- 7. Apply a differential or SE high-speed data signal to connectors J7/J8. DC blocks or the appropriate shift of voltage levels may be required!

- 8. Apply a differential or SE high-speed full rate clock signal to connectors J1/J2. DC blocks or the appropriate shift of voltage levels may be required!

- 9. Observe a high-speed sampled data signal at connectors J5/J6. Connect them to an oscilloscope or similar device with 50*Ohm* termination to ground either directly or through DC blocks. If a sampled version of the input data signal is not observed, adjust the phase of the input data or clock accordingly.

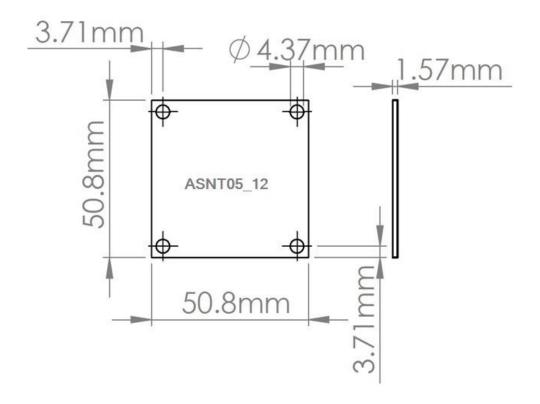

#### **Board Dimension**

Fig. 3. ASNT05\_12 Board Dimensions

Rev. 1.0.1 4 September 2020

# ASNT5012-PQC on ASNT05\_11 Evaluation Board DC-17Gbps High Sensitivity D-Type Flip-Flop Application Note

### **Part Description**

The ASNT5012-PQC high sensitivity D-type flip-flop accepts a broadband data signal at its differential input port dp/dn and delivers a retimed version of it to its differential output port outp/outn. Retiming of the input data is accomplished by applying a full rate input clock signal to the differential input port cp/cn.

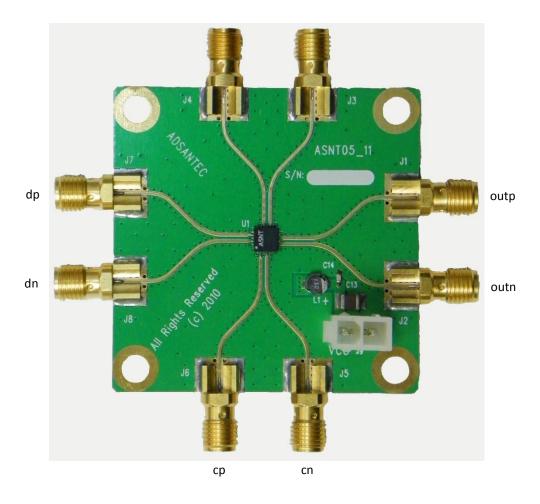

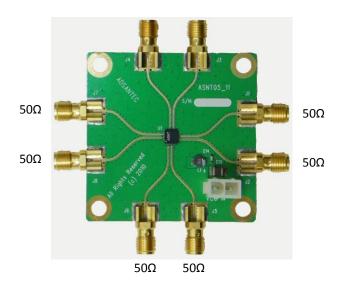

The part is mounted on an ASNT05\_11 evaluation board with 50*Ohm* transmission lines to transfer signals to/from the chip to 6 high-speed edge-mount female connectors (Emerson or similar) as shown in Fig. 4. The board has a MOLEX connector for the power supply, as well as signal filters, supply filters, and decoupling networks. The board measures approximately 2.0x2.0 inches, without connectors.

Fig. 4. Layout of ASNT05\_11 PCB

The signal and power connectors are described in Table 1 and Table 2 below.

Table 3. Signal Connectors

| Name   | Name    | Signal description                                              | Signal   | I/O type |

|--------|---------|-----------------------------------------------------------------|----------|----------|

| on PCB | on Chip |                                                                 | polarity |          |

| J7     | dp      | Differential data inputs with internal SE 50 <i>Ohm</i>         | Direct   | CML      |

| Ј8     | dn      | termination to VCC                                              | Inverted | input    |

| J1     | outp    | Differential outputs with internal SE 50 <i>Ohm</i> termination | Direct   | CML      |

| J2     | outn    | to VCC; require external SE 50 <i>Ohm</i> termination to VCC    | Inverted | output   |

| J6     | ср      | Differential clock inputs with internal SE 50 <i>Ohm</i>        | Direct   | CML      |

| J5     | cn      | termination to VCC                                              | Inverted | input    |

Table 4. Power Supply Connectors

| Name on PCB | Name on Chip | Supply type               | Supply voltage, V |

|-------------|--------------|---------------------------|-------------------|

| VCC         | vcc          | Main postive power supply | +3.3              |

| GND         | vee          | External ground           | 0                 |

### **Initial Setup and Basic Functionality**

- 10. The part is static sensitive. Please observe anti-static protection procedures!

- 11. Measure the resistance of all connector pins to VCC, including the power supply, while making sure the board is grounded. All I/O ports should measure 50*Ohms* while on the power supply connector, VCC should be a short, and GND should be high impedance. Fig. 5 shows the resistance values of the described I/O connectors.

Fig. 5. Impedance of I/O Connectors

- 12. Switch on the first external power supply unit and set it to a positive supply voltage with a value of +0.0V (negative output pin of the unit must be shorted to ground).

- 13. Connect the supply unit's output pins to the PCB's Molex connector marked VCC GND so that the positive output pin is connected to the VCC connector pin.

- 14. Gradually increase the positive supply voltage to +3.3V.

- 15. Monitor the supply current in accordance with the part's specifications. Current should be approximately 140mA.

- 16. Apply a differential or SE high-speed data signal to connectors J7/J8. DC blocks or the appropriate shift of voltage levels may be required!

- 17. Apply a differential or SE high-speed full rate clock signal to connectors J6/J5. DC blocks or the appropriate shift of voltage levels may be required!

- 18. Observe a high-speed sampled data signal at connectors J1/J2. Connect them to an oscilloscope or similar device with 50*Ohm* termination to ground through DC blocks. If a sampled version of the input data signal is not observed, adjust the phase of the input data or clock accordingly.

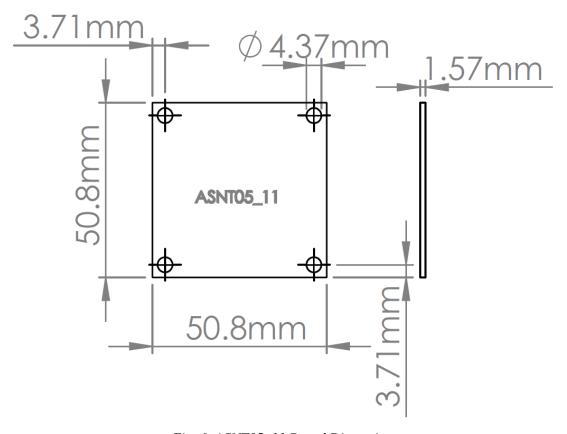

#### **Board Dimensions**

Fig. 6. ASNT05\_11 Board Dimensions

Rev. 1.0.1 7 September 2020

Office: (310) 530-9400 Fax: (310) 530-9402

www.adsantec.com

## **Revision History**

| Revision | Date    | Changes         |

|----------|---------|-----------------|

| 1.0.1    | 09-2020 | Initial Release |

Rev. 1.0.1 8 September 2020