# 5T9304

### DATA SHEET

## **General Description**

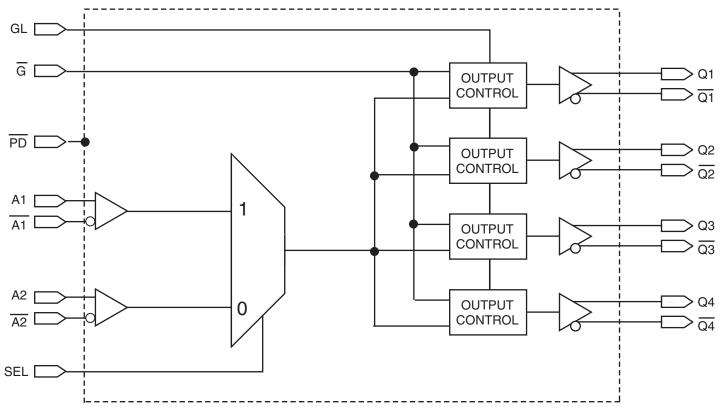

The 5T9304 differential clock buffer has a user-selectable differential input to four LVDS outputs. The fanout from a differential input to four LVDS outputs reduces loading on the preceding driver and provides an efficient clock distribution network. The 5T9304 can act as a translator from a differential HSTL, eHSTL, LVEPECL (2.5V), LVPECL (3.3V), CML, or LVDS input to LVDS outputs. A single-ended 3.3V / 2.5V LVTTL input can also be used to translate to LVDS outputs. The redundant input capability allows for an asynchronous change-over from a primary clock source to a secondary clock source. Selectable reference inputs are controlled by SEL.

The 5T9304 outputs can be asynchronously enabled/disabled. When disabled, the outputs will drive to the value selected by the GL pin. Multiple power and grounds reduce noise.

### Features

- Guaranteed low skew: 50ps (maximum)

- Very low duty cycle distortion: 125ps (maximum)

- Propagation delay: 1.75ns (maximum)

- Up to 450MHz operation

- Selectable inputs

- Hot insertable and over-voltage tolerant inputs

- 3.3V/2.5V LVTTL, HSTL eHSTL, LVEPECL (2.5V), LVPECL (3.3V), CML or LVDS input interface

- Selectable differential inputs to four LVDS outputs

- 2.5V V<sub>DD</sub>

- 0°C to 70°C ambient operating temperature

- Available in lead-free (RoHS 6) package

- •

## Applications

Clock distribution

## **Pin Assignment**

| GND             | 1  | 24 | H A2         |

|-----------------|----|----|--------------|

|                 |    | 24 |              |

| RESERVED        | =  | 22 |              |

| V <sub>DD</sub> | -  | 21 |              |

|                 | 5  | 20 |              |

| Q1              | 6  | 19 | 🗄 Q3         |

| Q2              | 7  | 18 | □ <u>Q</u> 4 |

| Q2              | 8  | 17 | 🗆 Q4         |

| V <sub>DD</sub> | 9  | 16 |              |

| SEL             | 10 | 15 | 🗆 GL         |

| G               | 11 | 14 | 🗆 A1         |

| GND             | 12 | 13 | 🗆 A1         |

|                 |    |    |              |

24-Lead TSSOP 4.4mm x 7.8mm x 1.0mm package body G Package Top View

5T9304

## **Block Diagram**

### Table 1. Pin Descriptions

| Number          | Name                                                                 |          | Туре                         | Description                                                                                                                                                                                                                                                                                   |

|-----------------|----------------------------------------------------------------------|----------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 12, 22       | GND                                                                  |          | Power                        | Power supply return for all power.                                                                                                                                                                                                                                                            |

| 2               | PD                                                                   | Input    | LVTTL                        | Power-down control. Shuts off entire chip. If LOW, the device goes into low power mode. Inputs and outputs are disabled. Both Qx and $\overline{Qx}$ outputs will pull to VDD. Set HIGH for normal operation. <sup>(3)</sup>                                                                  |

| 3               | RESERVED                                                             | Reserved |                              | Reserved pin.                                                                                                                                                                                                                                                                                 |

| 4, 9, 16, 21    | V <sub>DD</sub>                                                      |          | Power                        | Power supply for the device core and inputs.                                                                                                                                                                                                                                                  |

| 5, 7,<br>18, 20 | $\frac{\overline{Q1}, \overline{Q2},}{\overline{Q4}, \overline{Q3}}$ | Output   | LVDS                         | Complementary differential clock outputs.                                                                                                                                                                                                                                                     |

| 6, 8,<br>17, 19 | Q1, Q2,<br>Q4, Q3                                                    | Output   | LVDS                         | Differential clock outputs.                                                                                                                                                                                                                                                                   |

| 10              | SEL                                                                  | Input    | LVTTL                        | Reference clock select. When LOW, selects A2 and $\overline{A2}$ . When HIGH, selects A1 and $\overline{A1}$ .                                                                                                                                                                                |

| 11              | G                                                                    | Input    | LVTTL                        | Gate control for differential outputs Q1 and $\overline{Q1}$ through Q4 and $\overline{Q4}$ . When $\overline{G}$ is LOW, the differential outputs are active. When $\overline{G}$ is HIGH, the differential outputs are asynchronously driven to the level designated by GL <sup>(2)</sup> . |

| 13, 24          | A1, A2                                                               | Input    | Adjustable (1, 4)            | Clock input. A[1:2] is the "true" side of the differential clock input.                                                                                                                                                                                                                       |

| 14, 23          | <u>A1, A2</u>                                                        | Input    | Adjustable <sup>(1, 4)</sup> | Complementary clock inputs. $\overline{A[1:2]}$ is the complementary side of A[1:2].<br>For LVTTL single-ended operation, $\overline{A[1:2]}$ should be set to the desired toggle voltage for A[1:2]:<br>3.3V LVTTL VREF = 1650mV<br>2.5V LVTTL VREF = 1250mV                                 |

| 15              | GL                                                                   | Input    | LVTTL                        | Specifies output disable level. If HIGH, Qx outputs disable HIGH and $\overline{Qx}$ outputs disable LOW. If LOW, Qx outputs disable LOW and $\overline{Qx}$ outputs disable HIGH.                                                                                                            |

NOTES:

Inputs are capable of translating the following interface standards: Single-ended 3.3V and 2.5V LVTTL levels

Differential HSTL and eHSTL levels

Differential LVEPECL (2.5V) and LVPECL (3.3V) levels

Differential LVDS levels

Differential CML levels

2. Because the gate controls are asynchronous, runt pulses are possible. It is the user's responsibility to either time the gate control signals to minimize the possibility of runt pulses or be able to tolerate them in down stream circuitry.

- 3. It is recommended that the outputs be disabled before entering power-down mode. It is also recommended that the outputs remain disabled until the device completes power-up after asserting PD.

- 4. The user must take precautions with any differential input interface standard being used in order to prevent instability when there is no input signal.

### Table 2. Pin Characteristics (TA = +25°C, F = 1.0MHz)

| Symbol          | Parameter         | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|-------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub> | Input Capacitance |                 |         | 3       |         | pF    |

NOTE: This parameter is measured at characterization but not tested.

## **Function Tables**

#### Table 3A. Gate Control Output Table

| Control | Output | Outputs  |          |  |

|---------|--------|----------|----------|--|

| GL      | G      | Q[1:4]   | Q[1:4]   |  |

| 0       | 0      | Toggling | Toggling |  |

| 0       | 1      | LOW      | HIGH     |  |

| 1       | 0      | Toggling | Toggling |  |

| 1       | 1      | HIGH     | LOW      |  |

#### Table 3B. Input Selection Table

| Selection SEL pin | Inputs             |

|-------------------|--------------------|

| 0                 | A2, <del>A</del> 2 |

| 1                 | A1, <del>A</del> 1 |

### **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics or AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                                 | Rating                        |

|------------------------------------------------------|-------------------------------|

| Power Supply Voltage, V <sub>DD</sub>                | -0.5V to +3.6V                |

| Input Voltage, V <sub>I</sub>                        | -0.5V to +3.6V                |

| Output Voltage, V <sub>O</sub><br>Not to exceed 3.6V | -0.5 to V <sub>DD</sub> +0.5V |

| Storage Temperature, T <sub>STG</sub>                | -65°C to 150°C                |

| Junction Temperature, T <sub>J</sub>                 | 150°C                         |

### **Recommended Operating Range**

| Symbol          | Description                   | Minimum | Typical | Maximum | Units |

|-----------------|-------------------------------|---------|---------|---------|-------|

| Та              | Ambient Operating Temperature | 0       | 25      | 70      | °C    |

| V <sub>DD</sub> | Internal Power Supply Voltage | 2.3     | 2.5     | 2.7     | V     |

## **DC Electrical Characteristics**

| Table 4A. LVDS Power Supply DC Characteristics <sup>(1)</sup> , V <sub>D</sub> | $T_{D} = 2.5V \pm 0.2V, T_{\Delta} = 0^{\circ}C \text{ to } 70^{\circ}C$ |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Symbol           | Parameter                                      | Test Conditions                                                                      | Minimum | Typical <sup>(2)</sup> | Maximum | Units |

|------------------|------------------------------------------------|--------------------------------------------------------------------------------------|---------|------------------------|---------|-------|

| I <sub>DDQ</sub> | Quiescent V <sub>DD</sub> Power Supply Current | V <sub>DD</sub> = Max.,<br>All Input Clocks = LOW <sup>(2)</sup> ;<br>Output enabled |         |                        | 240     | mA    |

| I <sub>TOT</sub> | Total Power V <sub>DD</sub> Supply Current     | V <sub>DD</sub> = 2.7V;<br>F <sub>REFERENCE</sub> Clock = 450MHz                     |         |                        | 250     | mA    |

| I <sub>PD</sub>  | Total Power Down Supply Current                | $\overline{PD} = LOW$                                                                |         |                        | 5       | mA    |

NOTE 1. These power consumption characteristics are for all the valid input interfaces and cover the worst case conditions.

NOTE 2. The true input is held LOW and the complementary input is held HIGH.

### Table 4B. LVCMOS/LVTTL DC Characteristics<sup>(1)</sup>, $V_{DD} = 2.5V \pm 0.2V$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$

| Symbol           | Parameter                           | Test Conditions                                 | Minimum | Typical <sup>(2)</sup> | Maximum | Units |

|------------------|-------------------------------------|-------------------------------------------------|---------|------------------------|---------|-------|

| I <sub>IH</sub>  | Input High Current                  | V <sub>DD</sub> = 2.7V                          |         |                        | ±5      | μA    |

| IIL              | Input Low Current                   | V <sub>DD</sub> = 2.7V                          |         |                        | ±5      | μA    |

| V <sub>IK</sub>  | Clamp Diode Voltage                 | V <sub>DD</sub> = 2.3V, I <sub>IN</sub> = -18mA |         | -0.7                   | -1.2    | V     |

| V <sub>IN</sub>  | DC Input Voltage                    |                                                 | -0.3    |                        | 3.6     | V     |

| V <sub>IH</sub>  | DC Input High Voltage               |                                                 | 1.7     |                        |         | V     |

| V <sub>IL</sub>  | DC Input Low Voltage                |                                                 |         |                        | 0.7     | V     |

| V <sub>THI</sub> | DC Input Threshold Crossing Voltage |                                                 |         | V <sub>DD</sub> /2     |         | V     |

| V                | Single-Ended Reference Voltage (3)  | 3.3V LVTTL                                      |         | 1.65                   |         | V     |

| V <sub>REF</sub> |                                     | 2.5V LVTTL                                      |         | 1.25                   |         | V     |

NOTE 1. See Recommended Operating Range table.

NOTE 2. Typical values are at  $V_{DD} = 2.5V$ , +25°C ambient.

NOTE 3. For A[1:2] single-ended operation,  $\overline{A}$ [1:2] is tied to a DC reference voltage.

#### Table 4C. Differential DC Characteristics<sup>(1)</sup>, $V_{DD} = 2.5V \pm 0.2V$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$

| Symbol           | Parameter                                   | Test Conditions                                 | Minimum | Typical <sup>(2)</sup> | Maximum         | Units |

|------------------|---------------------------------------------|-------------------------------------------------|---------|------------------------|-----------------|-------|

| I <sub>IH</sub>  | Input High Current                          | V <sub>DD</sub> = 2.7V                          |         |                        | ±5              | μA    |

| IIL              | Input Low Current                           | V <sub>DD</sub> = 2.7V                          |         |                        | ±5              | μΑ    |

| V <sub>IK</sub>  | Clamp Diode Voltage                         | V <sub>DD</sub> = 2.3V, I <sub>IN</sub> = -18mA |         | -0.7                   | -1.2            | V     |

| V <sub>IN</sub>  | DC Input Voltage                            |                                                 | -0.3    |                        | 3.6             | V     |

| V <sub>DIF</sub> | DC Differential Voltage <sup>(3)</sup>      |                                                 | 0.1     |                        |                 | V     |

| V <sub>CM</sub>  | DC Common Mode Input Voltage <sup>(4)</sup> |                                                 | 0.05    |                        | V <sub>DD</sub> | V     |

NOTE 1. See *Recommended Operating Range* table.

NOTE 2. Typical values are at  $V_{DD} = 2.5V$ ,  $+25^{\circ}C$  ambient.

NOTE 3. VDIF specifies the minimum input differential voltage (VTR - VCP) required for switching where VTR is the "true" input level and VCP is the "complement" input level. The DC differential voltage must be maintained to guarantee retaining the existing HIGH or LOW input. The AC differential voltage must be achieved to guarantee switching to a new state.

NOTE 4. VCM specifies the maximum allowable range of (VTR + VCP) /2.

| Symbol             | Parameter                                                        | Test Conditions             | Minimum | Typical <sup>(2)</sup> | Maximum | Units |

|--------------------|------------------------------------------------------------------|-----------------------------|---------|------------------------|---------|-------|

| V <sub>OT(+)</sub> | Differential Output Voltage for the True Binary State            |                             | 247     |                        | 454     | mV    |

| V <sub>OT(-)</sub> | Differential Output Voltage for the<br>False Binary State        |                             | 247     |                        | 454     | mV    |

| $\Delta V_{OT}$    | Change in V <sub>OT</sub> Between Complementary<br>Output States |                             |         |                        | 50      | mV    |

| V <sub>OS</sub>    | Output Common Mode Voltage<br>(Offset Voltage)                   |                             | 1.125   | 1.2                    | 1.375   | v     |

| $\Delta V_{OS}$    | Change in V <sub>OS</sub> Between Complementary<br>Output States |                             |         |                        | 50      | mV    |

| I <sub>OS</sub>    | Outputs Short Circuit Current                                    | $V_{OUT+and} V_{OUT-} = 0V$ |         | 12                     | 24      | mA    |

| I <sub>OSD</sub>   | Differential Outputs Short Circuit Current                       | $V_{OUT+} = V_{OUT-}$       |         | 6                      | 12      | mA    |

#### Table 4D. LVDS DC Characteristics<sup>(1)</sup>, $V_{DD} = 2.5V \pm 0.2V$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$

NOTE 1. See Recommended Operating Range table.

NOTE 2. Typical values are at  $V_{DD} = 2.5V$ ,  $+25^{\circ}C$  ambient.

## **AC Electrical Characteristics**

#### Table 5A. HSTL Differential Input AC Characteristics, $V_{DD} = 2.5V \pm 0.2V$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$

| Symbol                          | Parameter                                               | Value          | Units |

|---------------------------------|---------------------------------------------------------|----------------|-------|

| V <sub>DIF</sub>                | Input Signal Swing <sup>(1)</sup>                       | 1              | V     |

| V <sub>X</sub>                  | Differential Input Signal Crossing Point <sup>(2)</sup> | 750            | mV    |

| D <sub>H</sub>                  | Duty Cycle                                              | 50             | %     |

| V <sub>THI</sub>                | Input Timing Measurement Reference Level <sup>(3)</sup> | Crossing Point | V     |

| t <sub>R</sub> / t <sub>F</sub> | Input Signal Edge Rate <sup>(4)</sup>                   | 2              | V/ns  |

NOTE 1. The 1V peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the VDIF (AC) specification under actual use conditions.

NOTE 2. A 750mV crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the Vx specification under actual use conditions.

NOTE 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

NOTE 4. The input signal edge rate of 2V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

#### Table 5B. eHSTL AC Differential Input Characteristics, $V_{DD} = 2.5V \pm 0.2V$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$

| Symbol                          | Parameter                                               | Value          | Units |

|---------------------------------|---------------------------------------------------------|----------------|-------|

| V <sub>DIF</sub>                | Input Signal Swing <sup>(1)</sup>                       | 1              | V     |

| V <sub>X</sub>                  | Differential Input Signal Crossing Point <sup>(2)</sup> | 900            | mV    |

| D <sub>H</sub>                  | Duty Cycle                                              | 50             | %     |

| V <sub>THI</sub>                | Input Timing Measurement Reference Level <sup>(3)</sup> | Crossing Point | V     |

| t <sub>R</sub> / t <sub>F</sub> | Input Signal Edge Rate <sup>(4)</sup>                   | 2              | V/ns  |

NOTE 1. The 1V peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the VDIF (AC) specification under actual use conditions.

NOTE 2. A 900mV crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the Vx specification under actual use conditions.

NOTE 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

NOTE 4. The input signal edge rate of 2V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

#### Table 5C. LVEPECL (2.5V) and LVPECL (3.3V) Differential Input AC Characteristics, $V_{DD} = 2.5V \pm 0.2V$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$

| Symbol                          | Parameter                                               | Maximum | Units          |      |

|---------------------------------|---------------------------------------------------------|---------|----------------|------|

| V <sub>DIF</sub>                | Input Signal Swing <sup>(1)</sup>                       |         | 732            | mV   |

| V <sub>X</sub>                  | Differential Input Cross Point Voltage <sup>(2)</sup>   | LVEPECL | 1082           | mV   |

|                                 |                                                         | LVPECL  | 1880           | mV   |

| D <sub>H</sub>                  | Duty Cycle                                              |         | 50             | %    |

| V <sub>THI</sub>                | Input Timing Measurement Reference Level <sup>(3)</sup> |         | Crossing Point | V    |

| t <sub>R</sub> / t <sub>F</sub> | Input Signal Edge Rate <sup>(4)</sup>                   |         | 2              | V/ns |

NOTE 1. The 732mV peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the VDIF (AC) specification under actual use conditions.

NOTE 2. A 1082mV LVEPECL (2.5V) and 1880mV LVPECL (3.3V) crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the Vx specification under actual use conditions.

NOTE 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

NOTE 4. The input signal edge rate of 2V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

#### Table 5D. LVDS Differential Input AC Characteristics, $T_A = 0^{\circ}C$ to $70^{\circ}C$

| Symbol                          | Parameter                                               | Maximum        | Units |  |

|---------------------------------|---------------------------------------------------------|----------------|-------|--|

| V <sub>DIF</sub>                | Input Signal Swing <sup>(1)</sup>                       | 400            | mV    |  |

| V <sub>X</sub>                  | Differential Input Cross Point Voltage <sup>(2)</sup>   | 1.2            | V     |  |

| D <sub>H</sub>                  | Duty Cycle                                              | 50             | %     |  |

| V <sub>THI</sub>                | Input Timing Measurement Reference Level <sup>(3)</sup> | Crossing Point | V     |  |

| t <sub>R</sub> / t <sub>F</sub> | Input Signal Edge Rate <sup>(4)</sup>                   | 2              | V/ns  |  |

NOTE 1. The 400mV peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the VDIF (AC) specification under actual use conditions.

NOTE 2. A 1.2V crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the Vx specification under actual use conditions.

NOTE 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

NOTE 4. The input signal edge rate of 2V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

#### Table 5E. AC Differential Input Characteristics<sup>(1)</sup>, $V_{DD} = 2.5V \pm 0.2V$ , $T_A = 0^{\circ}C$ to 70°C

| Symbol           | Parameter                                      | Minimum | Typical | Maximum         | Units |

|------------------|------------------------------------------------|---------|---------|-----------------|-------|

| V <sub>DIF</sub> | AC Differential Voltage <sup>(2)</sup>         | 0.1     |         | 3.6             | V     |

| V <sub>X</sub>   | Differential Input Cross Point Voltage         | 0.05    |         | V <sub>DD</sub> | V     |

| V <sub>CM</sub>  | Common Mode Input Voltage Range <sup>(3)</sup> | 0.05    |         | V <sub>DD</sub> | V     |

| V <sub>IN</sub>  | Input Voltage                                  | -0.3    |         | 3.6             | V     |

NOTE 1. The output will not change state until the inputs have crossed and the minimum differential voltage range defined by V<sub>DIF</sub> has been met or exceeded.

NOTE 2.  $V_{DIF}$  specifies the minimum input voltage ( $V_{TR} - V_{CP}$ ) required for switching where  $V_{TR}$  is the "true" input level and  $V_{CP}$  is the "complement" input level. The AC differential voltage must be achieved to guarantee switching to a new state. NOTE 3.  $V_{CM}$  specified the maximum allowable range of ( $V_{TR} + V_{CP}$ ) /2.

| Symbol                          | Parameter                                                                             | Test Conditions        | Minimum | Typical | Maximum | Units |

|---------------------------------|---------------------------------------------------------------------------------------|------------------------|---------|---------|---------|-------|

| <i>t</i> sk(o)                  | Same Device Output Pin-to-Pin Skew (2)                                                |                        |         |         | 50      | ps    |

| <i>t</i> sk(p)                  | Pulse Skew <sup>(3)</sup>                                                             |                        |         |         | 125     | ps    |

| <i>t</i> sk(pp)                 | Part-to-Part Skew <sup>(4)</sup>                                                      |                        |         |         | 300     | ps    |

| tp <sub>LH</sub>                | Propagation Delay, Low-to-High                                                        | A Crosspoint to Qn, Qn |         | 1.25    | 1.75    | ns    |

| tp <sub>HL</sub>                | Propagation Delay, High-to-Low                                                        | Crosspoint             |         | 1.25    | 1.75    | ns    |

| fo                              | Frequency Range <sup>(6)</sup>                                                        |                        |         |         | 450     | MHz   |

| t <sub>PGE</sub>                | Output Gate Enable Crossing<br>VTHI-to-Qn/Qn Crosspoint                               |                        |         |         | 3.5     | ns    |

| t <sub>PGD</sub>                | Output Gate Enable Crossing<br>VTHI-to-Qn/Qn Crosspoint Driven to<br>Designated Level |                        |         |         | 3.5     | ns    |

| t <sub>PWRDN</sub>              | PD Crossing V <sub>THI</sub> -to-Qn = V <sub>DD</sub> , $\overline{Qn} = V_{DD}$      |                        |         |         | 100     | μS    |

| t <sub>PWRUP</sub>              | Output Gate Disable Crossing V <sub>THI</sub> to Qn/Qn Driven to Designated Level     |                        |         |         | 100     | μS    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time <sup>(6)</sup>                                                  | 20% to 80%             | 125     |         | 600     | ps    |

#### Table 5F. AC Characteristics<sup>(1,5)</sup>, $V_{DD} = 2.5V \pm 0.2V$ , $T_A = 0^{\circ}C$ to 70°C

NOTE. Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

NOTE 1. AC propagation measurements should not be taken within the first 100 cycles of startup.

NOTE 2. Skew measured between Crosspoint of all differential output pairs under identical input and output interfaces, transitions and load conditions on any one device.

NOTE 3. Skew measured is the difference between propagation delay times tp<sub>HL</sub> and tp<sub>LH</sub> of any differential output pair under identical input and output interfaces, transitions and load conditions on any one device.

NOTE 4. Skew measured is the magnitude of the difference in propagation times between any single differential output pair of two devices, given identical transitions and load conditions at identical VDD levels and temperature.

NOTE 5. All parameters are tested with a 50% input duty cycle.

NOTE 6. Guaranteed by design but not production tested.

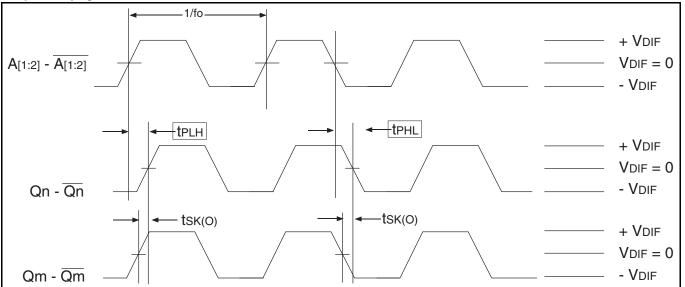

## **Differential AC Timing Waveforms**

**Output Propagation and Skew Waveforms**

NOTE 1: Pulse skew is calculated using the following expression:

Qn - Qn

$t_{sk(p)} = |tp_{HL} - tp_{LH}|$ Note that the  $tp_{HL}$  and  $tp_{LH}$  shown above as not valid measurements for this calculation because they are not taken from the same pulse. NOTE 2: AC propagation measurements should not be taken within the first 100 cycles of startup.

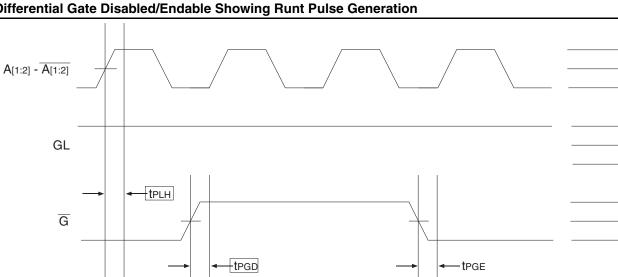

#### **Differential Gate Disabled/Endable Showing Runt Pulse Generation**

NOTE 1: As shown, it is possible to generate runt pulses on gate disable and enable of the outputs. It is the user's responsibility to time the G signal to avoid this problem.

+ VDIF VDIF = 0

- VDIF

Vін

Vтні VIL

Vін

Vтні VIL

+ VDIF VDIF = 0

- VDIF

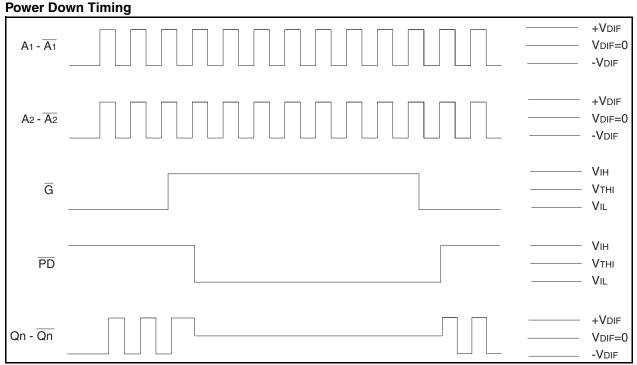

NOTE 1: It is recommended that outputs be disabled before entering power-down mode. It is also recommended that the outputs remain disabled until the device completes power-up after asserting  $\overline{PD}$ .

NOTE 2: The Power Down Timing diagram assumes that GL is HIGH.

NOTE 3: It should be noted that during power-down mode, the outputs are both pulled to  $V_{DD}$ . In the *Power Down Timing* diagram this is shown when Qn/Qn goes to  $V_{DIF} = 0$ .

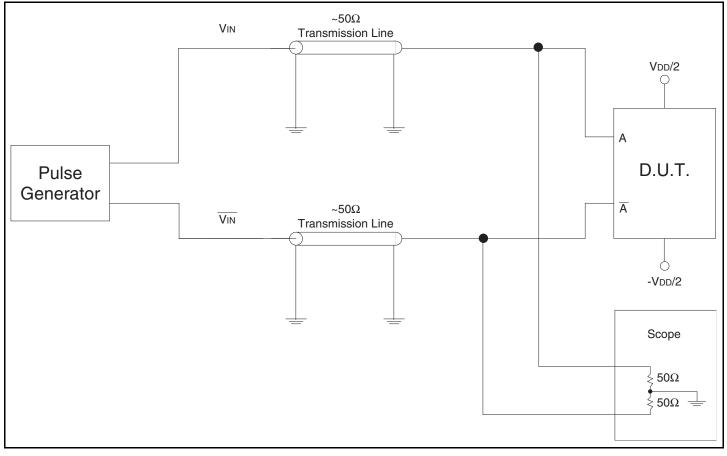

#### **Test Circuit for Differential Input**

#### Table 6A. Differential Input Test Conditions

| Symbol           | $V_{DD} = 2.5V \pm 0.2V$         | Unit |

|------------------|----------------------------------|------|

| V <sub>THI</sub> | Crossing of A and $\overline{A}$ | V    |

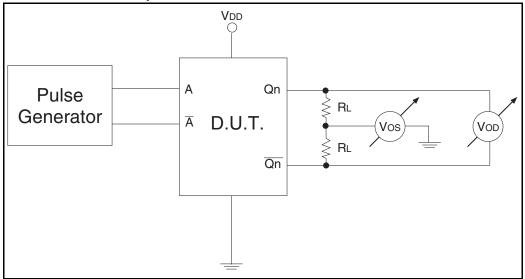

#### Test Circuit for DC Outputs and Power Down Tests

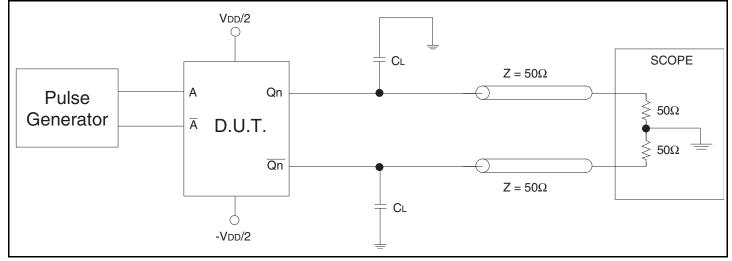

#### Test Circuit for Propagation, Skew, and Gate Enable/Disable Timing

#### Table 6B. Differential Input Test Conditions

| Symbol | $V_{DD} = 2.5V \pm 0.2V$ | Unit |

|--------|--------------------------|------|

| C      | 0 <sup>(1)</sup>         | pF   |

| υL     | 8 <sup>(1,2)</sup>       | pF   |

| RL     | 50                       | Ω    |

NOTE 1: Specifications only apply to "Normal Operations" test condition. The  $T_{IA}/E_{IA}$  specification load is for reference only. NOTE 2: The scope inputs are assumed to have a 2pF load to ground.  $T_{IA}/E_{IA} - 644$  specifies 5pF between the output pair. With  $C_L = 8pF$ , this gives the test circuit appropriate 5pF equivalent load.

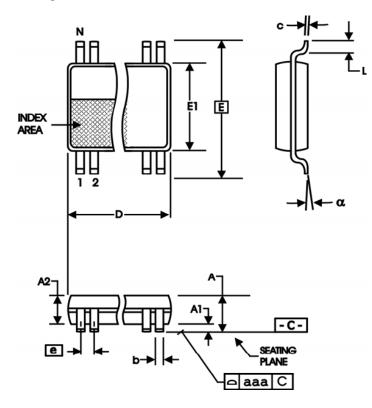

## Package Outline and Package Dimensions

Package Outline - G Suffix for 24 Lead TSSOP

#### Table 7. Package Dimensions

| All Din | nensions in Mi | illimeters |

|---------|----------------|------------|

| Symbol  | Minimum        | Maximum    |

| N       | 2              | 24         |

| Α       |                | 1.20       |

| A1      | 0.5            | 0.15       |

| A2      | 0.80           | 1.05       |

| b       | 0.19           | 0.30       |

| С       | 0.09           | 0.20       |

| D       | 7.70           | 7.90       |

| E       | 6.40           | Basic      |

| E1      | 4.30           | 4.50       |

| e       | 0.65           | Basic      |

| L       | 0.45           | 0.75       |

| α       | 0°             | 8°         |

| aaa     |                | 0.10       |

Reference Document: JEDEC Publication 95, MO-153

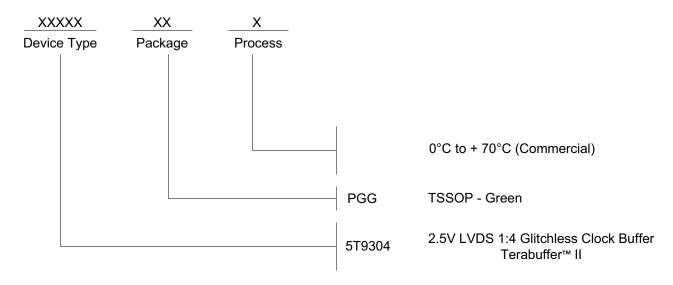

## **Ordering Information**

### Table 8. Ordering Information

# **Revision History Sheet**

| Rev | Table | Page | Description of Change                                                                         | Date    |

|-----|-------|------|-----------------------------------------------------------------------------------------------|---------|

| А   |       | 1    | Not Recommended For New Designs                                                               | 5/16/13 |

| A   | Т8    | 14   | Ordering Information - Removed Leaded Devices PDN N-13-11<br>Updated data sheet format        | 3/11/15 |

| A   | Т8    | 14   | Ordering Information - Corrected Commercial temperature.<br>Removed NRND from the data sheet. | 5/13/15 |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/