# 128Mb HyperRAM

### Table of Contents-

| 1.  | . FEATURES3 |          |                                                        |    |  |  |  |  |

|-----|-------------|----------|--------------------------------------------------------|----|--|--|--|--|

| 2.  | ORDEF       | R INFOR  | MATION                                                 | 3  |  |  |  |  |

| 3.  | BALL A      | SSIGN    | MENT                                                   | 4  |  |  |  |  |

| 4.  | BALL D      | ESCRIF   | PTIONS                                                 | 5  |  |  |  |  |

| 5.  | BLOCK       | DIAGR    | AM                                                     | 6  |  |  |  |  |

|     | 5.1         | Function | on Block Diagram (Single Die)                          | 6  |  |  |  |  |

|     | 5.2         | Packa    | ge Block Diagram (DDP)                                 | 7  |  |  |  |  |

| 6.  | FUNCT       | IONAL [  | DESCRIPTION                                            | 8  |  |  |  |  |

|     | 6.1         | HyperE   | Bus Interface                                          | 8  |  |  |  |  |

| 7.  | HYPER       | BUS TR   | RANSACTION DETAILS                                     | 11 |  |  |  |  |

|     | 7.1         | Comm     | and/Address Bit Assignments                            | 11 |  |  |  |  |

|     | 7.2         | Read 7   | Transactions                                           | 14 |  |  |  |  |

|     | 7.3         |          | Transactions (Memory Array Write)                      |    |  |  |  |  |

|     | 7.4         |          | Transactions without Initial Latency (Register Write)  |    |  |  |  |  |

| 8.  | MEMOR       |          | CE                                                     |    |  |  |  |  |

|     | 8.1         | HyperE   | Bus Interface Memory Space addressing                  |    |  |  |  |  |

|     |             | 8.1.1    | Density and Row Boundaries                             |    |  |  |  |  |

| 9.  | REGIST      |          | ACE                                                    |    |  |  |  |  |

|     | 9.1         |          | Bus Interface Register Addressing                      |    |  |  |  |  |

|     | 9.2         | •        | er Space Access                                        |    |  |  |  |  |

|     | 9.3         |          |                                                        |    |  |  |  |  |

|     | 9.4         | •        | uration Register 0                                     |    |  |  |  |  |

|     |             | 9.4.1    | Wrapped Burst                                          |    |  |  |  |  |

|     |             | 9.4.2    | Hybrid Burst                                           |    |  |  |  |  |

|     |             | 9.4.3    | Initial Latency                                        |    |  |  |  |  |

|     |             | 9.4.4    | Fixed Latency                                          |    |  |  |  |  |

|     |             | 9.4.5    | Drive Strength                                         |    |  |  |  |  |

|     |             | 9.4.6    | Deep Power Down                                        |    |  |  |  |  |

|     | 9.5         | •        | uration Register 1                                     |    |  |  |  |  |

|     |             | 9.5.1    | Master Clock Type                                      |    |  |  |  |  |

|     |             | 9.5.2    | Partial Array Refresh                                  |    |  |  |  |  |

|     |             | 9.5.3    | Hybrid Sleep                                           |    |  |  |  |  |

|     |             | 9.5.4    | Distributed Refresh Interval                           |    |  |  |  |  |

|     | 9.6         |          | Die-Package (DDP) Application                          |    |  |  |  |  |

|     |             | 9.6.1    | Die Stack Addressing                                   |    |  |  |  |  |

|     |             | 9.6.2    | Burst Operations - Die Boundary Crossing               |    |  |  |  |  |

|     |             | 9.6.3    | Die number assignment                                  |    |  |  |  |  |

|     |             | 9.6.4    | Latency mode                                           |    |  |  |  |  |

|     |             | 9.6.5    | IO pad capacitance                                     |    |  |  |  |  |

|     |             | 9.6.6    | Current consumption                                    |    |  |  |  |  |

|     |             | 9.6.7    | Partial Refresh                                        |    |  |  |  |  |

|     |             | 9.6.8    | Hybrid Sleep Mode (HSM) and Deep Power Down (DPD) mode |    |  |  |  |  |

| 10. | INTERF      | FACE ST  | TATES                                                  | 28 |  |  |  |  |

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

Publication Release Date: Sep. 03, 2020

### winbond == IO condition of interface states. 10.2 Interface Standby 29 10.2.2 Active Clock Stop. 29 10.2.3 11 2 Latch up Characteristics 31 ICC Characteristics 32 Power-Up Initialization 33 11.3.5 Power-Down 34 11.3.6 Hardware Reset 35 12.2 1241 Read Transactions 39

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

### 1. FEATURES

- Interface: HyperBus

- Power supply: 1.7V~2.0V or 2.7V~3.6V

- Maximum clock rate: 200MHz

- Double-Data Rate (DDR) Up to 400 MT/s

- · Clock:

- Single ended clock (CK)

- Differential clock (CK/CK#)

- Chip Select (CS#)

- 8-bit data bus (DQ[7:0])

- Hardware reset (RESET#)

- Read-Write Data Strobe (RWDS)

- Bidirectional Data Strobe / Mask

- Output at the start of all transactions to indicate refresh latency

- Output during read transactions as Read Data Strobe

- Input during write transactions as Write Data Mask

### **Performance and Power**

- · Configurable output drive strength

- Power Saving Modes

- Hybrid Sleep Mode

- Deep Power Down

- · Configurable Burst Characteristics

- Linear burst

- Wrapped burst lengths:

- 16 bytes (8 clocks)

- 32 bytes (16 clocks)

- 64 bytes (32 clocks)

- 128 bytes (64 clocks)

- Hybrid burst one wrapped burst followed by linear burst

- Array Refresh Modes

- Full Array Refresh

- Partial Array Refresh

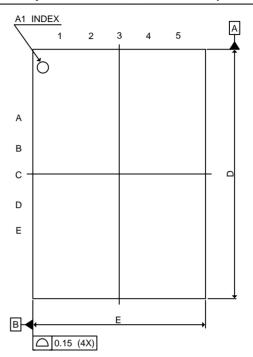

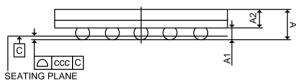

- Support package:

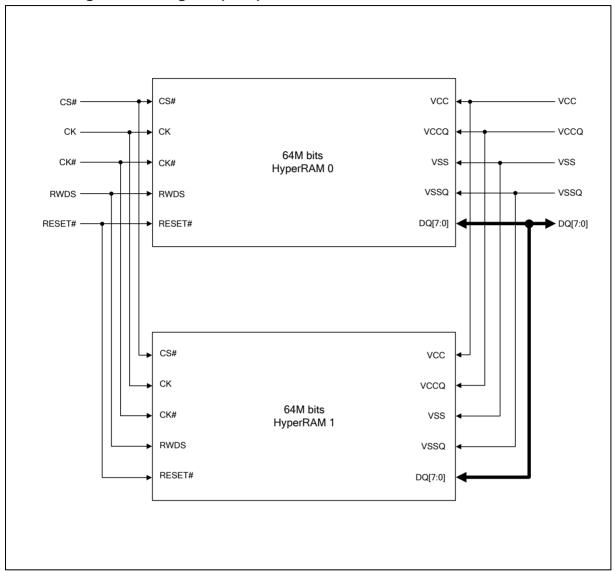

Dual-Die-Package (DDP), two of 64M bit chip sealed in one 24 balls TFBGA package

- Operating temperature range:

- -40°C ≤ TCASE ≤ 85°C

#### 2. ORDER INFORMATION

| Part Number  | VCC/VCCQ | I/O Width | Package             | Interface | Others             |

|--------------|----------|-----------|---------------------|-----------|--------------------|

| W957D8MFYA5I | 1.8V     | 8         | 24 balls TFBGA, DDP | HyperBus  | 200MHz, -40°C~85°C |

| W957A8MFYA5I | 3.0V     | 8         | 24 balls TFBGA, DDP | HyperBus  | 200MHz, -40°C~85°C |

| W957A8MFYA6I | 3.0V     | 8         | 24 balls TFBGA, DDP | HyperBus  | 166MHz, -40°C~85°C |

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

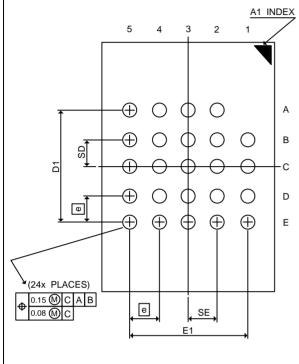

### BALL ASSIGNMENT

|                      | 1    | 2   | 3    | 4      | 5    |  |

|----------------------|------|-----|------|--------|------|--|

|                      |      |     |      |        |      |  |

| А                    |      | RFU | CS#  | RESET# | RFU  |  |

| В                    | CK#  | СК  | VSS  | VCC    | RFU  |  |

| С                    | VSSQ | RFU | RWDS | DQ2    | RFU  |  |

| D                    | VCCQ | DQ1 | DQ0  | DQ3    | DQ4  |  |

| E                    | DQ7  | DQ6 | DQ5  | VCCQ   | VSSQ |  |

| TOP VIEW (Ball Down) |      |     |      |        |      |  |

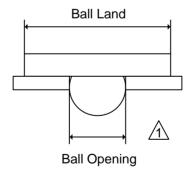

24 Balls TFBGA, 5x5-1 Ball Footprint, Top View

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

Publication Release Date: Sep. 03, 2020

### **BALL DESCRIPTIONS**

| Symbol  | Туре                       | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#     | Input                      | Chip Select: Bus transactions are initiated with a High to Low transition. Bus transactions are terminated with a Low to High transition. The master device has a separate CS# for each slave.                                                                                                                                                                                                                            |

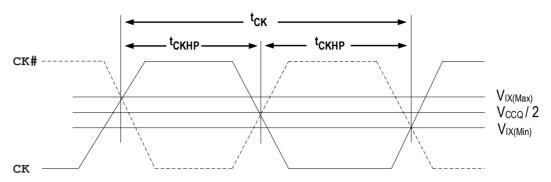

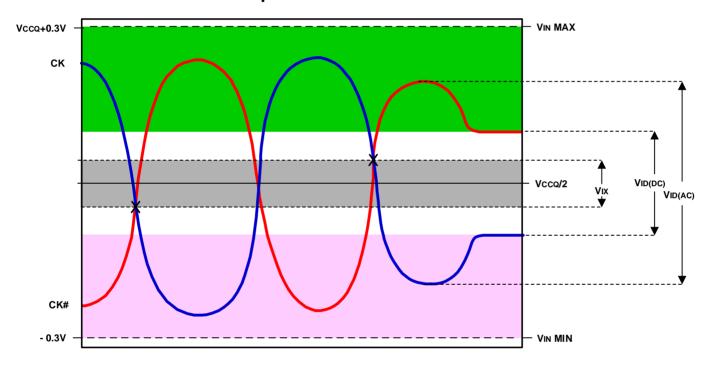

| CK, CK# | Input                      | Differential Clock: Command, address, and data information is output with respect to the crossing of the CK and CK# signals. Single Ended Clock: CK# is not used, only a single ended CK is used. The clock is not required to be free-running.                                                                                                                                                                           |

| DQ[7:0] | Input / Output             | Data Input / Output: Command, Address, and Data information is transferred on these signals during Read and Write transactions.                                                                                                                                                                                                                                                                                           |

| RWDS    | Input / Output             | Read Write Data Strobe:  During the Command/Address portion of all bus transactions RWDS is a slave output and indicates whether additional initial latency is required. Slave output during read data transfer, data is edge aligned with RWDS. Slave input during data transfer in write transactions to function as a data mask.  (High = additional latency, for DDP package, RWDS will not be allowed to drive Low). |

| RESET#  | Input,<br>Internal Pull-up | Hardware Reset: When Low the slave device will self-initialize and return to the Standby state. RWDS and DQ[7:0] are placed into the High-Z state when RESET# is Low. The slave RESET# input includes a weak pull-up, if RESET# is left unconnected it will be pulled up to the High state.  Note: The RESET# pin is maximum 4V tolerant.                                                                                 |

| Vcc     | Power Supply               | Vcc Power Supply: For supplying input buffer of CK/CK#, CS#, RESET#, DQ[7:0] and RWDS, internal circuitry and memory array.                                                                                                                                                                                                                                                                                               |

| Vccq    | Power Supply               | Vccq Power Supply: For supplying output buffer of DQ[7:0] and RWDS.                                                                                                                                                                                                                                                                                                                                                       |

| Vss     | Power Supply               | Vss Ground: Ground of Vcc.                                                                                                                                                                                                                                                                                                                                                                                                |

| VssQ    | Power Supply               | Vssq Ground: Ground of Vccq.                                                                                                                                                                                                                                                                                                                                                                                              |

| RFU     | No Connect                 | Reserved for Future Use: May or may not be connected internally, the signal/ball location should be left unconnected and unused by PCB routing channel for future compatibility. The signal/ball may be used by a signal in the future.                                                                                                                                                                                   |

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

### 5. BLOCK DIAGRAM

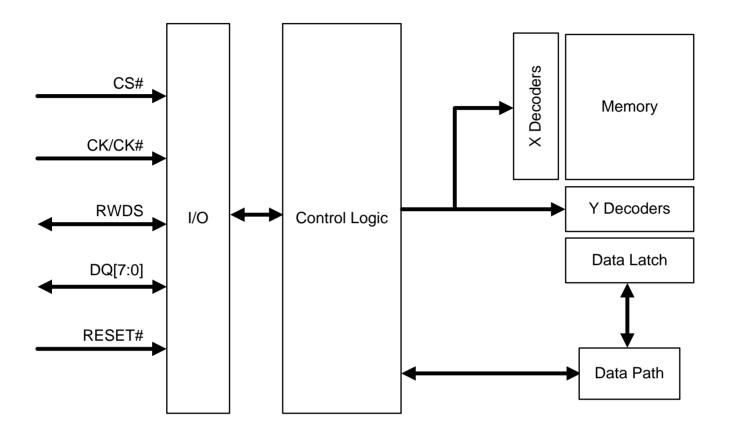

### 5.1 Function Block Diagram (Single Die)

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

## 5.2 Package Block Diagram (DDP)

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

### **FUNCTIONAL DESCRIPTION**

#### 6.1 **HyperBus Interface**

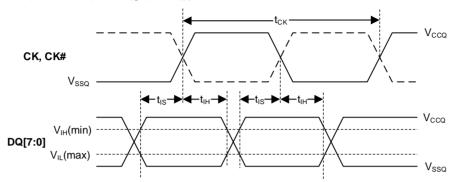

HyperBus is a low signal count, Double Data Rate (DDR) interface, that achieves high speed read and write throughput. The DDR protocol transfers two data bytes per clock cycle on the DQ input/output signals. A read or write transaction on HyperBus consists of a series of 16-bit wide, one clock cycle data transfers at the internal HyperRAM array with two corresponding 8-bit wide, one-half-clock-cycle data transfers on the DQ signals. All inputs and outputs are LV-CMOS compatible.

Command, address, and data information is transferred over the eight HyperBus DQ[7:0] signals. The clock (CK#, CK) is used for information capture by a HyperBus slave device when receiving command, address, or data on the DQ signals. Command or Address values are center aligned with clock transitions.

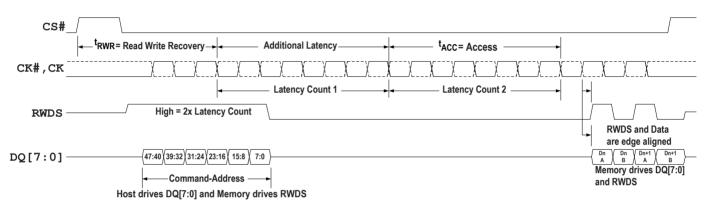

Every transaction begins with the assertion of CS# and Command-Address (CA) signals, followed by the start of clock transitions to transfer six CA bytes, followed by initial access latency and either read or write data transfers, until CS# is de-asserted.

Read and write transactions require two clock cycles to define the target row address and burst type, then an initial access latency of tACC. During the CA part of a transaction, the memory will indicate whether an additional latency for a required refresh time (tRFH) is added to the initial latency; by driving the RWDS signal to the High state. During the CA period the third clock cycle will specify the target word address within the target row. During a read (or write) transaction, after the initial data value has been output (or input), additional data can be read from (or written to) the row on subsequent clock cycles in either a wrapped or linear sequenced. When configured in linear burst mode, the device will automatically fetch the next sequential row from the memory array to support a continuous linear burst. Simultaneously accessing the next row in the array while the read or write data transfer is in progress, allows for a linear sequential burst operation that can provide a sustained data rate of 400 MB/s (1 byte (8 bit data bus) \* 2 (data clock edges) \* 200 MHz = 400 MB/s). Once linear burst reaches the last address of 64Mb of the accessed die, then the addressing will go back to minimum address of the die.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

The Read/Write Data Strobe (RWDS) is a bidirectional signal that indicates:

- When data will start to transfer from a HyperRAM device to the master device in read transactions (initial read latency)

- When data is being transferred from a HyperRAM device to the master device during read transactions (as a source synchronous read data strobe)

- When data may start to transfer from the master device to a HyperRAM device in write transactions (initial write latency)

- Data masking during write data transfers

During the CA transfer portion of a read or write transaction, RWDS acts as an output from a HyperRAM device to indicate whether additional initial access latency is needed in the transaction.

During read data transfers, RWDS is a read data strobe with data values edge aligned with the transitions of RWDS.

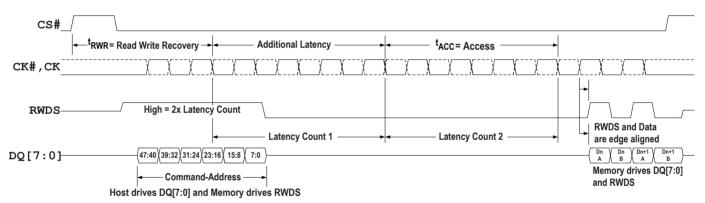

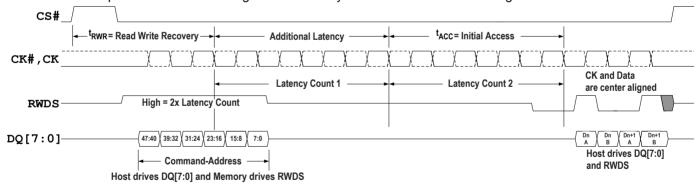

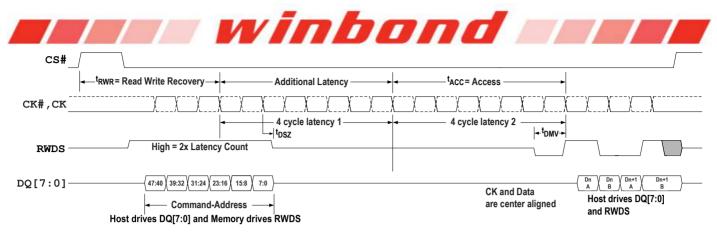

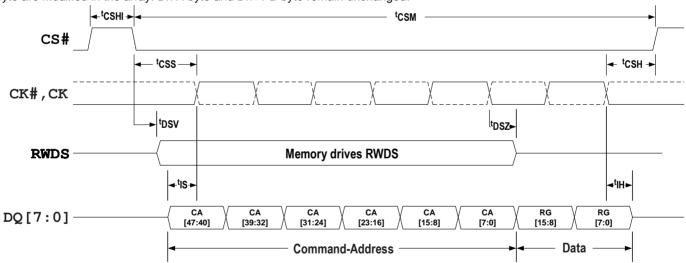

Figure 1 - Read Transaction, Additional Latency Count

During write data transfers, RWDS indicates whether each data byte transfer is masked with RWDS High (invalid and prevented from changing the byte location in a memory) or not masked with RWDS Low (valid and written to a memory). Data masking may be used by the host to byte align write data within a memory or to enable merging of multiple nonword aligned writes in a single burst write. During write transactions, data is center aligned with clock transitions.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

verse winbond =

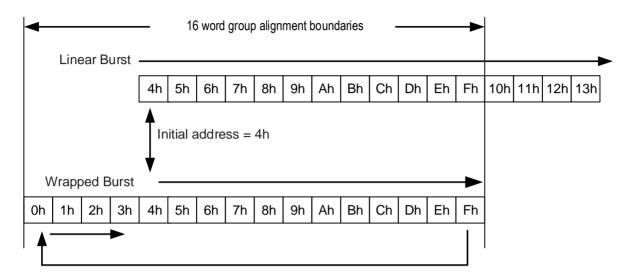

Read and write transactions are burst oriented, transferring the next sequential word during each clock cycle. Each individual read or write transaction can use either a wrapped or linear burst sequence.

Figure 2 - Linear Versus Wrapped Burst Sequence

During wrapped transactions, accesses start at a selected location and continue to the end of a configured word group aligned boundary, then wrap to the beginning location in the group, then continue back to the starting location. Wrapped bursts are generally used for critical word first cache line fill read transactions. During linear transactions, accesses start at a selected location and continue in a sequential manner until the transaction is terminated when CS# returns High. Linear transactions are generally used for large contiguous data transfers such as graphic images. Since each transaction command selects the type of burst sequence for that transaction, wrapped and linear bursts transactions can be dynamically intermixed as needed.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

- 10 -

### HYPERBUS TRANSACTION DETAILS

#### 7.1 **Command/Address Bit Assignments**

All HyperRAM bus transactions can be classified as either read or write. A bus transaction is started with CS# going Low with clock in idle state (CK=Low and CK#=High). The first three clock cycles transfer three words of Command/Address (CA0, CA1, CA2) information to define the transaction characteristics. The Command/Address words are presented with DDR timing, using the first six clock edges. The following characteristics are defined by the Command/Address information:

- Read or Write transaction

- Address Space: memory array space or register space

- Register space is used to access Device Identification (ID) registers and Configuration Registers (CR) that identify the device characteristics and determine the slave specific behavior of read and write transfers on the HyperBus interface.

- Whether a transaction will use a linear or wrapped burst sequence

- The target row (and half-page) address (upper order address)

- The target column (word within half-page) address (lower order address)

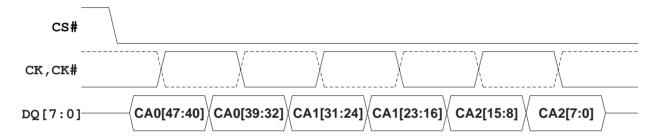

Figure 3 - Command-Address (CA) Sequence

#### Notes:

- 1. Figure shows the initial three clock cycles of all transactions on the HyperBus.

- 2. CK# of differential clock is shown as dashed line waveform.

- 3. CA information is "center aligned" with the clock during both Read and Write transactions.

- 4. Data bits in each byte are always in high to low order with bit 7 on DQ7 and bit 0 on DQ0.

| Table 1 - CA | Bit Assignment | to DQ Sig | jnals |

|--------------|----------------|-----------|-------|

|              |                |           |       |

|              |                |           |       |

| Signal | CA0[47:40] | CA0[39:32] | CA1[31:24] | CA1[23:16] | CA2[15:8] | CA2[7:0] |

|--------|------------|------------|------------|------------|-----------|----------|

| DQ[7]  | CA[47]     | CA[39]     | CA[31]     | CA[23]     | CA[15]    | CA[7]    |

| DQ[6]  | CA[46]     | CA[38]     | CA[30]     | CA[22]     | CA[14]    | CA[6]    |

| DQ[5]  | CA[45]     | CA[37]     | CA[29]     | CA[21]     | CA[13]    | CA[5]    |

| DQ[4]  | CA[44]     | CA[36]     | CA[28]     | CA[20]     | CA[12]    | CA[4]    |

| DQ[3]  | CA[43]     | CA[35]     | CA[27]     | CA[19]     | CA[11]    | CA[3]    |

| DQ[2]  | CA[42]     | CA[34]     | CA[26]     | CA[18]     | CA[10]    | CA[2]    |

| DQ[1]  | CA[41]     | CA[33]     | CA[25]     | CA[17]     | CA[9]     | CA[1]    |

| DQ[0]  | CA[40]     | CA[32]     | CA[24]     | CA[16]     | CA[8]     | CA[0]    |

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

- 11 -

Publication Release Date: Sep. 03, 2020

### Table 2 - Command/Address Bit Assignments

| CA Bit# | Bit Name                      | Bit Function                                                                                                                                                                                                                                                                                                                           |

|---------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47      | R/W#                          | Identifies the transaction as a read or write.  R/W#=1 indicates a Read transaction  R/W#=0 indicates a Write transaction                                                                                                                                                                                                              |

| 46      | Address Space<br>(AS)         | Indicates whether the read or write transaction accesses the memory or register space.  AS=0 indicates memory space AS=1 indicates the register space The register space is used to access device ID and Configuration registers.                                                                                                      |

| 45      | Burst Type                    | Indicates whether the burst will be linear or wrapped. Burst Type=0 indicates wrapped burst Burst Type=1 indicates linear burst                                                                                                                                                                                                        |

| 44-16   | Row & Upper<br>Column Address | Row & Upper Column component of the target address:  System word address bits A31-A3  Any upper Row address bits not used by a particular device density should be set to 0 by the host controller master interface. The size of Rows and therefore the address bit boundary between Row and Column address is slave device dependent. |

| 15-3    | Reserved                      | Reserved for future column address expansion. Reserved bits are don't care in current HyperBus devices but should be set to 0 by the host controller master interface for future compatibility.                                                                                                                                        |

| 2-0     | Lower Column<br>Address       | Lower Column component of the target address:  System word address bits A2-A0 selecting the starting word within a half-page.                                                                                                                                                                                                          |

### Notes:

- 1. The Column address selects the burst transaction starting word location within a Row. The Column address is split into an upper and lower portion. The upper portion selects an 8-word (16-byte) Half-page and the lower portion selects the word within a Half-page where a read or write transaction burst starts.

- 2. The initial read access time starts when the Row and Upper Column (Half-page) address bits are captured by a slave interface. Continuous linear read burst is enabled by memory devices internally interleaving access to 16 byte half-pages.

- 3. HyperBus protocol address space limit, assuming:

29 Row &Upper Column address bits

3 Lower Column address bits

Each address selects a word wide (16 bit = 2 byte) data value

29 + 3 = 32 address bits = 4G addresses supporting 8Gbyte (64Gbit) maximum address space

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

Publication Release Date: Sep. 03, 2020

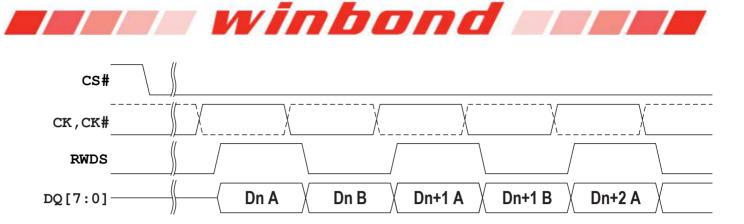

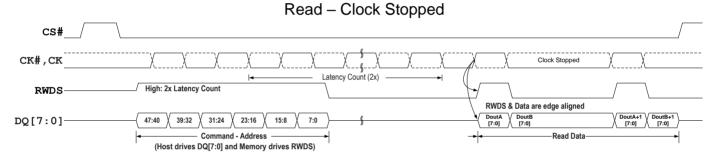

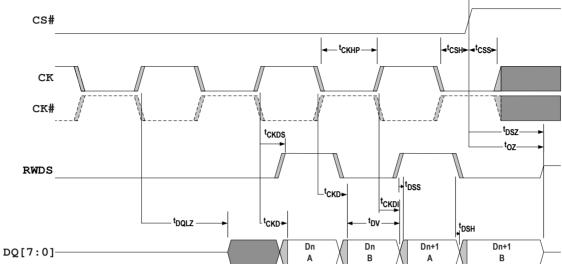

Figure 4 - Data Placement during a Read Transaction

#### Notes:

- 1. Figure shows a portion of a Read transaction on the HyperBus. CK# of differential clock is shown as dashed line waveform.

- 2. Data is "edge aligned" with the RWDS serving as a read data strobe during read transactions.

- 3. Data is always transferred in full word increments (word granularity transfers).

- 4. Word address increments in each clock cycle. Byte A is between RWDS rising and falling edges and is followed by byte B between RWDS falling and rising edges, of each word.

- 5. Data bits in each byte are always in high to low order with bit 7 on DQ7 and bit 0 on DQ0.

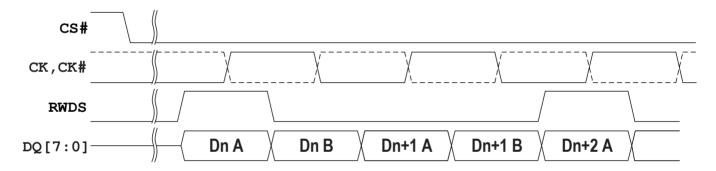

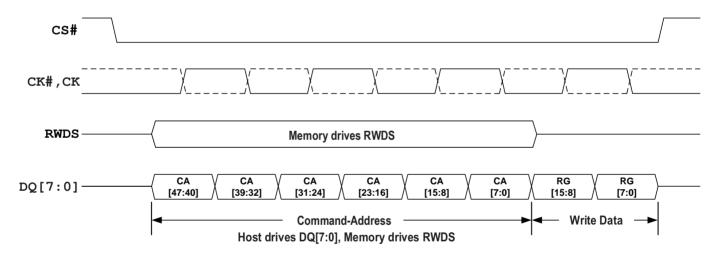

Figure 5 - Data Placement during a Write Transaction

#### Notes:

- 1. Figure shows a portion of a Write transaction on the HyperBus.

- 2. Data is "center aligned" with the clock during a Write transaction.

- 3. RWDS functions as a data mask during write data transfers with initial latency. Masking of the first and last byte is shown to illustrate an unaligned 3 byte write of data.

- 4. RWDS is not driven by the master during write data transfers with zero initial latency. Full data words are always written in this case. RWDS may be driven Low or left High-Z by the slave in this case.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

#### **Read Transactions**

The HyperBus master begins a transaction by driving CS# Low while clock is idle. The clock then begins toggling while CA words are transferred.

In CA0, CA[47] = 1 indicates that a Read transaction is to be performed. CA[46] = 0 indicates the memory space is being read or CA[46] = 1 indicates the register space is being read. CA[45] indicates the burst type (wrapped or linear). Read transactions can begin the internal array access as soon as the row and upper column address has been presented in CA0 and CA1 (CA[47:16]). CA2 (CA(15:0]) identifies the target Word address within the chosen row.

The HyperBus master then continues clocking for a number of cycles defined by the latency count setting in Configuration Register 0. The initial latency count required for a particular clock frequency is based on RWDS. If RWDS is High during the CA cycles, an additional latency count is inserted. Once these latency clocks have been completed the memory starts to simultaneously transition the Read-Write Data Strobe (RWDS) and output the target data.

New data is output edge aligned with every transition of RWDS. Data will continue to be output as long as the host continues to transition the clock while CS# is Low. However, the HyperRAM device may stop RWDS transitions with RWDS Low, between the deliveries of words, in order to insert latency between words when crossing memory array boundaries.

Wrapped bursts will continue to wrap within the burst length and linear burst will output data in a sequential manner across row boundaries. When a linear burst read reaches the last address in the array, continuing the burst beyond the last address will provide data from the beginning of the address range. Read transfers can be ended at any time by bringing CS# High when the clock is idle.

The clock is not required to be free-running. The clock may remain idle while CS# is High.

Figure 6 - Read Transaction with Additional Initial Latency

#### Notes:

- 1. Transactions are initiated with CS# falling while CK=Low and CK#=High.

- 2. CS# must return High before a new transaction is initiated.

- 3. CK# is the complement of the CK signal.CK# of a differential clock is shown as a dashed line waveform.

- 4. Read access array starts once CA[23:16] is captured.

- 5. The read latency is defined by the initial latency value in a configuration register.

- 6. In this read transaction example the initial latency count was set to four clocks.

- 7. In this read transaction a RWDS High indication during CA delays output of target data by an additional four clocks.

- 8. The memory device drives RWDS during read transactions.

- 9. For register read, the output data Dn A is RG[15:8], Dn B is RG[7:0], Dn+1 A is RG[15:8], Dn+1 B is RG[7:0].

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

### 7.3 Write Transactions (Memory Array Write)

The HyperBus master begins a transaction by driving CS# Low while clock is idle. Then the clock begins toggling while CA words are transferred

In CA0, CA[47] = 0 indicates that a Write transaction is to be performed, CA[46] = 0 indicates the memory space is being written. CA[45] indicates the burst type (wrapped or linear). Write transactions can begin the internal array access as soon as the row and upper column address has been presented in CA0 and CA1 (CA[47:16]). CA2 (CA(15:0]) identifies the target word address within the chosen row.

The HyperBus master then continues clocking for a number of cycles defined by the latency count setting in configuration register 0. The initial latency count required for a particular clock frequency is based on RWDS. If RWDS is High during the CA cycles, an additional latency count is inserted.

Once these latency clocks have been completed the HyperBus master starts to output the target data. Write data is center aligned with the clock edges. The first byte of data in each word is captured by the memory on the rising edge of CK and the second byte is captured on the falling edge of CK.

During the CA clock cycles, RWDS is driven by the memory.

During the write data transfers, RWDS is driven by the host master interface as a data mask. When data is being written and RWDS is High the byte will be masked and the array will not be altered. When data is being written and RWDS is Low the data will be placed into the array. Because the master is driving RWDS during write data transfers, neither the master nor the HyperRAM device is able to indicate a need for latency within the data transfer portion of a write transaction. The acceptable write data burst length setting is also shown in configuration register 0.

Data will continue to be transferred as long as the HyperBus master continues to transition the clock while CS# is Low. Legacy format wrapped bursts will continue to wrap within the burst length. Hybrid wrap will wrap once then switch to linear burst starting at the next wrap boundary. Linear burst accepts data in a sequential manner across page boundaries. Write transfers can be ended at any time by bringing CS# High when the clock is idle.

When a linear burst write reaches the last address in the memory array space, continuing the burst will write to the beginning of the address range.

The clock is not required to be free-running. The clock may remain idle while CS# is High.

Figure 7 - Write Transaction with Additional Initial Latency

#### Notes:

- 1. Transactions must be initiated with CK=Low and CK#=High.

- 2. CS# must return High before a new transaction is initiated.

- 3. During CA, RWDS is driven by the memory and indicates whether additional latency cycles are required.

- 4. In this example, RWDS indicates that additional initial latency cycles are required.

- 5. At the end of CA cycles the memory stops driving RWDS to allow the host HyperBus master to begin driving RWDS. The master must drive RWDS to a valid Low before the end of the initial latency to provide a data mask preamble period to the slave.

- 6. During data transfer, RWDS is driven by the host to indicate which bytes of data should be either masked or loaded into the array.

- 7. The figure shows RWDS masking byte Dn A and byte Dn+1 B to perform an unaligned word write to bytes Dn B and Dn+1 A.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

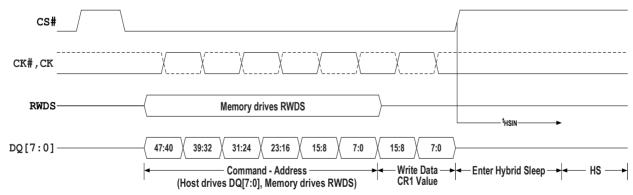

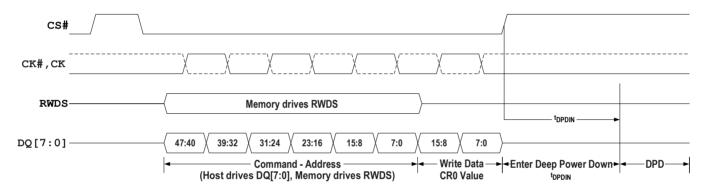

### Write Transactions without Initial Latency (Register Write)

A Write transaction starts with the first three clock cycles providing the Command/Address information indicating the transaction characteristics. CA0 may indicate that a Write transaction is to be performed and also indicates the address space and burst type (wrapped or linear).

Writes without initial latency are used for register space writes. HyperRAM device write transactions with zero latency mean that the CA cycles are followed by write data transfers. Writes with zero initial latency, do not have a turnaround period for RWDS. The HyperRAM device will always drive RWDS during the CA period to indicate whether extended latency is required for a transaction that has initial latency. However, the RWDS is driven before the HyperRAM devices has received the first byte of CA i.e. before the HyperRAM device knows whether the transaction is a read or write to register space. In the case of a write with zero latency, the RWDS state during the CA period does not affect the initial latency of zero. Since master write data immediately follows the CA period in this case, the HyperRAM device may continue to drive RWDS Low or may take RWDS to High-Z during write data transfer. The master must not drive RWDS during Writes with zero latency. Writes with zero latency do not use RWDS as a data mask function. All bytes of write data are written (full word writes).

The first byte of data in each word is presented on the rising edge of CK and the second byte is presented on the falling edge of CK. Write data is center aligned with the clock inputs. Write transfers can be ended at any time by bringing CS# High when clock is idle. The clock is not required to be free-running.

Figure 8 - Write Operation without Initial Latency

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

- 16 -

### **MEMORY SPACE**

#### 8.1 HyperBus Interface Memory Space addressing

Table 3 - Memory Space Address Map (word based - 16 bits)

| Unit Type                 | Count              | System Word<br>Address Bits | CA Bits | Notes                            |

|---------------------------|--------------------|-----------------------------|---------|----------------------------------|

| Rows within 128 Mb device | 16384 (Rows)       | A22~A9                      | 35~22   |                                  |

| Row                       | 1 (row)            | A8~A3                       | 21~16   | 512 (word addresses)<br>1K bytes |

| Half-Page                 | 8 (word addresses) | A2~A0                       | 2~0     | 8 words (16 bytes)               |

Table 4 - Memory Space Address Map (word based - 16 bits)

|                        |                          | 128Mb      |

|------------------------|--------------------------|------------|

| Row Address            | System Word Address Bits | A22~A9     |

| Row Address            | CA Bits                  | 35~22      |

| Column Address         | System Word Address Bits | A8~A0      |

| Column Address         | CA Bits                  | 21~16; 2~0 |

| Holf Dogo (HD) Addroop | System Word Address Bits | A8~A3      |

| Half-Page (HP) Address | CA Bits                  | 21~16      |

| Word of HP Address     | System Word Address Bits | A2~A0      |

| Word of TIP Address    | CA Bits                  | 2~0        |

#### Notes:

- 1. Each row has 64 Half-pages. Each Half-page has 8 words. Each column has 512 words (1K bytes).

- 2. Half-Page address is also named as upper column address. Word of HP address is also named as lower column address.

#### **Density and Row Boundaries** 8.1.1

The DRAM array size (density) of the device can be determined from the total number of system address bits used for the row and column addresses as indicated by the Row Address Bit Count and Column Address Bit Count fields in the ID0 register. For example: a 64-Mbit HyperRAM device has 9 column address bits and 13 row address bits for a total of 22 word address bits =  $2^{22}$  = 4M words = 8M bytes. The 9 column address bits indicate that each row holds  $2^9$  = 512 words = 1K bytes. The row address bit count indicates there are 8192 rows to be refreshed within each array refresh interval. The row count is used in calculating the refresh interval.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

### **REGISTER SPACE**

### **HyperBus Interface Register Addressing**

When CA[46] is 1 a read or write transaction accesses the Register Space.

### Table 5 - Register Space Address Map (for 2 Die DDP 128Mb)

| Register                                   | System<br>Address | _          | _    | _       | 31~27 | 26~24 | 23~22 | 21~19 | 18~11 | 10~3  | _    | 2~0 |

|--------------------------------------------|-------------------|------------|------|---------|-------|-------|-------|-------|-------|-------|------|-----|

|                                            | CA Bits           | 47         | 46   | 45      | 44~40 | 39~37 | 36~35 | 34~32 | 31~24 | 23~16 | 15~8 | 7~0 |

| 128 Mb<br>Identification Registe           | r 0- Die 0        |            | Re   | ead     |       | 000b  | 00b   | 000b  | 00h   | 00h   | 00h  | 00h |

| 128 Mb<br>Identification Registe           | r 0- Die 1        | Read       |      | 000b    | 01b   | 000b  | 00h   | 00h   | 00h   | 00h   |      |     |

| 128 Mb<br>Identification Register 1- Die 0 |                   | Read       |      | 000b    | 00b   | 000b  | 00h   | 00h   | 00h   | 01h   |      |     |

| 128 Mb<br>Identification Register 1- Die 1 |                   | Read       |      | 000b    | 01b   | 000b  | 00h   | 00h   | 00h   | 01h   |      |     |

| 128 Mb<br>Configuration Register 0- Die 0  |                   | Read/Write |      | 000b    | 00b   | 000b  | 01h   | 00h   | 00h   | 00h   |      |     |

| 128 Mb<br>Configuration Register 0- Die 1  |                   | Read/Write |      |         | 000b  | 01b   | 000b  | 01h   | 00h   | 00h   | 00h  |     |

| 128 Mb<br>Configuration Register 1- Die 0  |                   | Read/Write |      | 000b    | 00b   | 000b  | 01h   | 00h   | 00h   | 01h   |      |     |

| 128 Mb<br>Configuration Registe            | er 1- Die 1       |            | Read | I/Write |       | 000b  | 01b   | 000b  | 01h   | 00h   | 00h  | 01h |

#### Note:

CA45 may be either 0 or 1 for either wrapped or linear read. CA45 must be 1 as only linear single word register writes are supported.

The Burst type (wrapped/linear) definition is not supported in Register Reads. Hence C0h/E0h have the same effect.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

- 18 -

Publication Release Date: Sep. 03, 2020

### 9.2 Register Space Access

Register default values are loaded upon power-up or hardware reset. The registers can be altered at any time while the device is in the standby state.

Loading a register is accomplished with write transaction without initial latency using a single 16-bit word write transaction.

Each register is written with a separate single word write transaction. Register write transactions have zero latency, the single word of data immediately follows the CA. RWDS is not driven by the host during the write because RWDS is always driven by the memory during the CA cycles to indicate whether a memory array refresh is in progress. Because a register space write goes directly to a register, rather than the memory array, there is no initial write latency, related to an array refresh that may be in progress. In a register write, RWDS is also not used as a data mask because both bytes of a register are always written and never masked.

Reserved register fields must be written with their default value. Writing reserved fields with other than default values may produce undefined results.

**Note:** The host must not drive RWDS during a write to register space.

Note: The RWDS signal is driven by the memory during the CA period based on whether the memory array is being refreshed. This refresh indication does not affect the writing of register data.

Note: The RWDS signal returns to high impedance after the CA period. Register data is never masked. Both data bytes of the register data are loaded into the selected register.

Reading of a register is accomplished with read transaction with double initial latency using a single 16 bit read transaction. If more than one word is read, the same register value is repeated in each word read. The contents of the register is returned in the same manner as reading array data, with two latency counts, based on the state of RWDS during the CA period. The latency count is defined in the Configuration Register 0 Read Latency field (CR0[7:4]).

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

Publication Release Date: Sep. 03, 2020

### 9.3 Device Identification Registers

There are two read only, non-volatile, word registers, that provide information on the device selected when CS# is low. The device information fields identify:

- Manufacture

- Type

- Density

- Row address bit count

- Column address bit count

Table 6 - ID Register 0 Bit Assignments

| Bits    | Function                 | Settings (Binary)                   |

|---------|--------------------------|-------------------------------------|

|         |                          | 00b - Die 0                         |

| [15:14] | DDP Die Address          | 01b - Die 1                         |

| [10.14] | DDI Die Address          | 10b - Reserved                      |

|         |                          | 11b - Reserved                      |

| [13]    | Reserved                 | 0b - default                        |

| [12:8]  | Row Address Bit Count    | 01100b - The 13th row address bits* |

| [7:4]   | Column Address Bit Count | 1000b - The 9th column address bits |

| [3:0]   | Manufacturer             | 0110b - Winbond                     |

Note: For each die.

Table 7 - ID Register 1 Bit Assignments

| Bits   | Function    | Settings (Binary)                                        |

|--------|-------------|----------------------------------------------------------|

| [15:4] | Reserved    | 0000_0000_0000b (default)                                |

| [3:0]  | Device Type | 0001b – HyperRAM 2.0<br>0000b, 0010b to 1111b - Reserved |

### 9.4 Configuration Register 0

Configuration Register 0 (CR0) is used to define the power state and access protocol operating conditions for the HyperRAM device. Configurable characteristics include:

- Wrapped Burst Length (16, 32, 64, or 128 byte aligned and length data group)

- Wrapped Burst Type

- Legacy wrapped burst (sequential access with wrap around within a selected length and aligned group)

- Hybrid wrap (Legacy wrapped burst once then linear burst at start of the next sequential group)

- Initial Latency

- Fixed Latency

- The memory array read or writes transaction use fixed latency will always indicate a refresh latency and delay the read data transfer accordingly.

- Output Drive Strength

- Deep Power Down Mode

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

Publication Release Date: Sep. 03, 2020

Table 8 - Configuration Register 0 Bit Assignments

| CR0 Bit | Function                  | Settings (Binary)                                                                                                                                                                                                                                                                                      |

|---------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15]    | Deep Power Down<br>Enable | 1b - Normal operation (default) 0b - Deep Power Down mode Note: Only the accessed die get into Deep Power Down ( DPD) mode when write "0" to CR0[15], these stacked dual dies in DDP package are not able to stay at DPD mode simultaneously.                                                          |

| [14:12] | Drive Strength            | 000b - 34 ohms (default) 001b - 115 ohms 010b - 67 ohms 011b - 46 ohms 100b - 34 ohms 101b - 27 ohms 110b - 22 ohms 111b - 19 ohms                                                                                                                                                                     |

| [11:8]  | Reserved                  | 1b - Reserved (default) Reserved for Future Use. When writing this register, these bits should be set to 1 for future compatibility.                                                                                                                                                                   |

| [7:4]   | Initial Latency           | 0000b - 5 Clock Latency @ 133MHz Max Frequency 0001b - 6 Clock Latency @ 166MHz Max Frequency 0010b - 7 Clock Latency @ 200MHz Max Frequency (default) 0011b - Reserved 0100b - Reserved 1101b - Reserved 1110b - 3 Clock Latency @ 83MHz Max Frequency 1111b - 4 Clock Latency @ 100MHz Max Frequency |

| [3]     | Fixed Latency             | 1b - Fixed 2 times Initial Latency (default) Note: CR0[3] of each die of this DDP package must be programmed as "1" (Fixed Latency mode).                                                                                                                                                              |

| [2]     | Hybrid Burst Enable       | 0b: Wrapped burst sequences to follow hybrid burst sequencing 1b: Wrapped burst sequences in legacy wrapped burst manner (default)                                                                                                                                                                     |

| [1:0]   | Burst Length              | 00b - 128 bytes<br>01b - 64 bytes<br>10b - 16 bytes<br>11b - 32 bytes (default)                                                                                                                                                                                                                        |

#### 9.4.1 **Wrapped Burst**

A wrapped burst transaction accesses memory within a group of words aligned on a word boundary matching the length of the configured group. Wrapped access groups can be configured as 16, 32, 64, or 128 bytes alignment and length. During wrapped transactions, access starts at the CA selected location within the group, continues to the end of the configured word group aligned boundary, then wraps around to the beginning location in the group, then continues back to the starting location. Wrapped bursts are generally used for critical word first instruction or data cache line fill read accesses.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

### **Hvbrid Burst**

The beginning of a hybrid burst will wrap within the target address wrapped burst group length before continuing to the next half-page of data beyond the end of the wrap group. Continued access is in linear burst order until the transfer is ended by returning CS# High. This hybrid of a wrapped burst followed by a linear burst starting at the beginning of the next burst group, allows multiple sequential address cache lines to be filled in a single access. The first cache line is filled starting at the critical word. Then the next sequential line in memory can be read in to the cache while the first line is being processed.

Table 9 - CR0[2] Control of Wrapped Burst Sequence

| Bit | Default Value | Name                                                                                                                                                         |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   |               | Hybrid Burst Enable CR0[2]= 0b: Wrapped burst sequences to follow hybrid burst sequencing CR0[2]= 1b: Wrapped burst sequences in legacy wrapped burst manner |

Table 10 - Example Wrapped Burst Sequences (HyperBus Addressing)

| Burst Type | Wrap Boundary<br>(Bytes)     | Start Address<br>(Hex) | Address Sequence (Hex) (Words)                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hybrid 128 | 128 Wrap once<br>then Linear | XXXXXX03               | 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D, 1E, 1F, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D, 2E, 2F, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 3A, 3B, 3C, 3D, 3E, 3F, 00, 01, 02  (Wrap complete, now linear beyond the end of the initial 128 byte wrap group) 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 4A, 4B, 4C, 4D, 4E, 4F, 50, 51, |

| Hybrid 64  | 64 Wrap once<br>then Linear  | XXXXXX03               | 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D, 1E, 1F, 00, 01, 02, (Wrap complete, now linear beyond the end of the initial 64 byte wrap group) 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D, 2E, 2F, 30, 31,                                                                                                                                  |

| Hybrid 64  | 64 Wrap once<br>then Linear  | XXXXXX2E               | 2E, 2F, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 3A, 3B, 3C, 3D, 3E, 3F, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D, (Wrap complete, now linear beyond the end of the initial 64 byte wrap group) 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 4A, 4B, 4C, 4D, 4E, 4F, 50, 51,                                                                                                                                  |

| Hybrid 16  | 16 Wrap once<br>then Linear  | XXXXXX02               | 02, 03, 04, 05, 06, 07, 00, 01,<br>(Wrap complete, now linear beyond the end of the initial 16 byte wrap group)<br>08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12,                                                                                                                                                                                                                                                        |

| Hybrid 16  | 16 Wrap once<br>then Linear  | XXXXXX0C               | OC, OD, OE, OF, 08, 09, 0A, OB, (Wrap complete, now linear beyond the end of the initial 16 byte wrap group) 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A,                                                                                                                                                                                                                                                              |

| Hybrid 32  | 32 Wrap once<br>then Linear  | XXXXXX0A               | 0A, 0B, 0C, 0D, 0E, 0F, 00, 01, 02, 03, 04, 05, 06, 07, 08, 09<br>(Wrap complete, now linear beyond the end of the initial 32 byte wrap group)<br>10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A,                                                                                                                                                                                                                         |

| Wrap 64    | 64                           | XXXXXX03               | 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D, 1E, 1F, 00, 01, 02,                                                                                                                                                                                                                                                                                       |

| Wrap 64    | 64                           | XXXXXX2E               | 2E, 2F, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 3A, 3B, 3C, 3D, 3E, 3F, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D,                                                                                                                                                                                                                                                                                       |

| Wrap 16    | 16                           | XXXXXX02               | 02, 03, 04, 05, 06, 07, 00, 01,                                                                                                                                                                                                                                                                                                                                                                                       |

| Wrap 16    | 16                           | XXXXXX0C               | 0C, 0D, 0E, 0F, 08, 09, 0A, 0B,                                                                                                                                                                                                                                                                                                                                                                                       |

| Wrap 32    | 32                           | XXXXXX0A               | 0A, 0B, 0C, 0D, 0E, 0F, 00, 01, 02, 03, 04, 05, 06, 07, 08, 09,                                                                                                                                                                                                                                                                                                                                                       |

| Linear     | Linear Burst                 | XXXXXX03               | 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12, 13, 14, 15, 16, 17, 18,                                                                                                                                                                                                                                                                                                                               |

Note: Burst across die boundary is not supported in multi-die stack.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

### 9.4.3 Initial Latency

Memory Space read and write transactions or Register Space read transactions require some initial latency to open the row selected by the CA. This initial latency is tACC. The number of latency clocks needed to satisfy tACC depends on the HyperBus frequency and can vary from 3 to 7 clocks. The value in CR0[7:4] selects the number of clocks for initial latency. The default value is 7 clocks, allowing for operation up to a maximum frequency of 200MHz prior to the host system setting a lower initial latency value that may be more optimal for the system.

In the event a distributed refresh is required at the time a Memory Space read or writes transaction or Register Space read transaction begins, the RWDS signal goes High during the CA to indicate that an additional initial latency is being inserted to allow a refresh operation to complete before opening the selected row.

Register Space write transactions always have zero initial latency. RWDS may be High or Low during the CA period. The level of RWDS during the CA period does not affect the placement of register data immediately after the CA, as there is no initial latency needed to capture the register data. A refresh operation may be performed in the memory array in parallel with the capture of register data.

### 9.4.4 Fixed Latency

A configuration register option bit CR0[3] is provided to make all Memory Space read and write transactions or Register Space read transactions require the same initial latency by always driving RWDS High during the CA to indicate that two initial latency periods are required. This fixed initial latency is independent of any need for a distributed refresh; it simply provides a fixed (deterministic) initial latency for all of these transaction types. The fixed latency option may simplify the design of some HyperBus memory controllers or ensure deterministic transaction performance. Fixed latency is the default POR or reset configuration. The system must not clear this configuration bit to "0b".

### 9.4.5 Drive Strength

DQ and RWDS signal line loading, length, and impedance vary depending on each system design. Configuration register bits CR0[14:12] provide a means to adjust the DQ[7:0] and RWDS signal output impedance to customize the DQ and RWDS signal impedance to the system conditions to minimize high speed signal behaviors such as overshoot, undershoot, and ringing. The default POR or reset configuration value is 000b to select the mid-point of the available output impedance options.

The impedance values shown are typical for both pull-up and pull-down drivers at typical silicon process conditions, nominal operating voltage (1.8V or 3.0V) and 50°C. The impedance values may vary from the typical values depending on the Process, Voltage, and Temperature (PVT) conditions. Impedance will increase with slower process, lower voltage, or higher temperature. Impedance will decrease with faster process, higher voltage, or lower temperature.

Each system design should evaluate the data signal integrity across the operating voltage and temperature ranges to select the best drive strength settings for the operating conditions.

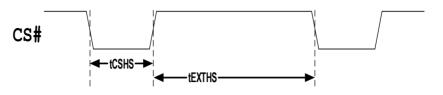

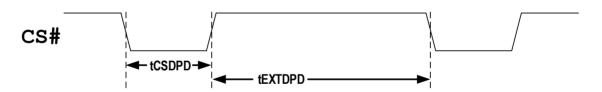

### 9.4.6 Deep Power Down

When the HyperRAM device is not needed for system operation, it may be placed in a very low power consuming state called Deep Power Down (DPD), by writing 0 to CR0[15]. When CR0[15] is cleared to 0, the device enters the DPD state within tDPDIN time and all refresh operations stop. The data in RAM is lost, (becomes invalid without refresh) during DPD state. Exiting DPD requires driving CS# Low then High, POR, or a reset. Only CS# and RESET# signals are monitored during DPD mode. All register contents are lost in Deep Power Down state and the device powers-up in its default state.

Note: In this DDP package, only the current programmed die can stay in Deep Power Down (DPD) mode and the previous programmed die in DPD mode will exit DPD when write "0" to CR0[15] to the current programmed die.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

Publication Release Date: Sep. 03, 2020

### 9.5 Configuration Register 1

Configuration Register 1 (CR1) is used to define the refresh array size, refresh rate and Hybrid Sleep for the HyperRAM device. Configurable characteristics include:

- Partial Array Refresh

- Hybrid Sleep State

- Refresh Rate

**Table 11 - Configuration Register 1 Bit Assignments**

| CR1 Bit | Function                     | Settings (Binary)                                                                                                                                                                                                                   |

|---------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15-8]  | Reserved                     | FFh - Reserved (default) Reserved for Future Use. When writing this register, these bits should keep FFh for future compatibility.                                                                                                  |

| [7]     | Reserved                     | 1b - Reserved (default) When writing this register, this bit should keep 1b.                                                                                                                                                        |

| [6]     | Master Clock Type            | 1b - Single Ended - CK (default) 0b - Differential - CK#, CK                                                                                                                                                                        |

| [5]     | Hybrid Sleep                 | 1b - Hybrid Sleep 0b - Normal operation (default) Note: Only the accessed die get into Hybrid Sleep mode when write "1" to CR1[5], these stacked dual dies in DDP package are not able to stay at Hybrid Sleep mode simultaneously. |

| [4:2]   | Partial Array Refresh        | 000b - Full Array (default) 001b - Bottom 1/2 Array 010b - Bottom 1/4 Array 011b - Bottom 1/8 Array 100b - None 101b - Top 1/2 Array 110b - Top 1/4 Array 111b - Top 1/8 Array Note: The array means default 64Mb density.          |

| [1:0]   | Distributed Refresh Interval | 10b - Reserved 11b - Reserved 00b - Reserved 01b - 4µS tCSM Note: CR1[1:0] is read only.                                                                                                                                            |

#### 9.5.1 **Master Clock Type**

Two clock types, namely single ended and differential, are supported by HyperRAM. CR1[6] selects which type to use.

#### 9.5.2 **Partial Array Refresh**

The partial array refresh configuration restricts the refresh operation in HyperRAM to a portion of the memory array specified by CR1[4:2]. This reduces the standby current. The default configuration refreshes the whole array.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

Publication Release Date: Sep. 03, 2020

### Hybrid Sleep

When the HyperRAM is not needed for system operation, it may be placed in Hybrid Sleep state if data in the device needs to be retained. Enter Hybrid Sleep state by writing 1 to CR1[5]. Bringing CS# Low will cause the device to exit HS state and set CR1[5] to 0. Also, POR, or a hardware reset will cause the device to exit Hybrid Sleep state. Note that a POR or a hardware reset disables refresh where the memory core data can potentially get lost.

Note: In this DDP package, only the current programmed die can stay in Hybrid sleep (HS) mode and the previous programmed die in HS mode will exit HS when write "0" to CR1[5] to the current programmed die.

#### 9.5.4 **Distributed Refresh Interval**

The DRAM array requires periodic refresh of all bits in the array. This can be done by the host system by reading or writing a location in each row within a specified time limit. The read or write access copies a row of bits to an internal buffer. At the end of the access the bits in the buffer are written back to the row in memory, thereby recharging (refreshing) the bits in the row of DRAM memory cells.

HyperRAM devices include self-refresh logic that will refresh rows automatically. The automatic refresh of a row can only be done when the memory is not being actively read or written by the host system. The refresh logic waits for the end of any active read or write before doing a refresh, if a refresh is needed at that time. If a new read or write begins before the refresh is completed, the memory will drive RWDS high during the CA period to indicate that an additional initial latency time is required at the start of the new access in order to allow the refresh operation to complete before starting the new access.

The required refresh interval for the entire memory array varies with temperature as shown in Table 12 - Array Refresh Interval per Temperature. This is the time within which all rows must be refreshed. Refresh of all rows could be done as a single batch of accesses at the beginning of each interval, in groups (burst refresh) of several rows at a time, spread throughout each interval, or as single row refreshes evenly distributed throughout the interval. The self-refresh logic distributes single row refresh operations throughout the interval so that the memory is not busy doing a burst of refresh operations for a long period, such that the burst refresh would delay host access for a long period.

Table 12 - Array Refresh Interval per Temperature

| Device Temperature (TCASE °C) | Array Refresh Interval (mS) | Array Rows | Recommended tcsm (µS) | CR1[1:0] |

|-------------------------------|-----------------------------|------------|-----------------------|----------|

| TCASE < 85                    | 64                          | 8192       | 4                     | 01b      |

The distributed refresh method requires that the host does not do burst transactions that are so long as to prevent the memory from doing the distributed refreshes when they are needed. This sets an upper limit on the length of read and writes transactions so that the refresh logic can insert a refresh between transactions. This limit is called the CS# low maximum time (tcsm). The tcsm value is determined by the array refresh interval divided by the number of rows in the array, then reducing this calculation by half to ensure that a distributed refresh interval cannot be entirely missed by a maximum length host access starting immediately before a distributed refresh is needed. Because tcsm is set to half the required distributed refresh interval, any series of maximum length host accesses that delay refresh operations will catch up on refresh operations at twice the rate required by the refresh interval divided by the number of rows.

The host system is required to respect the tCSM value by ending each transaction before violating tCSM. This can be done by host memory controller logic splitting long transactions when reaching the tCSM limit, or by host system hardware or software not performing a single read or write transaction that would be longer than tCSM.

As noted in Table 12 - Array Refresh Interval per Temperature, the array refresh interval is longer at lower temperatures such that tCSM could be increased to allow longer transactions. The host system can either use the tCSM value from the table for the maximum operating temperature or, may determine the current operating temperature from a temperature sensor in the system in order to set a longer distributed refresh interval.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

- 25 -

Publication Release Date: Sep. 03, 2020

### **Dual-Die-Package (DDP) Application**

#### 9.6.1 Die Stack Addressing

Table 13 - Die Stack Addressing

| HyperBus System Address   |                     |  |  |  |  |  |

|---------------------------|---------------------|--|--|--|--|--|

| Die 0 03FFFFFh ~ 0000000h |                     |  |  |  |  |  |

| Die 1                     | 07FFFFFh ~ 0400000h |  |  |  |  |  |

### **Burst Operations - Die Boundary Crossing**

Burst operation can be performed within one die. However, Burst reads and writes are not allowed crossing die boundaries.

#### 9.6.3 Die number assignment

Each die in a DDP is allocated with different die number (Die 0 and Die 1).

#### 9.6.4 Latency mode

For this DDP package Variable Latency mode is not allowed. Every operation must be under fixed latency mode and the CR0 [3] must be programmed as "1". The CR0 [3] is defined as below.

| CR0 Bit | Function             | Settings (Binary)                                                                                                                         |

|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [3]     | Fixed Latency Enable | 1b - Fixed 2 times Initial Latency (default) Note: CR0[3] of each die of this DDP package must be programmed as "1" (Fixed Latency mode). |

In fixed latency mode, when CS# asserted LOW,

- 1. The RWDS signal of each die of DDP will always drive to HIGH during CA phase;

- 2. The RWDS signal of the non-selected die of DDP will always drive to Hi-Z after CA phase;

- 3. The RWDS signal of the selected die of DDP will drive to L after CA phase.

#### IO pad capacitance

For this DDP package all IO pad of each stacked die share same IO pin of package. It means that the IO capacitance of each IO pin of package will be 2 times than an IO pad of each stacked die.

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

### **Current consumption**

For this DDP package the current consumption of standby will be 2 times than the consumption of each stacked die.

#### 9.6.7 **Partial Refresh**

For this DDP package the area under partial refresh will be allocated into partial area of each stacked die. The CR1[4:2] must be programmed chip by chip.

| CR1 Bit | Function              | Settings (Binary)                                                                                                                                         |  |  |  |  |  |

|---------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [4:2]   | Partial Array Refresh | 000b - Full Array (default) 001b - Bottom 1/2 Array 010b - Bottom 1/4 Array 011b - Bottom 1/8 Array 100b - None 101b - Top 1/2 Array 110b - Top 1/4 Array |  |  |  |  |  |

#### Hybrid Sleep Mode (HSM) and Deep Power Down (DPD) mode 9.6.8

For this DDP package only one of stacked die can be either in HSM mode or DPD mode. It is not feasible to program all of stacked die in HSM or DPD mode.

| CR0 Bit | Function                  | Settings (Binary)                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15]    | Deep Power Down<br>Enable | <ul> <li>1b - Normal operation (default)</li> <li>0b - Writing 0 to CR0[15] causes the device to enter Deep Power Down (DPD)</li> <li>Notes:</li> <li>1. HyperRAM will automatically set the value of CR0[15] to "1" after exit DPD.</li> <li>2. Only the current programmed die can stay in Deep Power Down (DPD) mode and the previous programmed die in DPD mode will exit DPD when write "0" to CR0[15] to the current programmed die.</li> </ul> |

| CR1 Bit | Function     | Settings (Binary)                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [5]     | Hybrid Sleep | 1b - Writing 1 to CR1[5] causes the device to enter Hybrid Sleep (HS) State 0b - Normal operation (default)  Note:  Only the current programmed die can stay in Hybrid sleep (HS) mode and the previous programmed die in HS mode will exit HS when write "0" to CR1[5] to the current programmed die. |  |  |  |  |  |

The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

- 27 -

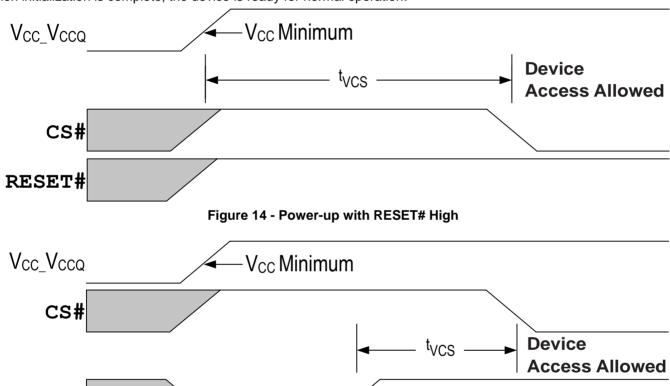

### 10. INTERFACE STATES

#### 10.1 IO condition of interface states

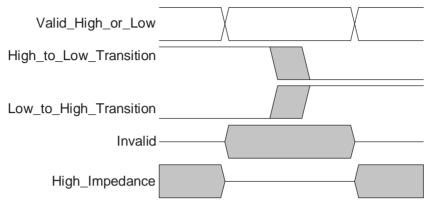

Below Interface States table describes the required value of each signal for each interface state.

#### **Table 14 - Interface States**

| Interface State                                           | Vcc / Vccq         | CS# | CK, CK# | DQ7-DQ0                                   | RWDS                          | RESET# |

|-----------------------------------------------------------|--------------------|-----|---------|-------------------------------------------|-------------------------------|--------|

| Power-Off                                                 | < V <sub>LKO</sub> | Х   | Х       | High-Z                                    | High-Z                        | Х      |

| Power-On (Cold) Reset                                     | Vcc / Vccq min     | Х   | Х       | High-Z                                    | High-Z                        | Х      |

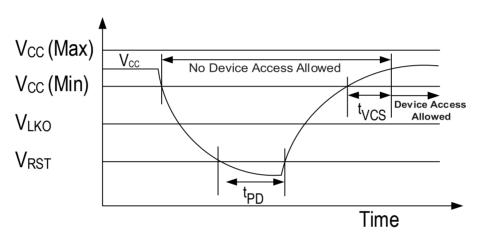

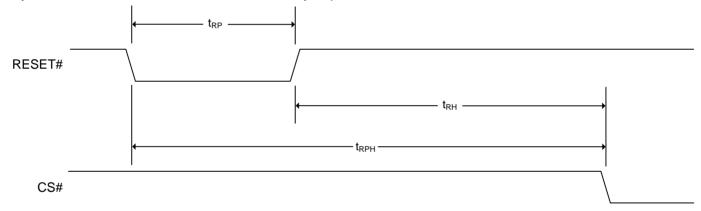

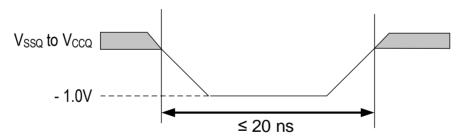

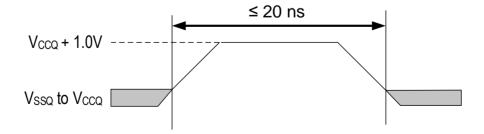

| Hardware (Warm) Reset                                     | Vcc / Vccq min     | Х   | Х       | High-Z                                    | High-Z                        | L      |