# THCX222R10

High Performance Re-driver with Linear Equalization

# **General Description**

THCX222R10 is a high performance bi-directional active re-driver for serial links with data rates up to 10Gbps.

THCX222R10 features a continuous time linear equalizer (CTLE) to provide a boost up to +14.8dB at 5 GHz. It opens an input eye completely closed due to inter-symbol interference (ISI) induced by the inter-connect mediums.

### Features

- Signal Conditioning with Linear Equalizer

- Linear Equalization up to +14.8dB@5GHz

- Adjustable Voltage Output Swing Linear Range

- Adjustable Receiver Equalization and DC Gain

- Support USB 3.1 Gen2

Receiver and LFPS Detect

- Single Supply Voltage (3.3V)

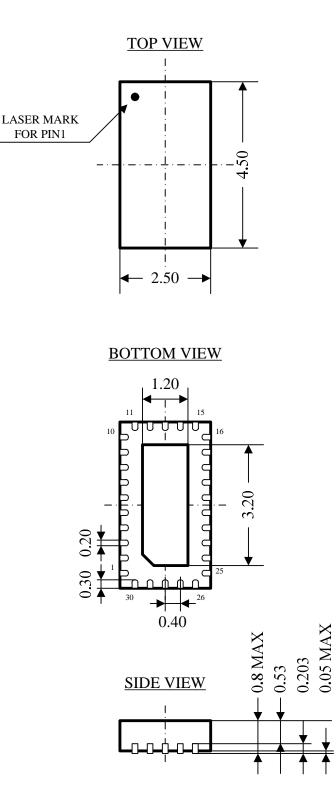

- Package : QFN30 (2.5mm x 4.5mm)

# Applications

- USB 3.1 Gen2

- USB Host and Devices

- Docking Stations

- Active Cable

- V-by-One<sup>®</sup> HS

- CML Interface

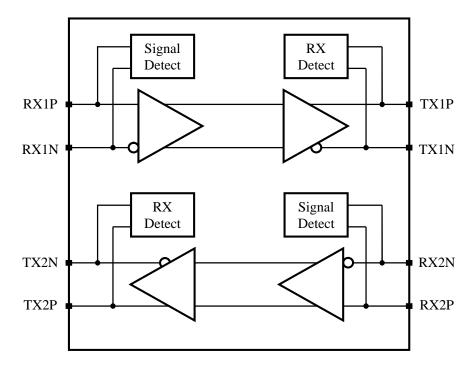

# **Block Diagram**

Copyright(C)2018 THine Electronics, Inc.

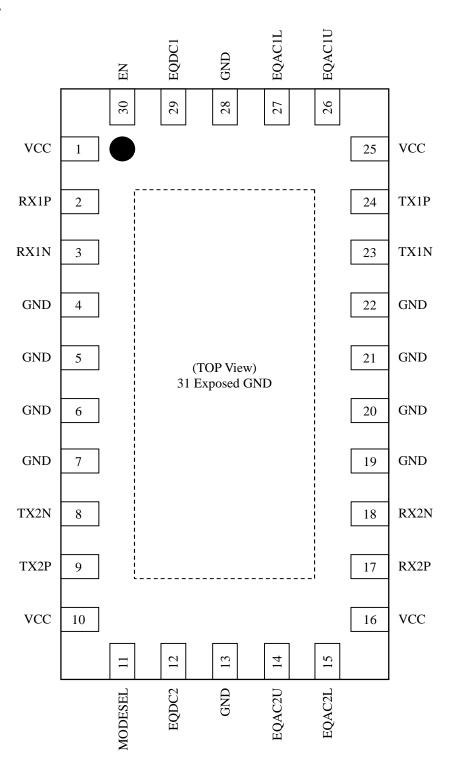

# **Pin Configuration**

Copyright(C)2018 THine Electronics, Inc.

THine Electronics, Inc.

CEL THine

### **Pin Description**

| Pin Name | Pin No        | Туре | Description                                                  |  |  |

|----------|---------------|------|--------------------------------------------------------------|--|--|

| RX1P     | 2             | CI   | Super-Speed CML Signal Input of Channel1(CH1)                |  |  |

| RX1N     | 3             | CI   | Super-Speed CML Signal Input of CH1                          |  |  |

| TX1P     | 24            | CO   | Super-Speed CML Signal Output of CH1                         |  |  |

| TX1N     | 23            | CO   | Super-Speed CML Signal Output of CH1                         |  |  |

| RX2P     | 17            | CI   | Super-Speed CML Signal Input of Channel2(CH2)                |  |  |

| RX2N     | 18            | CI   | Super-Speed CML Signal Input of CH2                          |  |  |

| TX2P     | 9             | CO   | Super-Speed CML Signal Output of CH2                         |  |  |

| TX2N     | 8             | CO   | Super-Speed CML Signal Output of CH2                         |  |  |

|          |               |      | Channel Enable. With internal $300k\Omega$ Pull-up Resistor. |  |  |

| EN       | 30            | 1    | 0 : Power Down                                               |  |  |

|          |               |      | 1 : Normal Operation                                         |  |  |

| EQAC1U   | 26            | 4LI  | CH1 Rx Equalizer Peak Gain & High Linear Mode setting        |  |  |

| EQACIO   | 20            | (*1) | This pin along with EQAC1L allows for up to 16 settings.     |  |  |

| EQAC1L   | 27            | 4LI  | CH1 Rx Equalizer Peak Gain & High Linear Mode setting        |  |  |

| LQACIL   | 21            | (*1) | This pin along with EQAC1U allows for up to 16 settings.     |  |  |

| EQAC2U   | 14            | 4LI  | CH2 Rx Equalizer Peak Gain & High Linear Mode setting        |  |  |

| LQACZO   | 14            | (*1) | This pin along with EQAC2L allows for up to 16 settings.     |  |  |

| EQAC2L   | 15            | 4LI  | CH2 Rx Equalizer Peak Gain & High Linear Mode setting        |  |  |

| LQHOZE   | 10            | (*1) | This pin along with EQAC2U allows for up to 16 settings.     |  |  |

| EQDC1    | 29            | 4LI  | CH1 Equalizer DC Gain Setting                                |  |  |

| EQDOT    | 20            | (*1) |                                                              |  |  |

| EQDC2    | 12            | 4LI  | CH2 Equalizer DC Gain Setting                                |  |  |

| EQDO2    | 12            | (*1) |                                                              |  |  |

|          |               |      | Chip Operation Mode Select, if EN=1                          |  |  |

|          |               | 4LI  | 0 : CH1/2 enable, RxDetect/SignalDetect enable               |  |  |

| MODESEL  | 11            | (*1) | R : CH1/2 enable, RxDetect enable, SignalDetect disable      |  |  |

|          |               | ( ') | F : CH1/2 enable, RxDetect/SignalDetect disable              |  |  |

|          |               |      | 1 : CH1 enable, CH2 disable, RxDetect/SignalDetect disable   |  |  |

| VCC      | 1, 10, 16, 25 | PWR  | Power Supply Pin for On-chip Regulator.                      |  |  |

|          | 4,5,6,7,13,   |      | Ground. Must be tied to the PCB ground plane through an      |  |  |

| GND      | 19,20,21,     | GND  | array of vias.                                               |  |  |

|          | 22,28,31      |      | Pin#31 is exposed pad ground.                                |  |  |

CI: CML Input Buffer, CO: CML Output Buffer

I: LVCMOS Input Buffer, 4LI: 4-Level LVCMOS Input Buffer,

PWR: Power Supply, GND: Ground

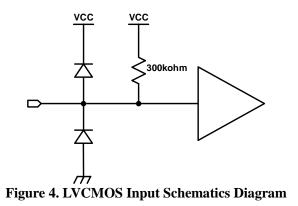

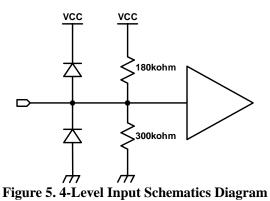

\*1 : 4-Level Input Buffer. With internal  $180k\Omega$  pull-up resistor and  $300k\Omega$  pull-down resistor.

# **Operation Mode Settings**

### Table 1. Operation Mode Setting

| Pin      | Settings         | Operation Mode                                                  |

|----------|------------------|-----------------------------------------------------------------|

| EN       | MODESEL          | Operation mode                                                  |

|          | 0(*1)            | CH1/2 Enable, RxDetect Enable, SignalDetect Enable              |

| 1        | R(*2)            | CH1/2 Enable, RxDetect Enable, SignalDetect Disable             |

| I        | F(*3)            | CH1/2 Enable, RxDetect Disable, SignalDetect Disable            |

|          | 1(*4)            | CH1 Enable, CH2 Disable, RxDetect Disable, SignalDetect Disable |

| 0        | Ignore           | Chip Power Down.                                                |

| *1 Tie ( | $0\Omega$ to GND |                                                                 |

\*1 Tie  $0\Omega$  to GND

\*2 Tie 180k $\Omega$ ±5% to GND

\*3 Leave pin Open

\*4 Tie  $0\Omega$  to VCC

# **Detect Function**

THCX222R10 has Input Signal Detect (SignalDetect) and Receiver Detect (RxDetect) functionality for USB3.x transmission.

Detect functionality must be disable when it is not USB3.x application.

# **Liner Equalizer Settings**

### Table 2. Equalization and -1dB Compression Point Linear Swing Settings

| EQACnU <sup>*1</sup> EQACnL <sup>*1</sup> Equalizer Settings (dB) |        | Equalizer Settings (dB) | Output Linear Swin | g Settings (mVppd) |  |  |

|-------------------------------------------------------------------|--------|-------------------------|--------------------|--------------------|--|--|

| EQACIIO                                                           | EQACIL | @5GHz                   | @100MHz            | @5GHz              |  |  |

| 0                                                                 | 0      | 7.5                     |                    |                    |  |  |

| 0                                                                 | R      | 8.8                     |                    |                    |  |  |

| 0                                                                 | F      | 9.9                     |                    |                    |  |  |

| 0                                                                 | 1      | 10.9                    | 000                | 760                |  |  |

| R                                                                 | 0      | 11.8                    | 830                | 760                |  |  |

| R                                                                 | R      | 12.6                    |                    |                    |  |  |

| R                                                                 | F      | 13.3                    |                    |                    |  |  |

| R                                                                 | 1      | 13.9                    |                    |                    |  |  |

| F                                                                 | 0      | 8.5                     |                    |                    |  |  |

| F                                                                 | R      | 9.7                     |                    |                    |  |  |

| F                                                                 | F      | 10.8                    |                    |                    |  |  |

| F                                                                 | 1      | 11.8                    | 1200               | 1000               |  |  |

| 1                                                                 | 0      | 12.6                    | 1200               | 1000               |  |  |

| 1                                                                 | R      | 13.5                    |                    |                    |  |  |

| 1                                                                 | F      | 14.2                    |                    |                    |  |  |

| 1                                                                 | 1      | 14.8                    |                    |                    |  |  |

\*1 n=1,2

**Table 3. Flat Gain Settings**

| EQDCn <sup>*1</sup> | Flat Gain Settings (dB)@Up to 300MHz |                           |  |  |  |

|---------------------|--------------------------------------|---------------------------|--|--|--|

| EQDCI               | EQACn <sup>*1</sup> U=0/R            | EQACn <sup>*1</sup> U=F/1 |  |  |  |

| 0                   | -2.6                                 | -1.2                      |  |  |  |

| R                   | -1.7                                 | -0.3                      |  |  |  |

| F                   | -0.2                                 | 1.3                       |  |  |  |

| 1                   | 3.8                                  | 5.2                       |  |  |  |

|                     |                                      | *1 n=1,2                  |  |  |  |

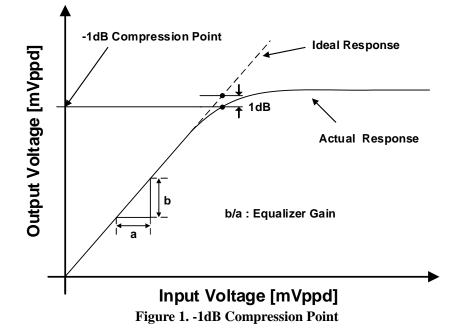

-1dB Compression Point is showed below. It means output voltage range that has linearity.

5/12

Copyright(C)2018 THine Electronics, Inc.

THine Electronics, Inc. Security E

# **Absolute Maximum Ratings**

### Table 4. Absolute Maximum Ratings

| Par          | ameter               | Min          | Тур | Max     | Unit   |

|--------------|----------------------|--------------|-----|---------|--------|

|              | oltage(VCC)          | -0.3         | -   | 4.0     | V      |

|              | ut/Output Voltage    | -0.3         | -   | VCC+0.3 | V      |

| 4-Level LVCN | IOS Input Voltage    | -0.3         | -   | VCC+0.3 | V      |

| CML Receiv   | er Input Voltage     | -0.3         | -   | VCC+0.3 | V      |

| CML Transmit | ter Output Voltage   | -0.3         | -   | VCC+0.3 | V      |

|              | HBM                  | -            | -   | ±4      | kV     |

| ESD Rating   | MM                   | -            | -   | ±200    | V      |

|              | CDM                  | -            | -   | ±1000   | V      |

| Storage      | Temperature          | re -55 - 125 |     | 125     | °C     |

| Junction     | Junction Temperature |              | -   | 125     | °C     |

| Reflow Peak  | lemperature/Time     | -            | -   | 260/10  | °C/sec |

# **<u>Recommended Operating Conditions</u>**

#### Table 5. Recommended Operating Condition

| Parameter               | Min | Тур | Max | Unit |

|-------------------------|-----|-----|-----|------|

| Supply Voltage(VCC)     | 3.0 | 3.3 | 3.6 | V    |

| Supply Ramp Requirement | 0.1 | -   | 50  | ms   |

| Operating Temperature   | -40 | -   | 85  | °C   |

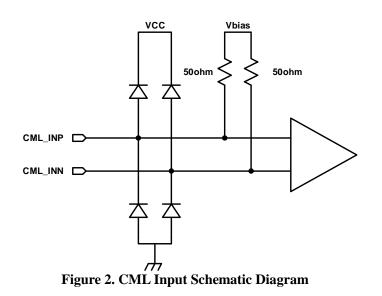

# **Equivalent CML Input Schematic Diagram**

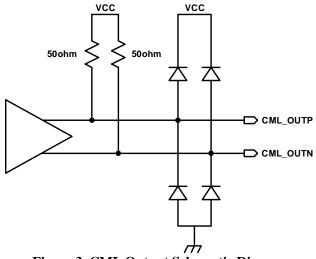

# Equivalent CML Output Schematic Diagram

Figure 3. CML Output Schematic Diagram

# **Equivalent LVCMOS Input Schematic Diagram**

# Equivalent 4-Level LVCMOS Input Schematic Diagram

# **Electrical Specification**

Supply Current

### Table 6. Supply Current

| Over recommended | l operating | supply | and | temperature | range | unless | otherwise | specified |  |

|------------------|-------------|--------|-----|-------------|-------|--------|-----------|-----------|--|

|------------------|-------------|--------|-----|-------------|-------|--------|-----------|-----------|--|

| Symbol | Parameter                   | Condition                 | Min | Тур | Max | Unit |

|--------|-----------------------------|---------------------------|-----|-----|-----|------|

| ICCW   | Active Mede Supply Current  | EQACn <sup>*1</sup> U=F/1 | -   | 84  | 150 | mA   |

| 10077  | Active Mode Supply Current  | EQACn <sup>*1</sup> U=0/R | -   | 69  | 123 | mA   |

| ICCSL  | Slumber Mode Supply Current | -                         | -   | 45  | 65  | mA   |

| ICCI   | Unplug Mode Supply Current  | -                         | -   | 1.2 | 2.9 | mA   |

| ICCS   | Power Down Supply Current   | -                         | -   | 120 | 180 | uA   |

\*1 n=1,2

### LVCMOS DC Specification

### Table 7. LVCMOS DC Specification

|        | Over recommended operating sup | pply and temperatur | re range | unless oth | erwise sp | ecified |

|--------|--------------------------------|---------------------|----------|------------|-----------|---------|

| Symbol | Parameter                      | Condition           | Min      | Тур        | Max       | Unit    |

| VIH    | High Level Input Voltage       | -                   | 2.0      | -          | VCC       | V       |

| VIL    | Low Level Input Voltage        | -                   | 0        | -          | 0.7       | V       |

4-Level LVCMOS DC Specification

### Table 8. 4-Level LVCMOS DC Specification

Over recommended operating supply and temperature range unless otherwise specified

| Symbol             | Parameter                        | Condition | Min            | Тур | Max            | Unit |

|--------------------|----------------------------------|-----------|----------------|-----|----------------|------|

| Vthl               | Low Level Input<br>Voltage       | 0(*1)     | 0              | -   | VCC*0.25 - 0.3 | V    |

| VTHR               | R-Level Input Voltage            | R(*2)     | VCC*0.25 + 0.3 | -   | VCC*0.5 - 0.3  | V    |

| VTHF               | F-Level Input Voltage            | F(*3)     | VCC*0.5 + 0.3  | -   | VCC*0.75 - 0.3 | V    |

| V <sub>THH</sub>   | High Level Input<br>Voltage      | 1(*4)     | VCC*0.75 + 0.3 | -   | VCC            | V    |

| I <sub>IH_4L</sub> | High level Input Leak<br>Current | VIN=VCC   | -100           | -   | 100            | uA   |

| $I_{IL_{4L}}$      | Low Level Input Leak<br>Current  | VIN=GND   | -100           | -   | 100            | uA   |

\*Must be tied for setting each level

\*1 : Tie  $0\Omega$  to GND

\*2 : Tie 180k $\Omega$ ±5% to GND

\*3 : Leave pin open

\*4 : Tie  $0\Omega$  to VCC

Receiver DC/AC Specification

### Table 9. Receiver DC/AC Specification

|                          | Over recommended operating                           | g supply and temper | ature rang | e unless | otherwise | specified |

|--------------------------|------------------------------------------------------|---------------------|------------|----------|-----------|-----------|

| Symbol                   | Parameter                                            | Condition           | Min        | Тур      | Max       | Unit      |

| VIN-DIFF-PP              | AC Coupled Differential Input<br>Peak to Peak Signal | 10Gbps PRBS9        | -          | -        | 1200      | mV        |

| R <sub>RX-DC</sub>       | Receiver DC Common Mode<br>Impedance                 | -                   | -          | 30       | -         | Ω         |

| R <sub>RX</sub> -DIFF-DC | DC Differential Impedance                            | -                   | 72         | 100      | 120       | Ω         |

| RRX-HIGH-IMP-DC-POS      | DC Input Common Mode Input<br>Impedance for V>0      | -                   | 25         | •        | -         | kΩ        |

| RL <sub>RX-DIFF</sub>    | Rx Differential Return Loss                          | 0.05 to 5 GHz       | -          | -7       | -         | dB        |

| RL <sub>RX-CM</sub>      | Rx Common Mode Return Loss                           | 0.05 to 5 GHz       | -          | -6       | -         | dB        |

Copyright(C)2018 THine Electronics,Inc.

|                           |                                                                                    | miller DC / AC specie | ication |      |     |        |  |  |

|---------------------------|------------------------------------------------------------------------------------|-----------------------|---------|------|-----|--------|--|--|

|                           | Over recommended operating supply and temperature range unless otherwise specified |                       |         |      |     |        |  |  |

| Symbol                    | Parameter                                                                          | Condition             | Min     | Тур  | Max | Unit   |  |  |

| T <sub>TX-DJ-DD</sub>     | Deterministic Jitter                                                               | Loss=18dB@5GHz        | -       | 0.25 | -   | Ulpp   |  |  |

| T <sub>TX-RJ-DD</sub>     | Random Jitter                                                                      | -                     | -       | 0.5  | -   | ps RMS |  |  |

| T <sub>TX-RISE-FALL</sub> | Tx Rise/Fall Time                                                                  | 20% to 80 %           | -       | 40   | -   | ps     |  |  |

| TRF-MISMATCH              | Tx Rise/Fall Mismatch                                                              | -                     | -       | 0.01 | -   | UI     |  |  |

| RL <sub>TX-DIFF</sub>     | Tx Differential Return Loss <sup>*1</sup>                                          | 0.05 to 5 GHz         | -       | -10  | -   | dB     |  |  |

| RLтх-см                   | Tx Common Mode Return<br>Loss <sup>*1</sup>                                        | 0.05 to 5 GHz         | -       | -6   | -   | dB     |  |  |

| RTX-DIFF-DC               | DC Differential Impedance                                                          | -                     | 72      | 100  | 120 | Ω      |  |  |

| VTX-RCV-DETECT            | The Amount of Voltage Change<br>Allowed during Receiver<br>Detection               | -                     | -       | -    | 0.6 | V      |  |  |

| V <sub>TX-DC-CM</sub>     | Transmitter DC Common Mode<br>Voltage                                              | -                     | -       | 1.9  | -   | V      |  |  |

| VTX-CM-AC-PP_ACTIVE       | Transmitter AC Common Mode<br>Voltage Active                                       | -                     | -       | -    | 100 | mVpp   |  |  |

| VTX-IDLE-DIFF-AC-pp       | Electrical Idle Differential<br>Peak-Peak Output Voltage                           | -                     | 0       | -    | 10  | mV     |  |  |

| VTX-IDLE-DIFF-DC          | DC Electrical Idle Differential<br>Output Voltage                                  | -                     | 0       | -    | 10  | mV     |  |  |

| CTX-PARASITIC             | Tx Input Capacitance                                                               | -                     | -       | -    | 1.1 | рF     |  |  |

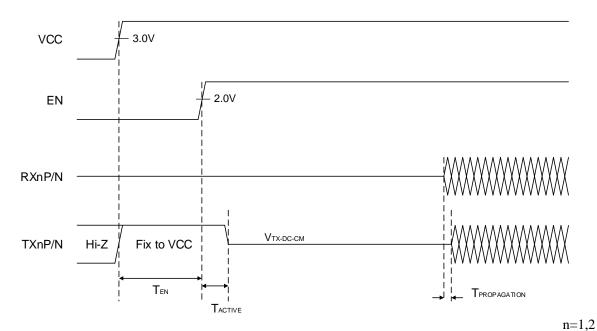

| T <sub>EN</sub>           | Power On to EN High Delay                                                          | -                     | 0       | -    | -   | ns     |  |  |

| TACTIVE                   | EN High to Active Delay                                                            | -                     | -       | -    | 200 | us     |  |  |

| TPROPAGATION              | Differential Propagation Delay                                                     | -                     | -       | 150  | -   | ps     |  |  |

Transmitter DC / AC Specifications

Table 10. Transmitter DC / AC specification

\*1 Confirmed evaluation board.

Figure 6. Power on Sequence (SignalDetect Disable/ RxDetect Disable)

| Copyright(C)2018 THine Electronics,Inc |   |

|----------------------------------------|---|

| copyright(c)2010 Time Electromes, me   | • |

# **Package**

Unit: mm

Copyright(C)2018 THine Electronics, Inc.

THine Electronics, Inc.

# **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. THine Electronics, Inc. ("THine") is not responsible for possible errors and omissions in this material. Please note even if errors or omissions should be found in this material, THine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without THine's prior permission is prohibited.

- 4. Note that even if infringement of any third party's industrial ownership should occur by using this product, THine will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

- 5. Product Application

- 5.1 Application of this product is intended for and limited to the following applications: audio-video device, office automation device, communication device, consumer electronics, smartphone, feature phone, and amusement machine device. This product must not be used for applications that require extremely high-reliability/safety such as aerospace device, traffic device, transportation device, nuclear power control device, combustion chamber device, medical device related to critical care, or any kind of safety device.

- 5.2 This product is not intended to be used as an automotive part, unless the product is specified as a product conforming to the demands and specifications of IATF16949 ("the Specified Product") in this data sheet. THine accepts no liability whatsoever for any product other than the Specified Product for it not conforming to the aforementioned demands and specifications.

- 5.3 THine accepts liability for demands and specifications of the Specified Product only to the extent that the user and THine have been previously and explicitly agreed to each other.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 9. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Act.

- 10. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition. Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses.

Contact: THine@cel.com

Copyright(C)2018 THine Electronics, Inc.