Triple input HDMI 1.4a compliant receiver interface with equalizer (up to 1080p for HDTV, and UXGA for PC formats

Rev. 3 — 19 November 2010

**Product data sheet**

## 1. General description

The TDA19977A; TDA19977B is a three input HDMI 1.4a compliant receiver with embedded EDID memory. The built-in auto-adaptive equalizer, improves signal quality and allows the use of cable lengths of up to 25 m which are laboratory tested with a 0.5 mm (24 AWG) cable at 2.05 gigasamples per second. The HDCP (TDA19977A only) key set is stored in non-volatile OTP (One Time Programmable) memory for maximum security. In addition, the TDA19977A; TDA19977B is delivered with software drivers to ease configuration and use.

The TDA19977A; TDA19977B supports:

- TV resolutions:

- 480i (1440  $\times$  480i at 60 Hz), 576i (1440  $\times$  576i at 50 Hz) to HDTV (up to 1920  $\times$  1080p at 50/60 Hz)

- WUXGA (1920  $\times$  1200p at 60 Hz) reduced blanking format

- PC resolutions:

- VGA (640  $\times$  480p at 60 Hz) to UXGA (1600  $\times$  1200p at 60 Hz)

- Deep Color mode in 10-bit and 12-bit (up to 205 MHz TMDS clock)

- Gamut boundary description

- IEC 60958/IEC 61937, OBA (One Bit Audio), DST (Direct Stream Transfer) and HBR (High Bit Rate) stream

The TDA19977A; TDA19977B includes:

- · An enhanced PC and TV format recognition system

- Generation of a 128/256/512  $\times$   $f_s$  system clock allowing the use of simple audio DACs without an integrated PLL (such as the UDA1334BTS)

- An embedded oscillator (an external crystal can also be used)

- Improved audio clock generation using an external reference clock

- OBA (as used in SACD), DST and HBR stream support

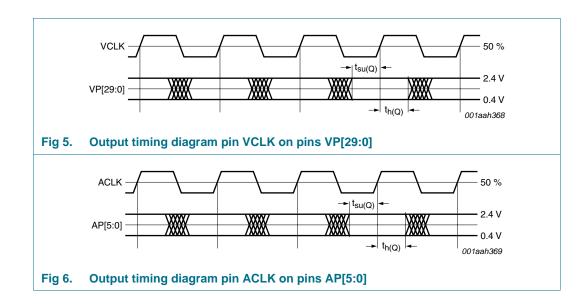

The TDA19977A; TDA19977B converts HDMI streams with or without HDCP (TDA19977A only) into RGB or YCbCr digital signals. The YCbCr digital output signal can be 4:4:4 or 4:2:2 semi-planar format based on the ITU-R BT.601 standard or 4:2:2 based on the ITU-R BT.656 format. The device can adjust the output timing of the video port by altering the values of  $t_{su(Q)}$  and  $t_{h(Q)}$ . In addition, all settings are controllable using the I<sup>2</sup>C-bus.

#### Triple input HDMI receiver interface with digital processing

## 2. Features and benefits

- Complies with the HDMI 1.4a, DVI 1.0, CEA-861-D and HDCP (TDA19977A only) 1.4 standards

- Three independent HDMI inputs, up to the HDMI frequency of 205 MHz

- Embedded auto-adaptive equalizer on all HDMI links

- EDID memory: 253 shared bytes and three bytes dedicated to each HDMI input

- Supports color depth processing (8-bit, 10-bit or 12-bit per color)

- Color gamut metadata packet with interrupt on each update, readable via the I<sup>2</sup>C-bus

- Up to four S/PDIF or I<sup>2</sup>S-bus outputs (eight channels) at a sampling rate up to 192 kHz with IEC 60958/IEC 61937 stream

- HBR audio stream up to 768 kHz with four demultiplexed S/PDIF or I<sup>2</sup>S-bus outputs

- HBR streams (compatible with DTS-HD master audio and Dolby TrueHD up to eight channels due to HBR packet for stream with a frame rate up to 768 kHz) support

- DSD and DST audio stream up to six DSD channels output for SACD with DST audio packet support

- Channel status decoder supports multi-channel reception

- Improved audio clock generation using an external reference clock

- System/master clock output (128/256/512 × f<sub>s</sub>) enables the use of the UDA1334BTS

- The HDMI interface supports:

- All HDTV formats up to 1920 × 1080p at 50/60 Hz and WUXGA (1920 × 1200p at 60 Hz) with support for reduced blanking

- 3D formats including all primary formats up to 1920 × 1080p at 30 Hz Frame Packing and 1920 × 1080p at 60 Hz Top-and-Bottom

- PC formats up to UXGA (1600 × 1200p at 60 Hz)

- Embedded oscillator (an external crystal can be used)

- Frame and field detection for interlaced video signal

- Sync timing measurements for format recognition

- Improved system for measurements of blanking and video active area allowing an accurate recognition of PC and TV formats

- HDCP (TDA19977A only) with repeater capability

- Embedded non-volatile memory storage of HDCP (TDA19977A only) keys

- Programmable color space input signal conversion from RGB-to-YCbCr or YCbCr-to-RGB

- Output formats: RGB 4:4:4, YCbCr 4:4:4, YCbCr 4:2:2 semi-planar based on the ITU-R BT.601 standard and YCbCr 4:2:2 ITU-R BT.656

- 8-bit, 10-bit or 12-bit output formats selectable using the I<sup>2</sup>C-bus (8-bit and 10-bit only in 4:4:4 format)

- I<sup>2</sup>C-bus adjustable timing of video port (t<sub>su(Q)</sub> and t<sub>h(Q)</sub>)

- Downsampling-by-two with selectable filters on Cb and Cr channels in 4:2:2 mode

- Internal video and audio pattern generator

- Controllable using the I<sup>2</sup>C-bus; 5 V tolerant and bit rate up to 400 kbit/s

- DDC-bus inputs 5 V tolerant and bit rate up to 400 kbit/s

- LV-TTL outputs

- Power-down mode

- CMOS process

TDA19977A\_TDA19977B

### Triple input HDMI receiver interface with digital processing

- 1.8 V and 3.3 V power supplies

- Lead-free (Pb) HLQFP144 package

## 3. Applications

- HDTV

- YCbCr or RGB HI-Speed video digitizer

- Projector, plasma and LCD TV

- Rear projection TV

- High-end TV

- Home theater amplifier

- DVD recorder

- AVR and HDMI splitter

## 4. Quick reference data

| Table 1.              | Quick reference data          |                                                                                        |       |      |       |      |

|-----------------------|-------------------------------|----------------------------------------------------------------------------------------|-------|------|-------|------|

| Symbol                | Parameter                     | Conditions                                                                             | Min   | Тур  | Мах   | Unit |

| Digital in            | outs: pins RXxC+, RXxC- [1]   |                                                                                        |       |      |       |      |

| f <sub>clk(max)</sub> | maximum clock frequency       |                                                                                        | 205   | -    | -     | MHz  |

| Clock tim             | ing output: pins VCLK, ACLK   | and SYSCLK                                                                             |       |      |       |      |

| f <sub>clk(max)</sub> | maximum clock frequency       | pin VCLK                                                                               | 165   | -    | -     | MHz  |

|                       |                               | pin ACLK                                                                               | 25    | -    | -     | MHz  |

|                       |                               | pin SYSCLK                                                                             | 50    | -    | -     | MHz  |

| Supplies              |                               |                                                                                        |       |      |       |      |

| V <sub>DDH(3V3)</sub> | HDMI supply voltage (3.3 V)   |                                                                                        | 3.135 | 3.3  | 3.465 | V    |

| V <sub>DDH(1V8)</sub> | HDMI supply voltage (1.8 V)   |                                                                                        | 1.71  | 1.8  | 1.89  | V    |

| V <sub>DDI(3V3)</sub> | input supply voltage (3.3 V)  |                                                                                        | 3.135 | 3.3  | 3.465 | V    |

| V <sub>DDC(1V8)</sub> | core supply voltage (1.8 V)   |                                                                                        | 1.71  | 1.8  | 1.89  | V    |

| V <sub>DDO(3V3)</sub> | output supply voltage (3.3 V) |                                                                                        | 3.135 | 3.3  | 3.465 | V    |

| Р                     | power dissipation             | Active mode                                                                            | [2]   |      |       |      |

|                       |                               | 720p at 60 Hz                                                                          | -     | 0.75 | -     | W    |

|                       |                               | 1080p at 60 Hz                                                                         | -     | 1.13 | -     | W    |

|                       |                               | 1080p at 60 Hz; Deep Color mode                                                        | -     | 1.63 | -     | W    |

| P <sub>cons</sub>     | power consumption             | Power-down mode                                                                        |       |      |       |      |

|                       |                               | pin PD = HIGH                                                                          | -     | 1    | -     | mW   |

|                       |                               | I <sup>2</sup> C-bus; EDID and HDCP <sup>[3]</sup> memory power-up                     | -     | 4    | -     | mW   |

|                       |                               | I <sup>2</sup> C-bus; EDID; activity detection and HDCP <sup>[3]</sup> memory power-up | -     | 150  | -     | mW   |

$[1] \quad x = A, B \text{ or } C.$

[2] At 30 % activity on video port output.

[3] HDCP decoding is only supported by the TDA19977A.

All information provided in this document is subject to legal disclaimers.

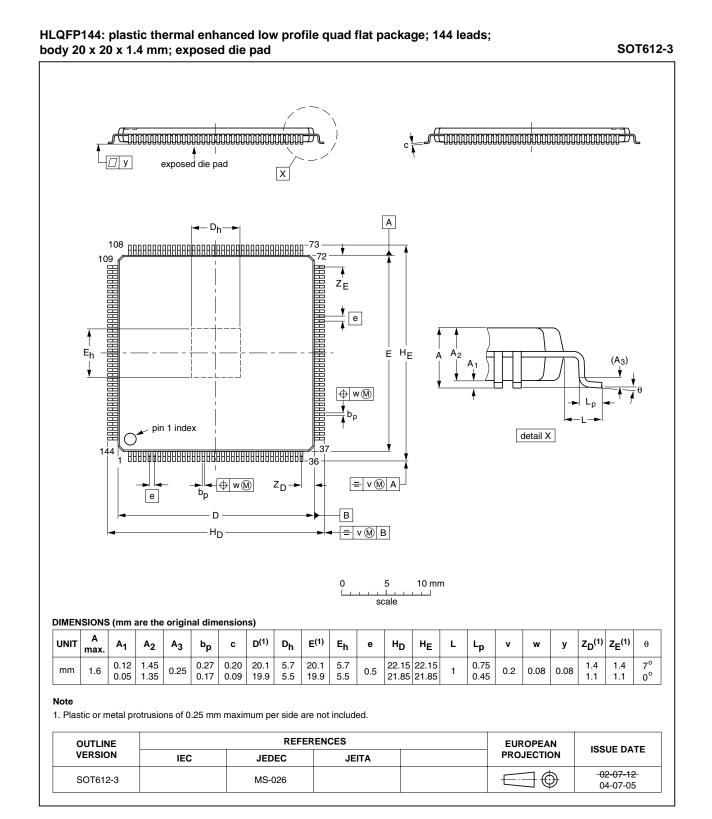

## 5. Ordering information

| Table 2.         Ordering information |          |                                                               |          |  |  |  |  |

|---------------------------------------|----------|---------------------------------------------------------------|----------|--|--|--|--|

| Type number                           | Package  | Package                                                       |          |  |  |  |  |

|                                       | Name     | Description                                                   | Version  |  |  |  |  |

| TDA19977AHV                           | HLQFP144 | plastic thermal enhanced low profile quad flat package;       | SOT612-3 |  |  |  |  |

| TDA19977BHV                           | HLQFP144 | 144 leads; body $20 \times 20 \times 1.4$ mm; exposed die pad |          |  |  |  |  |

TDA19977A\_TDA19977B

Product data sheet

Triple input HDMI receiver interface with digital processing

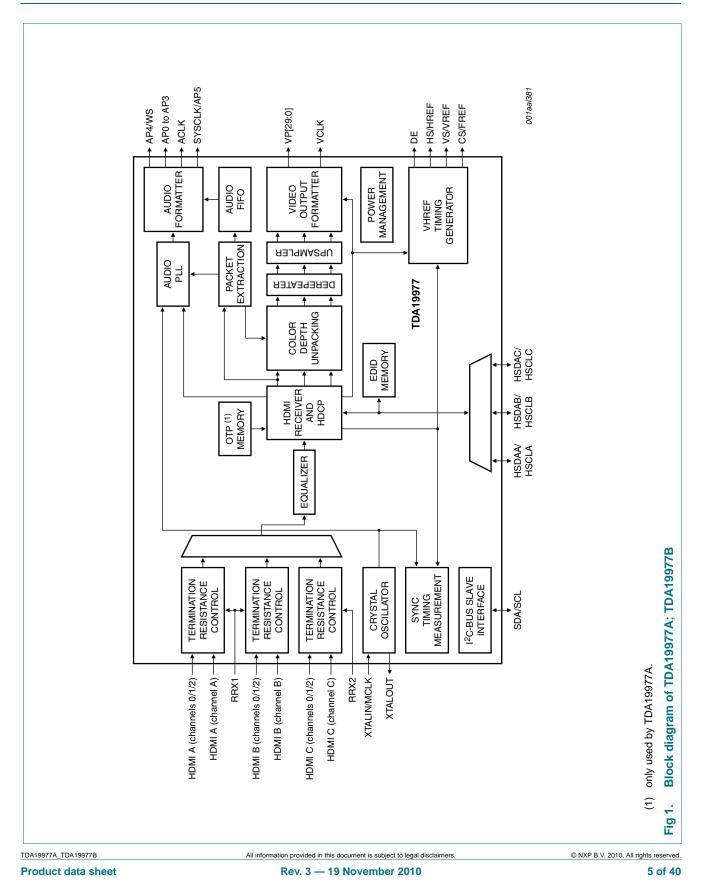

## 6. Block diagram

## Triple input HDMI receiver interface with digital processing

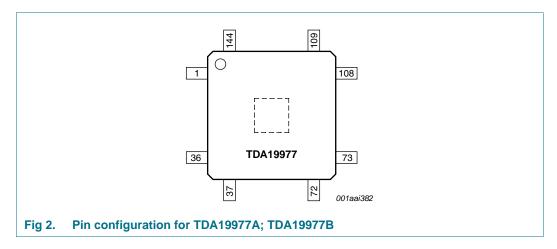

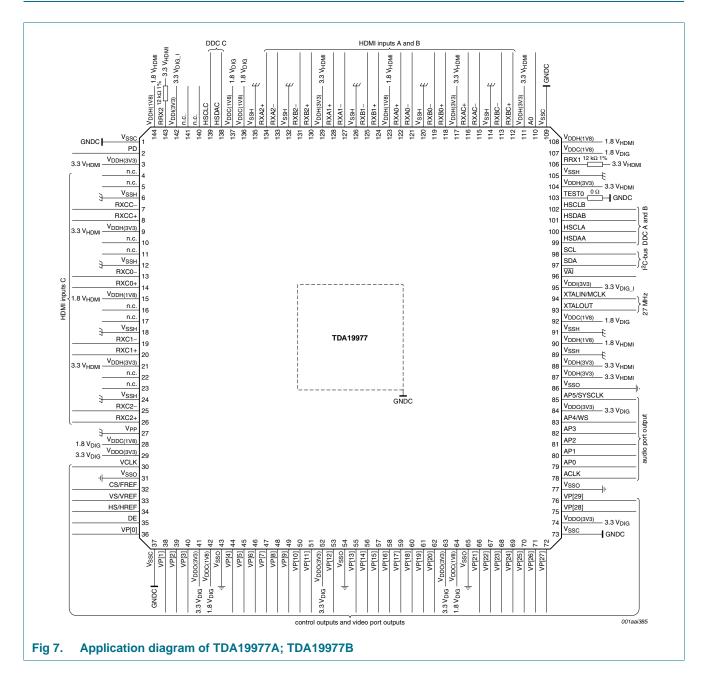

## 7. Pinning information

## 7.1 Pinning

## 7.2 Pin description

### Table 3. Pin description

| Or mark and           | Div | <b>T</b>            | Description                            |

|-----------------------|-----|---------------------|----------------------------------------|

| Symbol                | Pin | Type <sup>[1]</sup> | Description                            |

| V <sub>SSC</sub>      | 1   | G                   | ground for the digital core            |

| PD                    | 2   | I                   | power-down control input (active HIGH) |

| V <sub>DDH(3V3)</sub> | 3   | Р                   | HDMI receiver supply voltage; 3.3 V    |

| n.c.                  | 4   | I                   | not connected                          |

| n.c.                  | 5   | I                   | not connected                          |

| V <sub>SSH</sub>      | 6   | G                   | HDMI receiver ground                   |

| RXCC-                 | 7   | I                   | HDMI input C negative clock channel    |

| RXCC+                 | 8   | I                   | HDMI input C positive clock channel    |

| V <sub>DDH(3V3)</sub> | 9   | Р                   | HDMI receiver supply voltage; 3.3 V    |

| n.c.                  | 10  | I                   | not connected                          |

| n.c.                  | 11  | I                   | not connected                          |

| V <sub>SSH</sub>      | 12  | G                   | HDMI receiver ground                   |

| RXC0-                 | 13  | I                   | HDMI input C negative data channel 0   |

| RXC0+                 | 14  | I                   | HDMI input C positive data channel 0   |

| V <sub>DDH(1V8)</sub> | 15  | Р                   | HDMI receiver supply voltage; 1.8 V    |

| n.c.                  | 16  | I                   | not connected                          |

| n.c.                  | 17  | I                   | not connected                          |

| V <sub>SSH</sub>      | 18  | G                   | HDMI receiver ground                   |

| RXC1-                 | 19  | I                   | HDMI input C negative data channel 1   |

| RXC1+                 | 20  | I                   | HDMI input C positive data channel 1   |

| V <sub>DDH(3V3)</sub> | 21  | Р                   | HDMI receiver supply voltage; 3.3 V    |

| n.c.                  | 22  | I                   | not connected                          |

| n.c.                  | 23  | I                   | not connected                          |

|                       |     |                     |                                        |

TDA19977A\_TDA19977B

All information provided in this document is subject to legal disclaimers.

Product data sheet

# TDA19977A; TDA19977B

## Triple input HDMI receiver interface with digital processing

| Table 3.              | Pin description . | continued             |                                               |

|-----------------------|-------------------|-----------------------|-----------------------------------------------|

| Symbol                | Pin               | Type <mark>[1]</mark> | Description                                   |

| V <sub>SSH</sub>      | 24                | G                     | HDMI receiver ground                          |

| RXC2-                 | 25                | I                     | HDMI input C negative data channel 2          |

| RXC2+                 | 26                | I                     | HDMI input C positive data channel 2          |

| V <sub>PP</sub>       | 27                | Р                     | OTP memory programming voltage <sup>[2]</sup> |

| V <sub>DDC(1V8)</sub> | 28                | Р                     | digital core supply voltage; 1.8 V            |

| V <sub>DDO(3V3)</sub> | 29                | Р                     | video port output supply voltage; 3.3 V       |

| VCLK                  | 30                | 0                     | video clock output                            |

| V <sub>SSO</sub>      | 31                | G                     | video port output ground                      |

| CS/FREF               | 32                | 0                     | composite synchronization output              |

|                       |                   |                       | composite field output signal                 |

| VS/VREF               | 33                | 0                     | vertical synchronization output               |

|                       |                   |                       | vertical reference output                     |

| HS/HREF               | 34                | 0                     | horizontal synchronization output             |

|                       |                   |                       | reference output                              |

| DE                    | 35                | 0                     | data enable output                            |

| VP[0]                 | 36                | 0                     | video port output bit 0                       |

| V <sub>SSC</sub>      | 37                | G                     | digital core ground                           |

| VP[1]                 | 38                | 0                     | video port output bit 1                       |

| VP[2]                 | 39                | 0                     | video port output bit 2                       |

| VP[3]                 | 40                | 0                     | video port output bit 3                       |

| V <sub>DDO(3V3)</sub> | 41                | Р                     | video port output supply voltage; 3.3 V       |

| V <sub>DDC(1V8)</sub> | 42                | Р                     | digital core supply voltage; 1.8 V            |

| V <sub>SSO</sub>      | 43                | G                     | video port output ground                      |

| VP[4]                 | 44                | 0                     | video port output bit 4                       |

| VP[5]                 | 45                | 0                     | video port output bit 5                       |

| VP[6]                 | 46                | 0                     | video port output bit 6                       |

| VP[7]                 | 47                | 0                     | video port output bit 7                       |

| VP[8]                 | 48                | 0                     | video port output bit 8                       |

| VP[9]                 | 49                | 0                     | video port output bit 9                       |

| VP[10]                | 50                | 0                     | video port output bit 10                      |

| VP[11]                | 51                | 0                     | video port output bit 11                      |

| V <sub>DDO(3V3)</sub> | 52                | Р                     | video port output supply voltage; 3.3 V       |

| VP[12]                | 53                | 0                     | video port output bit 12                      |

| V <sub>SSO</sub>      | 54                | G                     | video port output ground                      |

| VP[13]                | 55                | 0                     | video port output bit 13                      |

| VP[14]                | 56                | 0                     | video port output bit 14                      |

| VP[15]                | 57                | 0                     | video port output bit 15                      |

| VP[16]                | 58                | 0                     | video port output bit 16                      |

| VP[17]                | 59                | 0                     | video port output bit 17                      |

| VP[18]                | 60                | 0                     | video port output bit 18                      |

| VP[19]                | 61                | 0                     | video port output bit 19                      |

TDA19977A\_TDA19977B

All information provided in this document is subject to legal disclaimers.

Product data sheet

© NXP B.V. 2010. All rights reserved. 7 of 40

# TDA19977A; TDA19977B

## Triple input HDMI receiver interface with digital processing

| Symbol                | Pin | Type <sup>[1]</sup> | Description                                                                                                                                                                                     |

|-----------------------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VP[20]                | 62  | 0                   | video port output bit 20                                                                                                                                                                        |

| V <sub>DDO(3V3)</sub> | 63  | Р                   | video port output supply voltage; 3.3 V                                                                                                                                                         |

| V <sub>DDC(1V8)</sub> | 64  | Р                   | digital core supply voltage; 1.8 V                                                                                                                                                              |

| V <sub>SSO</sub>      | 65  | G                   | video port output ground                                                                                                                                                                        |

| VP[21]                | 66  | 0                   | video port output bit 21                                                                                                                                                                        |

| VP[22]                | 67  | 0                   | video port output bit 22                                                                                                                                                                        |

| VP[23]                | 68  | 0                   | video port output bit 23                                                                                                                                                                        |

| VP[24]                | 69  | 0                   | video port output bit 24                                                                                                                                                                        |

| VP[25]                | 70  | 0                   | video port output bit 25                                                                                                                                                                        |

| VP[26]                | 71  | 0                   | video port output bit 26                                                                                                                                                                        |

| VP[27]                | 72  | 0                   | video port output bit 27                                                                                                                                                                        |

| V <sub>SSC</sub>      | 73  | G                   | digital core ground                                                                                                                                                                             |

| V <sub>DDO(3V3)</sub> | 74  | Р                   | video port output supply voltage; 3.3 V                                                                                                                                                         |

| VP[28]                | 75  | 0                   | video port output bit 28                                                                                                                                                                        |

| VP[29]                | 76  | 0                   | video port output bit 29                                                                                                                                                                        |

| V <sub>SSO</sub>      | 77  | G                   | video port output ground                                                                                                                                                                        |

| ACLK                  | 78  | 0                   | audio clock output                                                                                                                                                                              |

| AP0                   | 79  | 0                   | audio port 0 output                                                                                                                                                                             |

| AP1                   | 80  | 0                   | audio port 1 output                                                                                                                                                                             |

| AP2                   | 81  | 0                   | audio port 2 output                                                                                                                                                                             |

| AP3                   | 82  | 0                   | audio port 3 output                                                                                                                                                                             |

| AP4/WS                | 83  | 0                   | audio port 4 output                                                                                                                                                                             |

|                       |     |                     | word select output                                                                                                                                                                              |

| V <sub>DDO(3V3)</sub> | 84  | Р                   | video port output supply voltage; 3.3 V                                                                                                                                                         |

| AP5/SYSCLK            | 85  | 0                   | audio port 5 output                                                                                                                                                                             |

|                       |     |                     | system clock audio output                                                                                                                                                                       |

| V <sub>SSO</sub>      | 86  | G                   | video port output ground                                                                                                                                                                        |

| V <sub>DDH(3V3)</sub> | 87  | Р                   | HDMI audio PLL supply voltage; 3.3 V                                                                                                                                                            |

| V <sub>DDH(3V3)</sub> | 88  | Р                   | HDMI audio PLL supply voltage; 3.3 V                                                                                                                                                            |

| V <sub>SSH</sub>      | 89  | G                   | HDMI audio PLL ground                                                                                                                                                                           |

| V <sub>DDH(1V8)</sub> | 90  | Р                   | HDMI audio PLL supply voltage; 1.8 V                                                                                                                                                            |

| V <sub>SSH</sub>      | 91  | G                   | HDMI audio PLL ground                                                                                                                                                                           |

| V <sub>DDC(1V8)</sub> | 92  | Р                   | digital core supply voltage; 1.8 V                                                                                                                                                              |

| XTALOUT               | 93  | 0                   | crystal oscillator output                                                                                                                                                                       |

| XTALIN/MCLK           | 94  | I                   | crystal oscillator input                                                                                                                                                                        |

|                       |     |                     | test pattern clock input                                                                                                                                                                        |

| V <sub>DDI(3V3)</sub> | 95  | Р                   | digital inputs supply voltage; 3.3 V                                                                                                                                                            |

| VAI                   | 96  | 0                   | video activity indication output (open-drain); warns the<br>external microprocessor that a special event has<br>occurred; must be connected to a pull-up resistor; 5 V<br>tolerant (active LOW) |

| SDA                   | 97  | I/O                 | I <sup>2</sup> C-bus serial data input/output                                                                                                                                                   |

|                       |     |                     |                                                                                                                                                                                                 |

TDA19977A\_TDA19977B Product data sheet

# TDA19977A; TDA19977B

## Triple input HDMI receiver interface with digital processing

| Table 3.              | Pin description . | continued             |                                                                         |

|-----------------------|-------------------|-----------------------|-------------------------------------------------------------------------|

| Symbol                | Pin               | Type <mark>[1]</mark> | Description                                                             |

| SCL                   | 98                | I                     | l <sup>2</sup> C-bus serial clock input                                 |

| HSDAA                 | 99                | I/O                   | HDMI input/output A (HDCP[3]) DDC-bus serial data                       |

| HSCLA                 | 100               | I                     | HDMI input A (HDCP[3]) DDC-bus serial clock                             |

| HSDAB                 | 101               | I/O                   | HDMI input/output B (HDCP[3]) DDC-bus serial data                       |

| HSCLB                 | 102               | I                     | HDMI input B (HDCP <sup>[3]</sup> ) DDC-bus serial clock                |

| TEST0                 | 103               | I                     | reserved for test; connect to digital inputs ground (V <sub>SSC</sub> ) |

| V <sub>DDH(3V3)</sub> | 104               | Р                     | HDMI deep PLL supply voltage; 3.3 V                                     |

| V <sub>SSH</sub>      | 105               | G                     | HDMI deep PLL ground                                                    |

| RRX1                  | 106               | I                     | HDMI inputs A and B termination resistance control                      |

| V <sub>DDC(1V8)</sub> | 107               | Р                     | digital core supply voltage; 1.8 V                                      |

| V <sub>DDH(1V8)</sub> | 108               | Р                     | HDMI receiver supply voltage; 1.8 V                                     |

| V <sub>SSC</sub>      | 109               | G                     | digital core ground                                                     |

| A0                    | 110               | I                     | I <sup>2</sup> C-bus address control input                              |

| V <sub>DDH(3V3)</sub> | 111               | Р                     | HDMI receiver supply voltage; 3.3 V                                     |

| RXBC+                 | 112               | I                     | HDMI input B positive clock channel                                     |

| RXBC-                 | 113               | I                     | HDMI input B negative clock channel                                     |

| V <sub>SSH</sub>      | 114               | G                     | HDMI receiver ground                                                    |

| RXAC-                 | 115               | I                     | HDMI input A negative clock channel                                     |

| RXAC+                 | 116               | I                     | HDMI input A positive clock channel                                     |

| V <sub>DDH(3V3)</sub> | 117               | Р                     | HDMI receiver supply voltage; 3.3 V                                     |

| RXB0+                 | 118               | I                     | HDMI input B positive data channel 0                                    |

| RXB0-                 | 119               | I                     | HDMI input B negative data channel 0                                    |

| V <sub>SSH</sub>      | 120               | G                     | HDMI receiver ground                                                    |

| RXA0-                 | 121               | I                     | HDMI input A negative data channel 0                                    |

| RXA0+                 | 122               | I                     | HDMI input A positive data channel 0                                    |

| V <sub>DDH(1V8)</sub> | 123               | Р                     | HDMI receiver supply voltage; 1.8 V                                     |

| RXB1+                 | 124               | I                     | HDMI input B positive data channel 1                                    |

| RXB1-                 | 125               | I                     | HDMI input B negative data channel 1                                    |

| V <sub>SSH</sub>      | 126               | G                     | HDMI receiver ground                                                    |

| RXA1-                 | 127               | I                     | HDMI input A negative data channel 1                                    |

| RXA1+                 | 128               | I                     | HDMI input A positive data channel 1                                    |

| V <sub>DDH(3V3)</sub> | 129               | Р                     | HDMI receiver supply voltage; 3.3 V                                     |

| RXB2+                 | 130               | I                     | HDMI input B positive data channel 2                                    |

| RXB2-                 | 131               | I                     | HDMI input B negative data channel 2                                    |

| V <sub>SSH</sub>      | 132               | G                     | HDMI receiver ground                                                    |

| RXA2-                 | 133               | I                     | HDMI input A negative data channel 2                                    |

| RXA2+                 | 134               | I                     | HDMI input A positive data channel 2                                    |

| V <sub>SSH</sub>      | 135               | G                     | HDMI receiver ground                                                    |

| V <sub>DDC(1V8)</sub> | 136               | Р                     | digital core supply voltage; 1.8 V                                      |

| V <sub>DDC(1V8)</sub> | 137               | Р                     | digital core supply voltage; 1.8 V                                      |

| HSDAC                 | 138               | I/O                   | HDMI input/output C (HDCP <sup>[3]</sup> ) DDC-bus serial data          |

TDA19977A\_TDA19977B

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2010. All rights reserved.

#### Triple input HDMI receiver interface with digital processing

| Table 3.              | Pin description | continued           |                                                           |

|-----------------------|-----------------|---------------------|-----------------------------------------------------------|

| Symbol                | Pin             | Type <sup>[1]</sup> | Description                                               |

| HSCLC                 | 139             | I                   | HDMI input C (HDCP <sup>[3]</sup> ) DDC-bus serial clock  |

| n.c.                  | 140             | I/O                 | not connected                                             |

| n.c                   | 141             | I                   | not connected                                             |

| V <sub>DDI(3V3)</sub> | 142             | Р                   | digital inputs supply voltage; 3.3 V                      |

| RRX2                  | 143             | I                   | HDMI inputs C and D termination resistance control        |

| V <sub>DDH(1V8)</sub> | 144             | Р                   | HDMI receiver supply voltage; 1.8 V                       |

| Exposed di            | e pad -         | G                   | exposed die pad; connect to digital core ground (V_{SSC}) |

[1] P = power supply; G = ground; I = input; O = output and I/O = input/output.

[2] Connected to the ground of the HDMI receiver (V<sub>SSH</sub>) in normal operation.

[3] HDCP decoding is only supported by TDA19977A.

## 8. Functional description

The TDA19977A; TDA19977B converts digital data streams input by the HDMI sources into parallel digital data for use by media and video signal processing integrated circuits in devices for HDTV. Data streams can be decoded with or without HDCP protection.

Outputs from the TDA19977A; TDA19977B can be RGB 4:4:4, YCbCr 4:4:4, YCbCr 4:2:2 semi-planar format based on the ITU-R BT.601 standard or YCbCr 4:2:2 based on the ITU-R BT.656 format. Inputs can be both progressive and interlaced formats. The TDA19977A; TDA19977B comprises a color space conversion block, downsampling filters and an embedded timing code function. In addition, the HDCP (TDA19977A only) repeater function enables other HDMI devices to be connected to form an extended "total application".

#### 8.1 Software drivers

Software drivers are provided for easy configuration and use of the TDA19977A; TDA19977B. These drivers can be integrated with a large range of processors, with or without an operating system. They control activity detection, input selection, video mode identification, color conversion, Power-down modes, HDCP (TDA19977A only) and Info Frame notification.

#### 8.2 HDMI inputs

Control of the three HDMI inputs can be automatic using activity detection or using the I<sup>2</sup>C-bus. The HDMI receiver inputs are defined by pins RXx0+, RXx0-, RXx1+, RXx1-, RXx2+, RXx2-, RXxC+, RXxC-, RRXx, HSCLx and HSDAx. In the pin names, x equals A, B or C (as applicable).

### 8.3 Termination resistance control

The HDMI receiver input contains a termination resistance control set by an external resistor connected between pins RRXx and V<sub>DDH(3V3)</sub>. In RRXx, x equals 1 for inputs A and B or 2 for inputs C and D. Typically, the characteristic impedance is 50  $\Omega$  and the default value of the external terminal control resistor is 12 k $\Omega \pm 1$  %.

TDA19977A\_TDA19977B

### 8.4 Equalizer

The auto-adaptive equalizer automatically measures and selects the settings which provide the best signal quality for each cable. This improves signal quality and enables the use of cable lengths up to 25 m (laboratory tested, contact NXP for detailed information). The equalizer is fully automatic and consequently does not need any external control.

### 8.5 Activity detection

The TDA19977A; TDA19977B uses activity detection to automatically select the active HDMI input. An internal, fully programmable, frequency filter controls activity detection. It sees only the activity on the HDMI inputs with a frequency range between  $f_{min}$  (22.5 MHz) and  $f_{max}$  (205 MHz).

This activity detection can generate an interrupt enabling users to manage each HDMI input.

### 8.6 High-bandwidth digital content protection (TDA19977A only)

The HDMI receiver also contains the HDCP decryption function. The keys provided by the OTP non-volatile memory in encrypted format are decrypted and then stored in the HDCP module. This is particularly suitable for repeater applications. The TDA19977A manages all HDCP repeater functions based on the HDCP 1.4 specification.

Three DDC-buses HSCLA/HSDAA; HSCLB/HSDAB and HSCLC/HSDAC are integrated into the HDCP function, one bus for each HDMI input. The DDC-bus connected to the HDCP block is automatically selected based on the active HDMI input. The unused inputs are disconnected from the DDC-bus (no acknowledge). No additional CPU processing is required because the authentication phase and the re-key calculation are fully managed by the TDA19977A.

### 8.7 Color depth unpacking

In Deep Color mode, the TDA19977A; TDA19977B receives several fragments of a pixel group at the HDMI link frequency. This block translates the received pixel group into pixels at the pixel frequency. This operation is fully automatic and does not need any external control.

### 8.8 Derepeater

The HDMI source uses pixel repetition to increase the transmitted pixel clock for transmitting video formats at native pixel rates below 25 Mpixel/s or to increase the number of audio sample packets in each line. The derepeater function discards repeated pixels and divides the clock to reproduce the native video format.

### 8.9 Upsample

The HDMI source can use YCbCr 4:2:2 pixel encoding which enables the number of bits allocated per component to be increased up to 12. The upsample function transforms this 12-bit YCbCr 4:2:2 data stream into a 12-bit YCbCr 4:4:4 data stream by repeating or linearly interpolating the chrominance pixels Cb and Cr.

Upsampling mode is selected using the I<sup>2</sup>C-bus.

TDA19977A\_TDA19977B

Product data sheet

© NXP B.V. 2010. All rights reserved

#### 8.10 Packet extraction

Information sent during the Data Island periods are extracted from the HDMI data stream. Audio clock regeneration, general control and Info Frames can be read using the I<sup>2</sup>C-bus while audio samples are sent to the audio FIFO.

The TDA19977A; TDA19977B can receive the new HDMI 1.4a packets, general control and color gamut metadata information packets.

In audio applications, the TDA19977A; TDA19977B manages HBR packets for high bit rate compressed audio streams (IEC 61937), OBA samples and DST packets for OBA and SACD with DSD and DST audio streams.

The TDA19977A; TDA19977B includes a two channel status decoder supporting multi-channel reception for audio sample packets. This enables the user to obtain channel status information from the IEC 60958/IEC 61937 stream such as:

- The audio stream type (non-linear as IEC 61937 or L-PCM as IEC 60958)

- Copyright protection

- Sampling frequency

Refer to IEC 60958/IEC 61937 specifications for more details.

An update of each Info Frame or the channel status content is indicated by a register bit and the HIGH-to-LOW transition on output pin VAI. This makes CPU polling unnecessary.

### 8.11 Audio PLL

The TDA19977A; TDA19977B generates a 128/256/512  $\times$  f<sub>s</sub> system clock enabling the use of simple audio DACs without an integrated PLL, such as the UDA1334BTS. The programming of the audio PLL can be either automatic, using the audio clock regeneration parameters found in the Data Islands or set manually using the I<sup>2</sup>C-bus.

All standard audio sampling frequencies 32 kHz, 44.1 kHz, 88.2 kHz, 176.4 kHz, 48 kHz, 96 kHz and 192 kHz are accepted by the device.

### 8.12 Audio formatter

Audio samples can be output in either S/PDIF, I<sup>2</sup>S-bus formats or DSD (SACD). In I<sup>2</sup>S-bus or S/PDIF modes, up to eight audio channels can be controlled using the audio port pins (AP0 to AP5). In DSD mode (SACD), up to six audio channels can be controlled using these pins. The audio port mapping depends on the channel allocation (see <u>Table 4</u>, <u>Table 5</u> and <u>Table 6</u> for detailed information).

TDA19977A\_TDA19977B

### Triple input HDMI receiver interface with digital processing

| Audio port | Pin | Layout 0                         |                            |                          |  |

|------------|-----|----------------------------------|----------------------------|--------------------------|--|

|            |     | l <sup>2</sup> S-bus             | S/PDIF                     | OBA                      |  |

| AP5        | 85  | SYSCLK <sup>[1]</sup>            | SYSCLK <sup>[1]</sup>      | '                        |  |

| AP4        | 83  | WS (word select)                 | WS[1]                      |                          |  |

| AP3        | 82  |                                  |                            |                          |  |

| AP2        | 81  |                                  |                            |                          |  |

| AP1        | 80  |                                  |                            | DSD channel 1            |  |

| AP0        | 79  | SD                               | S/PDIF                     | DSD channel 0            |  |

| ACLK       | 78  | SCK (I <sup>2</sup> S-bus clock) | master clock for S/PDIF[1] | DSD clock                |  |

|            |     | $64 \times f_{\text{s}}$         | $64 	imes f_s$             | $64 \times f_{\text{s}}$ |  |

|            |     | $32 \times f_s$                  |                            |                          |  |

## Table 4. Audio port configuration (Layout 0) All audio ports are LV-TTL compatible

[1] Can be activated with the I<sup>2</sup>C-bus (optional).

## Table 5. Audio port configuration (Layout 1) All outline ports are LV/TTL compatible

All audio ports are LV-TTL compatible.

| Audio port | Pin | Layout 0                         |                                        |                |  |  |

|------------|-----|----------------------------------|----------------------------------------|----------------|--|--|

|            |     | l <sup>2</sup> S-bus             | S/PDIF                                 | OBA            |  |  |

| AP5        | 85  | SYSCLK <sup>[1]</sup>            | SYSCLK <sup>[1]</sup>                  | DSD channel 5  |  |  |

| AP4        | 83  | WS (word select)                 | WS[1]                                  | DSD channel 4  |  |  |

| AP3        | 82  | SD3                              | S/PDIF3                                | DSD channel 3  |  |  |

| AP2        | 81  | SD2                              | S/PDIF2                                | DSD channel 2  |  |  |

| AP1        | 80  | SD1                              | S/PDIF1                                | DSD channel 1  |  |  |

| AP0        | 79  | SD0                              | S/PDIF0                                | DSD channel 0  |  |  |

| ACLK       | 78  | SCK (I <sup>2</sup> S-bus clock) | master clock for S/PDIF <sup>[1]</sup> | DSD clock      |  |  |

|            |     | $64 	imes f_s$                   | $64 \times f_s$                        | $64 	imes f_s$ |  |  |

|            |     | $32 \times f_{s}$                |                                        |                |  |  |

[1] Can be activated with the I<sup>2</sup>C-bus (optional).

# Table 6.Audio port configuration for HBR and DST packetsAll audio ports are LV-TTL compatible.

| Audio port | Pin | HBR demultiplexed                |                                        | DST              |

|------------|-----|----------------------------------|----------------------------------------|------------------|

|            |     | I <sup>2</sup> S-bus             | S/PDIF                                 |                  |

| AP5        | 85  | SYSCLK <sup>[1]</sup>            | SYSCLK <sup>[1]</sup>                  |                  |

| AP4        | 83  | WS (word select)                 | WS[1]                                  | frame_start      |

| AP3        | 82  | SDx + 3                          | S/PDIFx + 3                            |                  |

| AP2        | 81  | SDx + 2                          | S/PDIFx + 2                            |                  |

| AP1        | 80  | SDx + 1                          | S/PDIFx + 1                            |                  |

| AP0        | 79  | SDx                              | S/PDIFx                                | DSD channel 0    |

| ACLK       | 78  | SCK (I <sup>2</sup> S-bus clock) | master clock for S/PDIF <sup>[1]</sup> | DSD clock        |

|            |     | $64 \times f_s$ (ACR)            | $64 	imes f_s$                         | $64 	imes f_s$   |

|            |     | $32 \times f_s$ (ACR)            |                                        | $128 \times f_s$ |

[1] Can be activated with the I<sup>2</sup>C-bus (optional).

TDA19977A\_TDA19977B

**Product data sheet**

#### 8.13 Sync timing measurement

To assist input format recognition, the vertical/horizontal periods and the horizontal pulse width are measured based on the externally generated MCLK frequency (27 MHz crystal). This function has an accuracy of 1 LSB =  $1 \times MCLK$  period.

#### 8.14 Format measurement timing

The TDA19977A; TDA19977B includes an improved system for accurate recognition of PC and TV formats. This system measures the parameters of blanking and video active area.

This function can be useful for example when the TDA19977A; TDA19977B receives PC format data in HDMI or DVI modes.

#### 8.15 Color space conversion

The color space conversion enables an RGB signal from the HDMI input to be converted into a YCbCr signal or converting the YCbCr signal from the HDMI input into an RGB signal. The color space conversion formula is:

| YG   | $\begin{bmatrix} C_{11} & C_{12} & C_{13} \\ C_{21} & C_{22} & C_{23} \\ C_{31} & C_{32} & C_{33} \end{bmatrix} \times \begin{pmatrix} \begin{bmatrix} CY \\ RV \\ BU \end{bmatrix} + \begin{bmatrix} O11 \\ O12 \\ O13 \end{bmatrix} + \begin{bmatrix} O01 \\ O02 \\ O03 \end{bmatrix}$ |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| VR = | $C_{21} C_{22} C_{23} \times   RV + O12   + OO2$                                                                                                                                                                                                                                         | (1) |

| UB   | $C_{31} C_{32} C_{33}  (BU  013)  003$                                                                                                                                                                                                                                                   |     |

Activation of the color space conversion function, programming of all coefficients and offsets is done using the  $l^2C$ -bus.

#### 8.16 4:2:2 downsampling filters

These filters downsample the Cb and Cr signals by a factor of 2. A delay has been added to the G/Y channel corresponding to the downsample filters pipeline delay to make sure the Y channel is in phase with the Cb and Cr channels.

Four different filters, from simple cut to ITU-R BT.601 compliant digital, can be selected using the I<sup>2</sup>C-bus.

#### 8.17 Range control

The range control function truncates the range of data to remove super-white and super-black pixels at specified ceiling and floor values.

#### 8.18 Dithering function

The error dispersal rounding (dithering) function can convert the color depth from 30-bit or 36-bit to reduced 30-bit or 24-bit color depth. When dithering is triggered, the TDA19977A; TDA19977B applies round, truncate or noise-shaping algorithms.

When the error dispersal rounding function is not used, the data coming from the filter is directly sent to the 4:2:2 formatter. The error dispersal rounding function works only with the active video signal.

TDA19977A\_TDA19977B

#### 8.19 4:2:2 formatter

The 4:2:2 formatter contains the YCbCr 4:2:2 semi-planar and the YCbCr 4:2:2 ITU-R BT.656 formatting functions. The selection of these functions is made using the  $I^2$ C-bus.

- In YCbCr 4:2:2 mode: the data frequency for the Y signal is equal to the pixel clock frequency. While the data frequency for the Cb and Cr signals is equal to half the pixel clock frequency

- In semi-planar mode: the output clock should be the same as the pixel clock

- In ITU-R BT.656 mode: the data frequency should be the same as the formatter clock frequency (e.g. pixel clock × 2)

The Start Active Video (SAV) and End Active Video (EAV) timing reference codes can be included in the data stream based on the HREF, VREF and FREF positions from the VHREF timing generator.

Specific codes programmed using the I<sup>2</sup>C-bus can replace the data stream during the blanking period to mask gain and clamp calibration.

#### 8.20 Video port selection

Each channel can be allocated to a specified video port using the I<sup>2</sup>C-bus (see <u>Section 13</u> <u>"Output video port formats" on page 21</u>) to optimize board layout at the interface with video processing ICs. For example:

- R, G or B in RGB 4:4:4 mode on VP[29:20]

- Y, Cb or Cr in YUV 4:4:4 mode on VP[19:10]

- Y or Cb-Cr in 4:2:2 semi-planar mode on VP[9:0]

- Cb-Y-Cr-Y in 4:2:2 ITU-R BT.656 mode on VP[9:0]

Each video port can be set to high-impedance using the I<sup>2</sup>C-bus.

### 8.21 Output buffers

The levels of the output buffers are LV-TTL compatible. Switching the outputs between active and high-impedance is set using the  $l^2$ C-bus.

The outputs HREF, VREF and FREF can be set to high-impedance (Z) or forced LOW (L), independently of the timing reference codes.

#### 8.22 VHREF timing generator

The VHREF timing generator outputs all of the timing signals used by the device:

- VREF, HREF and FREF signals for SAV, EAV and active video area definition

- VS and HS to change width and position compared with the HDMI inputs

### 8.23 I<sup>2</sup>C-bus serial interface

The I<sup>2</sup>C-bus serial interface enables the internal registers of the device to be programmed. The slave address of the device is selected by pin A0.

| TDA19977A_TDA19977B |   |

|---------------------|---|

| Product data shee   | t |

Downloaded from Arrow.com.

#### 8.24 Power management

The TDA19977A; TDA19977B can use one of three Power-down modes:

- level 0: full Power-down mode

- level 1: internal EDID memory with I<sup>2</sup>C-bus serial interface active

- level 2: internal EDID memory with I<sup>2</sup>C-bus serial interface and activity detection enabled

The user can activate these different modes with pin PD or using I<sup>2</sup>C-bus registers:

- level 0: PD pin is HIGH

- level 1: settings defined in the I<sup>2</sup>C-bus registers

- level 2: with settings defined in the I<sup>2</sup>C-bus registers

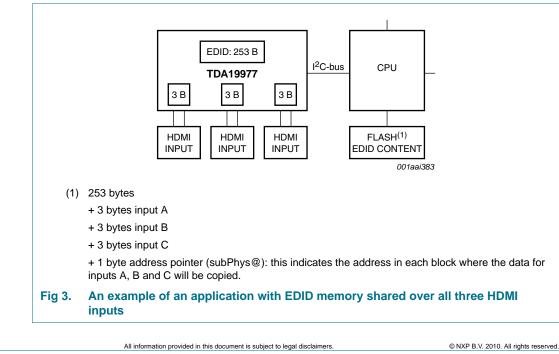

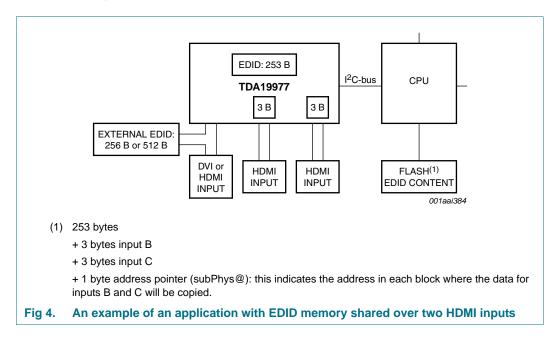

#### 8.25 EDID memory management

The TDA19977A; TDA19977B embedded EDID memory can be shared with all HDMI inputs. The embedded EDID memory shares 253 bytes with the three HDMI inputs. In addition, three bytes are dedicated to the physical address and checksum for each HDMI input (see Figure 3). This memory is accessible in parallel by all HDMI inputs. You can share the EDID memory over zero, one, two or three HDMI input(s) as shown in Figure 4.

The content of embedded volatile EDID memory must be programmed using the I<sup>2</sup>C-bus for each power-on of TDA19977A; TDA19977B. The embedded EDID memory remains accessible on each HDMI input when the TDA19977A; TDA19977B uses a different low-power mode.

The "physical address" of each HDMI input can be easily changed with the TDA19977A; TDA19977B without corrupting the integrity of each DDC-bus.

#### 8.25.1 EDID memory shared over all three HDMI inputs

TDA19977A\_TDA19977B

Product data sheet

Triple input HDMI receiver interface with digital processing

#### 8.25.2 EDID memory shared over two HDMI inputs

## 9. l<sup>2</sup>C-bus protocol

The TDA19977A; TDA19977B is a slave  $I^2$ C-bus device and the SCL pin is only an input pin. The timing and protocol for  $I^2$ C-bus are standard.

Bit A0 of the I<sup>2</sup>C-bus device address is externally selected by the A0 pin. The main device I<sup>2</sup>C-bus address is given in Table 7.

| Table 7. | I <sup>2</sup> C-bus | I <sup>2</sup> C-bus slave address |    |    |    |    |     |  |  |  |  |

|----------|----------------------|------------------------------------|----|----|----|----|-----|--|--|--|--|

| A6       | A5                   | A4                                 | A3 | A2 | A1 | A0 | R/W |  |  |  |  |

| 1        | 0                    | 0                                  | 1  | 1  | 0  | A0 | 0/1 |  |  |  |  |

## **10. Limiting values**

#### Table 8. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

|                       |                                  | •••        | ,     |       |      |

|-----------------------|----------------------------------|------------|-------|-------|------|

| Symbol                | Parameter                        | Conditions | Min   | Max   | Unit |

| V <sub>DDx(3V3)</sub> | supply voltage on all 3.3 V pins |            | -0.5  | +4.6  | V    |

| V <sub>DDx(1V8)</sub> | supply voltage on all 1.8 V pins |            | -0.5  | +2.5  | V    |

| $\Delta V_{DD}$       | supply voltage difference        |            | -0.5  | +0.5  | V    |

| lo                    | output current                   |            | -     | 35    | mA   |

| T <sub>stg</sub>      | storage temperature              |            | -55   | +150  | °C   |

| T <sub>amb</sub>      | ambient temperature              |            | 0     | 70    | °C   |

| Tj                    | junction temperature             |            | -     | 125   | °C   |

| V <sub>ESD</sub>      | electrostatic discharge voltage  | HBM        | -2000 | +2000 | V    |

|                       |                                  |            |       |       |      |

TDA19977A\_TDA19977B

## **11. Thermal characteristics**

| Table 9.             | Thermal characteristics                     |             |      |      |  |  |  |  |

|----------------------|---------------------------------------------|-------------|------|------|--|--|--|--|

| Symbol               | Parameter                                   | Conditions  | Тур  | Unit |  |  |  |  |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 22.8 | K/W  |  |  |  |  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |             | 11.1 | K/W  |  |  |  |  |

## **12. Characteristics**

#### Table 10. Characteristics

$T_{amb} = 0$  °C to 70 °C; typical values measured at  $T_{amb} = 25$  °C; unless otherwise specified.

| Symbol                   | Parameter                                            | Conditions                          |     | Min   | Тур  | Max   | Unit |

|--------------------------|------------------------------------------------------|-------------------------------------|-----|-------|------|-------|------|

| Supplies                 |                                                      |                                     |     |       |      |       |      |

| V <sub>DDH(3V3)</sub>    | HDMI supply voltage (3.3 V)                          |                                     |     | 3.135 | 3.3  | 3.465 | V    |

| V <sub>DDH(1V8)</sub>    | HDMI supply voltage (1.8 V)                          |                                     |     | 1.71  | 1.8  | 1.89  | V    |

| V <sub>DDI(3V3)</sub>    | input supply voltage (3.3 V)                         |                                     |     | 3.135 | 3.3  | 3.465 | V    |

| V <sub>DDC(1V8)</sub>    | core supply voltage (1.8 V)                          |                                     |     | 1.71  | 1.8  | 1.89  | V    |

| V <sub>DDO(3V3)</sub>    | output supply voltage (3.3 V)                        |                                     |     | 3.135 | 3.3  | 3.465 | V    |

| I <sub>DDH(3V3)</sub>    | HDMI supply current (3.3 V)                          | 720p at 60 Hz                       | [1] | -     | 103  | -     | mA   |

|                          |                                                      | 1080p at 60 Hz                      | [1] | -     | 106  | -     | mA   |

|                          |                                                      | 1080p at 60 Hz; Deep Color mode     | [1] | -     | 110  | -     | mA   |

| IDDH(1V8)                | HDMI supply current (1.8 V)                          | 720p at 60 Hz                       | [1] | -     | 48   | -     | mA   |

|                          |                                                      | 1080p at 60 Hz                      | [1] | -     | 68   | -     | mA   |

|                          |                                                      | 1080p at 60 Hz; Deep Color mode     | [1] | -     | 85   | -     | mA   |

| I <sub>DDI(3V3)</sub>    | input supply current (3.3 V)                         | 720p at 60 Hz                       | [1] | -     | 1    | -     | mA   |

|                          |                                                      | 1080p at 60 Hz                      | [1] | -     | 1    | -     | mA   |

|                          |                                                      | 1080p at 60 Hz; Deep Color mode     | [1] | -     | 1    | -     | mA   |

| I <sub>DDO(3V3)</sub>    | output supply current (3.3 V)                        | 720p at 60 Hz                       | [1] | -     | 49   | -     | mA   |

|                          |                                                      | 1080p at 60 Hz                      | [1] | -     | 78   | -     | mA   |

|                          |                                                      | 1080p at 60 Hz; Deep Color mode     | [1] | -     | 120  | -     | mA   |

| IDDC(1V8)                | core supply current (1.8 V)                          | 720p at 60 Hz                       | [1] | -     | 148  | -     | mA   |

|                          |                                                      | 1080p at 60 Hz                      | [1] | -     | 283  | -     | mA   |

|                          |                                                      | 1080p at 60 Hz; Deep Color mode     | [1] | -     | 453  | -     | mA   |

| $\Delta V_{DD(3V3-3V3)}$ | supply voltage difference between two 3.3 V supplies | start-up and established conditions |     | -100  | -    | +100  | mV   |

| $\Delta V_{DD(1V8-1V8)}$ | supply voltage difference between two 1.8 V supplies | start-up and established conditions |     | -100  | -    | +100  | mV   |

| Р                        | power dissipation                                    | active mode                         | [1] |       |      |       |      |

|                          |                                                      | 720p at 60 Hz                       |     | -     | 0.75 | -     | W    |

|                          |                                                      | 1080p at 60 Hz                      |     | -     | 1.13 | -     | W    |

|                          |                                                      | 1080p at 60 Hz; Deep Color mode     |     | -     | 1.63 | -     | W    |

TDA19977A\_TDA19977B

## Triple input HDMI receiver interface with digital processing

#### Table 10. Characteristics ...continued

$T_{amb} = 0$  °C to 70 °C; typical values measured at  $T_{amb} = 25$  °C; unless otherwise specified.

| Symbol                | Parameter                             | Conditions                                                                                                                   | Min                      | Тур                        | Мах   | Unit |

|-----------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------|-------|------|

| P <sub>cons</sub>     | power consumption                     | Power-down mode                                                                                                              |                          |                            |       |      |

|                       |                                       | pin PD = HIGH                                                                                                                | -                        | 1                          | -     | mW   |

|                       |                                       | I <sup>2</sup> C-bus; EDID and HDCP <sup>[2]</sup><br>memory power-up                                                        | -                        | 4                          | -     | mW   |

|                       |                                       | I <sup>2</sup> C-bus; EDID; activity detection and HDCP <sup>[2]</sup> memory power-up                                       | -                        | 150                        | -     | mW   |

| Clock timi            | ng output: pins VCLK, ACLK and S      | /SCLK                                                                                                                        |                          |                            |       |      |

| f <sub>clk(max)</sub> | maximum clock frequency               | pin VCLK                                                                                                                     | 165                      | -                          | -     | MHz  |

|                       |                                       | pin ACLK                                                                                                                     | 25                       | -                          | -     | MHz  |

|                       |                                       | pin SYSCLK                                                                                                                   | 50                       | -                          | -     | MHz  |

| δ <sub>clk</sub>      | clock duty cycle                      | pin VCLK                                                                                                                     | -                        | 50                         | -     | %    |

|                       |                                       | pin ACLK                                                                                                                     | -                        | 50                         | -     | %    |

|                       |                                       | pin SYSCLK                                                                                                                   | -                        | 50                         | -     | %    |

| Timing out            | tput: pins VP[29:0];                  | = 10 pF; see <u>Figure 5</u>                                                                                                 |                          |                            |       |      |

| t <sub>su(Q)</sub>    | data output set-up time               | CLKOUT_DEL = 0;<br>CLKOUT_TOG = 0                                                                                            | 1.50                     | -                          | -     | ns   |

|                       |                                       | CLKOUT_DEL = 1;<br>CLKOUT_TOG = 1;<br>CLKOUT_DEL_SEL[2:0] = 4                                                                | 0.40                     | -                          | -     | ns   |

| t <sub>h(Q)</sub>     | data output hold time                 | CLKOUT_DEL = 0;<br>CLKOUT_TOG = 0                                                                                            | 0.80                     | -                          | -     | ns   |

|                       |                                       | CLKOUT_DEL = 1;<br>CLKOUT_TOG = 1;<br>CLKOUT_DEL_SEL[2:0] = 4                                                                | 2.00                     | -                          | -     | ns   |

| t <sub>d(pipe)</sub>  | pipeline delay time                   | from inputs to outputs; all modes; clock interval                                                                            | -                        | $80 \times T_{\text{clk}}$ | -     |      |

| Timing out            | tput: pins AP[5:0] with respect to A( | CLK; f <sub>clk</sub> = 12.288 MHz; C <sub>L</sub> = 10 pF; s                                                                | see <mark>Figur</mark> e | e <u>6</u>                 |       |      |

| t <sub>su(Q)</sub>    | data output set-up time               |                                                                                                                              | 69                       | -                          | -     | ns   |

| t <sub>h(Q)</sub>     | data output hold time                 |                                                                                                                              | 2                        | -                          | -     | ns   |

| LV-TTL dig            | jital outputs: pins VP[29:0], VCLK, A | P[5:0], ACLK, DE, HS, VS, HREF, VI                                                                                           | REF, FRE                 | F; C <sub>L</sub> = 10     | pF    |      |

| V <sub>OL</sub>       | LOW-level output voltage              | I <sub>OL</sub> = 2 mA                                                                                                       | -                        | -                          | 0.4   | V    |

| V <sub>OH</sub>       | HIGH-level output voltage             | $I_{OH} = -2 \text{ mA}$                                                                                                     | 2.4                      | -                          | -     | V    |

| I <sub>LOZ</sub>      | OFF-state output leakage current      | high-impedance state; $V_0 = 0 V$                                                                                            | [3] _                    | 0                          | -     | μA   |

|                       |                                       | $V_O = V_{DDO(3V3)} \times {}^1 \vee_3$                                                                                      | 10                       | -                          | 100   | μA   |

|                       |                                       | $V_O = V_{DDO(3V3)} \times {}^2 \vee_3$                                                                                      | -100                     | -                          | -10   | μA   |

|                       |                                       | $V_O = V_{DDO(3V3)}$                                                                                                         | -                        | 0                          | -     | μA   |

| Digital inp           | uts: pins RXxC+, RXxC–[4]             |                                                                                                                              |                          |                            |       |      |

| V <sub>I(dif)</sub>   | differential input voltage            | $\label{eq:RRX1} \begin{array}{l} R_{RRX1} = 12 \; k\Omega \pm 1 \; \%; \\ R_{RRX2} = 12 \; k\Omega \pm 1 \; \% \end{array}$ | 150                      | -                          | 1200  | mV   |

| V <sub>I(cm)</sub>    | common-mode input voltage             |                                                                                                                              | 2.735                    | -                          | 3.475 | V    |

| f <sub>clk(max)</sub> | maximum clock frequency               |                                                                                                                              | 205                      | -                          | -     | MHz  |

|                       |                                       |                                                                                                                              |                          |                            |       |      |

| TDA19977A_TDA19977B | All information provided in this document is subject to legal disclaimers. | © NXP B.V. 2010. All rights reserved. |

|---------------------|----------------------------------------------------------------------------|---------------------------------------|

| Product data sheet  | Rev. 3 — 19 November 2010                                                  | 19 of 40                              |

#### Triple input HDMI receiver interface with digital processing

#### Table 10. Characteristics ... continued

$T_{amb} = 0$  °C to 70 °C; typical values measured at  $T_{amb} = 25$  °C; unless otherwise specified.

| Symbol                   | Parameter                        | Conditions                                                                                                                   | Min   | Тур | Max   | Unit |

|--------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| Digital inpu             | uts: pins RXx0+, RXx0–, RXx1+,   | RXx1–, RXx2+, RXx2– <u><sup>[4]</sup></u>                                                                                    |       |     |       |      |

| V <sub>I(dif)</sub>      | differential input voltage       | $\label{eq:RRX1} \begin{array}{l} R_{RRX1} = 12 \; k\Omega \pm 1 \; \%; \\ R_{RRX2} = 12 \; k\Omega \pm 1 \; \% \end{array}$ | 150   | -   | 1200  | mV   |

| V <sub>I(cm)</sub>       | common-mode input voltage        |                                                                                                                              | 2.735 | -   | 3.475 | V    |

| I <sup>2</sup> C-bus: pi | ns SCL and SDA <sup>[5]</sup>    |                                                                                                                              |       |     |       |      |

| f <sub>SCL</sub>         | SCL clock frequency              |                                                                                                                              | -     | -   | 400   | kHz  |

| Cb                       | capacitive load for each bus lin | e                                                                                                                            | -     | -   | 400   | pF   |

| Ci                       | capacitance for each I/O pin     |                                                                                                                              | -     | -   | 10    | pF   |

| DDC I <sup>2</sup> C-bu  | us: pins HSCLx, HSDAx [4][6]     |                                                                                                                              |       |     |       |      |

| f <sub>SCL</sub>         | SCL clock frequency              | Standard-mode                                                                                                                | -     | -   | 100   | kHz  |

|                          |                                  | Fast-mode                                                                                                                    | -     | -   | 400   | kHz  |

| Ci                       | capacitance for each I/O pin     |                                                                                                                              | -     | -   | 10    | pF   |

[1] At 30 % activity on video port output.

[2] HDCP decoding is only supported by TDA19977A.