# STUSBCD01B

## USB charger detection interface

## Features

- Capable of detecting dedicated USB chargers and host chargers (current sink and dedicated methods)

- Operates with V<sub>BAT</sub> supply voltage ranging from 2.2 V to 4.5 V

- Active high open drain hardware detection pin (DETECT)

- GPIO control interface

- 1.6 V 2.8 V interface voltage range (V<sub>IO</sub>)

- V<sub>BUS</sub> voltage 6 V clamping circuit

- Low DP-DM input capacitance

- ESD: HBM ± 2 kV, CDM 500 V on every pin

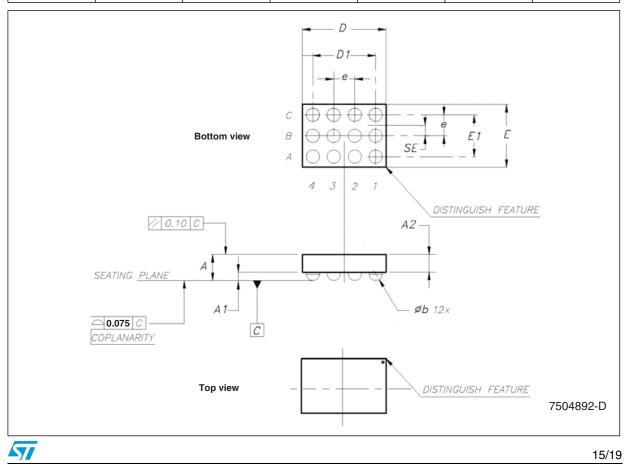

- 12 bumps Flip-Chip package, 1.6 x1.2 mm, pitch 0.4 mm, max thickness 0.60 mm, Halogen free RoHS compliant package

## **Applications**

- Mobile phones

- PDAs, MP3 players

## Description

The STUSBCD01B is a USB charger detection IC which can detect dedicated USB chargers, Host/Hub chargers or standard host ports connected to the USB DP/DM data lines.

The device implements two different detection methods in order to be able to distinguish between a dedicated charger and a Host/Hub charger.

Operation is controlled through three general purpose I/O pins; a hardware open drain detection output is also available.

An internal regulator provides the 1.8 V supply voltage for the internal blocks and state machine while a clamping device prevents  $V_{BUS}$  voltage from going over 6 V (typ.).

The STUSBCD01B is available in a 12 bumps Flip-Chip 0.4 mm pitch package.

#### Table 1. Device summary

| Order code   | Package                     | Packaging           |  |

|--------------|-----------------------------|---------------------|--|

| STUSBCD01BJR | Flip-Chip 12 (1.6 x 1.2 mm) | 3000 parts per reel |  |

November 2008

www.st.com

57

## Contents

| 1 | Application                                |

|---|--------------------------------------------|

| 2 | Pin configuration                          |

| 3 | Functional description5                    |

|   | 3.1 Detection methods 5                    |

|   | 3.2 Dedicated charger detection method 5   |

|   | 3.3 Current sink method 5                  |

|   | 3.4         Detection triggering         6 |

|   | 3.5 V <sub>BUS</sub> clamping 6            |

|   | 3.6 Internal regulator 6                   |

| 4 | Functional tables                          |

| 5 | Maximum ratings                            |

| 6 | Electrical characteristics                 |

| 7 | Timing diagrams                            |

| 8 | Package mechanical data 14                 |

| 9 | Revision history                           |

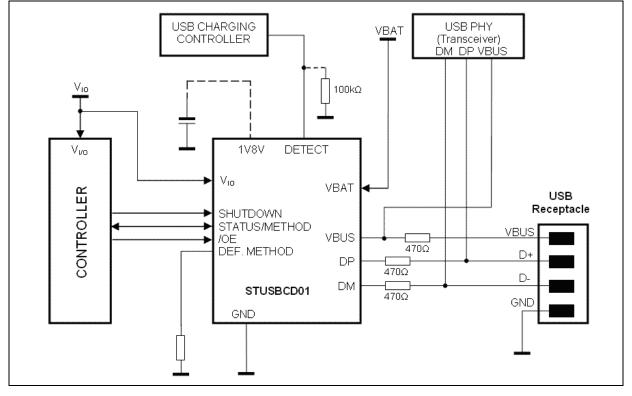

## 1 Application

57

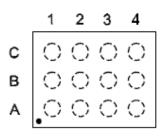

# 2 Pin configuration

| Figure 2. | Bump configuration | (top through view) |

|-----------|--------------------|--------------------|

|-----------|--------------------|--------------------|

#### Table 2. Pin description

| Bump<br>name | Symbol            | Туре | Description                                                                                                                                                                                                                                            |

|--------------|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C3           | VBAT              | PWR  | Analog supply voltage input (2.2 V - 4.5 V)                                                                                                                                                                                                            |

| C2           | GND               | PWR  | Ground reference                                                                                                                                                                                                                                       |

| A3           | V <sub>IO</sub>   | PWR  | Digital interface supply voltage (1.6 V - 2.8 V)                                                                                                                                                                                                       |

| B4           | DP                | AI/O | Connected to USB D+ Data line                                                                                                                                                                                                                          |

| A4           | DM                | AI/O | Connected to USB D- Data line                                                                                                                                                                                                                          |

| B2           | DETECT            | 0    | Hardware detection pin (open drain). 300 k $\Omega$ internal pull-down resistor. $V_{\text{BAT}}$ referred.                                                                                                                                            |

| A2           | SHUTDOWN          | I    | Standby mode selection pin. Active HIGH. Terminates the detection and resets the device.                                                                                                                                                               |

| A1           | /OE               | I    | Output enable for DETECT output. Active LOW.                                                                                                                                                                                                           |

| B1           | STATUS/<br>METHOD | AI/O | SW detection output: High when Charger detected. Pulled high or low through internal weak pull-up to 1V8V and weak pull-down. Detection method selection input: low for dedicated method, high for current sink method.                                |

| B3           | DEFAULT<br>METHOD | AI   | Hardware selection for detection method. Active only if $V_{IO}$ is not present.<br>Dedicated method is selected if driven low, current sink method if driven high.<br>$V_{BAT}$ referred. Do not leave floating to avoid increased power consumption. |

| C4           | VBUS              | AI   | $V_{\text{BUS}}$ voltage comparator input. Triggers the charger detection. 6V limited voltage when 10 V are applied externally.                                                                                                                        |

| C1           | 1V8V              | 0    | Regulator output voltage. Bypass capacitor not required.                                                                                                                                                                                               |

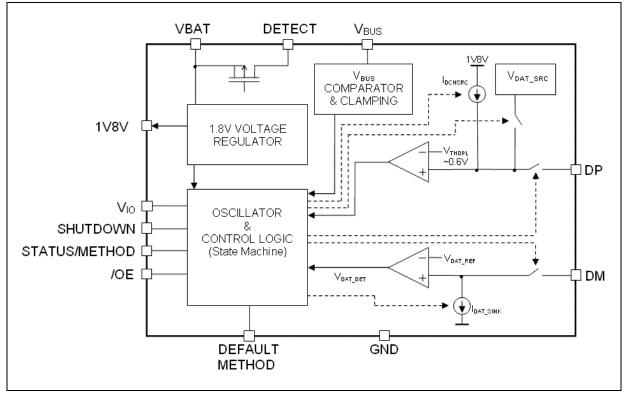

## 3 Functional description

The STUSBCD01B is designed to provide USB charger detection functionality to USB platforms which do not have this feature integrated in the PHY. The device can work with a supply voltage ranging from 2.2 V to 4.5 V and has an internal regulator which generates the 1.8 V voltage required for the internal blocks and state machine.

The STUSBCD01B can detect a dedicated charger or a Host/Hub charger connected to USB data lines and provides both an open drain pin and a digital I/O pin for the detection output signal. The open drain output can be disabled using the /OE input signal.

Two different detection methods, selectable through the STATUS/METHOD pin, are implemented in order to distinguish between a dedicated charger and a Host/Hub charger. If the interface voltage is not present the detection method is defined by the status of default method pin.

The STUSBCD01B features very low power consumption in Standby mode and low input capacitance on DP/DM pins. An over voltage protection circuit is also implemented on the VBUS pin in order to limit  $V_{BUS}$  voltage to 6 V and provide protection to external devices connected to it.

### 3.1 Detection methods

The STUSBCD01B implements a current source/sink method to detect dedicated chargers (wall chargers) and a current sink method for Host/Hub chargers (based on USB battery charging spec v1.0). If a standard Host/Hub is connected to the device it is recognized thanks to its pull-down resistors on DP/DM lines and therefore DETECT/STATUS outputs will be low.

### 3.2 Dedicated charger detection method

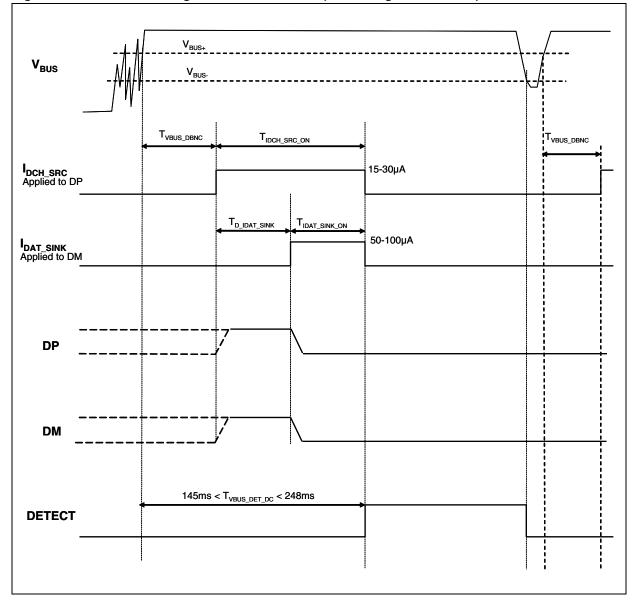

Selected driving method pin low during the falling edge of shutdown or driving default method pin low if V<sub>IO</sub> is not present. The dedicated charger detection method uses a current source on DP pin and a current sink on DM pin to detect the resistor (max 200  $\Omega$ ) which connects DP and DM in dedicated chargers.

### 3.3 Current sink method

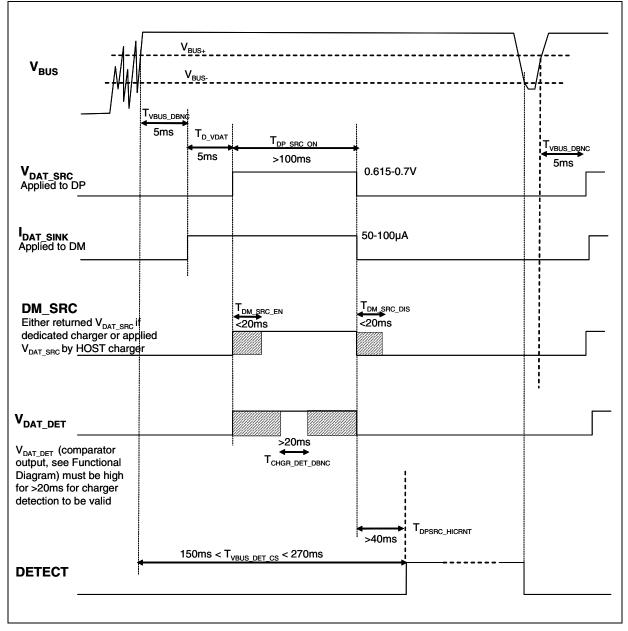

Selected driving method pin high during the falling edge of shutdown or driving default method pin high if  $V_{IO}$  is not present. A voltage source of VDAT\_SRC is connected to DP and a current of IDAT\_SINK is drawn from DM.

If a Host/Hub charger is connected, STUSBCD01B will see a voltage of VDAT\_SRC on pin DM. The same happens if a dedicated charger is connected and, therefore, in order to distinguish between the two, if the current sink method detection is successful it is necessary to run the dedicated charger detection method immediately after.

### 3.4 Detection triggering

USB Charger detection automatically starts when  $V_{BUS}$  voltage is over  $V_{TH\_VBUS}$  threshold and shutdown input is low.

If  $V_{BUS}$  drops under  $V_{TH\_VBUS}$  threshold or shutdown input is pulled high, the charger detection is immediately terminated.

If no charger is detected (DETECT = 0 and /OE = 0),  $V_{BUS}$  voltage is kept over  $V_{TH_VBUS}$  threshold and  $V_{IO}$  is not present then a new detection is started every 1 s.

If a charger is detected, detect and status pins are kept high until  $V_{BUS}$  drops under  $V_{TH}$  volume V<sub>TH</sub> volume volume

Any hardware detection (V<sub>IO</sub> not present) is terminated as soon as V<sub>IO</sub> voltage rises above V<sub>TH IO</sub> threshold.

## 3.5 V<sub>BUS</sub> clamping

The STUSBCD01B features a built in over voltage protection circuit which prevents  $V_{BUS}$  voltage from going over 6 V. The device is able to withstand continuous voltages of up to 10 V applied to  $V_{BUS}$  pin through an external resistor; in this case the clamping circuit limits the voltage to 6 V within 1 µs. A 470  $\Omega$  resistor in series between  $V_{BUS}$  voltage and  $V_{BUS}$  pin is required. Any external device needing  $V_{BUS}$  over-voltage protection must be connected to STUSBCD01B's  $V_{BUS}$  pin.

Minimum input resistance for  $V_{BUS}$  pin in normal operating conditions (up to ~ 5.3 V) is 400 k $\Omega$ .

### 3.6 Internal regulator

The STUSBCD01B has an internal regulator which outputs 1.8 V (nominal) to supply internal blocks. The regulator does not require any bypass capacitor for stability.

#### Figure 3. Functional diagram

## 4 Functional tables

| Table 3. | Operating mode |

|----------|----------------|

|----------|----------------|

| SHUTDOWN | /OE | V <sub>IO</sub> | VBAT          | VBUS          | STATUS-<br>DETECT | Operating mode          |

|----------|-----|-----------------|---------------|---------------|-------------------|-------------------------|

| Х        | Х   | Х               | Not available | х             | Х                 | Power down              |

| Н        | Х   | Available       | Available     | Not available | X <sup>(1)</sup>  | Standby (SW control)    |

| -        | -   | Not available   | Available     | Not available | L                 | Standby (NO SW control) |

| L        | Х   | Available       | Available     | Available     | L                 | Active, SW detection    |

| -        | -   | Not available   | Available     | Available     | L                 | Active, HW detection    |

1. Low when value is not forced by controller.

#### Table 4.Output signals

| V <sub>IO</sub> | Shutdown | Detection result     | /OE | Status/Method        | Detect                                |

|-----------------|----------|----------------------|-----|----------------------|---------------------------------------|

| Available       | L        | Charger detected     | L   | H (pull up active)   | Active (driving to $V_{BAT}$ )        |

| Available       | L        | Charger detected     | Н   | H (pull up active)   | L (internally pulled down)            |

| Available       | L        | Charger not detected | Х   | L (pull down active) | L (internally pulled down)            |

| Available       | Н        | -                    | Х   | Input                | L (internally pulled down)            |

| Not available   | -        | Charger detected     | -   | Undefined            | Active (driving to V <sub>BAT</sub> ) |

| Not available   | -        | Charger not detected | -   | Undefined            | L (internally pulled down)            |

### Table 5. Pin states during detection

| Detection method | DP                           | DM                          |

|------------------|------------------------------|-----------------------------|

| Dedicated        | Outputs I <sub>DCH_SRC</sub> | Sinks I <sub>DAT_SINK</sub> |

| Current sink     | Outputs V <sub>DAT_SRC</sub> | Sinks I <sub>DAT_SINK</sub> |

Note: See timing diagrams for more details.

## 5 Maximum ratings

| Symbol                            | Parameter                                                       | Value       | Unit |

|-----------------------------------|-----------------------------------------------------------------|-------------|------|

| V <sub>BAT</sub>                  | Battery supply voltage                                          | 6           | V    |

| N                                 | USB V <sub>BUS</sub> voltage                                    | 6           | V    |

| V <sub>BUS</sub>                  | USB $V_{BUS}$ voltage with external 470 $\Omega$ resistor       | 12          | V    |

| DP, DM, DETECT,<br>DEFAULT METHOD | Detection pins                                                  | 6           | V    |

| V <sub>X</sub>                    | All other pins                                                  | -0.5 to 4.6 | V    |

| T <sub>STG</sub>                  | Storage temperature range                                       | -65 to +150 | °C   |

| ESD <sup>(2)</sup>                | Electrostatic discharge voltage (according to HBM JESD22-A114D) | ± 2         | kV   |

|                                   | Electrostatic discharge voltage (according to CDM JESD22-C101C) | 200         | V    |

Table 6.Absolute maximum ratings (1)

1. Exceeding the absolute maximum rating may damage the device.

2. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5 k $\Omega$  in series with 100 pF.

Note: Absolute maximum ratings are those values above which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referenced to GND.

Table 7.

Recommended operating conditions <sup>(1)</sup>

| Symbol           | Parameter                | Min. | Тур. | Max. | Unit |

|------------------|--------------------------|------|------|------|------|

| V <sub>BAT</sub> | Analog supply voltage    | 2.2  | 4.2  | 4.5  | V    |

| V <sub>IO</sub>  | Interface supply voltage | 1.5  | 1.8  | 2.8  | V    |

| V <sub>BUS</sub> | V <sub>BUS</sub> voltage | 0    |      | 5.25 | V    |

1. The device is not guaranteed to function outside its operating rating.

9/19

## 6 Electrical characteristics

## Table 8.DC electrical characteristics (power supply and digital I/O pins) (1)(1)(1)(1)(1)(1)(1)(2)(1)(2)(1)

$(V_{BAT} = 4.2 \text{ V}, T_A = 25^{\circ}\text{C}, \text{ specifications over temperature, -40 to 85 °C})$

| Symbol             | Parameter                                     | Test conditions                                    | Min.                     | Тур. | Max.                  | Unit |

|--------------------|-----------------------------------------------|----------------------------------------------------|--------------------------|------|-----------------------|------|

| 1V8V               | LDO regulated voltage output                  | $V_{BUS} > V_{TH_VBUS}$ , $V_{BAT} = 2.2V$ to 4.5V | 1.76                     | 1.8  | 1.84                  | v    |

| I=                 | V <sub>BAT</sub> supply current               | V <sub>BAT</sub> = 2.2 to 4.5V; Standby mode       |                          |      | 20                    | μA   |

| IBAT               |                                               | V <sub>BAT</sub> = 2.2 to 4.5V; Detection          |                          |      | 1                     | mA   |

| I <sub>IO</sub>    | V <sub>IO</sub> supply current                | STATUS/METHOD="open"                               |                          |      | 5                     | μA   |

| V <sub>TH_IO</sub> | V <sub>IO</sub> detection threshold voltage   |                                                    |                          | 1    |                       | V    |

| V <sub>IL</sub>    | Low level input voltage ( <i>Note 1</i> )     | V <sub>IO</sub> = 1.6 to 2.8V                      |                          |      | 0.15 V <sub>IO</sub>  | v    |

| V <sub>IH</sub>    | High level input voltage (Note 1)             | V <sub>IO</sub> = 1.6 to 2.8V                      | 0.85 V <sub>IO</sub>     |      |                       | v    |

| V <sub>ILDM</sub>  | Low level input voltage<br>( <i>Note 2</i> )  |                                                    |                          |      | 0.15 V <sub>BAT</sub> | v    |

| V <sub>IHDM</sub>  | High level input voltage<br>( <i>Note 2</i> ) |                                                    | 0.85<br>V <sub>BAT</sub> |      |                       | v    |

| Ι <sub>ΙL</sub>    | Low level input leakage<br>(SHUTDOWN, /OE)    | $V_{IO}$ = 1.6 to 2.8V, all inputs at GND          |                          |      | ±5                    | μA   |

| I <sub>IH</sub>    | High level input leakage<br>(SHUTDOWN, /OE)   | $V_{IO}$ = 1.6 to 2.8V, all inputs at $V_{IO}$     |                          |      | ±5                    | μA   |

| V <sub>OL</sub>    | Low level output voltage<br>(STATUS)          | I <sub>OL</sub> = +10μA, V <sub>IO</sub> = 1.8V    | 0                        |      | 100                   | mV   |

| V <sub>OH</sub>    | High level output voltage<br>(STATUS)         | I <sub>OH</sub> = -10μA, V <sub>IO</sub> = 1.8V    | 1.7                      |      | 1.8                   | v    |

| C <sub>IN</sub>    | Input capacitance ( <i>Note 1</i> )           |                                                    |                          | 4    |                       | pF   |

1. Characterized specification(s), but not production tested.

Note: 1 Specification applies to the following pins: /OE, SHUTDOWN, STATUS/METHOD 2 Specification applies to DEFAULT METHOD pin.

| (V <sub>BAT</sub> = 4.2 V, T <sub>A</sub> = 25 °C | c, specifications over | r temperature, | -40 to 85 °C) |

|---------------------------------------------------|------------------------|----------------|---------------|

|                                                   |                        |                |               |

| Symbol                | Parameter                                     | Test conditions                                                | Min.                  | Тур. | Max.             | Unit |

|-----------------------|-----------------------------------------------|----------------------------------------------------------------|-----------------------|------|------------------|------|

| V <sub>BUS</sub>      | V <sub>BUS</sub> voltage                      |                                                                | 0                     |      | 5.25             | V    |

| I <sub>VBUS</sub>     | V <sub>BUS</sub> current                      | V <sub>BUS</sub> =0 to 5.25V                                   |                       |      | 10               | μA   |

| $V_{BUS\_CLMP}$       | V <sub>BUS</sub> clamping voltage             | R <sub>EXT</sub> = 470Ω                                        | 5.3                   |      | 6                | V    |

| V <sub>TH_VBUS</sub>  | V <sub>BUS</sub> voltage detection threshold  |                                                                | 2                     |      | 4                | V    |

| Z <sub>IN_VBUS</sub>  | V <sub>BUS</sub> input impedance              | V <sub>BUS</sub> max 5.25V                                     | 400                   |      |                  | kΩ   |

| C <sub>IN</sub>       | DP, DM input capacitance                      |                                                                |                       |      | 5                | pF   |

| V <sub>DAT_SRC</sub>  | Data source voltage (1)                       | I <sub>DP</sub> =I <sub>DAT_SRC</sub> <sup>(2)</sup>           | 0.615                 | 0.65 | 0.7              | V    |

| $V_{DAT\_REF}$        | Data detect voltage                           |                                                                | 0.25                  |      | 0.34             | V    |

| I <sub>DAT_SINK</sub> | Data sink current                             | V <sub>DM</sub> =V <sub>DAT_SINK</sub> <sup>(3)</sup>          | 50                    |      | 100              | μA   |

| I <sub>DCH_SRC</sub>  | Dedicated charger detection DP source current |                                                                | 15                    |      | 30               | μA   |

| V <sub>THDPL</sub>    | DP low threshold                              |                                                                |                       | 0.6  |                  | V    |

| Z <sub>PD_DET</sub>   | DETECT pin pull down impedance                | /OE=1                                                          | 240                   | 300  | 360              | kΩ   |

| V <sub>OH_DET</sub>   | DETECT output driving voltage                 | I <sub>OH_DET</sub> = 0.5mA,<br>V <sub>BAT</sub> = 2.2 to 4.5V | V <sub>BAT</sub> -0.2 |      | V <sub>BAT</sub> | v    |

1. Measured at DP pin. Includes effect of internal switches.

2.  $I_{DAT\_SRC} = 0$  to 200 µA according to USB specs.

3.  $V_{DAT\_SINK} = 0.15 V$  to 3.6 V according to USB specs.

### Table 10. AC electrical characteristics <sup>(1)</sup>

### $(V_{BAT} = 4.2 \text{ V}, T_A = 25 \text{ °C}, \text{ specifications over temperature, -40 to 85 °C})$

| Symbol                     | Parameter                                     | Test conditions                           | Min. | Тур. | Max. | Unit |

|----------------------------|-----------------------------------------------|-------------------------------------------|------|------|------|------|

| T <sub>VBUS_DBNC</sub>     | V <sub>BUS</sub> debounce time                |                                           | 5    |      | 8    | ms   |

| T <sub>DP_SRC_ON</sub>     | DP source on time                             | Current sink method                       | 100  |      | 170  | ms   |

| T <sub>CHGR_DET_DBNC</sub> | Charger detect debounce                       | Current sink method                       | 20   |      | 40   | ms   |

| T <sub>DPSRC_HICRNT</sub>  | DP source off to DETECT high time             | Current sink method                       | 40   |      | 70   | ms   |

| T <sub>D_VDAT</sub>        | V <sub>DAT_SRC</sub> on delay                 | Current sink method                       | 5    |      | 8    | ms   |

| T <sub>VBUS_DET_CS</sub>   | V <sub>BUS</sub> attach to DETECT high time   | Current sink method                       | 150  |      | 270  | ms   |

| T <sub>VBUS_DET_DC</sub>   | V <sub>BUS</sub> attach to DETECT high time   | Dedicated charger method                  | 145  |      | 248  | ms   |

| T <sub>IDCH_SRC_ON</sub>   | I <sub>DCH_SRC</sub> on time <sup>(2)</sup>   | Dedicated charger method                  | 140  |      | 240  | ms   |

| T <sub>IDAT_SINK_ON</sub>  | I <sub>DAT_SINK</sub> on time                 | Dedicated charger method                  | 40   |      | 70   | ms   |

| T <sub>D_IDAT_SINK</sub>   | $I_{DCH\_SRC}$ on to $I_{DAT\_SINK}$ on delay | Dedicated charger method                  | 100  |      | 170  | ms   |

| T <sub>PER_DET</sub>       | Periodic detection period                     | detection period Hardware detection, No 1 |      |      | 1.6  | s    |

| T <sub>W_H/L</sub>         | Minimum pulse width High/Low                  | All digital inputs                        | 2    |      |      | μs   |

1. All AC parameters guaranteed by design but not production tested.

2.  $T_{IDCH\_SRC\_ON} = T_{D\_IDAT\_SINK} + T_{IDAT\_SINK\_ON}$

57

## 7 Timing diagrams

Figure 5. Dedicated charger detection method (with charger connected)

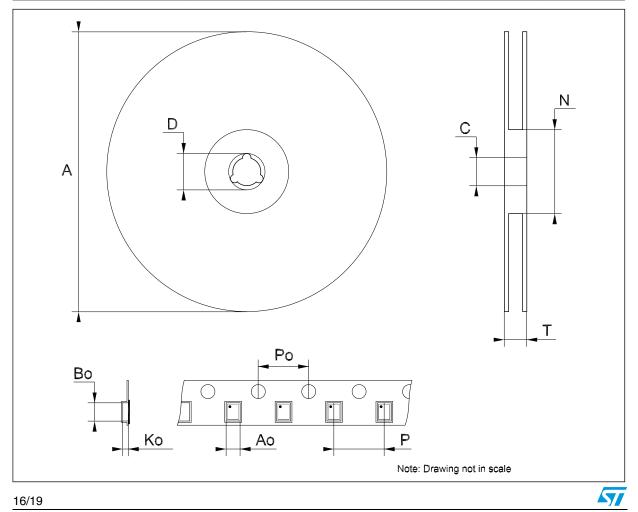

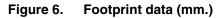

## 8 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

## Flip-Chip 12 mechanical data

| Dim  |       | mm.   |       | mils. |      |      |

|------|-------|-------|-------|-------|------|------|

| Dim. | Min.  | Тур.  | Max.  | Min.  | Тур. | Max. |

| А    | 0.52  | 0.56  | 0.60  | 20.5  | 22.0 | 23.6 |

| A1   | 0.17  | 0.20  | 0.23  | 6.7   | 7.9  | 9.1  |

| A2   | 0.35  | 0.36  | 0.37  | 13.8  | 14.2 | 14.6 |

| b    | 0.23  | 0.26  | 0.29  | 9.1   | 10.2 | 11.4 |

| D    | 1.543 | 1.593 | 1.643 | 60.7  | 62.7 | 64.7 |

| D1   |       | 1.20  |       |       | 47.2 |      |

| E    | 1.15  | 1.202 | 1.25  | 45.3  | 47.3 | 49.2 |

| E1   |       | 0.80  |       |       | 31.5 |      |

| е    |       | 0.40  |       |       | 15.7 |      |

| SE   |       | 0.20  |       |       | 7.9  |      |

Γ

|      | Tape & reel Flip-Chip 12 mechanical data |      |      |       |       |       |

|------|------------------------------------------|------|------|-------|-------|-------|

|      |                                          | mm.  |      | inch. |       |       |

| Dim. | Min.                                     | Тур. | Max. | Min.  | Тур.  | Max.  |

| А    |                                          |      | 180  |       |       | 7.087 |

| С    | 12.8                                     |      | 13.2 | 0.504 |       | 0.520 |

| D    | 20.2                                     |      |      | 0.795 |       |       |

| Ν    | 60                                       |      |      | 2.362 |       |       |

| Т    |                                          |      | 14.4 |       |       | 0.567 |

| Ao   | 1.43                                     | 1.48 | 1.53 | 0.056 | 0.058 | 0.060 |

| Во   | 1.71                                     | 1.76 | 1.81 | 0.067 | 0.069 | 0.071 |

| Ko   | 0.75                                     | 0.80 | 0.85 | 0.030 | 0.031 | 0.033 |

| Po   | 3.9                                      |      | 4.1  | 0.154 |       | 0.161 |

| Р    | 3.9                                      |      | 4.1  | 0.154 |       | 0.161 |

Downloaded from Arrow.com.

## 9 Revision history

### Table 11. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 18-Nov-2008 | 1        | Initial release. |

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com