# STULPI01A, STULPI01B

# High-speed USB On-The-Go ULPI transceiver

#### Datasheet -production data

# Features

- USB-IF high-speed certified to the universal serial bus specification rev. 2.0

- Meets the requirements of the universal serial bus specification rev. 2.0, On-The-Go supplement to the USB 2.0 specification 1.0a and ULPI transceiver specification 1.1

- Standard ULPI (UTMI+ low pin interface) 1.1 digital interface

- Fully compliant with ULPI 1.1 register set

- External square wave clock with V<sub>DVIO</sub> amplitude must be applied to oscillator input XI

- Supports 480 Mbit/s High-speed, 12 Mbit/s Full-speed and 1.5 Mbit/s Low-speed modes of operation

- Supports 2.7 V UART mode

- Supports session request protocol (SRP) and host negotiation protocol (HNP) for dual-role device features

- Ability to control external charge pump for higher VBUS currents

- Single supply, +3 V to +4.5 V voltage range

- Integrated dual voltage regulator to supply internal circuits with stable 3.3 V and 1.2 V

- Integrated overcurrent detector

- Integrated HS termination and FS/LS/OTG pull-up/pull-down resistors

- Integrated USB 2.0 "short-circuit withstand" protection

- Power-down mode with very low-power consumption for battery-powered devices

- Ideal for system ASICs with built-in USB host, device or OTG cores

- Available in µTFBGA36 RoHS package

- -40 to 85 °C operating temperature range

# **Applications**

- Mobile phones

- PDAs

- MP3 players

- Digital still cameras

- Set-top box

- Portable navigation devices

# Description

The STULPI01 is a high-speed USB 2.0 transceiver compliant with ULPI (UTMI+ low pin interface) and OTG (On-The-Go) specifications, providing a complete physical layer solution for any high-speed USB host, device or OTG dualrole core. It allows USB ASICs to interface with the physical layer of the USB through a 12-pin interface. It contains VBUS comparators, an ID line detector, USB differential drivers and receivers and a complete ULPI register map and interrupt generator. The STULPI01 transceiver is suitable for mobile applications and batterypowered devices because of its low-power consumption, Power-down operating mode and minimal die/package dimensions.

This is information on a product in full production.

# Contents

| 1 | Appli  | cation diagrams                                        |

|---|--------|--------------------------------------------------------|

| 2 | Bump   | configuration                                          |

| 3 | Maxin  | num ratings                                            |

| 4 | Electi | ical characteristics                                   |

| 5 | Timin  | g diagram                                              |

| 6 | Block  | description                                            |

|   | 6.1    | Oscillator and PLL                                     |

|   | 6.2    | Voltage reference                                      |

|   | 6.3    | Power-on reset (POR) 18                                |

|   | 6.4    | UTMI + CORE                                            |

|   | 6.5    | ULPI wrapper                                           |

|   | 6.6    | External charge pump 19                                |

|   | 6.7    | VBUS comparators and VBUS overcurrent (OC) detector 19 |

|   | 6.8    | VB_REF_FAULT pin                                       |

|   | 6.9    | Voltage regulator                                      |

|   | 6.10   | ID detector                                            |

|   | 6.11   | USB 2.0 PHY                                            |

|   | 6.12   | Power saving features 21                               |

|   | 6.13   | Modes of operation 21                                  |

|   |        | 6.13.1 ULPI synchronous mode                           |

|   |        | 6.13.2 6-pin FS/LS serial mode                         |

|   |        | 6.13.3 3-pin FS/LS serial mode                         |

|   | 6.14   | Car Kit (UART) mode                                    |

|   | 6.15   | Low-power mode                                         |

|   | 6.16   | Power-down mode                                        |

|    | 6.17  | VIO OFI   | F mode                   |

|----|-------|-----------|--------------------------|

|    | 6.18  | Startup   | procedure                |

|    |       | 6.18.1    | ULPI device detection    |

|    |       | 6.18.2    | SDR mode selection       |

|    |       | 6.18.3    | External clock detection |

|    |       | 6.18.4    | Reset behavior           |

|    |       | 6.18.5    | Interface protection     |

|    |       | 6.18.6    | Software reset           |

|    |       | 6.18.7    | High-speed mode entry25  |

| 7  | State | transitio | ons                      |

| 8  | ULPI  | register  | s                        |

| 9  | Packa | ige mec   | hanical data             |

| 10 | Order | codes     |                          |

| 11 | Revis | ion hist  | ory                      |

# List of tables

| Table 1.  | Bill of materials - external components    | 6  |

|-----------|--------------------------------------------|----|

| Table 2.  | Pinout and bump description                | 7  |

| Table 3.  | Absolute maximum ratings                   | 9  |

| Table 4.  | Thermal data                               | 9  |

| Table 5.  | Recommended operating conditions           | 9  |

| Table 6.  | Electrical characteristics                 | 0  |

| Table 7.  | Switching characteristics                  | 4  |

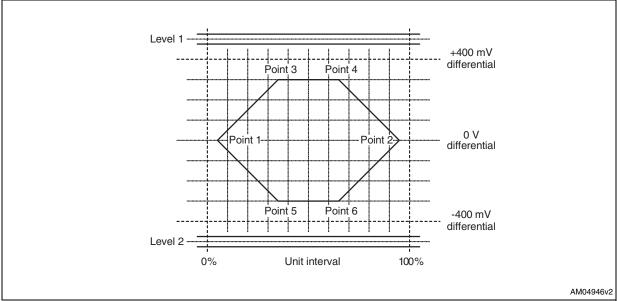

| Table 8.  | High-speed driver eye pattern1             | 6  |

| Table 9.  | VB_REF_FAULT configuration bit settings 2  | 0  |

| Table 10. | Car kit signals mapping                    | 2  |

| Table 11. | Low-power mode                             | 3  |

| Table 12. | USB state transitions                      | 8  |

| Table 13. | ULPI register map overview                 | 0  |

| Table 14. | Register access legend                     | 0  |

| Table 15. | Vendor and product ID                      | 1  |

| Table 16. | Power control register                     | 1  |

| Table 17. | Function control register                  | 2  |

| Table 18. | Interface control register                 | 3  |

| Table 19. | OTG control register                       |    |

| Table 20. | USB interrupt enable rising register       | 5  |

| Table 21. | USB interrupt enable falling register 3    | 6  |

| Table 22. | USB interrupt status register              | 6  |

| Table 23. | USB interrupt latch register               | 7  |

| Table 24. | Setting rules for interrupt latch register |    |

| Table 25. | Debug register                             | 8  |

| Table 26. | Scratch register                           | 8  |

| Table 27. | Car kit control register                   | 8  |

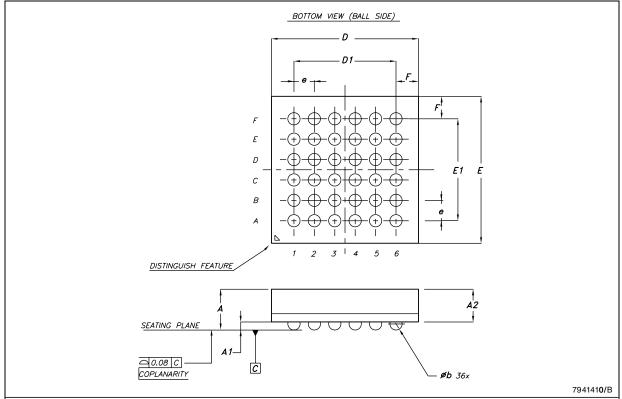

| Table 28. | µTFBGA36 mechanical data                   | 0  |

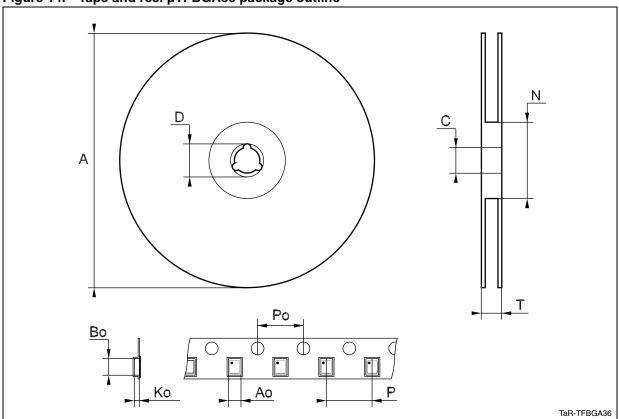

| Table 29. | Tape and reel µTFBGA36 mechanical data 4   | 1  |

| Table 30. | Order codes                                | .2 |

| Table 31. | Document revision history                  | .3 |

|           |                                            |    |

# List of figures

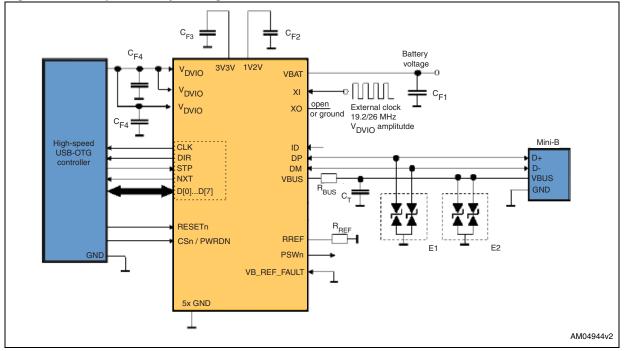

| Figure 1.  | Peripheral only, configuration with external clock. | . 6 |

|------------|-----------------------------------------------------|-----|

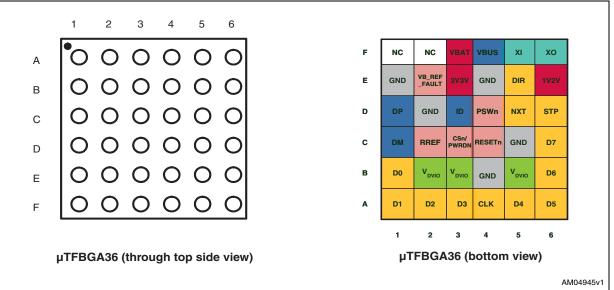

| Figure 2.  | Pin connections                                     | . 7 |

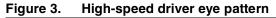

| Figure 3.  | High-speed driver eye pattern                       | 16  |

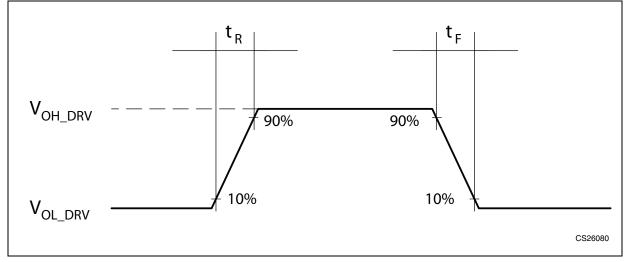

| Figure 4.  | Rise and fall time                                  | 17  |

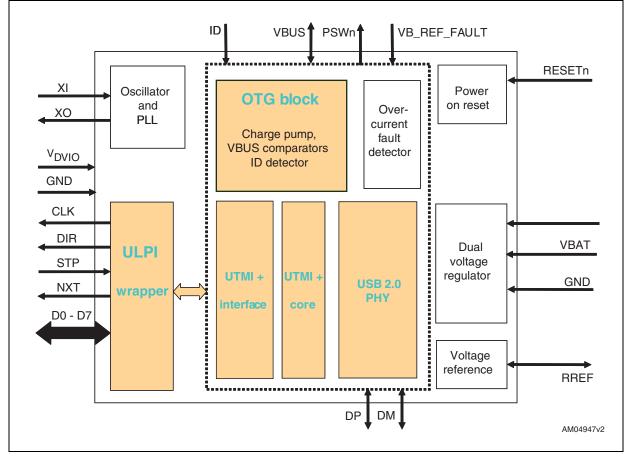

| Figure 5.  | Simplified block diagram                            | 17  |

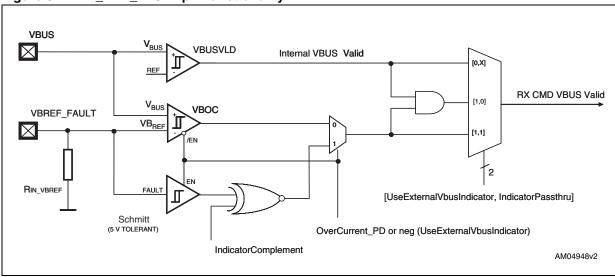

| Figure 6.  | VB_REF_FAULT pin functionality                      | 20  |

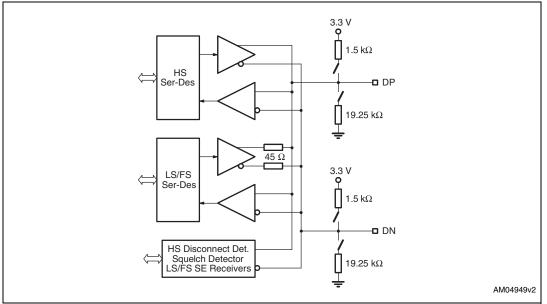

| Figure 7.  | USB 2.0 PHY block diagram.                          | 21  |

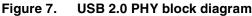

| Figure 8.  | Startup sequence                                    | 25  |

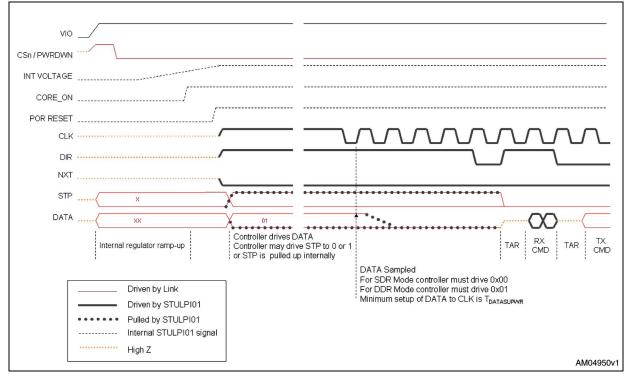

| Figure 9.  | RESETn behavior                                     | 26  |

| Figure 10. | High-speed mode entry                               | 26  |

| Figure 11. | UART mode entry (2.7 V)                             | 27  |

| Figure 12. | UART mode exit (2.7 V)                              | 27  |

| Figure 13. | µTFBGA36 package outline                            | 40  |

| Figure 14. | Tape and reel µTFBGA36 package outline              | 41  |

# 1 Application diagrams

### Figure 1. Peripheral only, configuration with external clock

| Table 1. | Bill of materials - external components |

|----------|-----------------------------------------|

|          | Din of materials - external components  |

|      | of materials - exteri |               |                                                                                                                                                                        |

|------|-----------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Qty. | Symbol                | Value         | Description                                                                                                                                                            |

| 1    | C <sub>F1</sub>       | 0.1 - 1 µF    | Filtering capacitor. Suggested components:<br>Murata 10 V X5R (GRM188R61A105KA61) or<br>Murata 10 V Y5V (GRM188F51A105ZA01) or<br>TAIYO YUDEN 25 V X5R (TMK107BJ105KA) |

| 2    | C <sub>F4</sub>       | 0.1 - 1 µF    | Filtering capacitor. Suggested components:<br>Murata 10 V X5R (GRM188R61A105KA61) or<br>Murata 10 V Y5V (GRM188F51A105ZA01) or<br>TAIYO YUDEN 25 V X5R (TMK107BJ105KA) |

| 1    | C <sub>F2</sub>       | 1 μF - 1.5 μF | Filtering capacitor. Suggested components:<br>Murata 10 V X5R (GRM188R61A105KA61) or<br>Murata 10 V Y5V (GRM188F51A105ZA01) or<br>TAIYO YUDEN 25 V X5R (TMK107BJ105KA) |

| 1    | C <sub>F3</sub>       | 1 - 4.7 µF    | Filtering capacitor. Suggested components:<br>Murata 10 V Y5V (GRM188F51A475ZE20) or<br>TAIYO YUDEN 6.3 V X5R (JMK107BJ475KA)                                          |

| 1    | C <sub>T</sub>        | 4.7 μF        | Tank capacitor                                                                                                                                                         |

| 1    | R <sub>REF</sub>      | 12 kΩ         | Reference resistor ±1%                                                                                                                                                 |

| 1    | E1                    |               | USBULC6-2F3                                                                                                                                                            |

| 1    | E2                    |               | ESDA14V2-2BF3                                                                                                                                                          |

| 1    | R <sub>BUS</sub>      | 2.2 kΩ        | Series overvoltage protection resistor                                                                                                                                 |

Doc ID 14817 Rev 4

# 2 Bump configuration

#### Figure 2. Pin connections

#### Table 2. Pinout and bump description

| Bump | Symbol    | Туре | Description                                                                                      |  |  |

|------|-----------|------|--------------------------------------------------------------------------------------------------|--|--|

| B1   | D0        | I/O  | Data bit [0] (V <sub>DVIO</sub> referred). UART TXD signal.                                      |  |  |

| A1   | D1        | I/O  | Data bit [1] (V <sub>DVIO</sub> referred). UART RXD signal.                                      |  |  |

| A2   | D2        | I/O  | Data bit [2] (V <sub>DVIO</sub> referred). UART reserved pin.                                    |  |  |

| A3   | D3        | I/O  | Data bit [3] (V <sub>DVIO</sub> referred). UART active high interrupt indication.                |  |  |

| A4   | CLK       | 0    | Clock out (V <sub>DVIO</sub> referred)                                                           |  |  |

| A5   | D4        | I/O  | Data bit [4] (V <sub>DVIO</sub> referred)                                                        |  |  |

| A6   | D5        | I/O  | Data bit [5] (V <sub>DVIO</sub> referred)                                                        |  |  |

| B6   | D6        | I/O  | Data bit [6] (V <sub>DVIO</sub> referred)                                                        |  |  |

| C6   | D7        | I/O  | Data bit [7] (V <sub>DVIO</sub> referred)                                                        |  |  |

| D6   | STP       | I    | ULPI stop signal (V <sub>DVIO</sub> referred)                                                    |  |  |

| D5   | NXT       | 0    | ULPI next signal (V <sub>DVIO</sub> referred)                                                    |  |  |

| E5   | DIR       | 0    | ULPI direction signal (V <sub>DVIO</sub> referred)                                               |  |  |

| C3   | CSn/PWRDN | I    | Chip select active low, power-down active high                                                   |  |  |

| C4   | RESETn    | I    | Active low asynchronous reset                                                                    |  |  |

| D1   | DP        | I/O  | Positive data line of the USB. 5 V tolerant.                                                     |  |  |

| C1   | DM        | I/O  | Negative data line of the USB. 5 V tolerant.                                                     |  |  |

| D3   | ID        | I    | ID pin of the USB connector for initial device role selection. 5 V tolerant.                     |  |  |

| F4   | VBUS      | I/O  | $V_{\text{BUS}}$ line of the USB interface, requires an external capacitor of 4.7 $\mu\text{F}.$ |  |  |

|      |           |      |                                                                                                  |  |  |

| Bump     | Symbol            | Туре | Description                                                                                                                          |

|----------|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| F1       | NC                |      | Not connected                                                                                                                        |

| F2       | NC                |      | Not connected.                                                                                                                       |

| E2       | VB_REF_FAULT      | I    | Voltage reference for internal OC detector input or digital input from external OC detector ( $V_{3V3V}$ referred). 5 V tolerant.    |

| D4       | PSWn              | 0    | External charge pump control, active low. 5 V tolerant, open drain.                                                                  |

| F5       | XI                | I    | External clock input (V <sub>DVIO</sub> referred).                                                                                   |

| F6       | ХО                | 0    | XO pin must be left floating or grounded (crystal is not supported).                                                                 |

| F3       | VBAT              | PWR  | Battery power input for the LDO (3 V – 4.5 V). Bypass $V_{BAT}$ to GND with a 1 $\mu F$ capacitor.                                   |

| E3       | 3V3V              | PWR  | 3.3 V LDO output. Bypass 3V3V to GND with a 1.5 $\mu$ F capacitor.                                                                   |

| E6       | 1V2V              | PWR  | 1.2 V LDO output. Bypass 1V2V to GND with a 1.5 $\mu$ F capacitor.                                                                   |

| C2       | RREF              | I/O  | Reference resistor (12 k $\Omega \pm 1\%$ )                                                                                          |

| B2/B3/B5 | V <sub>DVIO</sub> | PWR  | Digital I/O supply voltage. Bypass each $V_{DVIO}$ to GND with a 100 nF-1 $\mu$ F capacitor. Balls B2-B5 can share common capacitor. |

| C5/D2    | GND               | PWR  | Ground                                                                                                                               |

| B4/E4/E1 | GND               | PWR  | Ground                                                                                                                               |

Table 2.

Pinout and bump description (continued)

# 3 Maximum ratings

| Symbol               | Parameter                                                                      | Value        | Unit |

|----------------------|--------------------------------------------------------------------------------|--------------|------|

| V <sub>DVIO</sub>    | Digital I/O supply voltage                                                     | -0.3 to +4.0 | V    |

| V <sub>1V2</sub>     | Digital core supply voltage (provided internally by LDO)                       | -0.3 to +1.4 | V    |

| V <sub>3V3</sub>     | Analog supply voltage (provided internally by LDO)                             | -0.3 to +4.0 | V    |

| V <sub>BAT</sub>     | Battery supply voltage                                                         | -0.3 to +7.0 | V    |

| V <sub>DCDIG</sub>   | DC voltage on digital pins (CLK, DIR, STP, NXT, D[0-7], RESETn, XI, CSn/PWRDN) | -0.3 to +4.0 | V    |

| V <sub>DCVBUS</sub>  | DC voltage on 5 V tolerant pins (VBUS,VB_REF_FAULT, DP, DM, ID)                | -0.3 to +5.5 | V    |

| T <sub>STG</sub>     | Storage temperature range                                                      | -40 to +125  | °C   |

| V <sub>ESD-HBM</sub> | Electrostatic discharge voltage on all pins (according to JESD22-A114-B)       | ±2.0         | kV   |

#### Table 3. Absolute maximum ratings

Note: Absolute maximum ratings are those values above which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referenced to GND.

#### Table 4. Thermal data

| Symbol            | Parameter                                                                | Value | Unit |

|-------------------|--------------------------------------------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient (simulated value as per JEDEC JSD51) | 113.8 | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction-case (simulated value as per JEDEC JSD51)    | 47    | °C/W |

| R <sub>thJB</sub> | Thermal resistance junction-base (simulated value as per JEDEC JSD51)    | 66.2  | °C/W |

#### Table 5. Recommended operating conditions

| Symbol            | Parameter                                |       | Тур.       | Max.  | Unit |

|-------------------|------------------------------------------|-------|------------|-------|------|

| V <sub>BAT</sub>  | Battery supply voltage                   | 3.0   | 3.6        | 4.5   | V    |

| V <sub>DVIO</sub> | Digital I/O supply voltage               | 1.65  | 1.80       | 3.6   | V    |

| T <sub>A</sub>    | Operating temperature range              | -40   |            | +85   | °C   |

| C <sub>T</sub>    | Tank capacitor                           | 1     | 4.7        | 6.5   | μF   |

| R <sub>REF</sub>  | External reference resistor              | 11.88 | 12         | 12.12 | kΩ   |

| XTAL              | External square wave (01A, 01B versions) |       | 19.2 or 26 |       |      |

| ATAL              | Recommended rise/fall time               | 4     |            |       | ns   |

# 4 **Electrical characteristics**

| Symbol                | Parameter                                          | Test conditions <sup>(1)</sup>                                                   | Min.                        | Тур. | Max.                     | Unit |

|-----------------------|----------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------|------|--------------------------|------|

| Power consu           | mption                                             |                                                                                  |                             | •    |                          |      |

|                       |                                                    | Active mode (USB bus idle)                                                       |                             | 15   |                          | mA   |

|                       |                                                    | Active mode (FS<br>transmission, 12 Mb/s<br>traffic)                             |                             |      | 30                       | mA   |

|                       |                                                    | Active mode (HS transmission)                                                    |                             |      | 50                       | mA   |

| I <sub>BAT</sub>      | Supply current                                     | Suspend mode (not<br>including DP pull-up<br>current, external clock<br>stopped) |                             | 120  |                          | μA   |

|                       |                                                    | UART mode (no<br>transmission)                                                   |                             | 15   |                          | mA   |

|                       |                                                    | Power-down mode                                                                  |                             | 0.4  | 2                        | μA   |

|                       |                                                    | VIO OFF mode (V <sub>DVIO</sub> = 0)                                             |                             | 0.4  | 2                        | μA   |

| l=====                | ULPI bus supply current                            | Power-down mode                                                                  |                             | 0.1  | 10                       | μA   |

| I <sub>DVIO</sub>     | V <sub>DVIO</sub>                                  | Active mode, 4 pF load                                                           |                             | 1.8  |                          | mA   |

| Logic inputs          | and outputs                                        |                                                                                  |                             |      |                          |      |

| C <sub>ULPIIN</sub>   | ULPI port I/O capacitance                          |                                                                                  |                             | 2.4  | 3.5                      | pF   |

| V <sub>OH</sub>       | High level output voltage<br>(ULPI bus)            | I <sub>OH</sub> = -2 mA                                                          | V <sub>DVIO</sub><br>-0.15  |      |                          | v    |

| V <sub>OL</sub>       | Low level output voltage<br>(ULPI bus)             | I <sub>OL</sub> = +2 mA                                                          |                             |      | 0.15                     | v    |

| I <sub>OZH_PSWn</sub> | High level output leakage<br>(PSWn)                | V <sub>OH_PSWn</sub> = 3.3 V power<br>switch disabled                            |                             |      | 1.0                      | μA   |

| $V_{OL\_PSWn}$        | Low level output voltage<br>(PSWn)                 | I <sub>OL</sub> = +2 mA power switch enabled                                     |                             |      | 0.15                     | v    |

| V <sub>IH</sub>       | High level input voltage<br>(ULPI port and RESETn) |                                                                                  | 0.65 x<br>V <sub>DVIO</sub> |      |                          | v    |

| V <sub>IL</sub>       | Low level input voltage<br>(ULPI port and RESETn)  |                                                                                  |                             |      | 0.35 x V <sub>DVIO</sub> | v    |

| IIH                   | High level input leakage current                   | $V_{IH} = V_{DVIO} - 0.2 V$                                                      |                             |      | ±1.0                     | μA   |

## Table 6. Electrical characteristics

10/44

| Symbol                   | Parameter                                           | Test conditions                                   | Min.                        | Тур. | Max.                     | Unit |

|--------------------------|-----------------------------------------------------|---------------------------------------------------|-----------------------------|------|--------------------------|------|

| Ι <sub>ΙL</sub>          | Low level input leakage cur-<br>rent                | V <sub>IL</sub> = 0.2 V                           |                             |      | ±1.0                     | μA   |

| V <sub>PDH</sub>         | High level input voltage<br>(CSn/PWRDN pin)         | V <sub>BAT</sub> = 3.0 V to 4.5 V                 | 1.4                         |      |                          | v    |

| V <sub>PDL</sub>         | Low level input voltage<br>(CSn/PWRDN pin)          | V <sub>BAT</sub> = 3.0 V to 4.5 V                 |                             |      | 0.4                      | v    |

| I <sub>PDH</sub>         | High level input leakage<br>current (CSn/PWRDN pin) | V <sub>PD</sub> = 1.4 V, V <sub>BAT</sub> = 4.5 V |                             |      | ±1.0                     | μA   |

| I <sub>PDL</sub>         | Low level input leakage current (CSn/PWRDN pin)     | V <sub>PD</sub> = 0.4 V, V <sub>BAT</sub> = 4.5 V |                             |      | ±1.0                     | μA   |

| V <sub>FAULTH</sub>      | High level input voltage<br>(VB_REF_FAULT pin)      | Overcurrent_PD bit is set                         | 0.65 x V <sub>3V3</sub>     |      |                          | V    |

| V <sub>FAULTL</sub>      | Low level input voltage<br>(VB_REF_FAULT pin)       | Overcurrent_PD bit is set                         |                             |      | 0.15 x V <sub>3V3</sub>  | V    |

| $R_{IN\_VB\_REF}$        | VB_REF_FAULT pin input<br>resistance                |                                                   | 112                         | 148  | 168                      | kΩ   |

| V <sub>XI_HYST_EXT</sub> | External clock input<br>hysteresis                  | XO = '0' at reset                                 |                             | 500  |                          | mV   |

| V <sub>XIH</sub>         | High level input voltage<br>(XI pin)                | XO = '0' at reset                                 | 0.65 x<br>V <sub>DVIO</sub> |      |                          | v    |

| $V_{XIL}$                | Low level input voltage<br>(XI pin)                 | XO = '0' at reset                                 |                             |      | 0.15 x V <sub>DVIO</sub> | V    |

| VBUS                     |                                                     |                                                   |                             |      |                          |      |

| V <sub>BUS_LKG</sub>     | V <sub>BUS</sub> leakage voltage                    | No load                                           |                             |      | 200                      | mV   |

| R <sub>VBUS</sub>        | V <sub>BUS</sub> input impedance                    |                                                   | 40                          |      | 100                      | kΩ   |

| $V_{BUS_VLD}$            | V <sub>BUS</sub> valid comparator<br>threshold      | 1 k $\Omega$ series resistors                     | 4.4                         | 4.75 |                          | v    |

| N/                       | Session valid comparator                            | Low to high transition                            | 0.8                         | 1.45 | 2.0                      | V    |

| $V_{SESS_VLD}$           | threshold for both A and B device                   | High to low transition                            |                             | 1.25 |                          | V    |

| V <sub>SESS_END</sub>    | Session end comparator threshold                    |                                                   | 0.2                         |      | 0.8                      | v    |

| R <sub>VBUS_PU</sub>     | V <sub>BUS</sub> charge pull-up<br>resistance       |                                                   | 650                         | 950  | 1150                     | Ω    |

| R <sub>VBUS_PD</sub>     | V <sub>BUS</sub> discharge pull-down resistance     |                                                   | 800                         | 1250 | 1500                     | Ω    |

Table 6.

Electrical characteristics (continued)

| Table 6. | Electrical characteristics ( | continued | ) |

|----------|------------------------------|-----------|---|

|          |                              |           | / |

| Symbol                  | Parameter                                                      | Test conditions                              | Min.                        | Тур. | Max.                     | Unit |

|-------------------------|----------------------------------------------------------------|----------------------------------------------|-----------------------------|------|--------------------------|------|

| Overcurrent             | detector                                                       |                                              | l .                         | 1    | L                        |      |

| V <sub>OC</sub>         | Overcurrent trip threshold<br>VB_REF_FAULT – VBUS              | V <sub>OC</sub> = VB_REF_FAULT –<br>VBUS     | 20                          | 45   | 95                       | mV   |

| ID                      |                                                                |                                              |                             | •    |                          | •    |

| I <sub>ID_PU</sub>      | ID pin pull-up current                                         | $V_{ID} = 0 V$                               |                             | 70   |                          | μA   |

| R <sub>ID_GND</sub>     | ID line short resistance to detect ID GND state                |                                              |                             |      | 1                        | kΩ   |

| R <sub>ID_FLOAT</sub>   | ID line short resistance to detect ID FLOAT state              |                                              | 100                         |      |                          | kΩ   |

| UART mode               | (2.7 V ± 5%)                                                   |                                              |                             |      |                          |      |

| V <sub>OH_UART</sub>    | High level output voltage (D1, D3)                             | I <sub>OH</sub> = -2 mA                      | V <sub>DVIO</sub><br>- 0.15 |      |                          | V    |

| V <sub>OL_UART</sub>    | Low level output voltage<br>(D1, D3)                           | I <sub>OL</sub> = +2 mA                      |                             |      | 0.15                     | v    |

| V <sub>IH_UART_D0</sub> | High level input voltage<br>(D0)                               |                                              | 0.65 x<br>V <sub>DVIO</sub> |      |                          | v    |

| V <sub>IL_UART_D0</sub> | Low level input voltage (D0)                                   |                                              |                             |      | 0.35 x V <sub>DVIO</sub> | V    |

| V <sub>OH_DFMS</sub>    | High level output voltage (DP)                                 | I <sub>OH</sub> = -2 mA                      | 2.16                        |      | 2.85                     | v    |

| V <sub>OL_DFMS</sub>    | Low level output voltage<br>(DP)                               | $I_{OL}$ = +2 mA,<br>Pull-up = 10 k $\Omega$ | -0.10                       |      | 0.37                     | v    |

| V <sub>IH_DTMS</sub>    | High level input voltage<br>(DM)                               |                                              | 2.0                         |      | 3.0                      | v    |

| V <sub>IL_DTMS</sub>    | Low level input voltage<br>(DM)                                |                                              | -0.3                        |      | 0.81                     | V    |

| Full-speed/lo           | w-speed driver                                                 |                                              | •                           | 1    |                          |      |

| Z <sub>DRV</sub>        | Output impedance (acting<br>also as high-speed<br>termination) |                                              | 40.5                        |      | 49.5                     | Ω    |

| V <sub>OH_DRV</sub>     | High level output voltage                                      | R <sub>LH</sub> = 14.25 kΩ                   | 2.8                         |      | 3.6                      | V    |

| V <sub>OL_DRV</sub>     | Low level output voltage                                       | R <sub>LL</sub> = 1.425 kΩ                   | 0.0                         |      | 0.3                      | V    |

| V <sub>CRS</sub>        | Driver crossover voltage                                       | $C_{LOAD} = 50$ to 600 pF <sup>(2)</sup>     | 1.3                         | 1.67 | 2.0                      | V    |

| High-speed d            | river                                                          |                                              | •                           |      | •                        |      |

| V <sub>HSOI</sub>       | HS idle level                                                  |                                              | -10                         |      | 10                       | mV   |

| V <sub>HSDPJ</sub>      | HS data DP J state level                                       | (2)                                          | 380                         |      | 440                      | mV   |

| V <sub>HSDK</sub>       | HS data DP K state level                                       |                                              | -10                         |      | 10                       | mV   |

| Table 6.            | <b>Electrical characteristics</b>                                    | (continued)                           |       |      |      |      |

|---------------------|----------------------------------------------------------------------|---------------------------------------|-------|------|------|------|

| Symbol              | Parameter                                                            | Test conditions                       | Min.  | Тур. | Max. | Unit |

| V <sub>HSDNJ</sub>  | HS data DN J state level                                             | (2)                                   | 380   |      | 440  | mV   |

| V <sub>HSDNK</sub>  | HS data DN K state level                                             |                                       | -10   |      | 10   | mV   |

| V <sub>CHIRPJ</sub> | Chirp J level (differential voltage)                                 | (2)                                   | 700   |      | 1100 | mV   |

| V <sub>CHIRPK</sub> | Chirp K level (differential voltage                                  |                                       | -900  |      | -500 | mV   |

| Full-speed/L        | ow-speed receivers                                                   |                                       |       |      |      | •    |

| $V_{DI}$            | Diff. receiver input sensitivity (V <sub>DP</sub> -V <sub>DM</sub> ) | V <sub>CM</sub> = 0.8 to 2.5 V        | 200   |      |      | mV   |

| V                   | SE receivers switching                                               | Low to high transition                | 0.8   | 1.6  | 2.0  | V    |

| $V_{SE_{TH}}$       | threshold                                                            | High to low transition                | 0.8   | 1.1  | 2.0  | V    |

| R <sub>INP</sub>    | Input resistance                                                     | PU/PD resistors deactivated           | 300   |      |      | kΩ   |

| C <sub>IN</sub>     | Input capacitance                                                    | (2)                                   |       |      | 5    | pF   |

| $\Delta_{\rm CIN}$  | Difference in capacitance between DP and DM input                    |                                       |       |      | 10   | %    |

| V <sub>DT_LKG</sub> | Data line leakage voltage                                            | $R_{PU\_EXT} = 300 \text{ k}\Omega$   |       |      | 342  | mV   |

| High-speed          | receiver                                                             |                                       |       |      |      |      |

| V <sub>HSSQ</sub>   | HS squelch detector threshold                                        |                                       | 100   |      | 150  | mV   |

| V <sub>HSDSC</sub>  | HS disconnect detection threshold                                    |                                       | 525   |      | 625  | mV   |

| V <sub>HSCM</sub>   | HS data signaling common mode volt. range                            | (2)                                   | -50   |      | 500  | mV   |

| V <sub>HSTERM</sub> | Termination voltage in HS                                            | (2)                                   | -10   |      | 10   | mV   |

| Data pull-up        | /pull-down resistors                                                 |                                       |       |      |      |      |

| R <sub>PU</sub>     | Data line pull-up resistance<br>(DP, DM)                             |                                       | 1.425 |      |      | kΩ   |

| V <sub>IHZ</sub>    | FS idle high level voltage                                           |                                       | 2.7   |      |      | V    |

| R <sub>PD</sub>     | Data line pull-down<br>resistance (DP, DM)                           |                                       | 14.25 |      | 24.8 | kΩ   |

| Voltage regu        | ulator                                                               |                                       |       | I    |      |      |

| 3V3V                | 3.3 V internal power supply voltage                                  | V <sub>BAT</sub> = 3.6 V, Active mode | 3.26  | 3.4  | 3.54 | v    |

| 1V2V                | 1.2 V internal power supply voltage                                  | V <sub>BAT</sub> = 3.6 V, Active mode | 1.187 | 1.25 | 1.31 | v    |

#### Table 6. Electrical characteristics (continued)

1. Characteristics measured over recommended operating conditions unless otherwise noted. All typical values are referred to  $T_A = 25$  °C,  $V_{DVIO} = 1.8$  V,  $V_{BAT} = 3.6$  V,  $R_{REF} = 12$  kΩ;  $C_T = 4.7$  µF.

2. Guaranteed by design.

| Symbol                  | Parameter                                 | Test conditions <sup>(1)</sup>                 | Min.    | Тур. | Max.    | Unit |

|-------------------------|-------------------------------------------|------------------------------------------------|---------|------|---------|------|

| Reset                   |                                           |                                                |         |      |         |      |

| t <sub>RESETEXT</sub>   | Width of reset pulse on RESETn pin        |                                                | 10      |      |         | μs   |

| UART mode               |                                           |                                                |         |      |         |      |

| t <sub>RISE</sub>       | Switching time (max. low to min.<br>high) | C <sub>LOAD</sub> = 185 pF                     |         |      | 215     | ns   |

| t <sub>FALL</sub>       | Switching time (min. high to max.<br>low) | C <sub>LOAD</sub> = 185 pF                     |         |      | 215     | ns   |

| t <sub>PD_RX</sub>      | Delay time (50% DM to 50% D1)             | C <sub>L</sub> = 10 pF                         |         |      | 60      | ns   |

| t <sub>PD_TX</sub>      | Delay time (50% D0 to 50% DP)             |                                                |         |      | 60      | ns   |

| t <sub>UARTON2V7</sub>  | Turn-on time for TXD line (2V7)           | UART_2V7 = 1 measured<br>from DIR assertion    |         | 2    | 2.5     | ms   |

| t <sub>UARTOFF2V7</sub> | Turn-off time for TXD line (2V7)          | UART_2V7 = 1 measured<br>from STP assertion    |         |      | 1       | μs   |

| t <sub>UARTON</sub>     | Turn-on time for TXD line                 | UART_2V7 = 0 measured<br>from DIR assertion    |         |      | 60      | ns   |

| t <sub>UARTOFF</sub>    | Turn-off time for TXD line                | UART_2V7 = 0 measured<br>from DIR de-assertion |         |      | 60      | ns   |

| Low-speed o             | driver                                    | ·                                              |         |      |         |      |

| t <sub>LR</sub>         | Data signal rise time                     | C <sub>LOAD</sub> = 600 pF                     | 75      | 100  | 300     | ns   |

| t <sub>LF</sub>         | Data signal fall time                     | C <sub>LOAD</sub> = 600 pF                     | 75      | 100  | 300     | ns   |

| $RFM_{LS}$              | Rise and fall time matching               |                                                | -20     |      | 20      | %    |

| DR <sub>LS</sub>        | Low-speed data rate                       |                                                | 1.49925 |      | 1.50075 | Mb/s |

| t <sub>DDJ1</sub>       | Data jitter to next transition            | Includes freq. tolerances                      | -25     |      | 25      | ns   |

| t <sub>DDJ2</sub>       | Data jitter for paired transitions        | Includes freq. tolerances                      | -14     |      | 14      | ns   |

| t <sub>LEOPT</sub>      | SE0 interval of EOP                       |                                                | 1250    |      | 1500    | ns   |

| Full-speed d            | river                                     |                                                |         |      |         |      |

| t <sub>FR</sub>         | Data signal rise time                     | C <sub>LOAD</sub> = 50 pF                      | 4       |      | 20      | ns   |

| t <sub>FF</sub>         | Data signal fall time                     | C <sub>LOAD</sub> = 50 pF                      | 4       |      | 20      | ns   |

| RFM <sub>FS</sub>       | Rise and fall time matching               |                                                | -10     |      | +10     | %    |

| DR <sub>HS</sub>        | Full-speed data rate                      |                                                | 11.994  |      | 12.006  | Mb/s |

| t <sub>DJ1</sub>        | Data jitter to next transition            | Includes freq. tolerances                      | -3.5    |      | 3.5     | ns   |

| t <sub>DJ2</sub>        | Data jitter for paired transitions        | Includes freq. tolerances                      | -4      |      | 4       | ns   |

| t <sub>FEOPT</sub>      | SE0 interval of EOP                       |                                                | 160     |      | 175     | ns   |

| Clock generation        | ation constants                           |                                                |         |      |         | •    |

| t <sub>PLL</sub>        | PLL lock time                             | (2)                                            |         |      | 200     | μs   |

| t <sub>DLL</sub>        | DLL lock time                             | (2)                                            |         |      | 280     | μs   |

## Table 7.Switching characteristics

14/44

| Symbol                 | Parameter                                                                        | Test conditions                                                                        | Min.   | Тур.                           | Max.            | Unit       |

|------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------|--------------------------------|-----------------|------------|

| High-speed             | driver                                                                           |                                                                                        | 1      |                                | 1               | 1          |

| t <sub>HSR</sub>       | Data rise time                                                                   |                                                                                        | 500    |                                |                 | ps         |

| t <sub>HSF</sub>       | Data fall time                                                                   |                                                                                        | 500    |                                |                 | ps         |

|                        | Waveform requirements including jitter                                           |                                                                                        |        | ed by eye<br>( <i>Figure 3</i> | e pattern<br>3) |            |

| DR <sub>HS</sub>       | High-speed data rate                                                             |                                                                                        | 479.76 |                                | 480.24          | Mb/s       |

| ULPI interfa           | ce                                                                               | ·                                                                                      |        |                                |                 | ·          |

| CLOCK (me              | asured on CLK pin)                                                               |                                                                                        |        |                                |                 |            |

| f <sub>START_U</sub>   | Frequency (first transition)                                                     | (2)                                                                                    | 54     | 60                             | 66              | MHz        |

| f <sub>STEADY_U</sub>  | Frequency (steady-state)                                                         |                                                                                        | 59.97  | 60                             | 60.03           | MHz        |

| D <sub>START_U</sub>   | Duty cycle (first transition)                                                    |                                                                                        | 40     | 50                             | 60              | %          |

| D <sub>STEADY_U</sub>  | Duty cycle (steady-state)                                                        | (2)                                                                                    | 45     | 50                             | 55              | %          |

| T <sub>STEADY_U</sub>  | Time to reach steady-state<br>frequency and duty cycle after first<br>transition | (2)                                                                                    |        |                                | 1.4             | ms         |

| T <sub>JITTER_U</sub>  | Jitter                                                                           |                                                                                        |        | 400                            |                 | ps         |

| t <sub>SCLK60OUT</sub> | Clock startup time                                                               | Measured from assertion<br>of STP during suspend, or<br>after release of RESETn<br>pin | 250    |                                | 900             | μs         |

| ULPI contro            | l signals (SDR mode) <sup>(2)</sup>                                              | -                                                                                      | •      |                                | •               |            |

| T <sub>SC_U</sub>      | Control in setup time                                                            |                                                                                        | 6.0    |                                |                 | ns         |

| T <sub>HC_U</sub>      | Control in hold time                                                             | C <sub>LOAD</sub> = 15 pF<br>V <sub>DVIO</sub> = 1.65 - 3.6 V                          | 0.0    |                                |                 | ns         |

| T <sub>DC_U</sub>      | Control output delay                                                             |                                                                                        |        |                                | 9.0             | ns         |

| ULPI data s            | ignals (SDR mode) <sup>(2)</sup>                                                 |                                                                                        |        | •                              |                 | . <u>.</u> |

| T <sub>SD_U</sub>      | Data in setup time                                                               |                                                                                        | 6.0    |                                |                 | ns         |

| T <sub>HD_U</sub>      | Data in hold time                                                                | C <sub>LOAD</sub> = 15 pF<br>V <sub>DVIO</sub> = 1.65 - 3.6 V                          | 3.0    |                                |                 | ns         |

| T <sub>DD_U</sub>      | Data output delay                                                                |                                                                                        |        |                                | 9.0             | ns         |

### Table 7. Switching characteristics (continued)

1. Over recommended operating conditions unless otherwise noted. All the typical values are referred to  $T_A = 25 \text{ °C}$ ,  $V_{DVIO} = 1.8 \text{ V}$ ,  $V_{BAT} = 3.6 \text{ V}$ ,  $C_T = 4.7 \mu\text{F}$ .

2. Guaranteed by design.

| Table 8. | <b>High-speed</b> | driver e | eve | pattern |

|----------|-------------------|----------|-----|---------|

|          | ingii opood       | a        |     | pattorn |

|                              | -                               |                                   |         |         |         |         |         |         |

|------------------------------|---------------------------------|-----------------------------------|---------|---------|---------|---------|---------|---------|

| Parameter                    | Level 1                         | Level 2                           | Point 1 | Point 2 | Point 3 | Point 4 | Point 5 | Point 6 |

| Voltage level<br>(DP – DM)   | 525 mV <sup>(1)</sup><br>475 mV | –525 mV <sup>(1)</sup><br>–475 mV | 0 V     | 0 V     | 300 mV  | 300 mV  | –300 mV | –300 mV |

| Time<br>(% of unit interval) |                                 |                                   | 5%      | 95%     | 35%     | 65%     | 35%     | 65%     |

1. This value is valid for unit intervals following a transition. For all other intervals the other value is valid.

# 5 Timing diagram

### Figure 4. Rise and fall time

### Figure 5. Simplified block diagram

# 6 Block description

The STULPI01 integrates a comparator for the VBUS, ID line detector, differential HS data driver, differential and single-ended receivers, low dropout voltage regulators, and control logic.

The STULPI01 provides a complete solution for the connection of a digital USB host/device/OTG controller to a USB bus.

# 6.1 Oscillator and PLL

An external clock (digital square wave  $V_{DVIO}$  referred) driven into XI must be used (version STULPI01A or STULPI01B).

The PLL internally produces all frequencies needed for operation:

- 60-MHz clock for the UTMI core and ULPI interface controller

- 1.5 MHz for low-speed USB data

- 12 MHz for full-speed USB data

- 480 MHz for high-speed USB data

- Other internal frequencies for data conversion and data recovery.

# 6.2 Voltage reference

This block provides the precise reference voltage needed by the internal circuit. It requires a 12 k $\Omega$  +/- 1% resistor connected to the R<sub>BFF</sub> pin.

# 6.3 Power-on reset (POR)

The power-on reset circuit generates a reset pulse upon power-up which is used to initialize the entire digital logic. Power-on reset senses the  $V_{3V3V}$  and  $V_{1V2V}$  voltage. During the power-on reset pulse, the ULPI pins are in a high impedance state with pull-down/pull-up resistors disabled.

# 6.4 UTMI + core

This is the digital heart of the chip and performs the bit-stuffing, NRZI decoding and serial to parallel conversion during receive and the reverse operation during transmit for HS and FS/LS.

## 6.5 ULPI wrapper

This implements the ULPI related protocol and conversion from UTMI+ to ULPI interface. This block also implements the interrupt logic and complete ULPI register set.

18/44

# 6.6 External charge pump

It is possible to use an external charge pump or power switch controlled by the PSWn pin (active low open drain). This functionality is controlled by DrvVbus and DrvVbusExternal ULPI OTG control register bits.

# 6.7 V<sub>BUS</sub> comparators and V<sub>BUS</sub> overcurrent (OC) detector

These comparators monitor the V<sub>BUS</sub> voltage.

$V_{BUS}$  valid status signals that the voltage is above the  $V_{BUS\_VLD}$  level (4.4 V). Session valid status signals that the  $V_{BUS}$  voltage is above the  $V_{SESS\_VLD}$  level (0.8 to 2.0 V). Session end detector signals that  $V_{BUS}$  voltage is below  $V_{SESS\_END}$  level.

The STULPI01 also implements an embedded  $V_{BUS}$  overcurrent detector which compares  $V_{BUS}$  voltage to the external analog 5 V reference signal applied to the VB\_REF\_FAULT pin.

# 6.8 VB\_REF\_FAULT pin

V<sub>BUS</sub> overcurrent conditions can be monitored by either an internal or external OC detector. The internal OC detector is enabled when the overcurrent\_PD bit in the power control register (vendor-specific area) is set to 0b and Use External VBUS Indicator is set to 1b. In this mode, the VB\_REF\_FAULT pin functions as the input of the analog reference for internal overcurrent detector.

If the external charge pump is already equipped with an overcurrent detector, its output can be also monitored through the VB\_REF\_FAULT pin, but the overcurrent\_PD bit must be set to 1b. In this mode, VB\_REF\_FAULT functions as the standard digital input pin with 5 V tolerance. Functionality of the VB\_REF\_FAULT pin can be seen in more detail in *Figure 6*.

Note: After reset, the overcurrent\_PD bit is 1b, the internal overcurrent detector is disabled.

#### Figure 6. VB\_REF\_FAULT pin functionality

Table 9. VB\_REF\_FAULT configuration bit settings

| RX CMD VBUS valid        | Use External<br>Vbus Indicator | Overcurrent_PD | Indicator Pass-Thru | Indicator<br>complement |

|--------------------------|--------------------------------|----------------|---------------------|-------------------------|

| VBUSVLD                  | 0                              | 1              | Х                   | Х                       |

| VBOC                     | 1                              | 0              | 1                   | Х                       |

| VBOC and VBUSVLD         | 1                              | 0              | 0                   | Х                       |

| neg (FAULT)              | 1                              | 1              | 1                   | 0                       |

| FAULT                    | 1                              | 1              | 1                   | 1                       |

| VBUSVLD and FAULT        | 1                              | 1              | 0                   | 1                       |

| VBUS_VLD and neg (FAULT) | 1                              | 1              | 0                   | 0                       |

# 6.9 Voltage regulator

The dual output ultra low dropout voltage regulator provides the power supply for analog and digital internal circuits. An external capacitor on both the 3V3V and 1V2V pins is needed for proper operation.

# 6.10 ID detector

This block provides the sensing of the status of the ID line. It is capable of detecting whether the pin is floating or tied to the ground.

# 6.11 USB 2.0 PHY

The USB 2.0 PHY block provides a complete physical layer transceiver for low-speed, fullspeed, and high-speed USB operating modes. The analog part of this block deals with impedance adaptation, controlled voltage swing, and Common mode voltage generation

and sensing. The digital part consists of a serializer and deserializer, transforming serial bit stream to 8-bit parallel port, and finite state machine implementing the PHY protocol layer, bit stuffing, unstuffing, etc.

# 6.12 Power saving features

To reduce power consumption, the STULPI01 implements 2 Low-power modes of operation.

- 1. Low-power mode, which is defined in the ULPI specification.

- 2. Power-down mode to save more power in case USB function is not needed.

More information on these modes can be found in the following paragraphs.

# 6.13 Modes of operation

### 6.13.1 ULPI synchronous mode

The STULPI01 transceiver supports SDR mode operation (12-pin interface). The selection of SDR mode is performed during the startup reset procedure.

### 6.13.2 6-pin FS/LS serial mode

This mode is entered by writing to the corresponding bit in the Interface Control register.

### 6.13.3 3-pin FS/LS serial mode

This mode is entered by writing to the corresponding bit in the Interface Control register.

Doc ID 14817 Rev 4

# 6.14 Car Kit (UART) mode

This mode is entered by writing to the Car Kit mode bit in the interface control register. The STULPI01 does not implement all features of Car Kit mode, only the UART functionality is preserved.

| Table 10. | Car kit | signals | mapping |

|-----------|---------|---------|---------|

|-----------|---------|---------|---------|

| Default car kit signals mapping (UART_DIR = 0) |                     |             |  |  |  |  |  |

|------------------------------------------------|---------------------|-------------|--|--|--|--|--|

| Signal                                         | ULPI lines          | USB lines   |  |  |  |  |  |

| TXD                                            | DATA[0] (input) ->  | DM (output) |  |  |  |  |  |

| RXD                                            | DATA[1] (output) <- | DP (input)  |  |  |  |  |  |

| Reserved                                       | DATA[2] (input)     |             |  |  |  |  |  |

| INT                                            | DATA[3] (output)    |             |  |  |  |  |  |

| Car kit signals mapping                        | (UART_DIR = 1)      |             |  |  |  |  |  |

| Signal                                         | ULPI lines          | USB lines   |  |  |  |  |  |

| TXD                                            | DATA[0] (input) ->  | DP (output) |  |  |  |  |  |

| RXD                                            | DATA[1] (output) <- | DM (input)  |  |  |  |  |  |

| Reserved                                       | DATA[2] (input)     |             |  |  |  |  |  |

| INT                                            | DATA[3] (output)    |             |  |  |  |  |  |

TXD or RXD paths are activated only when the corresponding bits TXD\_EN/RXD\_EN in car kit control register bits (*Table 23*) are set.

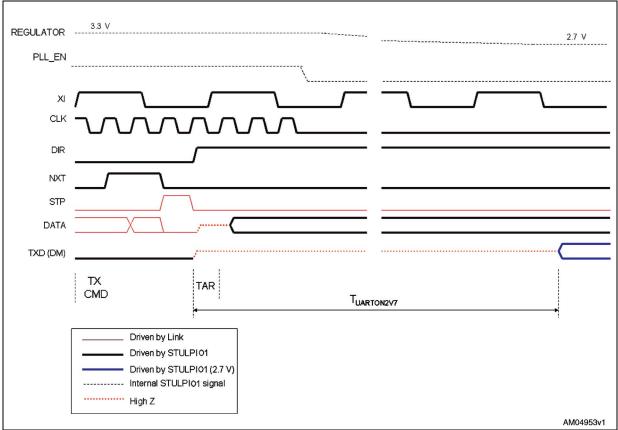

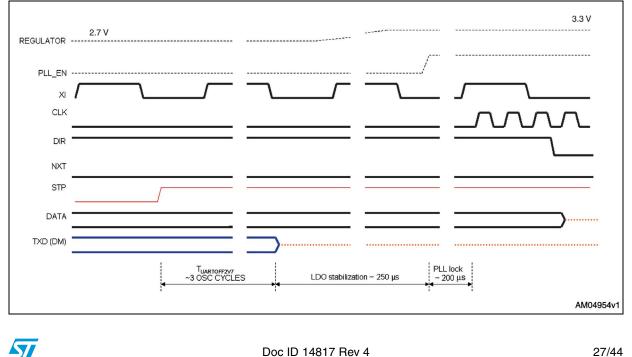

The UART\_2V7 bit controls the voltage level of UART signaling. If 2V7 volt signaling is used, after the UART mode is entered, PLL is disabled and the voltage on the regulator output starts to decrease to 2.7 V. After a time marked as  $t_{UARTON2V7}$ , the TXD output on the USB bus is enabled.

When leaving Car Kit mode, TXD is disabled immediately when the STP pin is asserted. The time required to exit Car Kit mode is equivalent to the time needed for PLL startup.

When 3.3 volt UART signaling is selected, the TXD line is enabled immediately after entering Car Kit mode, and disabled after exiting this mode.

Note: When Car Kit mode is used with 2V7 signaling, the PLL and output clock are always stopped regardless of the setting of the ClockSuspendM bit.

# 6.15 Low-power mode

The STULPI01 enters Low-power mode when the SuspendM bit in the interface control register is set to 0b. Most of the references are turned off, PLL and clock are turned off, but the full wake-up capability as defined in the ULPI specification is still maintained.

When in Low-power mode, the PHY drives D3-D0 with the signals listed in *Table 11*. Line state is driven combinatorially from the SE receivers. The INT signal is asserted whenever any unmasked interrupt occurs. The PHY latches interrupt events directly from analog circuitry because the clock is powered down.

#### Table 11. Low-power mode

| Signal        | Map to | Dir | Description                                                                           |  |  |  |  |

|---------------|--------|-----|---------------------------------------------------------------------------------------|--|--|--|--|

| Linestate (0) | D0     | out | Driven combinatorially from SE receivers                                              |  |  |  |  |

| Linestate (1) | D1     | out | Driven combinatorially from SE receivers                                              |  |  |  |  |

| Reserved      | D2     | out | Reserved                                                                              |  |  |  |  |

| INT           | D3     | out | Active high interrupt indication. Asserted whenever<br>any unmasked interrupt occurs. |  |  |  |  |

Low-power mode is exited by asserting the STP pin high. PLL is started immediately, and when the clock becomes stable, it is passed on the output of the CLK pin. Then, after a minimum of 5 clock cycles, DIR is deasserted and Low-power mode is exited. The SuspendM bit is reset to 1b.

*Note:* The STP signal must be kept high until the DIR is deasserted, otherwise Low-power mode is not exited.

# 6.16 Power-down mode

Power-down mode is entered by asserting the CSn/PWRDN pin high. Internal voltage regulators are disabled, and the device has minimum possible power consumption. The STULPI01 has no wake-up capability or USB functionality during Power-down mode. This mode can be exited by deasserting the CSn/PWRDN pin. Voltage regulators are turned on and the internal power-on reset circuit resets the chip to initial state. ULPI interface pins are in high impedance state during Power-down mode.

# 6.17 VIO OFF mode

If  $V_{\text{DVIO}}$  is below the minimum value, VIO OFF mode is entered. The behavior of the device in VIO OFF mode is the same as in Power-down mode.

# 6.18 Startup procedure

### 6.18.1 ULPI device detection

The link detects ULPI device presence by sampling the DIR signal at the reset time (*Figure 8*). The NXT signal is '0' after reset to signal an 8-bit device to the link controller. CLK is '1' to signal a DDR capable device.

### 6.18.2 SDR mode selection

The STULPI01 samples the D0 line on the first rising edge of the output clock on the CLK pin. When the sampled value is '0', the STULPI01 remains in SDR mode.

SDR mode can be selected again only after hardware reset. During software reset mode, selection is not performed.

Doc ID 14817 Rev 4

Note: IMPORTANT: The controller must not drive the DATA lines to a value other than 0x00 or 0x01 during the first rising edge of ULPI CLK, otherwise the behavior of the device may be undefined.

### 6.18.3 External clock detection

The square wave clock can be applied to the oscillator input. The input square wave clock amplitude is referenced to  $V_{\text{DVIO}}$ .

The XO pin can be left floating or grounded.

#### 6.18.4 Reset behavior

A typical startup sequence is shown in *Figure 12*.

The STULPI01 contains an internal power-on reset generator which senses the V3V3V and V1V2V voltage. Assertion of RESETn is not necessary for proper initialization. However, if required, this pin can be also used. The internal reset signal is the combination of the signal from the RESETn pin and the signal from the internal power-on reset circuit.

When RESETn is asserted, all internal registers are reset to their default values, the output DIR signal is driven to '1', and data lines are pulled low by weak pull-downs.

During reset, the STP pin can be driven low, high, or can be left floating. It is pulled up by internal pull-up and the ULPI interface enters a holding state.

During the reset state, the NXT signal is driven low and the CLK is driven high.

When the PLL is stabilized, the clock on the CLK pin is enabled, and DIR is deasserted.

Note: The minimum duration of the external reset signal is TRESETEXT. (See Table 7).

When internal POR reset is asserted, the reset procedure is equivalent to the RESETn signal, with the only exception being that the ULPI lines are in high impedance state. All pull-downs and pull-ups on the ULPI signals are also disabled.

### 6.18.5 Interface protection

The STULPI01 activates weak pull-downs on data lines and pull-up on the STP during reset and holding state. These are to provide interface protection during startup and anytime the link is not able to drive the ULPI lines properly.

The holding state is entered when the controller drives the STP for more than 1 clock cycle. Any command on the ULPI bus is ignored in this state. For more information see ULPI specification 1.1, section 3.12 (Safeguarding PHY input signals).

Interface protection can be switched off at any time after startup in order to save power, by writing the Interface Protect Disable bit in the Interface Control register to 1b.

#### 6.18.6 Software reset

The STULPI01 supports software reset by writing the RESET bit in the function control register to 1b.

During software reset, DIR is asserted and the pull-down resistors on data lines are enabled, but the ULPI registers remain unaffected. Software reset initializes UTMI core logic only. Also, during software reset, external clock detection, SDR mode selection is not performed, and the clock is not turned off (PLL is not restarted).

24/44

#### STULPI01A, STULPI01B

*Note:* Software reset is not required in the startup procedure for the STULPI. The chip is ready for operation after the hardware reset procedure.

### 6.18.7 High-speed mode entry

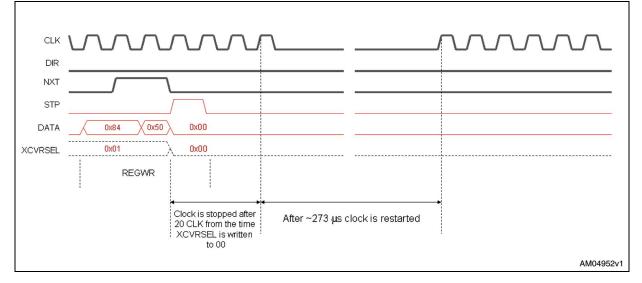

In High-speed mode, the internal 480-MHz clock is generated by the DLL, which must be calibrated any time the device enters High-speed mode by writing '00' to the XcvrSel field in the Function Control register. During the DLL calibration, it is not possible to accept any commands, therefore, to avoid any communication problems with the controller, the clock on the ULPI interface is stopped. See *Figure 10* for more information.

#### Figure 8. Startup sequence

#### Figure 9. RESETn behavior

#### Figure 10. High-speed mode entry

### Figure 11. UART mode entry (2.7 V)

## Figure 12. UART mode exit (2.7 V)

Doc ID 14817 Rev 4

# 7 State transitions

#### Table 12. USB state transitions

|                                                         |            | Regis      | ter setti | ings       |            |           | Resis     | tor se    | ttings    | ;         |

|---------------------------------------------------------|------------|------------|-----------|------------|------------|-----------|-----------|-----------|-----------|-----------|

| Signaling mode                                          | XcvrSelect | TermSelect | OpMode    | DpPulldown | DmPulldown | rpu_dp_en | rpu_dm_en | rpd_dp_en | rpd_dm_en | hsterm_en |

| General settings                                        |            |            |           |            |            |           |           |           |           |           |

| 3-state drivers                                         | XXb        | Xb         | 01b       | 0b         | 0b         | 0b        | 0b        | 0b        | 0b        | 0b        |

| 3-state drivers with pull-down enabled                  | XXb        | Xb         | 01b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Power-up or V <sub>bus</sub> < V <sub>th(SESSEND)</sub> | 01b        | 0b         | 00b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host settings                                           |            |            |           |            |            |           |           |           |           |           |

| Host chirp                                              | 00b        | 0b         | 10b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 1b        |

| Host high-speed                                         | 00b        | 0b         | 00b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 1b        |

| Host full-speed                                         | X1b        | 1b         | 00b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host HS/FS suspend                                      | 01b        | 1b         | 00b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host HS/FS resume                                       | 01b        | 1b         | 10b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host low-speed                                          | 10b        | 1b         | 00b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host low-speed suspend                                  | 10b        | 1b         | 00b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host low-speed resume                                   | 10b        | 1b         | 10b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host test_J/Test_K                                      | 00b        | 0b         | 10b       | 1b         | 1b         | 0b        | 0b        | 1b        | 1b        | 1b        |

| Peripheral settings                                     |            |            |           |            |            |           |           |           |           |           |

| Peripheral chirp                                        | 00b        | 1b         | 10b       | 0b         | 0b         | 1b        | 0b        | 0b        | 0b        | 0b        |

| Peripheral high-speed                                   | 00b        | 0b         | 00b       | 0b         | 0b         | 0b        | 0b        | 0b        | 0b        | 1b        |

| Peripheral full-speed                                   | 01b        | 1b         | 00b       | 0b         | 0b         | 1b        | 0b        | 0b        | 0b        | 0b        |

| Peripheral HS/FS suspend                                | 01b        | 1b         | 00b       | 0b         | 0b         | 1b        | 0b        | 0b        | 0b        | 0b        |

| Peripheral HS/FS resume                                 | 01b        | 1b         | 10b       | 0b         | 0b         | 1b        | 0b        | 0b        | 0b        | 0b        |

| Peripheral low-speed                                    | 10b        | 1b         | 00b       | 0b         | 0b         | 0b        | 1b        | 0b        | 0b        | 0b        |

| Peripheral low-speed suspend                            | 10b        | 1b         | 00b       | 0b         | 0b         | 0b        | 1b        | 0b        | 0b        | 0b        |

| Peripheral low-speed resume                             | 10b        | 1b         | 10b       | 0b         | 0b         | 0b        | 1b        | 0b        | 0b        | 0b        |

| Peripheral test_J/Test_K                                | 00b        | 0b         | 10b       | 0b         | 0b         | 0b        | 0b        | 0b        | 0b        | 1b        |

| Table 12. | USB state transitions (continu | ied) |

|-----------|--------------------------------|------|

|-----------|--------------------------------|------|

|                                       | Register settings |            |        |            |            |           | Resistor settings |           |           |           |  |

|---------------------------------------|-------------------|------------|--------|------------|------------|-----------|-------------------|-----------|-----------|-----------|--|

| Signaling mode                        | XcvrSelect        | TermSelect | OpMode | DpPulldown | DmPulldown | rpu_dp_en | rpu_dm_en         | rpd_dp_en | rpd_dm_en | hsterm_en |  |

| OTG device, peripheral chirp          | 00b               | 1b         | 10b    | 0b         | 1b         | 1b        | 0b                | 0b        | 1b        | 0b        |  |

| OTG device, peripheral high-speed     | 00b               | 0b         | 00b    | 0b         | 1b         | 0b        | 0b                | 0b        | 1b        | 1b        |  |

| OTG device, peripheral full-speed     | 01b               | 1b         | 00b    | 0b         | 1b         | 1b        | 0b                | 0b        | 1b        | 0b        |  |

| OTG device, peripheral HS/FS suspend  | 01b               | 1b         | 00b    | 0b         | 1b         | 1b        | 0b                | 0b        | 1b        | 0b        |  |

| OTG device, peripheral HS/FS resume   | 01b               | 1b         | 10b    | 0b         | 1b         | 1b        | 0b                | 0b        | 1b        | 0b        |  |

| OTG device, peripheral, Test_J/Test_K | 00b               | 0b         | 10b    | 0b         | 1b         | 0b        | 0b                | 0b        | 1b        | 1b        |  |

# 8 ULPI registers

| Table 13. | ULPI | register | map | overview |

|-----------|------|----------|-----|----------|

|           |      |          |     |          |

| Field name                                  |             | Address (6 bits) |           |         |     |  |  |

|---------------------------------------------|-------------|------------------|-----------|---------|-----|--|--|

| Field name                                  | Size (bits) | Rd               | Wr        | Set     | Clr |  |  |

| Immediate register set                      |             |                  |           | 1       |     |  |  |

| Vendor ID low                               | 8           | 00h              | -         | -       | -   |  |  |

| Vendor ID high                              | 8           | 01h              | -         | -       | -   |  |  |

| Product ID low                              | 8           | 02h              | -         | -       | -   |  |  |

| Product ID high                             | 8           | 03h              | -         | -       | -   |  |  |

| Function control                            | 8           | 04-06h           | 04h       | 05h     | 06h |  |  |

| Interface control                           | 8           | 07-09h           | 07h       | 08h     | 09h |  |  |