# VOICEBAND CODEC WITH MICROPHONE/SPEAKER DRIVE

#### **Features**

Complete voice codec solution includes the following:

- 84 dB ADC Dynamic Range

- 84 dB DAC Dynamic Range

- 4–12 kHz Sample Rates

- 30 dB Microphone Pre-Amp

- Programmable Input Gain/ Attenuation: –34.5 dB to 12 dB

- Programmable Output Gain/ Attenuation: –34.5 dB to 12 dB ■

- Support for 32 Ω Headphones

- 3:1 Analog Input Mixer

- 3.3–5.0 V Power Supply

- Direct Serial Interface to DSPs

- Direct Connection to Si303x/44/56, serial interface DAA chipsets

- Low profile 16-Pin SOIC Package

- RoHS-compliant package available

# Ordering Information: See page 29.

# **Applications**

- Modem Voice Channel (DSVD)

- Telephony

- Speech Processing

- General Purpose Analog I/O

- Companion chip for FDX

ISOmodems with voice features

# Description

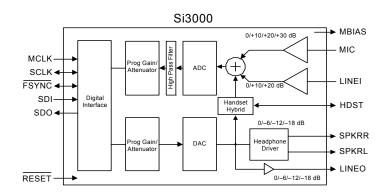

The Si3000 is a complete voice band audio codec solution that offers high integration by incorporating programmable input and output gain/ attenuation, a microphone bias circuit, handset hybrid circuit, and an output drive for 32  $\Omega$  headphones. The Si3000 can be connected directly to the Si3034, Si3035, Si3044, and Si3056 North American and international DAA chipsets through their daisy-chaining serial interface. It also serves as a companion chip to a FAT ISOmodem chipset with voice features, providing hardware support for a handset and speaker phone. The device operates from a single 3.3 to 5 V power supply and is available in a 16-pin small outline package (SOIC).

# **Functional Block Diagram**

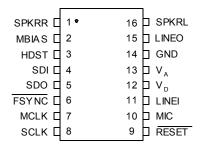

Pin Assignments Si3000 16 SPKRL SPKRR ☐ 1 º 15 LINEO MBIAS ☐ 2 14 GND HDST ☐ 3 SDI 🛮 4 13 🗖 V SDO d 5 FSYNC 6 11 LINE MCLK ☐ 7 10 | MIC SCLK ☐ 8 9 RESET

2

# TABLE OF CONTENTS

| <u>Section</u>                            | <u>Page</u> |

|-------------------------------------------|-------------|

| 1. Electrical Specifications              |             |

| 2. Functional Description                 |             |

| 2.1. Analog Inputs                        |             |

| 2.2. Pre-amp/Microphone Bias Circuit      |             |

| 2.3. Programmable Input Gain/Attenuation  |             |

| 2.4. Analog Outputs                       |             |

| 2.5. Programmable Output Gain/Attenuation |             |

| 2.6. Line Output                          |             |

| 2.7. Speaker Output                       |             |

| 2.8. Digital Interface                    |             |

| 2.9. Clock Generation Subsystem           |             |

| 2.10. Sleep Mode                          |             |

| 2.11. Loopback Operation                  |             |

| 2.12. Reducing Power-on Pop Noise         |             |

| 3. Control Registers                      |             |

| 4. Pin Descriptions: Si3000               |             |

| 5. Ordering Guide                         |             |

| 6. Package Outline: 16-Pin SOIC           |             |

| 7. 16-Pin SOIC Land Pattern               |             |

| 8. Package Markings (Top Markings)        |             |

| 8.1. Si3000-C-GS Top Marking              |             |

| 8.2. Si3000-C-FS Top Marking              |             |

| Document Change List                      |             |

| Contact Information                       |             |

3

# 1. Electrical Specifications

#### **Table 1. Recommended Operating Conditions**

| Parameter                                     | Symbol         | Test Condition | Min <sup>1</sup> | Тур     | Max <sup>1</sup> | Unit |

|-----------------------------------------------|----------------|----------------|------------------|---------|------------------|------|

| Ambient Temperature                           | T <sub>A</sub> | F and K-grade  | 0                | 25      | 70               | °C   |

| Si3000 Supply Voltage, Analog <sup>2</sup>    | V <sub>A</sub> |                | 3.0              | 3.3/5.0 | 5.25             | V    |

| Si3000 Supply Voltage, Digital <sup>2,3</sup> | V <sub>D</sub> |                | 3.0              | 3.3/5.0 | 5.25             | V    |

#### Notes:

- 1. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25°C unless otherwise stated.

- 2. The digital supply,  $V_{D_i}$  and analog supply,  $V_{A_i}$  can operate from either 3.3 V or 5.0 V. The Si3000 supports interface to 3.3 V logic when operating from 3.3 V.  $V_D$  must be within 0.6 V of  $V_A$ .

- **3.** The Si3000 specifications are guaranteed using the typical application circuit (including component tolerance) of Figure 13.

# Table 2. DC Characteristics, $V_A/V_D = 5 V$

$(V_A = 5 V \pm 5\%, V_D = 5 V \pm 5\%, T_A = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                                     | Symbol          | Test Condition         | Min | Тур | Max | Unit |

|-----------------------------------------------|-----------------|------------------------|-----|-----|-----|------|

| High Level Input Voltage                      | V <sub>IH</sub> |                        | 3.5 | _   | _   | V    |

| Low Level Input Voltage                       | V <sub>IL</sub> |                        | _   | _   | 0.8 | V    |

| High Level Output Voltage                     | V <sub>OH</sub> | I <sub>O</sub> = -2 mA | 3.5 | _   | _   | V    |

| Low Level Output Voltage                      | V <sub>OL</sub> | I <sub>O</sub> = 2 mA  | _   | _   | 0.4 | V    |

| Input Leakage Current                         | ΙL              |                        | -10 | _   | 10  | μA   |

| Power Supply Current, Analog <sup>1</sup>     | I <sub>A</sub>  | V <sub>A</sub> pin     | _   | 6.5 | 10  | mA   |

| Power Supply Current, Digital <sup>2</sup>    | I <sub>D</sub>  | V <sub>D</sub> pin     | _   | 10  | 15  | mA   |

| Total Supply Current, Sleep Mode <sup>3</sup> |                 |                        | _   | _   | 1.5 | mA   |

#### Notes:

- 1. No loads at DAC outputs, no load at MBIAS, Fs=12.5 kHz.

- 2. Slave mode operation, Fs = 12.5 kHz.

- 3. All inputs, except MCLK, are held static, and all outputs are unloaded.

## Table 3. DC Characteristics, $V_A/V_D = 3.3 V$

$(V_A = 3.3 \text{ V} \pm 10\%, V_D = 3.3 \text{ V} \pm 10\%, T_A = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                                     | Symbol          | Test Condition         | Min | Тур | Max  | Unit |

|-----------------------------------------------|-----------------|------------------------|-----|-----|------|------|

| High Level Input Voltage                      | V <sub>IH</sub> |                        | 2.4 | _   | _    | V    |

| Low Level Input Voltage                       | V <sub>IL</sub> |                        | _   | _   | 8.0  | V    |

| High Level Output Voltage                     | V <sub>OH</sub> | I <sub>O</sub> = -2 mA | 2.4 | _   | _    | V    |

| Low Level Output Voltage                      | V <sub>OL</sub> | I <sub>O</sub> = 2 mA  | _   | _   | 0.35 | V    |

| Input Leakage Current                         | ΙL              |                        | -10 | _   | 10   | μA   |

| Power Supply Current, Analog                  | I <sub>A</sub>  | V <sub>A</sub> pin     | _   | 6   | 10   | mA   |

| Power Supply Current, Digital <sup>2</sup>    | I <sub>D</sub>  | V <sub>D</sub> pin     | _   | 6   | 10   | mA   |

| Total Supply Current, Sleep Mode <sup>3</sup> |                 |                        | _   | _   | 1.5  | mA   |

#### Notes:

- 1. No loads at DAC outputs, no load at MBIAS, Fs=12.5 kHz.

- 2. Slave mode operation, Fs = 12.5 kHz.

- 3. All inputs, except MCLK, are held static, and all outputs are unloaded.

#### **Table 4. AC Characteristics**

$(V_A, V_D = 5 V \pm 5\% \text{ or } 3.3 V \pm 10\%, T_A = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                                     | Symbol          | Test Condition                      | Min   | Тур            | Max         | Unit             |

|-----------------------------------------------|-----------------|-------------------------------------|-------|----------------|-------------|------------------|

| ADC Resolution                                |                 |                                     | _     | 16             | _           | Bits             |

| ADC Dynamic Range <sup>1,2</sup>              | ADCDR           | VIN = 1 kHz, -3 dB                  | 80    | 84             | _           | dB               |

| ADC Total Harmonic Distortion <sup>3</sup>    | ADCTHD          | VIN = 1 kHz, -3 dB, MIC/LINEI       | _     | -80            | -62         | dB               |

| $V_A, V_D = 3.3 V \pm 10\%$                   |                 | VIN = 1 kHz, -3 dB, HDST            | _     | -80            | -62         |                  |

| ADC Total Harmonic Distortion <sup>3</sup>    | ADCTHD          | VIN = 1 kHz, –3 dB, MIC/LINEI       | _     | -80            | <b>–76</b>  | dB               |

| $V_A, V_D = 5 V \pm 5\%$                      |                 | VIN = 1 kHz, -3 dB, HDST            | _     | -80            | <b>-71</b>  |                  |

| ADC Full Scale Level (0 dB gain) <sup>4</sup> | V <sub>RX</sub> | Vin = 1 kHz                         | _     | 1              | _           | V <sub>rms</sub> |

| ADC Programmable Input Gain                   |                 |                                     | -34.5 | _              | 12          | dB               |

| ADC Input Gain Step Size                      |                 |                                     | _     | 1.5            | _           | dB               |

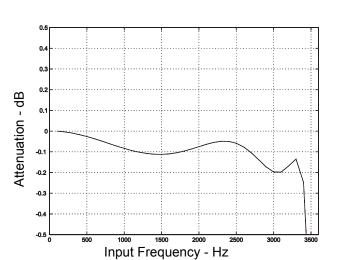

| ADC Freq Response <sup>5</sup>                | F <sub>RR</sub> | Low –3 dB corner                    | _     | 33             | _           | Hz               |

| ADC Freq Response <sup>5</sup>                | F <sub>RR</sub> | 300 Hz                              | -0.1  | _              | 0           | dB               |

| ADC Freq Response                             | F <sub>RR</sub> | 3400 Hz                             | -0.2  | _              | 0           | dB               |

| Line In Preamp Gain                           |                 |                                     | _     | 0/10/20        | _           | dB               |

| Mic In Preamp Gain                            |                 |                                     |       | 0/10/20/<br>30 | _           | dB               |

| ADC Input Resistance                          |                 | 0 dB Preamp Gain                    | _     | 20             | _           | kΩ               |

| ADC Input Capacitance                         |                 |                                     | _     | 15             | _           | pF               |

| ADC Gain Drift                                | A <sub>T</sub>  | VIN = 1 kHz                         | _     | 0.002          | _           | dB/°C            |

| DAC Resolution                                |                 |                                     | _     | 16             | _           | Bits             |

| DAC Dynamic Range <sup>1,2</sup>              | DACDR           | VIN = 1 kHz, –6 dB                  | 80    | 84             | _           | dB               |

| DAC Total Harmonic Distortion <sup>3</sup>    | DACTHD          | VIN=1 kHz,–6 dB,LINEO,600 $\Omega$  | _     | -76            | -60         | dB               |

| $V_A, V_D = 3.3 V \pm 10\%$                   |                 | VIN=1 kHz,–6 dB, SPKR, 60 $\Omega$  | _     | -72            | -60         |                  |

|                                               |                 | VIN=1 kHz,–6 dB, HDST, 600 $\Omega$ | _     | -80            | <b>–</b> 70 |                  |

| DAC Total Harmonic Distortion <sup>3</sup>    | DACTHD          | VIN=1 kHz,-3 dB,LINEO,600 Ω         | _     | -76            | -65         | dB               |

| $V_A, V_D = 5 V \pm 5\%$                      |                 | VIN=1 kHz,–3 dB, SPKR, 60 $\Omega$  | _     | <b>-72</b>     | -65         |                  |

|                                               |                 | VIN=1 kHz,–3 dB, HDST, 600 $\Omega$ | _     | -80            | <b>–</b> 76 |                  |

| DAC Full Scale Level (0 dB gain)              | V <sub>RX</sub> |                                     | _     | 1              | _           | V <sub>rms</sub> |

| DAC Programmable Output Gain                  |                 |                                     | -34.5 | _              | 12          | dB               |

#### Notes:

- 1. DR = VIN + 20 log (RMS signal/RMS noise). Measurement bandwidth is 300 to 3400 Hz. Valid sample rate ranges between 4000 and 12000 Hz.

- 2. 0 dB setting for analog and digital attenuation/gain.

- 3. THD = 20 log (RMS distortion/RMS signal). Valid sample rate ranges between 4000 and 12000 Hz.

- **4.** At 0 dB gain setting, 1  $V_{rms}$  input corresponds to -1.5 dB of full scale digital output code.

- **5.** These characteristics are determined by external components. See Figure 13.

- **6.** With a 600  $\Omega$  load. Output starts clipping with half of full scale digital input, which corresponds to a 0.5  $V_{rms}$  output.

## Table 4. AC Characteristics (Continued)

$(V_A, V_D = 5 V \pm 5\% \text{ or } 3.3 V \pm 10\%, T_A = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                                 | Symbol             | Test Condition   | Min   | Тур   | Max | Unit             |

|-------------------------------------------|--------------------|------------------|-------|-------|-----|------------------|

| DAC Output Gain Step Size                 |                    |                  | _     | 1.5   | _   | dB               |

| DAC Freq Response <sup>5</sup>            | F <sub>RR</sub>    | Low –3 dB corner | _     | 33    | _   | Hz               |

| DAC Freq Response <sup>5</sup>            | F <sub>RR</sub>    | 300 Hz           | -0.01 | _     | 0   | dB               |

| DAC Freq Response                         | F <sub>RR</sub>    | 3400 Hz          | -0.2  | _     | 0   | dB               |

| DAC Line Output Load Resistance           |                    |                  | 600   | _     | _   | Ω                |

| DAC Line Output Load Capacitance          |                    |                  | _     | _     | 40  | pF               |

| DAC SPKR Output Load Resistance           |                    |                  | _     | 60    | _   | Ω                |

| DAC Gain Drift                            | A <sub>T</sub>     | VIN = 1 kHz      | _     | 0.002 | _   | dB/°C            |

| Interchannel Isolation (Crosstalk)        |                    |                  | _     | 90    | _   | dB               |

| HDST Full Scale Level Input               |                    |                  | _     | 0.5   | _   | V <sub>rms</sub> |

| HDST Full Scale Level Output <sup>6</sup> |                    |                  | _     | 1.0   | _   | V <sub>rms</sub> |

| HDST Output Resistance                    | Rout               | DC               | _     | 600   | _   | Ω                |

| MIC Bias Voltage                          | V <sub>mbias</sub> |                  | _     | 2.5   | _   | V                |

| MIC Power Supply Rejection Ratio          | PSRR               |                  | _     | 40    | _   | dB               |

#### Notes:

- 1. DR = VIN + 20 log (RMS signal/RMS noise). Measurement bandwidth is 300 to 3400 Hz. Valid sample rate ranges between 4000 and 12000 Hz.

- 2. 0 dB setting for analog and digital attenuation/gain.

- 3. THD = 20 log (RMS distortion/RMS signal). Valid sample rate ranges between 4000 and 12000 Hz.

- **4.** At 0 dB gain setting, 1  $V_{rms}$  input corresponds to -1.5 dB of full scale digital output code.

- **5.** These characteristics are determined by external components. See Figure 13.

- **6.** With a 600  $\Omega$  load. Output starts clipping with half of full scale digital input, which corresponds to a 0.5  $V_{rms}$  output.

#### Table 5. Absolute Maximum Ratings

| Parameter                                | Symbol           | Value                          | Unit |

|------------------------------------------|------------------|--------------------------------|------|

| DC Supply Voltage                        | $V_D, V_A$       | -0.5 to 6.0                    | V    |

| Input Current, Si3000 Digital Input Pins | I <sub>IN</sub>  | ±10                            | mA   |

| Digital Input Voltage                    | V <sub>IND</sub> | -0.3 to (V <sub>D</sub> + 0.3) | V    |

| Operating Temperature Range              | T <sub>A</sub>   | -10 to 100                     | °C   |

| Storage Temperature Range                | T <sub>STG</sub> | -40 to 150                     | °C   |

**Note:** Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

SHIPPN LAD

## Table 6. Switching Characteristics—General Inputs

$(V_A, V_D = 5 \text{ V} \pm 5\% \text{ or } 3.3 \text{ V} \pm 10\%, T_A = 0 \text{ to } 70^{\circ}\text{C}, C_L = 20 \text{ pF})$

| Parameter <sup>1</sup>         | Symbol           | Test Condition | Min   | Тур | Max | Unit |

|--------------------------------|------------------|----------------|-------|-----|-----|------|

| Cycle Time, MCLK               | t <sub>mc</sub>  |                | 16.67 | _   | _   | ns   |

| MCLK Duty Cycle                | t <sub>dty</sub> |                | 40    | 50  | 60  | %    |

| Rise Time, MCLK                | t <sub>r</sub>   |                | _     | _   | 5   | ns   |

| Fall Time, MCLK                | t <sub>f</sub>   |                | _     | _   | 5   | ns   |

| RESET Pulse Width <sup>2</sup> | t <sub>rl</sub>  |                | 250   | _   | _   | ns   |

| Rise Time, RESET               | t <sub>Rr</sub>  |                | _     | 1   | _   | μs   |

#### Notes:

- All timing (except Rise and Fall time) is referenced to the 50% level of the waveform. Input test levels are V<sub>IH</sub> = V<sub>D</sub> 0.4 V, V<sub>IL</sub> = 0.4 V. Rise and Fall times are referenced to the 20% and 80% levels of the waveform.

The minimum RESET pulse width is the greater of 5 µs or 10 MCLK cycle times.

Figure 1. General Inputs Timing Diagram

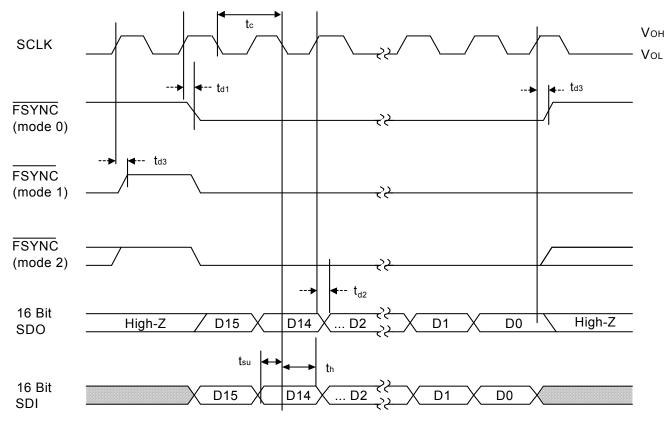

Table 7. Switching Characteristics—Serial Interface

$(V_A, V_D = 5 \text{ V} \pm 5\% \text{ or } 3.3 \text{ V} \pm 10\%, T_A = 0 \text{ to } 70^{\circ}\text{C}, C_L = 20 \text{ pF})$

| Parameter                                                                                                                                               | Symbol           | Test Condition | Min | Тур      | Max | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-----|----------|-----|------|

| Cycle Time, SCLK                                                                                                                                        | t <sub>c</sub>   |                | 354 | 1/256 Fs |     | ns   |

| SCLK Duty Cycle                                                                                                                                         | t <sub>dty</sub> |                | _   | 50       | _   | %    |

| Delay Time, SCLK ↑ to FSYNC ↓                                                                                                                           | t <sub>d1</sub>  |                | _   | _        | 10  | ns   |

| Delay Time, SCLK ↑ to SDO Valid                                                                                                                         | t <sub>d2</sub>  |                | _   | _        | 20  | ns   |

| Delay Time, SCLK ↑ to FSYNC ↑                                                                                                                           | t <sub>d3</sub>  |                | _   | _        | 10  | ns   |

| Setup Time, SDI, before SCLK $\downarrow$                                                                                                               | t <sub>su</sub>  |                | 25  | _        | _   | ns   |

| Hold Time, SDI, after SCLK $\downarrow$                                                                                                                 | t <sub>h</sub>   |                | 20  | _        | _   | ns   |

| Setup Time, FSYNC (mode 2) before MCLK $\downarrow$                                                                                                     | t <sub>su</sub>  |                | 25  | _        | _   | ns   |

| Hold Time, FSYNC (mode 2) after MCLK ↓                                                                                                                  | t <sub>h</sub>   |                | 20  | _        | _   | ns   |

| <b>Note:</b> All timing is referenced to the 50% level of the waveform. Input test levels are $V_{IH} = V_D - 0.4 \text{ V}$ , $V_{IL} = 0.4 \text{ V}$ |                  |                |     |          |     |      |

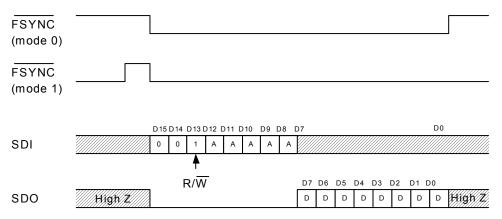

Figure 2. Serial Interface Timing Diagram

8

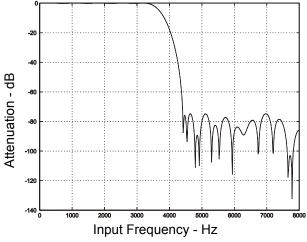

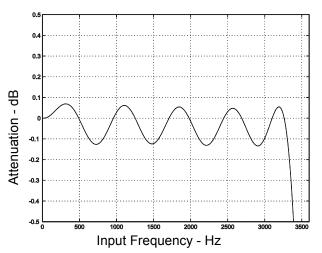

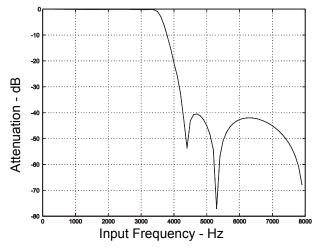

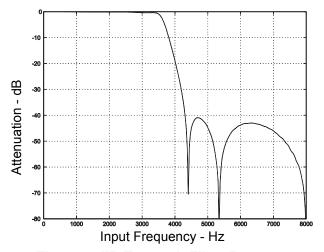

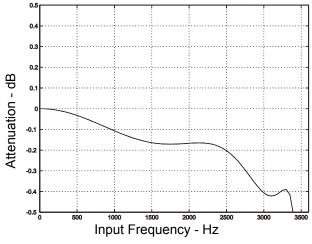

## Table 8. Digital FIR Filter Characteristics—Transmit and Receive

$(V_A, V_D = 5 \text{ V} \pm 5\% \text{ or } 3.3 \text{ V} \pm 10\%, \text{ Sample Rate} = 8 \text{ kHz}, T_A = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                                    | Symbol                                                                                         | Min  | Тур   | Max | Unit |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------|------|-------|-----|------|--|--|

| Passband (3 dB, HPFD = 1)                    | F <sub>(3 dB)</sub>                                                                            | 0    | _     | 3.6 | kHz  |  |  |

| Passband (3 dB, HPFD = 0)                    | F <sub>(3 dB)</sub>                                                                            | 0.01 | _     | 3.6 | kHz  |  |  |

| Passband Ripple Peak-to-Peak                 |                                                                                                | -0.1 | _     | 0.1 | dB   |  |  |

| Stopband                                     |                                                                                                | _    | 4.4   | _   | kHz  |  |  |

| Stopband Attenuation                         |                                                                                                | -74  | _     | _   | dB   |  |  |

| Group Delay                                  | t <sub>gd</sub>                                                                                | _    | 12/Fs | _   | sec  |  |  |

| Note: Typical FIR filter characteristics for | Note: Typical FIR filter characteristics for Fs = 8000 Hz are shown in Figures 3, 4, 5, and 6. |      |       |     |      |  |  |

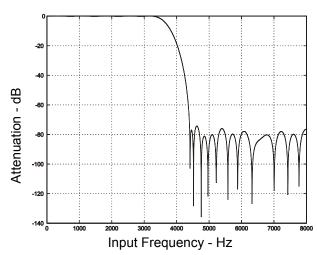

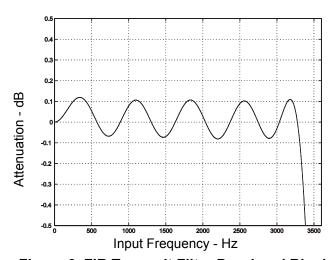

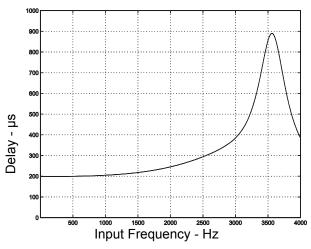

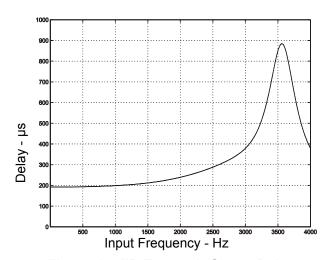

# Table 9. Digital IIR Filter Characteristics—Transmit and Receive

$(V_A, V_D = 5 V \pm 5\% \text{ or } 3.3 V \pm 10\%, \text{ Sample Rate} = 8 \text{ kHz}, T_A = 70^{\circ}\text{C})$

| Parameter                    | Symbol              | Min  | Тур    | Max | Unit |

|------------------------------|---------------------|------|--------|-----|------|

| Passband (3 dB, HPFD = 1)    | F <sub>(3 dB)</sub> | 0    | _      | 3.6 | kHz  |

| Passband (3 dB, HPFD = 0)    | F <sub>(3 dB)</sub> | 0.01 | _      | 3.6 | kHz  |

| Passband Ripple Peak-to-Peak |                     | -0.2 | _      | 0.2 | dB   |

| Stopband                     |                     | _    | 4.4    | _   | kHz  |

| Stopband Attenuation         |                     | -40  | _      | _   | dB   |

| Group Delay                  | t <sub>gd</sub>     | _    | 1.6/Fs | _   | sec  |

**Note:** Typical IIR filter characteristics for Fs = 8000 Hz are shown in Figures 7, 8, 9, and 10. Figures 11 and 12 show group delay versus input frequency.

Figure 3. FIR Receive Filter Response

Figure 5. FIR Transmit Filter Response

Figure 4. FIR Receive Filter Passband Ripple

Figure 6. FIR Transmit Filter Passband Ripple

For Figures 3–6, all filter plots apply to a sample rate of Fs = 8 kHz. The filters scale with the sample rate as follows:

$$F_{(0.1 \text{ dB})} = 0.4125 \text{ Fs}$$

$$F_{(-3 dB)} = 0.45 Fs$$

where Fs is the sample frequency.

SILICON LARS

Figure 7. IIR Receive Filter Response

Figure 8. IIR Receive Filter Passband Ripple

Figure 9. IIR Transmit Filter Response

Figure 10. IIR Transmit Filter Passband Ripple

Figure 11. IIR Receive Group Delay

Figure 12. IIR Transmit Group Delay

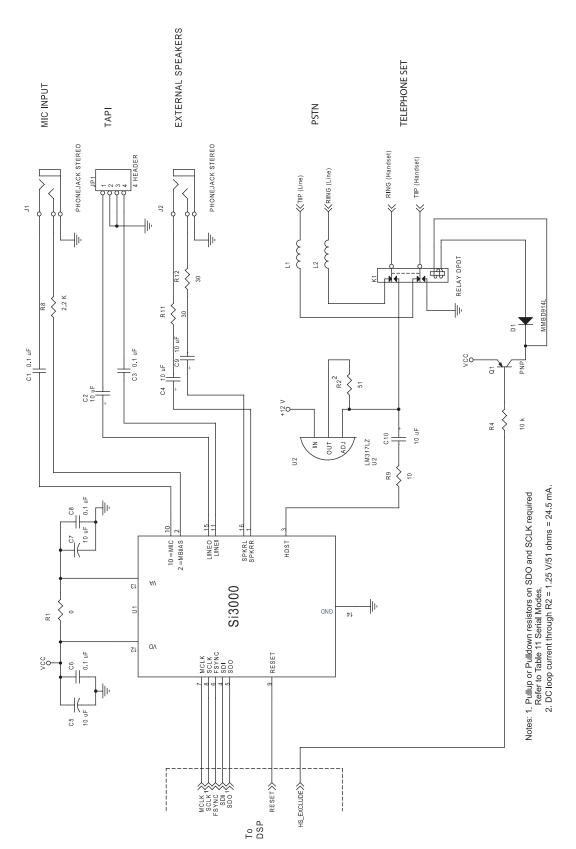

Figure 13. Si3000 Typical Application Circuit

Table 10. Component Values—Typical Application

| Symbol             | Value              |

|--------------------|--------------------|

| C1,C3,C6,C8        | 0.1 μF, 16 V, ±20% |

| C2,C4,C5,C7,C9,C10 | 10 μF, 16 V, ±20%  |

| D1                 | Motorola MMBD914L  |

| J1,J2              | Phonejack Stereo   |

| JP1                | 4 Header           |

| K1                 | Relay DPDT         |

| L1,L2              | Ferrite Bead       |

| R1                 | 0 Ω, 1/4 W ±5%     |

| R2                 | 51 Ω, 1/4 W ±5%    |

| R4                 | 10 kΩ, 1/4 W ±5%   |

| R8                 | 2.2 k, 1/4 W, ±5%  |

| R9                 | 10 Ω, 1/16 W, ±5%  |

| R11,R12            | 30 Ω, 1/16 W, ±5%  |

| U2                 | LM317LZ            |

| Q1                 | PNP Transistor     |

# 2. Functional Description

The Si3000 is a highly integrated voice bandwidth audio codec which contains a single 16-bit A/D converter and D/A converter. The analog input path contains a microphone input with selectable gain, a line level input with selectable gain, and a handset input. Each of the inputs go through a mixer prior to A/D conversion. The result of this A/D conversion is a 16-bit 2s complement signed number. Following the A/D converter is a digital programmable gain amplifier. The analog output path contains a digital programmable gain amplifier feeding a single 16-bit D/A converter. The DAC output is provided to a line output, a headphone drive output, and a handset output. Control for the various functions available on the Si3000 as well as the audio data are communicated to the device over a serial interface.

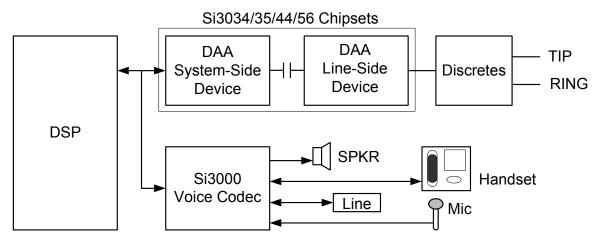

The Si3000 can be connected directly to the Si3035, Si3034, Si3044, or Si3056 in modem applications requiring a voice channel, or the device can be used as a stand-alone codec in other voice band applications. The Si3000 offers high integration, and it needs only a few low-cost, discrete components as shown in Figure 13.

# 2.1. Analog Inputs

The typical connection diagram (Figure 13) shows the recommended external analog circuitry for the Si3000. The device supports three mono analog inputs—line level, microphone level, and a handset input. Each of these inputs is provided to a mixer circuit prior to A/D conversion. Each analog input may also be muted by writing the appropriate bits in the control registers. Unused analog inputs should be tied to GND through a  $0.1~\mu F$  capacitor. This prevents any DC current flow.

### 2.2. Pre-amp/Microphone Bias Circuit

An internal amplifier with a selectable gain of 0 dB, 10 dB, 20 dB, or 30 dB is provided for the MIC input and an internal amplifier with a selectable gain of 0 dB, 10 dB, or 20 dB, is provided for the LINEI input. AC coupling is required for both inputs because any DC offset on the input will be amplified if gain is selected. Gain settings for the LINEI and MIC inputs are achieved by writing the RX Gain Control 1 register 5. When gain is disabled, these inputs become line level inputs with a full-scale input of 1 Vrms.

A microphone bias circuit is provided on-chip which consists of a 2.5 V reference output capable of sourcing up to 5 mA of current. This circuit can be used for active microphones requiring a bias source.

# 2.3. Programmable Input Gain/Attenuation

The signals from the microphone, line, or handset inputs are mixed and then routed to the A/D converter and a digital programmable gain circuit which provides up to 12 dB of gain or –34.5 dB of attenuation in 1.5 dB steps. Level changes only take effect on zero crossings to minimize audible artifacts. The requested level change is implemented if no zero crossing is found after 256 frames. Write the ADC Volume Control register 6 to set digital input gain/attenuation.

# 2.4. Analog Outputs

The analog outputs of the D/A converter are routed to a line level output (LINEO), a pair of speaker outputs (SPKRL and SPKRR), and a handset. Each analog output can be independently muted.

Figure 14. Si3000 with Silicon Labs DAA System Diagram

### 2.5. Programmable Output Gain/Attenuation

Prior to D/A conversion, the Si3000 contains a digital programmable gain/attenuator which provides up to 12 dB of gain or –34.5 dB of attenuation in 1.5 dB steps. Level changes only take effect on zero crossings to minimize audible artifacts. The requested level change is implemented if no zero crossing is found after 256 frames. Write the DAC Volume Control (register 7) to set digital input gain/attenuation.

### 2.6. Line Output

LINEO is a line level analog output signal centered around a common mode voltage. The minimum recommended load impedance is  $600~\Omega.$  This output is a fully filtered output with a 1 Vrms full scale range. The only external component required is the  $10~\mu F$  DC blocking capacitor shown in Figure 13 on page 12. This output may be muted through the LOM bit in register 6 or attenuated by setting the analog attenuation bits in register 9.

### 2.7. Speaker Output

The SPKRL and SPKRR are mono, in-phase, analog outputs capable of driving a small loudspeaker whose impedance is typically 32  $\Omega$  (see Figure 13 on page 12). The speaker outputs may be muted through the SLM and SRM bits in the DAC Gain Control register 7 or attenuated by setting the analog attenuation bits in register 9.

# 2.8. Digital Interface

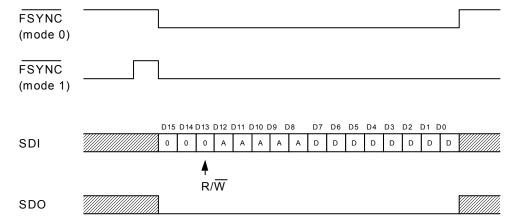

The Si3000 has two serial interface modes that support most standard modem DSPs. These modes are selected by the addition of a 50 k $\Omega$  pull-down/up resistor on the SDO and SCLK pins as shown in Figure 13 on page 12. The key difference between these two serial modes is the operation of the FSYNC signal. Table 11 summarizes the serial mode definitions.

**Table 11. Serial Modes**

| Mode           | SCLK*                           | SDO* | Description                   |  |  |  |  |  |

|----------------|---------------------------------|------|-------------------------------|--|--|--|--|--|

| 0              | 0                               | 0    | FSYNC frames data             |  |  |  |  |  |

| 1              | 0                               | 1    | FSYNC pulse starts data frame |  |  |  |  |  |

| 2              | 1                               | 0    | Slave mode                    |  |  |  |  |  |

| 3 1 1 Reserved |                                 |      |                               |  |  |  |  |  |

| *Note:         | *Note: Pull-up/pull-down states |      |                               |  |  |  |  |  |

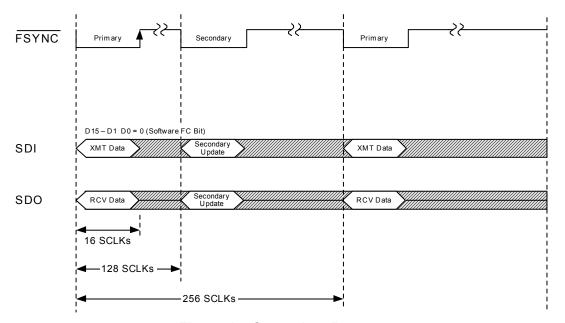

The digital interface consists of a single synchronous serial link which communicates audio and control data. In slave mode, SCLK is connected only to the pullup/pulldown resistor, and MCLK is a 256 Fs input which is internally multiplied using the on-chip phase-locked loop (PLL) to clock the A/D converter and D/A converter. In master mode, the master clock (MCLK) is an input and the serial data clock (SCLK) is an output. The MCLK

frequency and the value of the sample rate control registers 3 and 4 determine the sample rate (Fs). The serial port clock, SCLK, runs at 256 bits per frame, where the frame rate is equivalent to the sample rate. Digital information is transferred between the DSP and the Si3000 in the form of 16-bit Primary Frames and 16-bit Scandary Frames.

the Si3000 in the form of 16-bit Primary Frames and 16-bit Secondary Frames. There are separate pins for receive (SDO) and transmit (SDI) functions, providing simultaneous receive/transmit operation within each frame.

Primary Frames are used for digital audio data samples. Primary Frames occur at the frame rate and are always present.

Secondary Frames are used for accessing internal Si3000 registers. Secondary Frames are not always present and are requested on-demand. When Secondary Frames are present, they occur mid-point between Primary Frames. Hence, no Primary Frames are dropped.

On Primary Frame transmits (DSP to Si3000), the Si3000 treats the LSB (16th bit) as a flag to request a Secondary Frame. Set the primary frame LSB = 1 to request a secondary frame; otherwise, set the primary frame LSB = 0. Therefore, out of 16-bits of transmit data on SDI, only 15-bits represent actual audio data. When secondary frames are not present, no transmission occurs during this time slot.

On Primary Frames receives (Si3000 to DSP), the Si3000 drives SDO with 16-bits of audio data, if the Si3000 is in either Serial Mode 0 or 1. However, if the Si3000 is in SLAVE mode (Mode 2), the Si3000 supplies 15-bits of Audio Data to the DSP and always drives the LSB zero. This feature is designed to work with the Si3021 register 14 SSEL set to 10. In this system configuration, when the DSP receives Primary Frames, it can check the LSB to determine whether the receive data is from the Si3021 or from the Si3000.

On Secondary Frame receives and transmits; the Si3000 treats the input and output serial stream as 16-bits of data. Figure 15 shows the relative timing of the serial frames.

Figure 16 and Figure 17 illustrate the secondary frame write cycle and read cycle, respectively. During a read cycle, the R/W bit is high and the 5-bit address field contains the address of the register to be read. The contents of the 8-bit control register are placed on the SDO signal. During a write cycle, the R/W bit is low and the 5-bit address field contains the address of the register to be written. The 8-bit data to be written immediately follows the address on SDI. Only one register can be read or written during each secondary frame. See "3. Control Registers" on page 19 for the register addresses and functions.

Figure 15. Secondary Request

Figure 16. Secondary Communication Data Format—Write Cycle

Figure 17. Secondary Frame Format—Read Cycle

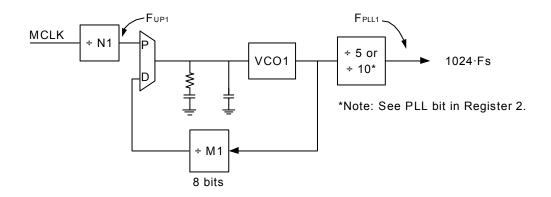

Figure 18. Clock Generation Subsystem (PLL)

### 2.9. Clock Generation Subsystem

The Si3000 contains an on-chip clock generator. Using a single MCLK input frequency, the Si3000 can generate all the desired standard modem sample rates, as well as the common 11.025 kHz rate for audio playback.

The clock generator consists of a phase-locked loop (PLL1) that achieves the desired sample frequency. Figure 18 illustrates the clock generator. The architecture of the PLL allows for fast lock time on initial start-up, fast lock time when changing modem sample rates and high noise immunity. A large number of MCLK frequencies between 1 MHz and 60 MHz are supported.

#### 2.9.1. Programming the Clock Generator

As noted in Figure 18, the clock generator must output a clock equal to 1024\*Fs, where Fs is the desired sample rate. The 1024\*Fs clock is determined through programming of the following registers:

Register 3 - N1 divider, 8 bits.

Register 4 - M1 divider, 8 bits

N1 (register 3) and M1 (register 4) are 8-bit unsigned values.  $F_{MCLK}$  is the clock provided to the MCLK pin. Table 12 lists several standard crystal rates that could be supplied to MCLK.

When programming the registers of the clock generator, the order of register writes is important. For PLL updates, N1 (register 3) must always be written first, immediately followed by a write to M1 (register 4).

**Note:** The values shown in Table 12 satisfy the equations above. However, when programming the registers for N1 and M1, the value placed in these registers must be one less than the value calculated from the equations.

Table 12. MCLK Examples for 8 kHz

| MCLK (MHz) | N1  | M1  |

|------------|-----|-----|

| 1.8432     | 9   | 200 |

| 4.0000     | 25  | 256 |

| 4.0960     | 1   | 10  |

| 5.2800     | 33  | 256 |

| 5.7600     | 9   | 64  |

| 6.1440     | 3   | 20  |

| 8.1920     | 1   | 5   |

| 9.2160     | 9   | 40  |

| 10.0800    | 63  | 256 |

| 10.5600    | 33  | 128 |

| 11.0592    | 27  | 100 |

| 12.288     | 3   | 10  |

| 14.7456    | 9   | 25  |

| 16.0000    | 25  | 64  |

| 18.4320    | 9   | 20  |

| 24.5760    | 3   | 5   |

| 25.8048    | 63  | 100 |

| 33.7600    | 211 | 256 |

| 44.2368    | 27  | 25  |

| 46.0800    | 9   | 8   |

| 47.9232    | 117 | 100 |

| 48.0000    | 75  | 64  |

| 56.0000    | 175 | 128 |

| 59.200     | 185 | 128 |

#### 2.9.2. PLL Lock Times

The Si3000 changes sample rates very quickly. However, lock time will vary based on the programming of the clock generator. The following relationship describes the boundaries on PLL locking time:

PLL lock time < 1 ms

It is recommended that the PLL be programmed during initialization.

The final design consideration for the clock generator is the update rate of PLL. The following criteria must be satisfied in order for the PLL to remain stable:

$$F_{UP1} = F_{MCLK}/(N1) \ge 144kHz$$

Where F<sub>UP1</sub> is shown in Figure 18.

#### 2.9.3. Setting Generic Sample Rates

The above clock generation description focuses on common modem sample rates. The restrictions and equations above still apply; however, a more generic relationship between MCLK and Fs (the desired sample rate) is needed. The following equation describes this relationship:

$$\frac{M1}{N1} = \frac{5 \cdot 1024 \cdot Fs}{MCLK}$$

where *Fs* is the sample frequency, and all other symbols are shown in Figure 18.

Knowing the MCLK frequency and desired sample rate the values for the M1 and N1 registers can be determined. When determining these values, remember to consider the range for each register as well as the minimum update rate for the first PLL.

The values determined for M1 and N1 must be adjusted by minus one when determining the value written to the respective registers. This is due to internal logic, which adds one to the value stored in the register. This addition allows the user to write a zero value in any of the registers and the effective divide-by is one. A special case occurs when both M1 and N1 are programmed with a zero value. When M1 and N1 are both zero, the PLL is bypassed.

# 2.10. Sleep Mode

The Si3000 supports a low-power sleep mode. Sleep mode is activated by setting the Chip Power Down (CPD) bit in register 1. When the Si3000 is in sleep mode, the MCLK signal may be stopped or remain active, but it *must* be active before waking up the Si3000. To take the Si3000 out of sleep mode, pulse the reset pin (RESET) low. In summary, the power down/up sequence is as follows:

- 1. Set the Power Down bit (PDN, register 6, bit 3).

- 2. MCLK may stay active or stop.

- 3. Restore MCLK before initiating the power up sequence.

- Reset the Si3000 using the RESET pin (after MCLK is present).

- 5. Program the registers to desired settings.

### 2.11. Loopback Operation

The Si3000 advanced design provides the manufacturer with increased ability to determine system functionality during production line tests, as well as support for end-user diagnostics. Two loopback modes exist for this purpose, allowing increased coverage of system components.

The digital loopback1 mode allows an external device to send audio data to the SDI input pin and receive the signal through the SDO output pin. In this mode, the group delay of the digital filters is present. This mode allows testing of the digital filters, DAC, and ADC. To enable this mode, set the DL1 bit of register 2, and clear DL2.

The digital loopback2 mode allows an external device to send audio data to the SDI input pin and receive the signal through the SDO output pin. This mode allows testing of the digital filters, but not the ADC and DAC. To enable this mode, set the DL2 bit of register 2, and clear DL1.

# 2.12. Reducing Power-on Pop Noise

To minimize power-on pop during initialization, a waiting period is recommended before powering up the analog output drivers. The waiting period starts when the reset signal to the Si3000 is negated. The wait time required is dependent on the external load. Typically, the load consists of an AC coupling capacitor in series with an equivalent load resistor to ground. The equivalent load resistor can either be a speaker load, or the input resistance of an external amplifier. The rule-of-thumb for the waiting period in msec is derived by C\*(12+R). For example, in the case of a 10  $\mu F$  AC coupling capacitor and resistive load of 1.0 k $\Omega$  the recommended waiting period is  $10^*(12+1) = 130$  msec.

If the analog outputs drive external amplifiers, another factor to consider is the voltage division ratio determined by R/(R+12), where R represents the input resistance of the external amplifier. This ratio must be kept as small as possible. A good target value is R = 1 k $\Omega$ . If needed, add a load resistor in parallel with the amplifier input to lower the effective input resistance of the amplifier stage.

# 3. Control Registers

**Note:** Any register not listed here is reserved and should not be written. Any register bit labelled reserved should be written to zero during writes to the register. Register 0 can be read (always returns 0) and written safely.

**Table 13. Register Summary**

| Register | Name               | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------------|---------------|-------|-------|-------|-------|-------|-------|-------|

| 1        | Control 1          | SR            |       |       | SPD   | LPD   | HPD   | MPD   | CPD   |

| 2        | Control 2          |               |       |       | HPFD  | PLL   | DL1   | DL2   |       |

| 3        | PLL1 Divide N1     |               |       |       | Divid | er N1 |       |       |       |

| 4        | PLL1 Multiply M1   | Multiplier M1 |       |       |       |       |       |       |       |

| 5        | RX Gain Control 1  | LI            | G     | LIM   | М     | CG    | МСМ   | HIM   | IIR   |

| 6        | ADC Volume Control |               |       |       | RXG   |       |       | LOM   | НОМ   |

| 7        | DAC Volume Control | TXG           |       |       |       |       | SLM   | SRM   |       |

| 8        | Status Report      | SLSC          | SRSC  | LOSC  |       |       |       |       |       |

| 9        | Analog Attenuation |               |       |       |       | LOT   |       |       | )T    |

# Register 1. Control 1

| Bit  | D7  | D6 | D5 | D4  | D3  | D2  | D1  | D0  |

|------|-----|----|----|-----|-----|-----|-----|-----|

| Name | SR  |    |    | SPD | LPD | HPD | MPD | CPD |

| Туре | R/W |    |    | R/W | R/W | R/W | R/W | R/W |

Reset settings = 0000\_0000

| Bit | Name     | Function                                                                                                                                                   |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SR       | Software Reset.  1 = Sets all registers to their reset value.  0 = Enables chip for normal operation.  Note: Bit will automatically clear after being set. |

| 6:5 | Reserved | Read returns zero.                                                                                                                                         |

| 4   | SPD      | Speaker Drive Power Down.  1= Normal operation  0 = Power down left and right speaker drive.                                                               |

| 3   | LPD      | Line Drive Power Down.  1 = Normal operation  0 = Power down line driver.                                                                                  |

| 2   | HPD      | Handset Drive Power Down.  1 = Normal operation  0 = Power down handset driver.                                                                            |

| 1   | MPD      | MIC Bias Power Down.  1 = Power down MIC bias buffer.  0 = Normal operation                                                                                |

| 0   | CPD      | Chip Power Down. 1 = Puts Si3000 into power down mode. 0 = Normal operation                                                                                |

# Register 2. Control 2

| Bit  | D7 | D6 | D5 | D4   | D3  | D2  | D1  | D0 |

|------|----|----|----|------|-----|-----|-----|----|

| Name |    |    |    | HPFD | PLL | DL1 | DL2 |    |

| Туре |    |    |    | R/W  | R/W | R/W | R/W |    |

Reset Settings = 0000\_0000

| Bit | Name     | Function                                                                                                     |

|-----|----------|--------------------------------------------------------------------------------------------------------------|

| 7:5 | Reserved | Read returns zero.                                                                                           |

| 4   | HPFD     | High Pass Filter (HPF) Disable.  1 = HPF disabled  0 = HPF enabled                                           |

| 3   | PLL      | PLL Divide by 10.  1 = Sets final stage of PLL to divide by 10.  0 = Sets final stage of PLL to divide by 5. |

| 2   | DL1      | Digital Loopback.  1 = Enables digital loopback (DAC analog out → ADC analog in).  0 = Normal operation      |

| 1   | DL2      | Digital Loopback.  1 = Enables digital loopback (DAC one bit → ADC one bit).  0 = Normal operation           |

| 0   | Reserved | Read returns zero.                                                                                           |

# Register 3. PLL1 Divide N1

| Bit  | D7 | D6         | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

|------|----|------------|----|----|----|----|----|----|--|--|--|

| Name |    | Divider N1 |    |    |    |    |    |    |  |  |  |

| Туре |    |            |    | R/ | W  |    |    |    |  |  |  |

Reset settings = 0000\_0000

| Bit | Name | Function                                                              |

|-----|------|-----------------------------------------------------------------------|

| 7:0 | N1   | N1.                                                                   |

|     |      | Contains the (value – 1) for determining the output frequency on PLL. |

# Register 4. PLL1 Multiply M1

| Bit  | D7 | D6            | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

|------|----|---------------|----|----|----|----|----|----|--|--|--|--|

| Name |    | Multiplier M1 |    |    |    |    |    |    |  |  |  |  |

| Туре |    |               |    | R/ | W  |    |    |    |  |  |  |  |

Reset settings = 0000\_0000

| Bit | Name | Function                                                              |

|-----|------|-----------------------------------------------------------------------|

| 7:0 | M1   | M1.                                                                   |

|     |      | Contains the (value – 1) for determining the output frequency on PLL. |

# Register 5. RX Gain Control 1

| Bit  | D7  | D6  | D5  | D4 | D3 | D2  | D1  | D0  |

|------|-----|-----|-----|----|----|-----|-----|-----|

| Name | LI  | LIG |     | MC | CG | MCM | HIM | IIR |

| Туре | R/W |     | R/W | R/ | W  | R/W | R/W | R/W |

Reset settings = 0100\_0111

| Bit | Name | Function                           |

|-----|------|------------------------------------|

| 7:6 | LIG  | Line in Gain.                      |

|     |      | 11 = 20 dB gain                    |

|     |      | 10 = 10 dB gain                    |

|     |      | 01 = 0 dB gain                     |

|     |      | 00 = Reserved                      |

| 5   | LIM  | Line in Mute.                      |

|     |      | 1 = Line input muted               |

|     |      | 0 = Line input goes to mixer       |

| 4:3 | MCG  | MIC Input Gain.                    |

|     |      | 11 = 30 dB gain                    |

|     |      | 10 = 20 dB gain                    |

|     |      | 01 = 10 dB gain                    |

|     |      | 00 = 0 dB gain                     |

| 2   | MCM  | MIC Input Mute.                    |

|     |      | 1 = Mute MIC input                 |

|     |      | 0 = MIC input goes into mixer.     |

| 1   | HIM  | Handset Input Mute.                |

|     |      | 1 = Mute handset input             |

|     |      | 0 = Handset input goes into mixer. |

| 0   | IIR  | IIR Enable.                        |

|     |      | 1 = Enables IIR filter             |

|     |      | 0 = Enables FIR filter             |

# Register 6. ADC Volume Control

| Bit  | D7 | D6  | D5 | D4 | D3 | D2 | D1  | D0  |

|------|----|-----|----|----|----|----|-----|-----|

| Name |    | RXG |    |    |    |    | LOM | НОМ |

| Туре |    | R/W |    |    |    |    | R/W | R/W |

Reset settings = 0101\_1100

| Bit | Name     | Function                                                                                  |

|-----|----------|-------------------------------------------------------------------------------------------|

| 7   | Reserved | Read returns zero.                                                                        |

| 6:2 | RXG      | RX PGA Gain Control.<br>11111 = 12 dB<br>10111 = 0 dB<br>00000 = -34.5 dB<br>LSB = 1.5 dB |

| 1   | LOM      | Line Out Mute.  0 = Mute  1 = Active                                                      |

| 0   | НОМ      | Handset Out Mute.  0 = Mute 1 = Active                                                    |

# Register 7. DAC Volume Control

| Bit  | D7 | D6  | D5 | D4 | D3 | D2 | D1  | D0  |

|------|----|-----|----|----|----|----|-----|-----|

| Name |    | TXG |    |    |    |    | SLM | SRM |

| Туре |    | R/W |    |    |    |    | R/W | R/W |

Reset settings = 0101\_1100

| Bit | Name     | Function                                                                                  |

|-----|----------|-------------------------------------------------------------------------------------------|

| 7   | Reserved | Read returns zero.                                                                        |

| 6:2 | TXG      | TX PGA Gain Control.<br>11111 = 12 dB<br>10111 = 0 dB<br>00000 = -34.5 dB<br>LSB = 1.5 dB |

| 1   | SLM      | SPKR_L Mute.  0 = Mute  1 = Active                                                        |

| 0   | SRM      | SPKR_R Mute. 0 = Mute 1 = Active                                                          |

# Register 8. Status Report

| Bit  | D7   | D6   | D5   | D4 | D3 | D2 | D1 | D0 |

|------|------|------|------|----|----|----|----|----|

| Name | SLSC | SRSC | LOSC |    |    |    |    |    |

| Туре | R    | R    | R    |    |    |    |    |    |

Reset settings = 0000\_0000

| Bit | Name     | Function                                                                                               |

|-----|----------|--------------------------------------------------------------------------------------------------------|

| 7   | SLSC     | SPK_L Short Circuit.  1 = Indicate short circuit status is detected at left speaker.  0 = Normal mode  |

| 6   | SRSC     | SPK_R Short Circuit.  1 = Indicate short circuit status is detected at right speaker.  0 = Normal mode |

| 5   | LOSC     | Line Out Short Circuit.  1 = Indicate short circuit status is detected at line out.  0 = Normal mode   |

| 4:0 | Reserved | Read returns zero.                                                                                     |

# Register 9. Analog Attenuation

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|----|----|----|----|----|----|----|----|

| Name |    |    |    |    | LC | T  | SC | OT |

| Туре |    |    |    |    | R/ | W  | R/ | W  |

Reset settings = 0000\_0000

| Bit | Name     | Туре                                                                                                                                                                                                                              |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved | Read returns zero.                                                                                                                                                                                                                |

| 3:2 | LOT      | Line Out Attenuation.  11 = -18 dB analog attenuation on Line Output.  10 = -12 dB analog attenuation on Line Output.  01 = -6 dB analog attenuation on Line Output.  00 = 0 dB analog attenuation on Line Output.                |

| 2:0 | SOT      | Speaker Out Attenuation.  11 = -18 dB analog attenuation on Speaker Output.  10 = -12 dB analog attenuation on Speaker Output.  01 = -6 dB analog attenuation on Speaker Output.  00 = 0 dB analog attenuation on Speaker Output. |

# 4. Pin Descriptions: Si3000

| Pin# | Pin Name       | Description                                                                                                                                      |

|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | SPKRR          | Speaker Right Output.                                                                                                                            |

|      |                | Analog output capable of driving a 60 $\Omega$ load.                                                                                             |

| 2    | MBIAS          | Microphone bias output.                                                                                                                          |

| 3    | HDST           | Handset Input/Output.                                                                                                                            |

|      |                | Handset analog input/output.                                                                                                                     |

| 4    | SDI            | Serial Port Data In.                                                                                                                             |

|      |                | Serial communication and control data that is generated by the System DSP to the Si3000.                                                         |

| 5    | SDO            | Serial Port Data Out.                                                                                                                            |

|      |                | Serial communication data that is provided by the Si3000 to the system DSP.                                                                      |

| 6    | FSYNC          | Frame Sync Output.                                                                                                                               |

|      |                | Data framing signal that is used to indicate the start and stop of a communication data frame.                                                   |

| 7    | MCLK           | Master Clock Input.                                                                                                                              |

|      |                | High speed master clock input. Generally supplied by the system crystal clock or DSP.                                                            |

| 8    | SCLK           | Serial Port Bit Clock Input/Output.                                                                                                              |

|      |                | Controls the serial data on SDO and latches the data on SDI. This pin is an input in slave mode and an output in master mode.                    |

| 9    | RESET          | Reset.                                                                                                                                           |

|      |                | An active low input that is used to reset all control registers to a defined initialized state. Also used to bring the Si3000 out of sleep mode. |

| 10   | MIC            | MIC Input.                                                                                                                                       |

|      |                | Microphone level or line level input. This input contains selectable gain of 0, 10, 20, or 30 dB with a full scale input level of 1 $V_{RMS}$ .  |

| 11   | LINEI          | Line Input.                                                                                                                                      |

|      |                | Line level input with selectable gain of 0, 10, or 20 dB. The full scale input level is 1 $V_{\text{RMS}}$ .                                     |

| 12   | V <sub>D</sub> | Digital Supply Voltage.                                                                                                                          |

|      |                | Provides the digital supply voltage to the Si3000. Nominally either 5 or 3.3 V and within 0.6 V of $V_{\text{A}}$ .                              |

# Si3000

| Pin# | Pin Name       | Description                                                                                                                                |

|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 13   | V <sub>A</sub> | Analog Supply Voltage.  Provides the analog supply voltage to the Si3000. Nominally either 5 or 3.3 V and within 0.6 V of V <sub>D</sub> . |

| 14   | GND            | Ground. Connects to the system digital ground.                                                                                             |

| 15   | LINEO          | Line Output.  Line level analog output with a 1 V <sub>RMS</sub> full scale output level.                                                  |

| 16   | SPKRL          | Speaker Left Output. Analog output capable of driving a 60 $\Omega$ load.                                                                  |

# 5. Ordering Guide

Table 14. Ordering Guide

| Part Number                                                                | Package | Lead-Free | Temp. Range  |  |  |  |

|----------------------------------------------------------------------------|---------|-----------|--------------|--|--|--|

| Si3000-C-FS                                                                | SOIC-16 | Yes       | 0 to 70 °C   |  |  |  |

| Si3000-C-GS                                                                | SOIC-16 | Yes       | –40 to 85 °C |  |  |  |

| *Note: Add an "R" at the end of the device to denote tape and reel option. |         |           |              |  |  |  |

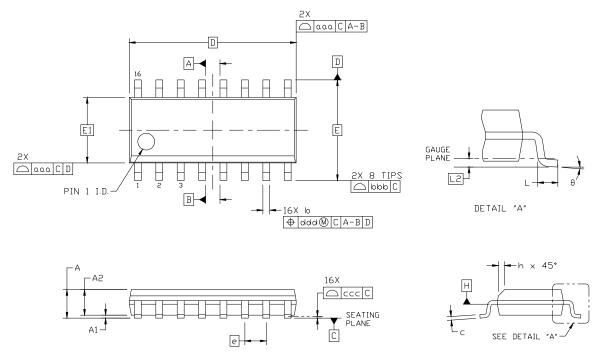

# 6. Package Outline: 16-Pin SOIC

Figure 19 illustrates the package details for the Si3000. Table 15 lists the values for the dimensions shown in the illustration.

Figure 19. 16-Pin Small Outline Integrated Circuit (SOIC) Package

**Table 15. Package Diagram Dimensions**

| Dimension | Min      | Max  |  |

|-----------|----------|------|--|

| A         | _        | 1.75 |  |

| A1        | 0.10     | 0.25 |  |

| A2        | 1.25     |      |  |

| b         | 0.31     | 0.51 |  |

| С         | 0.17     | 0.25 |  |

| D         | 9.90 BSC |      |  |

| E         | 6.00 BSC |      |  |

| E1        | 3.90 BSC |      |  |

| е         | 1.27 BSC |      |  |

| Dimension | Min      | Max  |

|-----------|----------|------|

| L         | 0.40     | 1.27 |

| L2        | 0.25 BSC |      |

| h         | 0.25     | 0.50 |

| θ         | 0°       | 8°   |

| aaa       | 0.10     |      |

| bbb       | 0.20     |      |

| ccc       | 0.10     |      |

| ddd       | 0.25     |      |

|           |          |      |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MS-012, Variation AC.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

SILICON LARS

#### 7. 16-Pin SOIC Land Pattern

Figure illustrates the recommended land pattern for the Si3000 16-pin SOIC. Table 16 lists the values for the dimensions shown in the illustration.

Figure 20. 16-Pin SOIC Land Pattern Diagram

Table 16. 16-Pin MSOP Land Pattern Dimensions

| Dimension | Feature            | mm   |

|-----------|--------------------|------|

| C1        | Pad Column Spacing | 5.40 |

| E         | Pad Row Pitch      | 1.27 |

| X1        | Pad Width          | 0.60 |

| Y1        | Pad Length         | 1.55 |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ASME Y14.5M-1994.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \mu m$  minimum, all the way around the pad.

#### Stencil Design

- 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- 8. The ratio of stencil aperture to land pad size should be 1:1.

#### **Card Assembly**

- **9.** A No-Clean, Type-3 solder paste is recommended.

- 10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

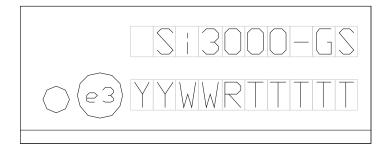

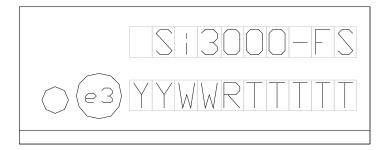

# 8. Package Markings (Top Markings)

Codes for the Si3000-C-GS and Si3000-C-FS top marks are as follows:

- YY = Current Year

- WW = Work Week

- R = Die Revision

- TTTTT = Trace Code

# 8.1. Si3000-C-GS Top Marking

# 8.2. Si3000-C-FS Top Marking

# **DOCUMENT CHANGE LIST**

#### Revision 1.0 to Revision 1.1

- Updated Functional Block Diagram.

- Removed all B-grade references.

- Updated Table 4 (AC Characteristics).

- Updated Figure 14.

- Removed analog loopback feature description.

#### Revision 1.1 to Revision 1.2

- Updated "Features" on page 1 and "5. Ordering Guide" on page 29 to add updated support for leadfree, RoHS-compliant packages.

- Updated document for compatibility with Silicon Laboratories 3rd generation serial interface DAA, the Si3056.

- Updated Figure 13 on page 12.

- Updated MIC and MICBIAS pin number labels.

- Changed standardized minimum input/output attenuation level to –34.5 dB. In some instances, this level was incorrectly specified at –36 dB.

- Updated SOIC package outline drawing and dimensions table.

#### Revision 1.2 to Revision 1.3

- Updated Table 6 on page 7.

- Updated Figure 1 on page 7.

- Updated Figure 2 on page 8.

- Updated Figure 13 on page 12.

- Updated "2.8. Digital Interface" on page 15.

- Updated "2.11. Loopback Operation" on page 18.

- Updated "4. Pin Descriptions: Si3000" on page 27.

#### Revision 1.3 to Revision 1.4

- Added extended temperature Si3000-C-GS to Table 14 ordering guide.

- Added Section 7, 16-Pin SOIC Land Pattern.

- Added Section 8, Package Top Markings.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701

http://www.silabs.com