SCH3227/SCH3226/SCH3224/SCH3222

# LPC IO with 8042 KBC, Reset Generation, HWM and Multiple Serial Ports

### **Product Features**

- General Features

- 3.3 Volt Operation (SIO Block is 5 Volt Tolerant)

- Programmable Wake-up Event (PME) Interface

- PC99, PC2001 Compliant

- ACPI 2.0 Compliant

- Serial IRQ Interface Compatible with Serialized IRQ Support for PCI Systems

- ISA Plug-and-Play Compatible Register Set

- Four Address Options for Power On Configuration Port

- System Management Interrupt (SMI)

- General Purpose I/O pins: see Table 1-1

- GPIOs with VID compatible inputs: see Table 1-1

- Support for power button on PS/2 Keyboard

- Security Key Register (32 byte) for Device Authentication

- Low Pin Count Bus (LPC) Interface

- Supports Bus frequencies of 19MHz to 33MHz

- Watchdog Timer

- Resume and Main Power Good Generator

- Programmable Clock Output to 16 Hz

- · Keyboard Controller

- 8042 Software Compatible

- 8 Bit Microcomputer

- 2k Bytes of Program ROM

- 256 Bytes of Data RAM

- Four Open Drain Outputs Dedicated for Keyboard/ Mouse Interface

- Asynchronous Access to Two Data Registers and One Status Register

- Supports Interrupt and Polling Access

- 8 Bit Counter Timer

- Port 92 Support

- Fast Gate A20 and KRESET Outputs

- Phoenix Keyboard BIOS ROM

- Multiple Serial Ports

- 4 Full Function Serial Ports (SCH3227, SCH3226, SCH3222)

- 2 Full Function Serial Ports (SCH3224)

- Two additional 4-pin Serial Ports available by strap option (SCH3227, SCH3226)

- Two additional 4-pin Serial Ports available always (SCH3224, SCH3222)

- High Speed NS16C550A Compatible UARTs with Send/Receive 16-Byte FIFOs

- Supports 230k, 460k, 921k and 1.5M Baud

- Programmable Baud Rate Generator

- Modem Control Circuitry

- 480 Address and 15 IRQ Options

- Support IRQ Sharing among serial ports

- RS485 Auto Direction Control Mode

- Infrared Port

- Multiprotocol Infrared Interface

- IrDA 1.0 Compliant

- SHARP ASK IR

- 480 Addresses, Up to 15 IRQ

- Multi-Mode<sup>™</sup> Parallel Port with ChiProtect<sup>™</sup>

- Available in SCH3227, SCH3224

- Standard Mode IBM PC/XT®, PC/AT®, and PS/2™ Compatible Bi-directional ParallelPort

- Enhanced Parallel Port (EPP) Compatible EPP 1.7 and EPP 1.9 (IEEE 1284 Compliant)

- IEEE 1284 Compliant Enhanced Capabilities Port (ECP)

- ChiProtect Circuitry for Protection

- 960 Address, Up to 15 IRQ and Four DMA Options

- Hardware Monitor

- Available in SCH3227, SCH3226, SCH3224

- Monitor Power supplies (+2.5V, +5V, +12V, Vccp (processor voltage), VCC, Vbat and Vtr.

- Remote Thermal Diode Sensing for Two External Temperature Measurements accurate to 1.5°C

- Internal Ambient Temperature Measurement

- Limit Comparison of all Monitored Values

- Programmable Automatic FAN control based on temperature

- nHWM\_INT Pin for out-of-limit Temperature or Voltage Indication

- Thermtrip signal for over temperature indication

- IDE Reset Output and 3 PCI Reset Buffers with Software Control Capability (SCH3227 and SCH3226 by strap option)

- Power Button Control and AC Power Failure Recovery (SCH3227 and SCH3226 by strap option)

- Temperature Ranges Available

- Industrial (+85°C to -40°C)

- Commercial (+70°C to 0°C)

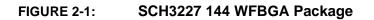

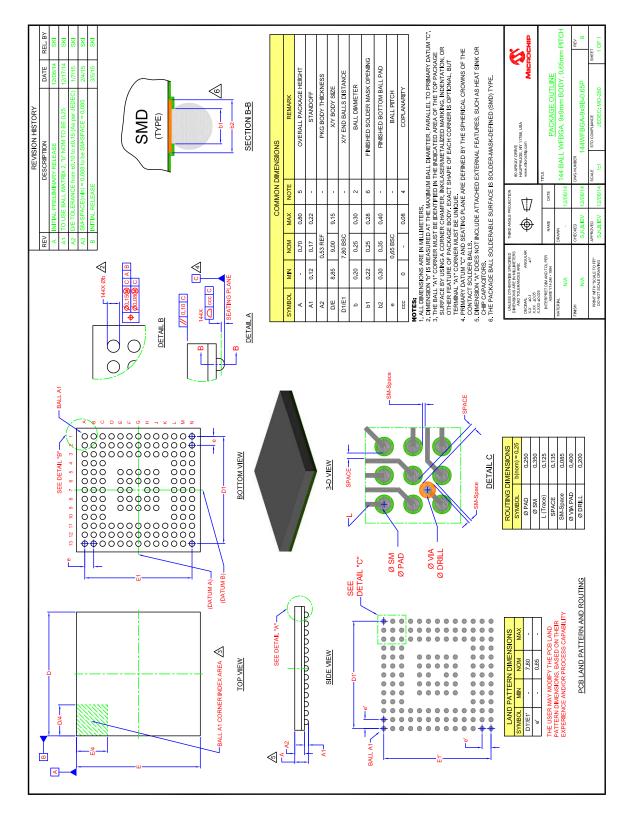

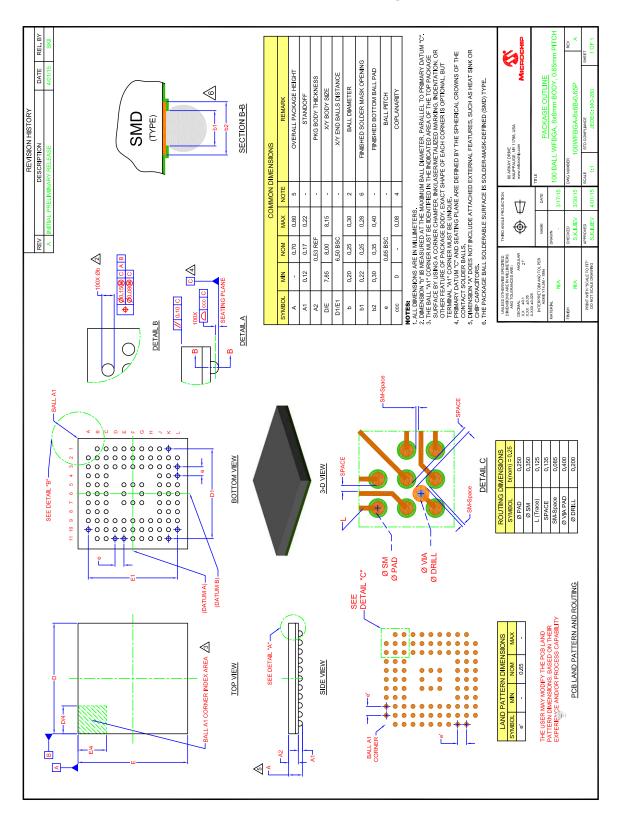

- WFBGA RoHS Compliant Packages

- 144-ball (SCH3227)

- 100-ball (SCH3226, SCH3224)

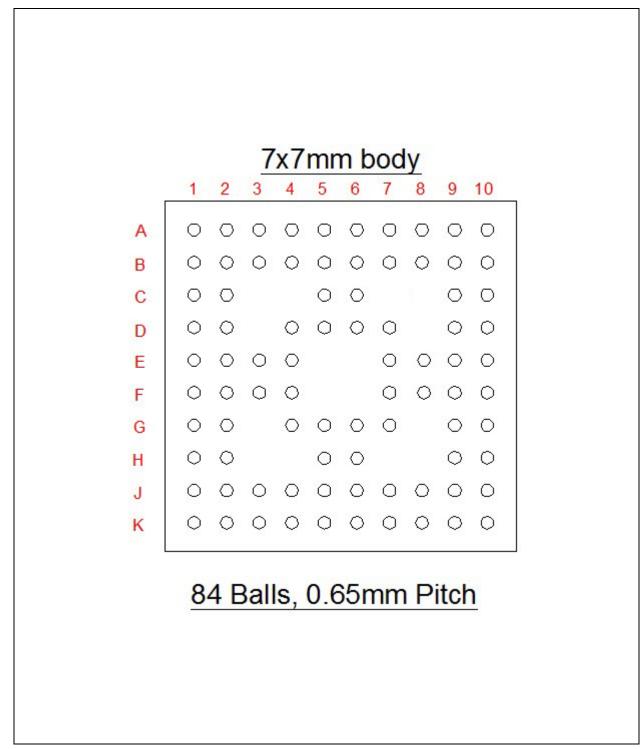

- 84-ball (SCH3222)

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 1.0 INTRODUCTION

### 1.1 General Description

The SCH3227/SCH3226/SCH3224/SCH3222 Product Family is a 3.3V (Super I/O Block is 5V tolerant) PC99/PC2001 compliant Super I/O controller with an LPC interface. The Product Family also includes Hardware Monitoring capabilities, enhanced Security features, Power Control logic and Motherboard Glue logic.

See Table 1-1 on page 4 for features available per family member.

The Product Family is ACPI 1.0/2.0 compatible and therefore supports multiple low power-down modes. It incorporates sophisticated power control circuitry (PCC), which includes support for keyboard.

The Product Family supports the ISA Plug-and-Play Standard register set (Version 1.0a). The I/O Address, hardware IRQ and DMA Channel of each Logical Device may be reprogrammed through the internal configuration registers. There are up to 480 I/O address location options (960 for the Parallel Port), a Serialized IRQ interface, and a choice of three Legacy DMA channel assignments.

Super I/O functionality includes an 8042 based keyboard and mouse controller, one IrDA 1.0 infrared port and multiple serial ports. Some family members (Table 1-1) also provide an IEEE 1284 EPP/ECP compatible parallel port.

The serial ports are fully functional NS16550 compatible UARTs that support data rates up to 1.5 Mbps. There are both 8-pin Serial Ports and 4-pin Serial Ports. The reduced-pin serial ports have selectable input and output controls. The Serial Ports contain programmable direction control, which will automatically drive nRTS when the Output Buffer is loaded, then drive nRTS when the Output Buffer is empty.

Hardware Monitoring capability has programmable, automatic fan control. Three fan tachometer inputs and three pulse width modulator (PWM) fan control outputs are available.

Hardware Monitoring capability also includes temperature, voltage and fan speed monitoring. It has the ability to alert the system to out-of-limit conditions and automatically control the speeds of multiple fans in response. There are four analog inputs for monitoring external voltages of +5V, +2.5V, +12V and Vccp (core processor voltage), as well as internal monitoring of the device's internal VCC, VTR, and VBAT power supplies. Hardware Monitoring includes support for monitoring two external temperatures via thermal diode inputs and an internal sensor for measuring local ambient temperature. The nHWM\_INT pin is implemented to indicate out-of-limit temperature, voltage, and fan speed conditions. Hardware Monitoring features are accessible via the LPC bus, and the same interrupt event reported on the nHWM\_INT pin also creates PME wakeup events. A separate THERMTRIP output is available, which generates a pulse output on a programmed over-temperature condition. This can be used to generate a reset or shutdown indication to the system.

The Motherboard Glue logic includes various power management and system logic including generation of nRSMRST, a programmable Clock output, and reset generation. The reset generation includes a watchdog timer which can be used to generate a reset pulse. The width of this pulse is selectable via an external strapping option.

System related functionality, which offers flexibility to the system designer, includes General Purpose I/O control functions, and control of two LED's.

<sup>© 2016</sup> Microchip Technology Inc.

| Function                           | SCH3227                                      | SCH3226                                      | SCH3224  | SCH3222 |

|------------------------------------|----------------------------------------------|----------------------------------------------|----------|---------|

| LPC Bus Interface                  | YES                                          | YES                                          | YES      | YES     |

| PnP Config w/<br>4 Port Addresses  | YES                                          | YES                                          | YES      | YES     |

| Serial IRQ and SMI                 | YES                                          | YES                                          | YES      | YES     |

| Keyboard Controller                | YES                                          | YES                                          | YES      | YES     |

| Watchdog Timer                     | YES                                          | YES                                          | YES      | YES     |

| Parallel Port                      | YES                                          | NO                                           | YES      | NO      |

| Reset Generator                    | YES                                          | YES                                          | YES      | YES     |

| Serial Ports, Full                 | 4                                            | 4                                            | 2        | 4       |

| Additional Serial<br>Ports, 4-Pin  | 2 avail.<br>(by strap option)                | 2 avail.<br>(by strap option)                | 2        | 2       |

| Infrared Port                      | YES                                          | YES                                          | YES      | YES     |

| Programmable Clock<br>Output       | YES                                          | YES                                          | YES      | YES     |

| IDE / PCI Reset<br>Outputs         | By strap option (vs.<br>4-pin Serial Ports). | By strap option (vs.<br>4-pin Serial Ports). | NO       | NO      |

| Power Button / AC<br>Fail Support  | By strap option (vs.<br>4-pin Serial Ports). | By strap option (vs.<br>4-pin Serial Ports). | NO       | NO      |

| GPIOs                              | 40                                           | 40                                           | 24       | 23      |

| GPIO with VID<br>Compatible Inputs | 6                                            | 6                                            | 0        | 6       |

| Hardware Monitor                   | YES                                          | YES                                          | YES      | NO      |

| WFBGA Package                      | 144-ball                                     | 100-ball                                     | 100-ball | 84-ball |

TABLE 1-1: DEVICE SPECIFIC SUMMARY

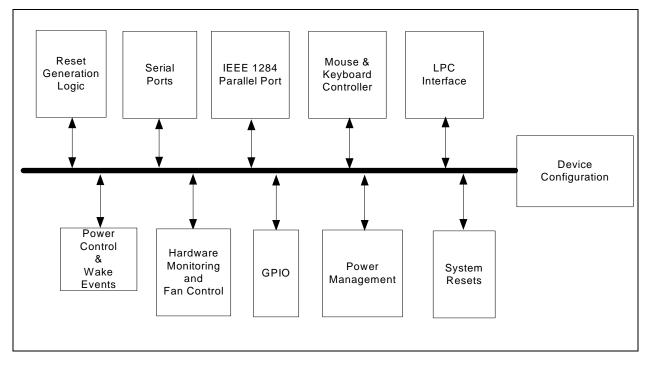

An internal block diagram of the SCH3227/SCH3226/SCH3224/SCH3222 Product Family is shown in Figure 1-1.

FIGURE 1-1: ARCHITECTURAL OVERVIEW

<sup>© 2016</sup> Microchip Technology Inc.

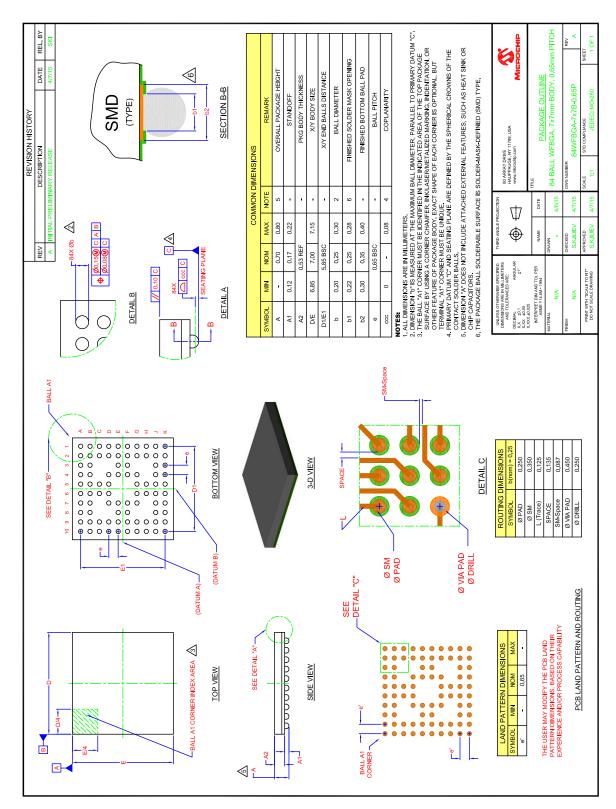

### 2.0 PACKAGE OUTLINES

Downloaded from Arrow.com.

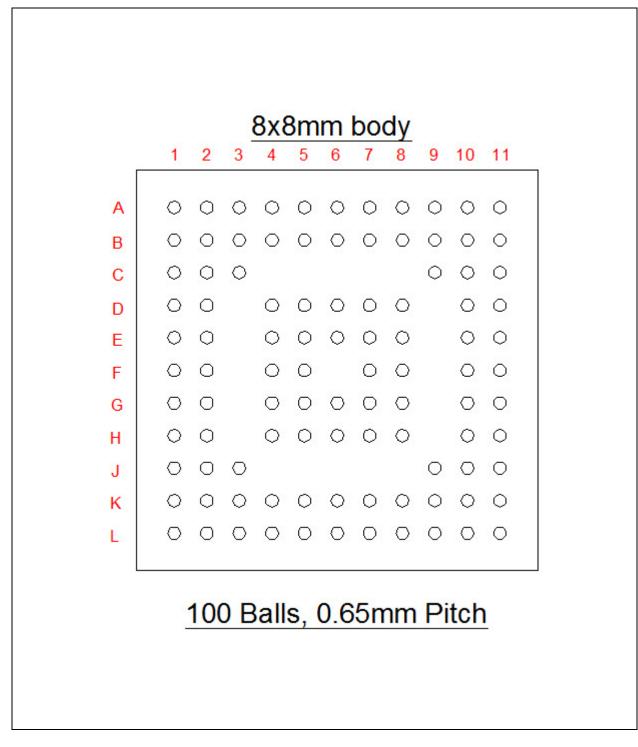

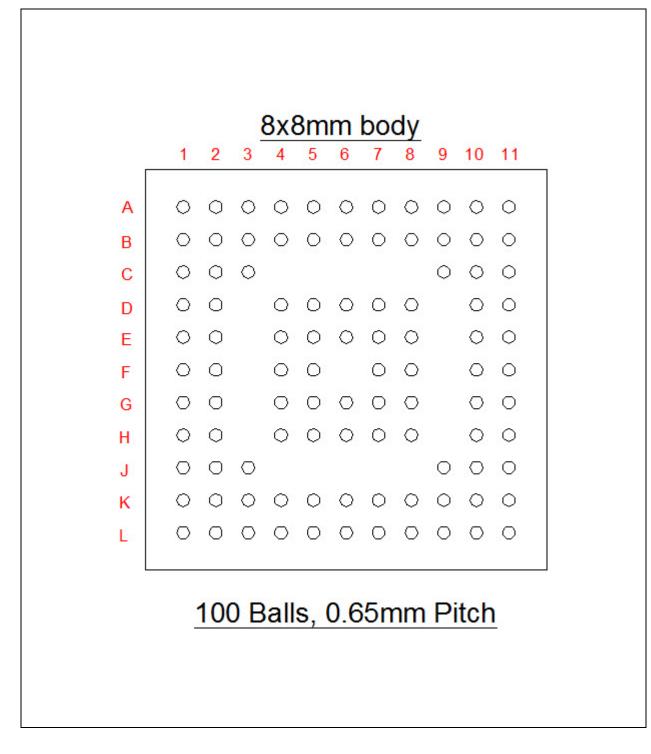

### FIGURE 2-2: SCH3226, SCH3224 100 WFBGA Package

# SCH3227/SCH3226/SCH3224/SCH3222

### FIGURE 2-3: SCH3222 84 WFBGA Package

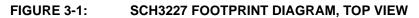

### 3.0 BALL LAYOUTS

### 3.1 SCH3227 Ball Layout Summary

Highlighted rows indicate balls whose function depends on the STRAPOPT strap input.

| BALL# | FUNCTION: STRAPOPT=1          | FUNCTION: STRAPOPT=0          |

|-------|-------------------------------|-------------------------------|

| K13   | STRAPOPT (=VTR <sup>a</sup> ) | STRAPOPT (=VSS <sup>a</sup> ) |

| M4    | RESERVED=VTR <sup>b</sup>     | RESERVED=VTR <sup>b</sup>     |

| C3    | +12V_IN                       | +12V_IN                       |

| D3    | +5V_IN                        | +5V_IN                        |

| E6    | GP40                          | GP40                          |

| E3    | VTR                           | VTR                           |

| E5    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| F8    | TEST=VSS <sup>c</sup>         | TEST=VSS <sup>c</sup>         |

| F7    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| F3    | VSS                           | VSS                           |

| F6    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| F5    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| G8    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| G6    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| H8    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| G5    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| H7    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| H6    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| H5    | RESERVED=VSS <sup>c</sup>     | RESERVED=VSS <sup>c</sup>     |

| D2    | CLOCKI                        | CLOCKI                        |

| E2    | LAD0                          | LADO                          |

| D1    | LAD1                          | LAD1                          |

| E1    | LAD2                          | LAD2                          |

| F2    | LAD3                          | LAD3                          |

| F1    | LFRAME#                       | LFRAME#                       |

| G2    | LDRQ#                         | LDRQ#                         |

| H1    | PCI_RESET#                    | PCI_RESET#                    |

| G1    | PCI_CLK                       | PCI_CLK                       |

| H2    | SER_IRQ                       | SER_IRQ                       |

| H3    | VSS                           | VSS                           |

| J3    | VCC                           | VCC                           |

| J1    | GP44 / TXD6                   | nIDE_RSTDRV / GP44            |

| J2    | GP45 / RXD6                   | nPCIRST1 / GP45               |

| K3    | GP46 / nSCIN6                 | nPCIRST2 / GP46               |

| L3    | GP47 / nSCOUT6                | nPCIRST3 / GP47               |

| K1    | AVSS                          | AVSS                          |

| L1    | VBAT                          | VBAT                          |

| K2    | GP27 / nIO_SMI / P17          | GP27 / nIO_SMI / P17          |

| L2    | KDAT / GP21                   | KDAT / GP21                   |

| M1    | KCLK / GP22                   | KCLK / GP22                   |

| M2    | MDAT / GP32                   | MDAT / GP32                   |

| N1    | MCLK / GP33                   | MCLK / GP33                   |

| M3    | GP36 / nKBDRST                | GP36 / nKBDRST                |

#### TABLE 3-1: SCH3227 SUMMARIES BY STRAP OPTION

| BALL# | FUNCTION: STRAPOPT=1  | FUNCTION: STRAPOPT=0  |  |

|-------|-----------------------|-----------------------|--|

| N2    | GP37 / A20M           | GP37 / A20M           |  |

| L5    | VSS                   | VSS                   |  |

| N3    | VTR                   | VTR                   |  |

| N4    | nINIT                 | nINIT                 |  |

| M5    | nSLCTIN               | nSLCTIN               |  |

| L6    | PD0                   | PD0                   |  |

| N5    | PD1                   | PD1                   |  |

| M6    | PD2                   | PD2                   |  |

| L7    | PD3                   | PD3                   |  |

| N6    | PD4                   | PD4                   |  |

| M7    | PD5                   | PD5                   |  |

| N7    | PD6                   | PD6                   |  |

| L8    | PD7                   | PD7                   |  |

| L9    | VSS                   | VSS                   |  |

| M8    | SLCT                  | SLCT                  |  |

| N8    | PE                    | PE                    |  |

| N9    | BUSY                  | BUSY                  |  |

| M9    | nACK                  | nACK                  |  |

| N10   | nERROR                | nERROR                |  |

| M10   | nALF                  | nALF                  |  |

| N11   | nSTROBE               | nSTROBE               |  |

| M11   | nRI1                  | nRI1                  |  |

| N12   | nDCD1                 | nDCD1                 |  |

| L11   | RXD1                  | RXD1                  |  |

| M12   | TXD1 / SIOXNOROUT     | TXD1 / SIOXNOROUT     |  |

| N13   | nDSR1                 | nDSR1                 |  |

| L12   | nRTS1 / SYSOPT0       | nRTS1 / SYSOPT0       |  |

| M13   | nCTS1                 | nCTS1                 |  |

| J12   | nDTR1 / SYSOPT1       | nDTR1 / SYSOPT1       |  |

| K12   | GP50 / nRI2           | GP50 / nRI2           |  |

| L13   | VTR                   | VTR                   |  |

| J13   | VSS                   | VSS                   |  |

| H11   | GP51 / nDCD2          | GP51 / nDCD2          |  |

| H12   | GP52 / RXD2(IRRX2)    | GP52 / RXD2(IRRX2)    |  |

| H13   | GP53 / TXD2(IRTX2)    | GP53 / TXD2(IRTX2)    |  |

| G13   | GP54 / nDSR2          | GP54 / nDSR2          |  |

| G12   | GP55 / nRTS2 / RESGEN | GP55 / nRTS2 / RESGEN |  |

| G11   | GP56 / nCTS2          | GP56 / nCTS2          |  |

| F13   | GP57 / nDTR2          | GP57 / nDTR2          |  |

| F12   | RXD5                  | PB_OUT#               |  |

| F11   | TXD5                  | PS_ON#                |  |

| E13   | nSCOUT5               | PB_IN#                |  |

| E12   | nSCIN5                | SLP_SX#               |  |

| D13   | GP10 / RXD3           | GP10 / RXD3           |  |

#### TABLE 3-1: SCH3227 SUMMARIES BY STRAP OPTION (CONTINUED)

<sup>© 2016</sup> Microchip Technology Inc.

| TABLE 3-1: | SCH3227 SUMMARIES BY STRAP OPTION ( | CONTINUED) |

|------------|-------------------------------------|------------|

|------------|-------------------------------------|------------|

| BALL# | FUNCTION: STRAPOPT=1                               | FUNCTION: STRAPOPT=0                 |

|-------|----------------------------------------------------|--------------------------------------|

| D12   | GP11 / TXD3                                        | GP11 / TXD3                          |

| E11   | GP14 / nDSR3                                       | GP14 / nDSR3                         |

| C13   | GP17 / nRTS3                                       | GP17 / nRTS3                         |

| B13   | GP16 / nCTS3                                       | GP16 / nCTS3                         |

| C12   | GP42 / nIO_PME                                     | GP42 / nIO_PME                       |

| D11   | VTR                                                | VTR                                  |

| A13   | GP15 / nDTR3                                       | GP15 / nDTR3                         |

| B12   | GP61 / nLED2 / CLKO                                | GP61 / nLED2 / CLKO                  |

| C11   | GP60 / nLED1 / WDT                                 | GP60 / nLED1 / WDT                   |

| A12   | GP13 / nRI3                                        | GP13 / nRI3                          |

| B11   | GP12 / nDCD3                                       | GP12 / nDCD3                         |

| A11   | GP31 / nRI4                                        | GP31 / nRI4                          |

| C10   | GP63 / nDCD4                                       | GP63 / nDCD4                         |

| B10   | CLKI32                                             | CLKI32                               |

| A10   | nRSMRST                                            | nRSMRST                              |

| B9    | VSS                                                | VSS                                  |

| C9    | GP64 / RXD4                                        | GP64 / RXD4                          |

| A9    | GP65 / TXD4                                        | GP65 / TXD4                          |

| A8    | GP66 / nDSR4                                       | GP66 / nDSR4                         |

| B8    | GP67 / nRTS4                                       | GP67 / nRTS4                         |

| C8    | GP62 / nCTS4                                       | GP62 / nCTS4                         |

| A7    | GP34 / nDTR4                                       | GP34 / nDTR4                         |

| B7    | PWRGD_OUT                                          | PWRGD_OUT                            |

| A6    | PWRGD_PS                                           | PWRGD_PS                             |

| C7    | nFPRST / GP30                                      | nFPRST / GP30                        |

| E8    | VTR                                                | VTR                                  |

| E7    | VSS                                                | VSS                                  |

| B6    | nTHERMTRIP                                         | nTHERMTRIP                           |

| A5    | nHWM_INT                                           | nHWM_INT                             |

| C6    | PWM3                                               | PWM3                                 |

| B5    | PWM2                                               | PWM2                                 |

| A4    | PWM1                                               | PWM1                                 |

| B4    | FANTACH3                                           | FANTACH3                             |

| C5    | FANTACH2                                           | FANTACH2                             |

| C4    | FANTACH1                                           | FANTACH1                             |

| A3    | HVSS                                               | HVSS                                 |

| B3    | HVTR                                               | HVTR                                 |

| A2    | REMOTE2-                                           | REMOTE2-                             |

| A1    | REMOTE2+                                           | REMOTE2+                             |

| B1    | REMOTE1-                                           | REMOTE1-                             |

| C1    | REMOTE1+                                           | REMOTE1+                             |

| C2    | VCCP_IN                                            | VCCP_IN                              |

| B2    | +2.5V_IN                                           | +2.5V_IN                             |

|       | RESERVED=N/C <sup>d</sup> : E9, F9, G9, H9, J5, J6 | 6, J7, J8, J9, G3, J11, K11, L4, L10 |

a. The STRAPOPT connection defines pin functions for this package, and also the contents of the Device ID register at Plug&Play Index 0x20:

When connected to VTR, the table column STRAPOPT=1 applies, and Device ID = 0x7F.

When connected to VSS, the table column STRAPOPT=0 applies, and Device ID = 0x7D.

b. For correct operation, this lead must always be connected to VTR.

- c. For correct operation and minimal current consumption, this lead must always be connected to VSS.

- d. Make No Connection to these leads.

<sup>© 2016</sup> Microchip Technology Inc.

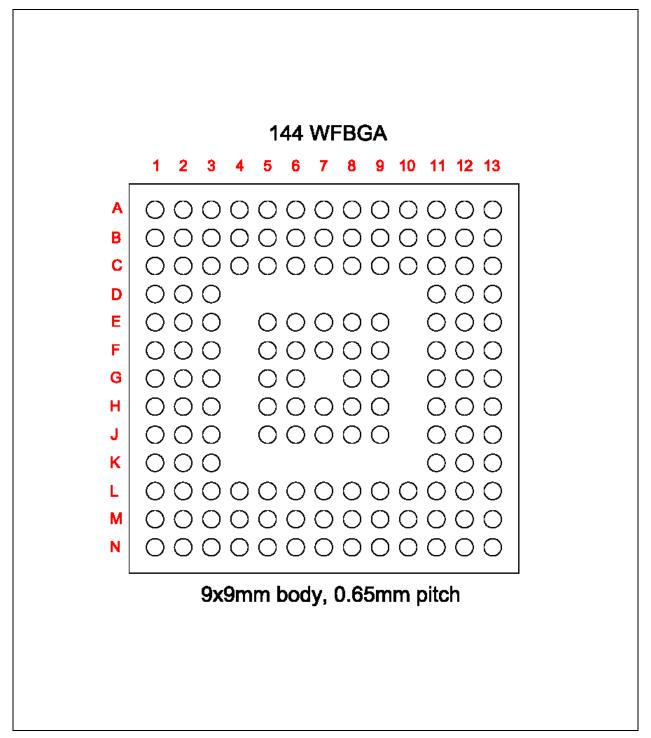

### 3.2 SCH3226 Ball Layout Summary

Highlighted rows indicate balls whose function depends on the STRAPOPT strap input.

| BALL# | FUNCTION: STRAPOPT=1          | FUNCTION: STRAPOPT=0          |

|-------|-------------------------------|-------------------------------|

| L8    | STRAPOPT (=VTR <sup>a</sup> ) | STRAPOPT (=VSS <sup>a</sup> ) |

| C2    | +12V_IN                       | +12V_IN                       |

| C1    | +5V_IN                        | +5V_IN                        |

| C3    | GP40 / DRVDEN0(out)           | GP40 / DRVDEN0(out)           |

| D3    | VTR                           | VTR                           |

| G5    | TEST                          | TEST                          |

| D2    | VSS                           | VSS                           |

| E3    | CLOCKI                        | CLOCKI                        |

| F3    | LAD0                          | LAD0                          |

| E2    | LAD1                          | LAD1                          |

| D1    | LAD2                          | LAD2                          |

| F2    | LAD3                          | LAD3                          |

| E1    | LFRAME#                       | LFRAME#                       |

| G3    | LDRQ#                         | LDRQ#                         |

| F1    | PCI_RESET#                    | PCI_RESET#                    |

| G1    | PCI_CLK                       | PCI_CLK                       |

| G2    | SER_IRQ                       | SER_IRQ                       |

| H1    | VSS                           | VSS                           |

| H2    | VCC                           | VCC                           |

| H3    | GP44 / TXD6                   | nIDE_RSTDRV / GP44            |

| J2    | GP45 / RXD6                   | nPCIRST1 / GP45               |

| K2    | GP46 / nSCIN6                 | nPCIRST2 / GP46               |

| J3    | GP47 / nSCOUT6                | nPCIRST3 / GP47               |

| J1    | AVSS                          | AVSS                          |

| K1    | VBAT                          | VBAT                          |

| K3    | GP27 / nIO_SMI / P17          | GP27 / nIO_SMI / P17          |

| J4    | KDAT / GP21                   | KDAT / GP21                   |

| L2    | KCLK / GP22                   | KCLK / GP22                   |

| L3    | MDAT / GP32                   | MDAT / GP32                   |

| K4    | MCLK / GP33                   | MCLK / GP33                   |

| L4    | GP36 / nKBDRST                | GP36 / nKBDRST                |

| L5    | GP37 / A20M                   | GP37 / A20M                   |

| G7    | VSS                           | VSS                           |

| G6    | VTR                           | VTR                           |

| K7    | nRl1                          | nRI1                          |

| L6    | nDCD1                         | nDCD1                         |

| K8    | RXD1                          | RXD1                          |

| J8    | TXD1 / SIOXNOROUT             | TXD1 / SIOXNOROUT             |

| K6    | nDSR1                         | nDSR1                         |

| K5    | nRTS1 / SYSOPT0               | nRTS1 / SYSOPT0               |

| J7    | nCTS1                         | nCTS1                         |

| J6    | nDTR1 / SYSOPT1               | nDTR1 / SYSOPT1               |

| J5    | GP50 / nRI2                   | GP50 / nRI2                   |

TABLE 3-2: SCH3226 SUMMARIES BY STRAP OPTION

© 2016 Microchip Technology Inc.

| BALL# | FUNCTION: STRAPOPT=1  | FUNCTION: STRAPOPT=0  |

|-------|-----------------------|-----------------------|

| L9    | VTR                   | VTR                   |

| L7    | VSS                   | VSS                   |

| K9    | GP51 / nDCD2          | GP51 / nDCD2          |

| J9    | GP52 / RXD2(IRRX2)    | GP52 / RXD2(IRRX2)    |

| H9    | GP53 / TXD2(IRTX2)    | GP53 / TXD2(IRTX2)    |

| G9    | GP54 / nDSR2          | GP54 / nDSR2          |

| L10   | GP55 / nRTS2 / RESGEN | GP55 / nRTS2 / RESGEN |

| K10   | GP56 / nCTS2          | GP56 / nCTS2          |

| J10   | GP57 / nDTR2          | GP57 / nDTR2          |

| H10   | RXD5                  | PB_OUT#               |

| K11   | TXD5                  | PS_ON#                |

| J11   | nSCOUT5               | PB_IN#                |

| H11   | nSCIN5                | SLP_SX#               |

| F9    | GP10 / RXD3           | GP10 / RXD3           |

| G10   | GP11 / TXD3           | GP11 / TXD3           |

| E9    | GP14 / nDSR3          | GP14 / nDSR3          |

| F10   | GP17 / nRTS3          | GP17 / nRTS3          |

| G11   | GP16 / nCTS3          | GP16 / nCTS3          |

| F11   | GP42 / nIO_PME        | GP42 / nIO_PME        |

| E10   | VTR                   | VTR                   |

| E11   | GP15 / nDTR3          | GP15 / nDTR3          |

| D9    | GP61 / nLED2 / CLKO   | GP61 / nLED2 / CLKO   |

| D10   | GP60 / nLED1 / WDT    | GP60 / nLED1 / WDT    |

| D11   | GP13 / nRI3           | GP13 / nRI3           |

| C11   | GP12 / nDCD3          | GP12 / nDCD3          |

| C10   | GP31 / nRI4           | GP31 / nRI4           |

| C9    | GP63 / nDCD4          | GP63 / nDCD4          |

| B11   | CLKI32                | CLKI32                |

| B10   | nRSMRST               | nRSMRST               |

| A10   | VSS                   | VSS                   |

| C8    | GP64 / RXD4           | GP64 / RXD4           |

| B9    | GP65 / TXD4           | GP65 / TXD4           |

| A9    | GP66 / nDSR4          | GP66 / nDSR4          |

| B8    | GP67 / nRTS4          | GP67 / nRTS4          |

| A8    | GP62 / nCTS4          | GP62 / nCTS4          |

| C7    | GP34 / nDTR4          | GP34 / nDTR4          |

| A7    | PWRGD_OUT             | PWRGD_OUT             |

| B7    | PWRGD_PS              | PWRGD_PS              |

| E7    | nFPRST / GP30         | nFPRST / GP30         |

| F7    | VTR                   | VTR                   |

| C6    | VSS                   | VSS                   |

| B6    | nTHERMTRIP            | nTHERMTRIP            |

| E6    | nHWM_INT              | nHWM_INT              |

| A6    | PWM3                  | PWM3                  |

### TABLE 3-2: SCH3226 SUMMARIES BY STRAP OPTION

| FUNCTION: STRAPOPT=1 | FUNCTION: STRAPOPT=0                                                                                |                                                                                                                                                                                       |

|----------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM2                 | PWM2                                                                                                |                                                                                                                                                                                       |

| PWM1                 | PWM1                                                                                                |                                                                                                                                                                                       |

| FANTACH3             | FANTACH3                                                                                            |                                                                                                                                                                                       |

| FANTACH2             | FANTACH2                                                                                            |                                                                                                                                                                                       |

| FANTACH1             | FANTACH1                                                                                            |                                                                                                                                                                                       |

| HVSS                 | HVSS                                                                                                |                                                                                                                                                                                       |

| HVTR                 | HVTR                                                                                                |                                                                                                                                                                                       |

| REMOTE2-             | REMOTE2-                                                                                            |                                                                                                                                                                                       |

| REMOTE2+             | REMOTE2+                                                                                            |                                                                                                                                                                                       |

| REMOTE1-             | REMOTE1-                                                                                            |                                                                                                                                                                                       |

| REMOTE1+             | REMOTE1+                                                                                            |                                                                                                                                                                                       |

| VCCP_IN              | VCCP_IN                                                                                             |                                                                                                                                                                                       |

| +2.5V_IN             | +2.5V_IN                                                                                            |                                                                                                                                                                                       |

|                      | FUNCTION: STRAPOPT=1PWM2PWM1FANTACH3FANTACH2FANTACH1HVSSHVTRREMOTE2-REMOTE2+REMOTE1-REMOTE1+VCCP_IN | FUNCTION: STRAPOPT=1FUNCTION: STRAPOPT=0PWM2PWM2PWM1PWM1FANTACH3FANTACH3FANTACH2FANTACH2FANTACH1FANTACH1HVSSHVSSHVTRHVTRREMOTE2-REMOTE2-REMOTE1-REMOTE1-REMOTE1+VCCP_INVCCP_INVCCP_IN |

#### TABLE 3-2: SCH3226 SUMMARIES BY STRAP OPTION

a. The STRAPOPT connection defines pin functions for this package, and also the contents of the Device ID register at Plug&Play Index 0x20:

When connected to VTR, the table column STRAPOPT=1 applies, and Device ID = 0x7F.

and Device ID = 0x/F.

When connected to VSS, the table column STRAPOPT=0 applies, and Device ID = 0x7D.

<sup>© 2016</sup> Microchip Technology Inc.

### 3.3 SCH3224 Ball Layout Summary

| BALL# | FUNCTION <sup>a</sup>              |

|-------|------------------------------------|

| C3    | +12V_IN                            |

| C2    | +5V_IN                             |

| D3    | VTR                                |

| E6    | TEST                               |

| D2    | VSS                                |

| F2    | CLOCKI                             |

| E2    | LADO                               |

| D1    | LAD1                               |

| E3    | LAD2                               |

| F3    | LAD3                               |

| E1    | LFRAME#                            |

| G3    | LDRQ#                              |

| F1    | PCI_RESET#                         |

| G1    | PCI_CLK                            |

| G2    | SER_IRQ                            |

| H1    | VSS                                |

| H2    | VCC                                |

| H3    | GP44 / TXD6                        |

| F5    | GP45 / RXD6                        |

| E5    | GP46 / nSCIN6                      |

| J2    | GP47 / nSCOUT6                     |

| J1    | AVSS                               |

| K1    | VBAT                               |

| J3    | GP27 / nIO_SMI / P17               |

| J4    | KDAT / GP21                        |

| K3    | KCLK / GP22                        |

| K2    | MDAT / GP32                        |

| L2    | MCLK / GP33                        |

| L3    | GP36 / nKBDRST                     |

| J5    | GP37 / A20M                        |

| K4    | RESERVED=N/C (Make no connection.) |

| G6    | VTR                                |

| K5    | nINIT                              |

| G5    | nSLCTIN                            |

| J6    | PD0                                |

| L5    | PD1                                |

| K6    | PD2                                |

| L4    | PD3                                |

| L6    | PD4                                |

| C10   | PD5                                |

| K7    | PD6                                |

| J7    | PD7                                |

| G7    | VSS                                |

### TABLE 3-3: SCH3224 SUMMARY

© 2016 Microchip Technology Inc.

| TABLE 3 | · · · · ·             |

|---------|-----------------------|

| BALL#   | FUNCTION <sup>a</sup> |

| C7      | SLCT                  |

| E7      | PE                    |

| L8      | BUSY                  |

| K8      | nACK                  |

| J8      | nERROR                |

| G11     | nALF                  |

| K9      | nSTROBE               |

| L10     | nRI1                  |

| J9      | nDCD1                 |

| K10     | RXD1                  |

| K11     | TXD1 / SIOXNOROUT     |

| J10     | nDSR1                 |

| J11     | nRTS1 / SYSOPT0       |

| H9      | nCTS1                 |

| H10     | nDTR1 / SYSOPT1       |

| H11     | GP50 / nRI2           |

| L9      | VTR                   |

| L7      | VSS                   |

| G9      | GP51 / nDCD2          |

| G10     | GP52 / RXD2(IRRX2)    |

| F11     | GP53 / TXD2(IRTX2)    |

| F10     | GP54 / nDSR2          |

| E11     | GP55 / nRTS2 / RESGEN |

| D11     | GP56 / nCTS2          |

| F9      | GP57 / nDTR2          |

| D10     | RXD5                  |

| B11     | TXD5                  |

| E9      | nSCOUT5               |

| D9      | nSCIN5                |

| C11     | GP42 / nIO_PME        |

| E10     | VTR                   |

| B10     | GP61 / nLED2 / CLKO   |

| C9      | GP60 / nLED1 / WDT    |

| C1      | CLKI32                |

| B9      | nRSMRST               |

| A10     | VSS                   |

| C8      | PWRGD_OUT             |

| A9      | PWRGD_PS              |

| B8      | nFPRST / GP30         |

| F7      | VTR                   |

| C6      | VSS                   |

| B7      | nTHERMTRIP            |

| A8      | nHWM_INT              |

| A7      | PWM3                  |

### TABLE 3-3: SCH3224 SUMMARY (CONTINUED)

| TABLE 3-3: SCH3224 SUMMARY (CONTINUED |

|---------------------------------------|

|---------------------------------------|

| BALL# | FUNCTION <sup>a</sup> |

|-------|-----------------------|

| B6    | PWM2                  |

| A6    | PWM1                  |

| A5    | FANTACH3              |

| B5    | FANTACH2              |

| C5    | FANTACH1              |

| B4    | HVSS                  |

| C4    | HVTR                  |

| A4    | REMOTE2-              |

| A3    | REMOTE2+              |

| A2    | REMOTE1-              |

| B1    | REMOTE1+              |

| B3    | VCCP_IN               |

| B2    | +2.5V_IN              |

a. Device ID register at Plug&Play Index 0x20 holds 0x7F.

<sup>© 2016</sup> Microchip Technology Inc.

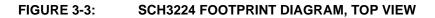

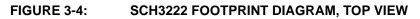

### 3.4 SCH3222 Ball Layout Summary

| TABLE 3-4: | SCH3222 SUMMARY       |  |  |  |  |

|------------|-----------------------|--|--|--|--|

| BALL#      | FUNCTION <sup>a</sup> |  |  |  |  |

| B1         | +5V_IN                |  |  |  |  |

| A1         | GP40                  |  |  |  |  |

| C1         | VTR                   |  |  |  |  |

| A2         | TEST                  |  |  |  |  |

| D1         | VSS                   |  |  |  |  |

| E1         | CLOCKI                |  |  |  |  |

| B2         | LAD0                  |  |  |  |  |

| C2         | LAD1                  |  |  |  |  |

| B3         | LAD2                  |  |  |  |  |

| D2         | LAD3                  |  |  |  |  |

| F1         | LFRAME#               |  |  |  |  |

| F2         | PCI_RESET#            |  |  |  |  |

| F3         | PCI_CLK               |  |  |  |  |

| E3         | SER_IRQ               |  |  |  |  |

| G2         | VSS                   |  |  |  |  |

| G1         | VCC                   |  |  |  |  |

| H1         | GP44 / TXD6           |  |  |  |  |

| J1         | GP45 / RXD6           |  |  |  |  |

| J2         | GP46 / nSCIN6         |  |  |  |  |

| K1         | GP47 / nSCOUT6        |  |  |  |  |

| K2         | AVSS                  |  |  |  |  |

| H2         | VBAT                  |  |  |  |  |

| K3         | GP27 / nIO_SMI / P17  |  |  |  |  |

| J3         | KDAT / GP21           |  |  |  |  |

| J4         | KCLK / GP22           |  |  |  |  |

| F4         | MDAT / GP32           |  |  |  |  |

| E4         | MCLK / GP33           |  |  |  |  |

| J5         | GP36 / nKBDRST        |  |  |  |  |

| K4         | GP37 / A20M           |  |  |  |  |

| K6         | VSS                   |  |  |  |  |

| K5         | VTR                   |  |  |  |  |

| K7         | VSS                   |  |  |  |  |

| K8         | nRI1                  |  |  |  |  |

| H5         | nDCD1                 |  |  |  |  |

| K10        | RXD1                  |  |  |  |  |

| J10        | TXD1 / SIOXNOROUT     |  |  |  |  |

| K9         | nDSR1                 |  |  |  |  |

| J9         | nRTS1 / SYSOPT0       |  |  |  |  |

| H10        | nCTS1                 |  |  |  |  |

| H9         | nDTR1 / SYSOPT1       |  |  |  |  |

| J8         | GP50 / nRI2           |  |  |  |  |

| G9         | VTR                   |  |  |  |  |

| J7         | VSS                   |  |  |  |  |

| G5         | GP51 / nDCD2          |  |  |  |  |

TABLE 3-4. SCH3222 SUMMARY

$\ensuremath{\textcircled{}^{\odot}}$  2016 Microchip Technology Inc.

|       | ABLE 3-4: SCH3222 SUMMARY (CONTINUED) |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|

| BALL# | <b>FUNCTION</b> <sup>a</sup>          |  |  |  |  |

| G10   | GP52 / RXD2(IRRX2)                    |  |  |  |  |

| F10   | GP53 / TXD2(IRTX2)                    |  |  |  |  |

| G7    | GP54 / nDSR2                          |  |  |  |  |

| J6    | GP55 / nRTS2 / RESGEN                 |  |  |  |  |

| H6    | GP56 / nCTS2                          |  |  |  |  |

| F9    | GP57 / nDTR2                          |  |  |  |  |

| F8    | RXD5                                  |  |  |  |  |

| F7    | TXD5                                  |  |  |  |  |

| G6    | nSCOUT5                               |  |  |  |  |

| E9    | nSCIN5                                |  |  |  |  |

| E10   | GP10 / RXD3                           |  |  |  |  |

| D10   | GP11 / TXD3                           |  |  |  |  |

| G4    | GP14 / nDSR3                          |  |  |  |  |

| E8    | GP17 / nRTS3                          |  |  |  |  |

| E7    | GP16 / nCTS3                          |  |  |  |  |

| D7    | GP42 / nIO_PME                        |  |  |  |  |

| D4    | VTR                                   |  |  |  |  |

| C10   | GP15 / nDTR3                          |  |  |  |  |

| D9    | GP61 / nLED2 / CLKO                   |  |  |  |  |

| C9    | GP60 / nLED1 / WDT                    |  |  |  |  |

| B9    | GP13 / nRI3                           |  |  |  |  |

| B10   | GP12 / nDCD3                          |  |  |  |  |

| A10   | GP31 / nRl4                           |  |  |  |  |

| A9    | GP63 / nDCD4                          |  |  |  |  |

| D6    | CLKI32                                |  |  |  |  |

| B8    | nRSMRST                               |  |  |  |  |

| A4    | VSS                                   |  |  |  |  |

| A8    | GP64 / RXD4                           |  |  |  |  |

| A7    | GP65 / TXD4                           |  |  |  |  |

| C6    | GP66 / nDSR4                          |  |  |  |  |

| B7    | GP67 / nRTS4                          |  |  |  |  |

| C5    | GP62 / nCTS4                          |  |  |  |  |

| B6    | GP34 / nDTR4                          |  |  |  |  |

| B5    | PWRGD_OUT                             |  |  |  |  |

| B4    | PWRGD_PS                              |  |  |  |  |

| A6    | nFPRST / GP30                         |  |  |  |  |

| A3    | VTR                                   |  |  |  |  |

| D5    | VSS                                   |  |  |  |  |

| A5    | VSS                                   |  |  |  |  |

| E2    | VSS                                   |  |  |  |  |

### TABLE 3-4: SCH3222 SUMMARY (CONTINUED)

a. Device ID register at Plug&Play Index 0x20 holds 0x7F.

### 4.0 **REVISION HISTORY**

### TABLE 4-1: REVISION HISTORY

| <b>Revision Level &amp; Date</b> | Section/Figure/Entry | Correction |  |

|----------------------------------|----------------------|------------|--|

| DS00002108A (02-16-16)           | Document Release     |            |  |

<sup>© 2016</sup> Microchip Technology Inc.

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO                  | - [X] ·<br>│<br>Temperature<br>Range             | - XX -<br>∏<br>Package                               | - [XX]<br> <br>Tape and Reel<br>Option | Exa<br>a) |      | <b>:</b><br>227-SZ<br>nercial temperature, 144-pin WFBGA,                                                                                                                                                                                                                              |

|--------------------------|--------------------------------------------------|------------------------------------------------------|----------------------------------------|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | SCH3227/SCH3226/S                                | SCH3224/SCH3222                                      | 2                                      | b)        |      | 227I-SZ-TR<br>rial temperature, 144-pin WFBGA, Tape<br>I                                                                                                                                                                                                                               |

| Temperature<br>Range:    | Blank = $0^{\circ}C$ to<br>I = $-40^{\circ}C$ to |                                                      |                                        |           |      |                                                                                                                                                                                                                                                                                        |

| Package:                 | SY = 100-pin WI                                  | FBGA (SCH3227)<br>FBGA (SCH3226. \$<br>BGA (SCH3222) | SCH3224)                               |           |      |                                                                                                                                                                                                                                                                                        |

| Tape and Reel<br>Option: | Blank = Standard pa<br>TR = Tape and R           |                                                      |                                        | Note      | ə 1: | Tape and Reel identifier only appears in<br>the catalog part number description. This<br>identifier is used for ordering purposes and<br>is not printed on the device package.<br>Check with your Microchip Sales Office for<br>package availability with the Tape and Reel<br>option. |

<sup>© 2016</sup> Microchip Technology Inc.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REP-RESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 9781522402992

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV — ISO/TS 16949—

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

DS00002108A-page 28

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

**India - Bangalore** Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15