## SUPPLEMENT

S71KS512SC0 S71KL256SC0 S71KL512SC0

# HyperFlash<sup>™</sup> and HyperRAM<sup>™</sup> Multi-Chip Package 1.8V/3V

#### **Distinctive Characteristics**

- HyperFlash<sup>™</sup> and HyperRAM<sup>™</sup> in Multi-Chip Package (MCP)

- □ 1.8V, 512 Mb HyperFlash and 64 Mbit HyperRAM (S71KS512SC0)

- □ 3.0V, 512 Mb HyperFlash and 64 Mbit HyperRAM (S71KL512SC0)

- □ 3.0V, 256 Mb HyperFlash and 64 Mbit HyperRAM (S71KL256SC0)

- □ FBGA 24-ball, 6 × 8 × 1.0 mm package

- HyperBus Interface

- □ 1.8V I/O, 12 bus signals

- Differential clock (CK/CK#)

- □ 3.0V I/O, 11 bus signals

- Single ended clock (CK)

- □ Chip Select (CS#)

- □ 8-bit data bus (DQ[7:0])

- □ Read-Write Data Strobe (RWDS)

- Bidirectional Data Strobe/Mask

- Output at the start of all transactions to indicate refresh latency

- · Output during read transactions as Read Data Strobe

- Input during write transactions as Write Data Mask (Hyper-RAM only)

- Optional Signals

- □ Reset

- INT# output to generate external interrupt

- Busy to Ready Transition

- □ RSTO# Output to generate system level Power-On Reset (POR)

- User configurable RSTO# Low period

- High Performance

- □ Double-Data Rate (DDR)

- Two data transfers per clock

- $\hfill \square$  Up to 166-MHz clock rate (333 MB/s) at 1.8V  $\hfill V_{CC}$

- $\Box$  Up to 100-MHz clock rate (200 MB/s) at 3.0V V<sub>CC</sub>

## **SUPPLEMENT**

## **Contents**

| General Description                  | 3 |

|--------------------------------------|---|

| HyperBus MCP Family with HyperFlash  |   |

| and HyperRAM                         | 3 |

| HyperBus MCP 3 V Signal Descriptions | 4 |

| HyperBus MCP Block Diagram           | 5 |

| Physical Interface                   | 6 |

| HyperBus MCP — FBGA 24-Ball,         |   |

| 5x5 Array Footprint                  | 6 |

| Physical Diagram                     | 7 |

| Electrical Specifications            | 8 |

| Absolute Maximum Ratings             |   |

| DC Characteristics                   |   |

| Ordering Part Numbers                   | T  |

|-----------------------------------------|----|

| Valid Combinations - Standard           | 1  |

| Valid Combinations — Automotive Grade / |    |

| AEC-Q100                                | 12 |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information | 14 |

| Worldwide Sales and Design Support      | 14 |

| Products                                | 14 |

| PSoC® Solutions                         | 14 |

| Cypress Developer Community             | 14 |

| Technical Support                       | 14 |

## **General Description**

This supplementary datasheet provides MCP device related information for a HyperBus MCP family, incorporating both HyperFlash and HyperRAM memories. The document describes how the features, operation, and ordering options of the related memories have been enhanced or changed from the standard memory devices incorporated in the MCP. The information contained in this document modifies any information on the same topics established by the documents listed in Table 1 and should be used in conjunction with those documents. This document may also contain information that was not previously covered by the listed documents. The information is intended for hardware system designers and software developers of applications, operating systems, or tools.

Table 1. Affected Documents/Related Documents

| Title                                                                                                                                                             | Cypress Publication Number |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| HyperBus™ Specification Low Signal Count, High Performance DDR Bus                                                                                                | 001-99253                  |

| S26KL512S / S26KS512S / S26KL256S / S26KS256S / S26KL128S / S26KS128S, 512 MBIT (64 MBYTE), 256 Mbit (32 Mbyte), 128 Mbit (16 Mbyte) 1.8V/3.0V HyperFlash™ Family | 001-99198                  |

| S27KL0641, S27KS0641, S71KL1281, S71KS1281: HyperRAM <sup>™</sup> Self-Refresh DRAM 3.0V/ 1.8V 64/128 Mbit (8/16 Mbyte)                                           | 001-97964                  |

#### HyperBus MCP Family with HyperFlash and HyperRAM

For systems needing both Flash and self-refresh DRAM, the HyperBus products family includes MCP devices that combine HyperFlash and HyperRAM in a single package. A HyperBus MCP reduces board space and Printed Circuit Board (PCB) signal routing congestion while also maintaining or improving signal integrity over separately packaged memory configurations.

The HyperBus MCP family offers 1.8V/3V interface HyperFlash densities of 512 Mb (64 Mbyte) and 256 Mb (32 Mbyte) in combination with HyperRAM 64 Mb (8 Mbyte).

This supplemental datasheet addresses only the MCP related differences from the HyperBus Specification and the individual HyperFlash and HyperRAM datasheets. For all other information related to the individual memories in the MCP, refer to the HyperBus, HyperFlash, and HyperRAM datasheets.

Document Number: 002-03902 Rev. \*D Page 3 of 14

## **HyperBus MCP 3 V Signal Descriptions**

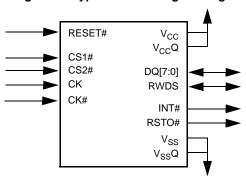

Figure 1. HyperBus MCP Signal Diagram

**Table 2. Signal Descriptions**

| Symbol            | Туре                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CS1#              | Input               | Chip Select 1: Chip Select for the HyperFlash memory. HyperBus transactions are initiated with a High to Low transition. HyperBus transactions are terminated with a Low to High transition.                                                                                                                                                                                                                                                                                             |  |

| CS2#              | Input               | Chip Select 2: Chip Select for the HyperRAM memory. HyperBus transactions are initiated with a High to Low transition. HyperBus transactions are terminated with a Low to High transition.                                                                                                                                                                                                                                                                                               |  |

| СК                | Input               | Single-ended Clock 3.0V: Command-Address/Data information is input or output with respect to the edges of the CK.  Note: Single-ended clock is available on 3.0V devices only.                                                                                                                                                                                                                                                                                                           |  |

| CK/CK#            | Input               | Differential Clock 1.8V: Command-Address/Data information is input or output with respect to the crossing edges of the CK/CK# pair.  Note: Differential clock is available on 1.8V devices only.                                                                                                                                                                                                                                                                                         |  |

| RWDS              | Output              | Read-Write Data Strobe: Output data during read transactions are edge aligned with RWDS. RWDS is an input during write transactions to function as a HyperRAM data mask. At the beginning of all bus transactions RWDS is an output and indicates whether additional initial latency count is required.  1 = Additional latency count 0 = No additional latency count                                                                                                                    |  |

| DQ[7:0]           | Input/Output        | Data Input/Output: Command-Address/Data information is transferred on these DQs d Read and Write transactions.                                                                                                                                                                                                                                                                                                                                                                           |  |

| INT#              | Output (open drain) | INT Output (Optional): When Low, the HyperFlash device is indicating that an internal event has occurred. This signal is intended to be used as a system level interrupt for the device to indicate that an on-chip event has occurred. INT# is an open-drain output.                                                                                                                                                                                                                    |  |

| RESET#            | Input               | Hardware RESET (Optional): When Low, the HyperFlash memory will self initialize and return to the idle state. RWDS and DQ[7:0] is placed into the High-Z state when RESET# is Low. RESET# includes a weak pull-up, if RESET# is left unconnected it will be pulled up to the High state. RESET# is not connected to the HyperRAM.                                                                                                                                                        |  |

| RSTO#             | Output (open drain) | RSTO# Output (Optional): RSTO# is an open-drain output used to indicate when a POR is occurring within the HyperFlash memory and can be used as a system level reset signal. Upon completion of the internal POR the RSTO# signal will transition from Low to high impedance after a user defined timeout period has elapsed. Upon transition to the high impedance state the external pull-up resistance will pull RSTO# High and the device immediately is placed into the Idle state. |  |

| V <sub>CC</sub>   | Power Supply        | Core Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| V <sub>CC</sub> Q | Power Supply        | Input/Output Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>SS</sub>   | Power Supply        | Core Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| V <sub>SS</sub> Q | Power Supply        | Input/Output Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

Document Number: 002-03902 Rev. \*D

## **HyperBus MCP Block Diagram**

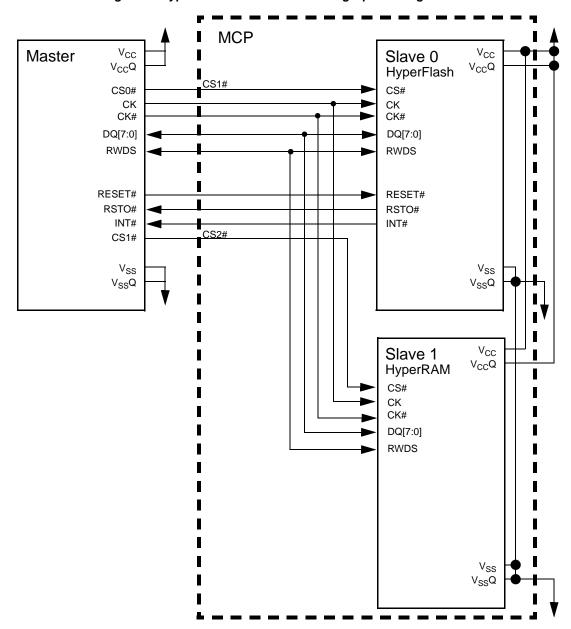

Figure 2. HyperBus Connections Including Optional Signals

#### Note

1. CK# is for 1.8V devices only.

## **Physical Interface**

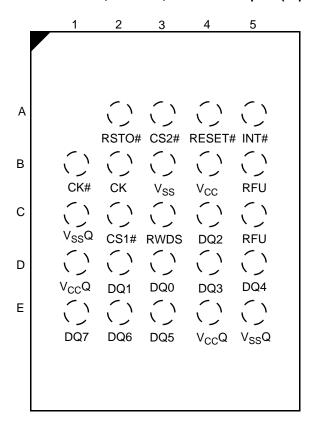

## HyperBus MCP — FBGA 24-Ball, 5x5 Array Footprint

Figure 3. 24-Ball FBGA, 6 x 8 mm, 5 x 5 Ball Footprint (Top View)

#### Notes

- 2. C2 and A3 are chip select (CS#) signals 1 and 2 used for HyperFlash and HyperRAM devices respectively.

- V<sub>SS</sub> and V<sub>SSQ</sub> are internally connected.

CK# (B1) is RFU in 3.0V devices

## **Physical Diagram**

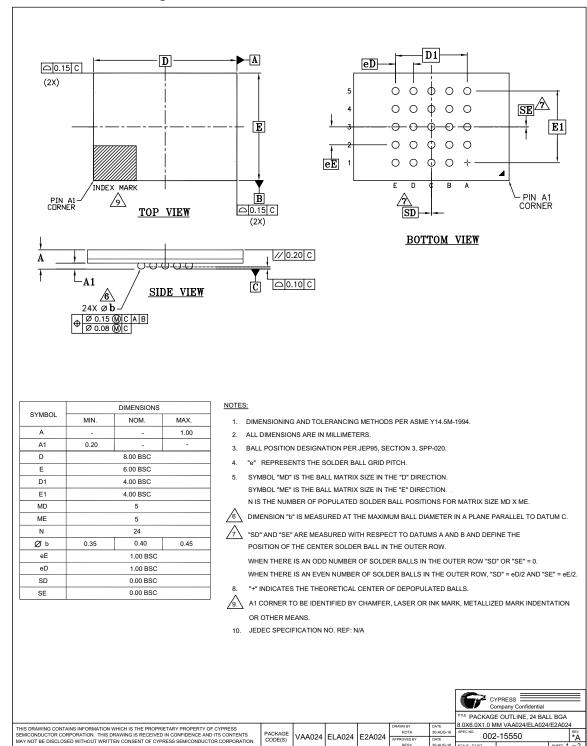

Figure 4. ELA024 — FBGA 24-Ball 6 x 8 x 1 mm

## **Electrical Specifications**

For the general description of the HyperBus interface electrical specifications, refer to the HyperBus Specification. The following section describes HyperFlash device dependent aspects of electrical specifications.

#### Absolute Maximum Ratings

Ambient Temperature with Power Applied: -65 °C to +105 °C

#### DC Characteristics

Only one memory may have its chip select active (Low) at any point in time. For each of the conditions below refer to the Hyper-Flash and HyperRAM datasheets for the most accurate information:

- Active core read or write current will be that of the selected device plus the standby current of the non-selected device. But, the added standby current is generally not significant as it is less than 300 μA.

- Active IO read current will be that of the selected device.

- Active clock stop current will be that of the selected device plus the standby current of the non-selected device. But, the added standby current is generally not significant as it is less than 300 μA.

- Program or erase current will be that of the HyperFlash device. Note however, that program and erase operations are long time frame events that extend beyond the duration of a HyperFlash chip select period. Thus, if the HyperRAM is selected for read or write during an on going HyperFlash program or erase operation, the active current will be the sum of the HyperFlash program or erase operation and the HyperRAM read or write current.

- Standby current, when neither memory is selected and no embedded flash operation is in progress, is the sum of the memory standby currents.

- Deep Power Down (DPD) current, is the sum of the memory DPD currents.

- Power On Reset (POR) current is the sum of the memory standby currents.

- Input leakage current is the sum of the memory input leakage currents.

For reference purpose, Table 3 aids in the estimation of the above operating conditions current consumption. However, refer to the HyperFlash and HyperRAM datasheets for the most accurate information.

Table 3. 3.0V DC Characteristics (CMOS Compatible)

| Parameter                                             | Description                                                                                              | Test Conditions                                                                 | Min | Typ <sup>[6]</sup> | Max   | Unit |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|--------------------|-------|------|

| I <sub>LI</sub>                                       | Input Leakage Current                                                                                    | $V_{IN} = V_{SS}$ to $V_{CC}$ ,<br>$V_{CC} = V_{CC}$ max                        | -   | _                  | ±4.0  | μΑ   |

| I <sub>LO</sub>                                       | Output Leakage Current                                                                                   | $V_{OUT} = V_{SS}$ to $V_{CC}$ ,<br>$V_{CC} = V_{CC}$ max                       | -   | _                  | ±2.0  | μА   |

| I                                                     | V <sub>CC</sub> Active Read Current - HyperFlash reading (core current only, IO switching current is not | $CS\# = V_{IL}$ , @100 MHz,<br>$V_{CC} = 3.6V$                                  | -   | 80.2               | 100.3 | mA   |

| ICC1HF                                                | included)                                                                                                | $CS\# = V_{IL}$ , @166 MHz,<br>$V_{CC} = 1.95V$                                 | -   | 130.2              | 180.3 | mA   |

| lia=                                                  | V <sub>CC</sub> Q Active Read Current of IOs - HyperFlash                                                | $CS\# = V_{IL}, @100 \text{ MHz}, \\ V_{CC}Q = 3.6V, C_{LOAD} = 20 \text{ pF}$  | -   | 80                 | 100   | mA   |

| I <sub>IO1HF</sub>                                    | reading                                                                                                  | $CS\# = V_{IL}, @166 \text{ MHz}, \\ V_{CC}Q = 1.95V, C_{LOAD} = 20 \text{ pF}$ | -   | 80                 | 100   | mA   |

| I                                                     | V <sub>CC</sub> Active Read Current - HyperRAM reading                                                   | $CS\# = V_{IL}$ , @100 MHz, $V_{CC} = 3.6V$                                     | -   | 20.1               | 35.3  | mA   |

| I <sub>CC1HR</sub> V <sub>CC</sub> Active Read Currel | VCC Active Read Current - HyperKAlvi reading                                                             | $CS\# = V_{IL}, @166 \text{ MHz}, V_{CC} = 1.95 V$                              | -   | 20.1               | 60.3  | mA   |

| I <sub>CC2HR</sub> V <sub>CC</sub> A                  | V Active Write Current Livear DAM verting                                                                | $CS\# = V_{IL}, @100 \text{ MHz}, \\ V_{CC} = 3.6V$                             | -   | 15.1               | 35.3  | mA   |

|                                                       | V <sub>CC</sub> Active Write Current - HyperRAM writing                                                  | CS# = V <sub>IL</sub> , @166 MHz,<br>V <sub>CC</sub> = 1.95V                    | _   | 15.1               | 60.3  | mA   |

| . Voc Ac                                              | V <sub>CC</sub> Active Read Current - HyperFlash embedded                                                | CS# = V <sub>IL</sub> , @100 MHz,<br>V <sub>CC</sub> = 3.6V                     | _   | 80                 | 135   | mA   |

| I <sub>CC1HFHR</sub>                                  | operation plus HyperRAM reading <sup>[6]</sup>                                                           | CS# = V <sub>IL</sub> , @166 MHz,<br>V <sub>CC</sub> = 1.95V                    | _   | 80                 | 160   | mA   |

|                                                       | V <sub>CC</sub> Active Write Current - HyperFlash embedded                                               | CS# = V <sub>IL</sub> , @100 MHz,<br>V <sub>CC</sub> = 3.6V                     | _   | 75                 | 135   | mA   |

| ICC2HFHR                                              | operation plus HyperRAM writing <sup>[6]</sup>                                                           | CS# = V <sub>IL</sub> , @166 MHz,<br>V <sub>CC</sub> = 1.95V                    | _   | 75                 | 160   | mA   |

| I <sub>CC3P</sub>                                     | V <sub>CC</sub> Active Program Current <sup>[5, 6]</sup>                                                 | V <sub>CC</sub> = V <sub>CC</sub> max                                           | _   | 60                 | 100   | mA   |

| I <sub>CC3E</sub>                                     | V <sub>CC</sub> Active Erase Current <sup>[5, 6]</sup>                                                   | V <sub>CC</sub> = V <sub>CC</sub> max                                           | _   | 60                 | 100   | mA   |

| I <sub>CC4I</sub>                                     | $V_{CC}$ Standby Current for Industrial Temperature (– 40 °C to +85 °C)                                  | $CS\#$ , $RESET\# = V_{CC}$ , $V_{CC} = V_{CC} \max$                            | -   | 160                | 300   | μA   |

| I <sub>CC4IC</sub>                                    | V <sub>CC</sub> Standby Current for Industrial Plus<br>Temperature (–40 °C to +105 °C)                   | $CS\#$ , RESET# = $V_{CC}$ , $V_{CC} = V_{CC}$ max                              | -   | 160                | 600   | μΑ   |

| I <sub>CC5</sub>                                      | V <sub>CC</sub> Reset Current                                                                            | $CS\# = V_{IH}$ , RESET $\# = V_{SS}$ , $V_{CC} = V_{CC} \max (1.8V/3.0V)$      | -   | 10                 | 20    | mA   |

| I <sub>CC6</sub>                                      | Active Clock Stop Mode <sup>[7]</sup>                                                                    | $V_{IH} = V_{CC}, V_{IL} = V_{SS},$<br>$V_{CC} = 1.95V/3.6V$                    | -   | 11.3               | 24    | mA   |

| I <sub>CC7</sub>                                      | V <sub>CC</sub> Current during Power-Up (POR)                                                            | $CS\# = X, V_{CC} = V_{CC} max$<br>(1.95V/3.6V)                                 | -   | 100                | 135   | mA   |

- NoteS

I<sub>CC</sub> active while Embedded Algorithm is in progress.

Not 100% tested.

Active Clock Stop Mode enables the lower power mode when the CK signals remain stable for t<sub>ACC</sub> + 30 ns

Typical I<sub>CC</sub> values are measured at t<sub>AI</sub> = 25 °C and V<sub>CC</sub> = V<sub>CCQ</sub> = 1.8V/3.0V (not applicable to I<sub>DPD</sub> for 85 °C and 105 °C).

Table 3. 3.0V DC Characteristics (CMOS Compatible) (Continued)

| Parameter | Description                                           | Test Conditions                                                    | Min | Typ <sup>[6]</sup> | Max | Unit |

|-----------|-------------------------------------------------------|--------------------------------------------------------------------|-----|--------------------|-----|------|

|           | Deep Power-Down Current 512/64 Mb @ 25°C              |                                                                    | _   | 34.1               | 112 | μΑ   |

|           | Deep Power-Down Current 512/64 Mb @ 85°C              | CS#, RESET#,                                                       | _   | 36.6               | 120 | μΑ   |

|           | Deep Power-Down Current 512/64 Mb @ 105°C             | $V_{CC} = V_{CC} \text{ max } (1.95 \text{V}/3.6 \text{V})$        | _   | 37.4               | 340 | μΑ   |

|           | Deep Power-Down Current (all other densities) @ 25°C  | HyperFlash in Standby                                              | -   | 34.1               | 112 | μΑ   |

|           | Deep Power-Down Current (all other densities) @ 85°C  | HyperRAM in Deep Power                                             | -   | 37.4               | 140 | μΑ   |

| 1         | Deep Power-Down Current (all other densities) @ 105°C | Down                                                               | -   | 37.4               | 340 | μΑ   |

| IDPD      | Deep Power-Down Current 512/64 Mb @ 25°C              | CC# DECET#                                                         |     | 143                | 218 | μΑ   |

|           | Deep Power-Down Current 512/64 Mb @ 85°C              | CS#, RESET#,<br>V <sub>CC</sub> = V <sub>CC</sub> max (1.95V/3.6V) |     | 165                | 250 | μΑ   |

|           | Deep Power-Down Current 512/64 Mb @ 105°C             | VCC = VCC max (1.00 V/0.0 V)                                       |     | 230                | 350 | μΑ   |

|           | Deep Power-Down Current (all other densities) @ 25°C  | HyperFlash in Deep Power<br>Down                                   |     | 138                | 206 | μΑ   |

|           | Deep Power-Down Current (all other densities) @ 85°C  | HyperRAM in Standby                                                |     | 139                | 210 | μΑ   |

|           | Deep Power-Down Current (all other densities) @ 105°C | Trype Standay                                                      |     | 140                | 215 | μΑ   |

#### Notes

- $I_{\rm CC}$  active while Embedded Algorithm is in progress. Not 100% tested.

- Active Clock Stop Mode enables the lower power mode when the CK signals remain stable for t<sub>ACC</sub> + 30 ns

Typical I<sub>CC</sub> values are measured at t<sub>AI</sub> = 25 °C and V<sub>CC</sub> = V<sub>CCQ</sub> = 1.8V/3.0V (not applicable to I<sub>DPD</sub> for 85 °C and 105 °C).

Table 4. 1.8V/3.0V Capacitive Characteristics

| Description                            |               | Parameter | Min  | Max  | Unit |  |

|----------------------------------------|---------------|-----------|------|------|------|--|

| Input Capacitance (CK, CK#)[7,8,9]     | CI            | 6.0       | 10.0 | pF   |      |  |

| Output Capacitanas (PMDS)[78.9]        | S71KL/S512SC0 | СО        | 8.0  | 10.0 | F    |  |

| Output Capacitance (RWDS)[7,8,9]       | S71KL/S256SC0 | CO        | 6.0  | 10.5 | - pF |  |

| I/O Pin Capacitance (DQx)[7,8,9]       | S71KL/S512SC0 | CIO       | 8.0  | 10.0 | nE   |  |

| 1/O Fin Capacitance (DQX)              | S71KL/S256SC0 | CIO       | 8.0  | 10.5 | pF   |  |

| I/O Pin Capacitance Delta (DQx)[7,8,9] | CIOD          | _         | 1.0  | pF   |      |  |

| INT#, RSTO# Pin Capacitance, RST       | COP           |           | 8.0  | pF   |      |  |

## Notes

<sup>9.</sup> These values are guaranteed by design and are tested on a sample basis only.

10. Pin capacitance is measured according to JEP147 procedure for measuring capacitance using a vector network analyzer. V<sub>CC</sub>, V<sub>CC</sub>Q are applied and all other pins (except the pin under test) floating. DQs should be in the High Impedance state.

11. The capacitance values for the CK, CK#, RWDS and DQx pins must have similar capacitance values to allow for signal propagation time matching in the system. The capacitance value for CS# is not as critical because there are no critical timings between CS# going active (Low) and data being presented on the DQs bus.

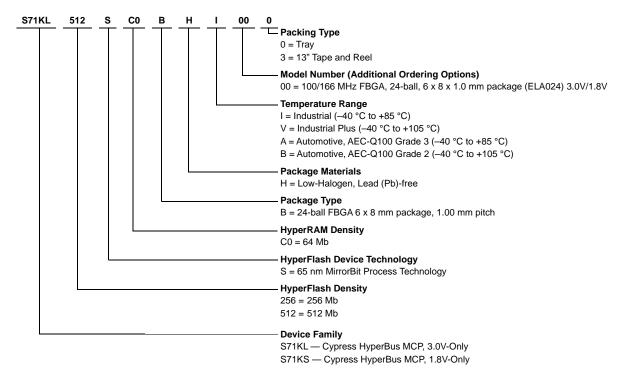

## **Ordering Part Numbers**

The ordering part number is formed by a valid combination of the following:

#### **Valid Combinations - Standard**

Table 5 lists configurations planned to be available in volume. The table will be updated as new combinations are released. Contact your local sales representative to confirm availability of specific combinations and to check on newly released combinations.

**Table 5. Valid Standard Combinations**

| Device Number | HyperRAM<br>Density | Package<br>and<br>Material | Temperature<br>Range | Model<br>Number | Packing<br>Type | Ordering Part Number<br>(x = Packing Type) | Package Marking |                   |               |                   |               |

|---------------|---------------------|----------------------------|----------------------|-----------------|-----------------|--------------------------------------------|-----------------|-------------------|---------------|-------------------|---------------|

| S71KL256S     | C0                  | ВН                         | 1.1/                 | 00              | 0, 3            | S71KL256SC0BHI00x                          | 1KL256SC0HI00   |                   |               |                   |               |

| 37 IKL2303    | CO                  | CU                         | DIT                  | 1, V            | I, V 00         | 00                                         | 0, 3            | S71KL256SC0BHV00x | 1KL256SC0HV00 |                   |               |

| S71KL512S     | C0                  | ВН                         | I, V                 | I, V 00         | 0.2             | S71KL512SC0BHI00x                          | 1KL512SC0HI00   |                   |               |                   |               |

| 37 IKL3123    |                     |                            |                      |                 | 00              | 1, V 00                                    | 0, 3            | S71KL512SC0BHV00x | 1K5L12SC0HV00 |                   |               |

| S71KS512S     | C0 BH               | DU                         | DII                  | 1.1/            | 1.1/            | 1. 1/                                      | 00              | 00                |               | S71KS512SC0BHI00x | 1KS512SC0HI00 |

| 3/1855125     | CO                  | DΠ                         | I, V                 | 00              | 0, 3            | S71KS512SC0BHV00x                          | 1KS512SC0HV00   |                   |               |                   |               |

#### Note

12. FBGA package marking omits the leading S7, the package type character and packing type character from the ordering part number.

#### Valid Combinations — Automotive Grade / AEC-Q100

Table 6 lists configurations that are Automotive Grade / AEC-Q100 qualified and are planned to be available in volume. The table will be updated as new combinations are released. Consult your local sales representative to confirm availability of specific combinations and to check on newly released combinations.

Production Part Approval Process (PPAP) support is only provided for AEC-Q100 grade products.

Products to be used in end-use applications that require ISO/TS-16949 compliance must be AEC-Q100 grade products in combination with PPAP. Non–AEC-Q100 grade products are not manufactured or documented in full compliance with ISO/TS-16949 requirements.

AEC-Q100 grade products are also offered without PPAP support for end-use applications that do not require ISO/TS-16949 compliance.

Table 6. Valid Combinations — Automotive Grade / AEC-Q100

| Device Number | HyperRAM<br>Density | Package<br>and<br>Material | Temperature<br>Range | Model<br>Number | Packing<br>Type | Ordering Part Number<br>(x = Packing Type) | Package Marking |

|---------------|---------------------|----------------------------|----------------------|-----------------|-----------------|--------------------------------------------|-----------------|

| S71KL256S     | C0                  | ВН                         | A, B                 | 00              | 0, 3            | S71KL256SC0BHA00x                          | 1KL256SC0HA00   |

|               |                     |                            |                      |                 |                 | S71KL256SC0BHB00x                          | 1KL256SC0HB00   |

| S71KL512S     | C0                  | ВН                         | A, B                 | 00              | 0, 3            | S71KL512SC0BHA00x                          | 1KL512SC0HA00   |

|               |                     |                            |                      |                 |                 | S71KL512SC0BHB00x                          | 1KL512SC0HB00   |

| S71KS512S     | C0                  | ВН                         | A, B                 | 00              | 0, 3            | S71KS512SC0BHA00x                          | 1KS512SC0HA00   |

|               |                     |                            |                      |                 |                 | S71KS512SC0BHB00x                          | 1KS512SC0HB00   |

#### Note

FBGA package marking omits the leading S7, the package type character and packing type character from the ordering part number.

Document Number: 002-03902 Rev. \*D

## **Document History Page**

| Rev. | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 5023814 | MAMC               | 11/23/2015         | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *A   | 5188954 | RYSU               | 07/07/2016         | Updated HyperBus MCP 3 V Signal Descriptions: Updated Table 2: Updated details in "Description" column corresponding to RESET# pin. Updated HyperBus MCP Block Diagram. Updated Physical Interface: Updated HyperBus MCP — FBGA 24-Ball, 5x5 Array Footprint: Added Note 2. Updated Physical Diagram: Added Figure 4. Updated Electrical Specifications: Updated DC Characteristics: Updated Table 3: Changed typical value of I <sub>CC5</sub> parameter from 20 mA to 10 mA. Changed maximum value of I <sub>CC5</sub> parameter from 40 mA to 20 mA. Updated Table 4: Updated values of all parameters. Updated to new template.                                              |

| *B   | 5442136 | RYSU               | 09/27/2016         | Updated Document Title to read as "S71KL512SC0, HyperFlash™ and HyperRAM™ Multi-Chip Package 3V".  Removed part number "S71KL256SC0" related information in all instances across the document.  Removed 256 Mb density related information in all instances across the document.  Updated Ordering Part Numbers:  Added Automotive, AEC-Q100 Grade 3 and Automotive, AEC-Q100 Grade 2 Temperature Range details.  Removed 128 Mb, 256 Mb details.  Updated Valid Combinations - Standard:  Removed S71KL256S and its corresponding details.  Added Valid Combinations — Automotive Grade / AEC-Q100.  Updated to new template.                                                   |

| *C   | 5560279 | RYSU               | 12/20/2016         | Updated Document Title to read as "S71KL256SC0/S71KL512SC0, HyperFlash™ and HyperRAM™ Multi-Chip Package 3 V".  Added part number "S71KL256SC0" related information in all instances across the document.  Added 256 Mb density related information in all instances across the document Updated Electrical Specifications:  Updated DC Characteristics:  Updated Table 4:  Added values corresponding to S71KL256SC0.  Updated Ordering Part Numbers:  Added 256 Mb details.  Updated Valid Combinations - Standard:  Added S71KL256S and its corresponding details.  Updated Valid Combinations — Automotive Grade / AEC-Q100:  Added S71KL256S and its corresponding details. |

| *D   | 5635102 | SZZX               | 02/23/2017         | Added S71KS512S and its corresponding details. Updated Sales and Copyright information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## **SUPPLEMENT**

S71KS512SC0 S71KL256SC0 S71KL512SC0

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers

Automotive

Clocks & Buffers

Interface

Internet of Things

Memory

Cypress.com/automotive

cypress.com/clocks

cypress.com/interface

cypress.com/iot

cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

#### **PSoC® Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2015-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.