## **PN7150**

# High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Rev. 4.0 — 25 June 2020 317440

Product data sheet COMPANY PUBLIC

### 1 Introduction

This document describes the functionality and electrical specification of the NFC Controller PN7150.

Additional documents describing the product functionality further are available for designin support. Refer to the references listed in this document to get access to the full documentation provided by NXP.

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

### 2 General description

Plug'n play and high-performance full NFC solution PN7150 is a full NFC controller solution with integrated firmware and NCI interface designed for contactless communication at 13.56 MHz. It is compatible with NFC forum requirements.

PN7150 is designed based on learnings from previous NXP NFC device generation. It is the ideal solution for rapidly integrating NFC technology in any application, especially those running O/S environment like Linux and Android, reducing Bill of Material (BOM) size and cost, thanks to:

- Full NFC forum compliancy (see [1]) with small form factor antenna

- · Embedded NFC firmware providing all NFC protocols as pre-integrated feature

- Direct connection to the main host or microcontroller, by I<sup>2</sup>C-bus physical and NCI protocol

- · Ultra-low power consumption in polling loop mode

- Highly efficient integrated power management unit (PMU) allowing direct supply from a battery

PN7150 embeds a new generation RF contactless front-end supporting various transmission modes according to NFCIP-1 and NFCIP-2, ISO/IEC 14443, ISO/IEC 15693, MIFARE Classic IC-based card and FeliCa card specifications. It embeds an Arm Cortex-M0 microcontroller core loaded with the integrated firmware supporting the NCI 1.0 host communication. It also allows to provide a higher output power by supplying the transmitter output stage from 3.0 V to 4.75 V.

The contactless front-end design brings a major performance step-up with on one hand a higher sensitivity and on the other hand the capability to work in active load modulation communication enabling the support of small antenna form factor.

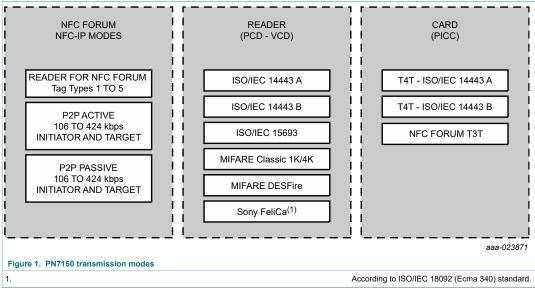

Supported transmission modes are listed in Figure 1. For contactless card functionality, the PN7150 can act autonomously if previously configured by the host in such a manner.

PN7150 integrated firmware provides an easy integration and validation cycle as all the NFC real-time constraints, protocols and device discovery (polling loop) are being taken care internally. In few NCI commands, host SW can configure the PN7150 to notify for card or peer detection and start communicating with them.

PN7150

All information provided in this document is subject to legal disclaimers.

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

#### 3 Features and benefits

- Includes NXP ISO/IEC14443-A and Innovatron ISO/IEC14443-B intellectual property licensing rights

- Arm Cortex-M0 microcontroller core

- · Highly integrated demodulator and decoder

- Buffered output drivers to connect an antenna with minimum number of external components

- · Integrated RF level detector

- Integrated Polling Loop for automatic device discovery

- RF protocols supported

- NFCIP-1, NFCIP-2 protocol (see [8] and [11])

- ISO/IEC 14443A, ISO/IEC 14443B PICC, NFC Forum T4T modes via host interface (see [3])

- NFC Forum T3T via host interface

- ISO/IEC 14443A, ISO/IEC 14443B PCD designed according to NFC Forum digital protocol T4T platform and ISO-DEP (see [1])

- FeliCa PCD mode

- MIFARE Classic PCD encryption mechanism (MIFARE Classic 1K/4K)

- NFC Forum tag 1 to 5 (MIFARE Ultralight, Jewel, Open FeliCa tag, MIFARE DESFire) (see [1])

- ISO/IEC 15693/ICODE VCD mode (see [9])

- Supported host interfaces

- NCI protocol interface according to NFC Forum standardization (see [2])

- I<sup>2</sup>C-bus High-speed mode (see [4])

- · Integrated power management unit

- Direct connection to a battery (2.3 V to 5.5 V voltage supply range)

- Support different Hard Power-Down/Standby states activated by firmware

- Autonomous mode when host is shut down

- Automatic wake-up via RF field, internal timer and I<sup>2</sup>C-bus interface

- Integrated non-volatile memory to store data and executable code for customization

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

### 4 Applications

- All devices requiring NFC functionality especially those running in an Android or Linux environment

- TVs, set-top boxes, blu-ray decoders, audio devices

- · Home automation, gateways, wireless routers

- · Home appliances

- · Wearables, remote controls, healthcare, fitness

- Printers, IP phones, gaming consoles, accessories

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

#### 5 Quick reference data

Table 1. Quick reference data

| Symbol                 | Parameter                           | Conditions                                                                   |            | Min  | Тур | Max  | Unit |

|------------------------|-------------------------------------|------------------------------------------------------------------------------|------------|------|-----|------|------|

| $V_{BAT}$              | battery supply voltage              | Card Emulation and Passive<br>Target; V <sub>SS</sub> = 0 V                  | [1]<br>[2] | 2.3  | -   | 5.5  | V    |

|                        |                                     | Reader, Active Initiator and<br>Active Target; V <sub>SS</sub> = 0 V         | [1]<br>[2] | 2.7  | -   | 5.5  | V    |

| V <sub>DD</sub>        | supply voltage                      | internal supply voltage                                                      |            | 1.65 | 1.8 | 1.95 | V    |

| V <sub>DD(PAD)</sub>   | V <sub>DD(PAD)</sub> supply voltage | supply voltage for host interface                                            |            |      |     |      |      |

|                        |                                     | • 1.8 V host supply;V <sub>SS</sub> = 0 V                                    | [1]        | 1.65 | 1.8 | 1.95 | V    |

|                        |                                     | • 3 V host supply; V <sub>SS</sub> = 0 V                                     | [1]        | 3.0  | -   | 3.6  | V    |

| I <sub>BAT</sub>       | battery supply current              | in Hard Power Down state;V <sub>BAT</sub> = 3.6 V; T = 25 °C                 | [3]        | -    | 10  | 14   | μA   |

|                        |                                     | in Standby state;V <sub>BAT</sub> = 3.6 V; T = 25 °C                         |            | -    | 20  | -    | μΑ   |

|                        |                                     | in Monitor state;V <sub>BAT</sub> = 2.75 V; T = 25 °C                        |            | -    | -   | 14   | μΑ   |

|                        |                                     | in low-power polling loop; $V_{BAT}$ = 3.6 V; T = 25 °C;loop time = 500 ms   | [4]        | -    | 150 | -    | μΑ   |

|                        |                                     | PCD mode at typical 3 V                                                      | [2]        | -    | -   | 190  | mA   |

| I <sub>O(VDDPAD)</sub> | output current on pin $V_{DD(PAD)}$ | total current which can be pulled on V <sub>DD(PAD)</sub> referenced outputs |            | -    | -   | 15   | mA   |

| I <sub>th(Ilim)</sub>  | current limit threshold current     | current limiter on $V_{DD(TX)}$ pin; $V_{DD(TX)} = 3.3$ V                    | [2]        | -    | 180 | -    | mA   |

| P <sub>tot</sub>       | total power dissipation             | Reader; $I_{VDD(TX)} = 100 \text{ mA}; V_{BAT} = 5.5 \text{ V}$              |            | -    | -   | 420  | mW   |

| T <sub>amb</sub>       | ambient temperature                 | JEDEC PCB-0.5                                                                |            | -30  | -   | +85  | °C   |

<sup>[1]</sup>  $V_{SS}$  represents  $V_{SS(PAD)}$  and  $V_{SS(TX)}$ .

<sup>[2]</sup> The antenna should be tuned not to exceed this current limit (the detuning effect when coupling with another device must be taken into account).

<sup>[3]</sup> External clock on NFC\_CLK\_XTAL1 must be LOW.

<sup>[4]</sup> See [10] for computing the power consumption as it depends on several parameters.

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

#### 6 Versions

#### 6.1 Version C11006

PN7150B0HN/C11006 contains a firmware update compared to the previous version.

The firmware version is 10.01.AE and contains the following new features and fixes:

- Anti tearing mechanism: An Anti tearing mechanism has been added. For details, please refer to the User Manual UM10936.

- A fix has been added that addresses a collision resolution problem for ISO 15693 tags in case there are multiple tags in the field.

#### 6.2 Version C11004

PN7150B0HN/C11004 has been withdrawn.

#### 6.3 Version C11002

PN7150B0HN/C11002 and PN7150B0UK/C11002 is the initial released version.

The firmware version is 10.01.A0

**Product data sheet**

**COMPANY PUBLIC**

6 / 66

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

#### **Ordering information** 7

**Table 2. Ordering information**

| Type number                      | Package |                                                                                                                 |           |

|----------------------------------|---------|-----------------------------------------------------------------------------------------------------------------|-----------|

|                                  | Name    | Description                                                                                                     | Version   |

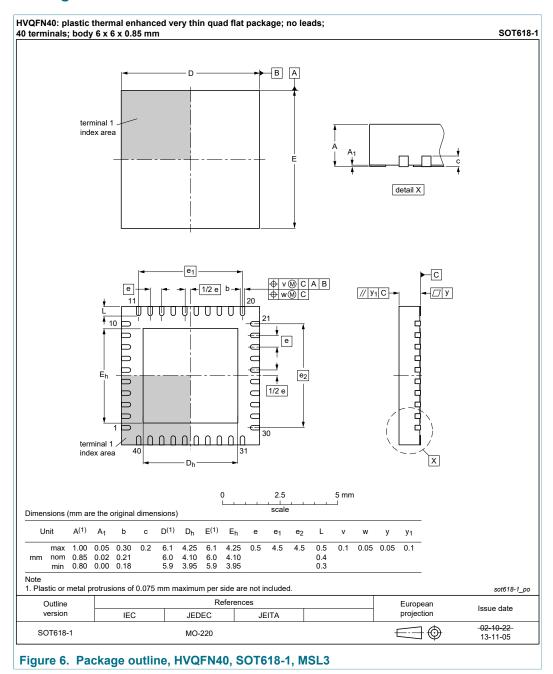

| PN7150B0HN/C110xx <sup>[1]</sup> | HVQFN40 | plastic thermal enhanced very thin quad<br>flat package; no leads; 40 terminals;<br>body; 6 mm × 6 mm × 0.85 mm | SOT618-1  |

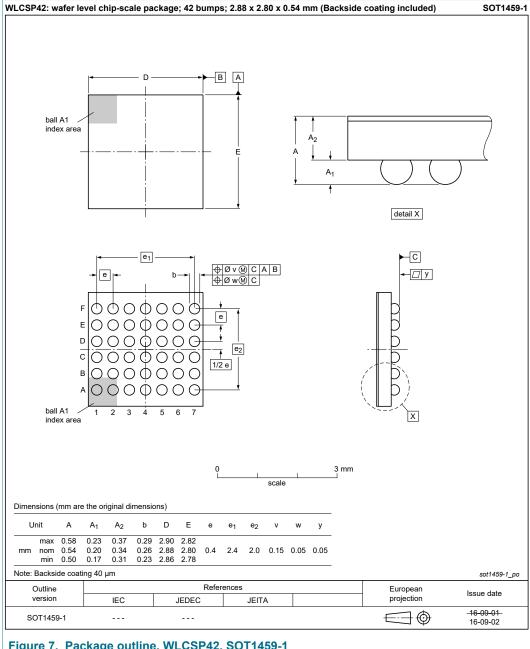

| PN7150B0UK/C110xx <sup>[1]</sup> | WLCSP42 | wafer level chip-scale package; 42<br>bumps; 2.88 mm × 2.80 mm × 0.54 mm<br>(Backside coating included)         | SOT1459-1 |

|                                  |         | Do not use for new designs. Planned for discontinuation.                                                        |           |

[1] xx = firmware code variant

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

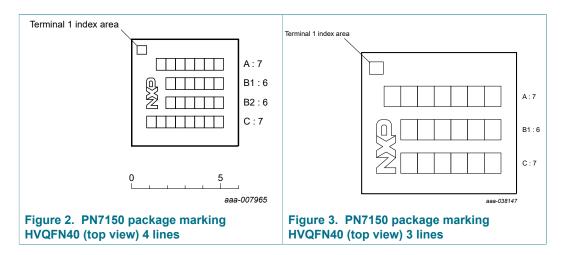

### 8 Marking HVQFN40

Table 3. Marking codes

| Type number        | Marking code                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line A             | 7 characters used: basic type number:PN7150x where x is the FW variant                                                                                                                                                                                                                                                                                                                                                         |

| Line B1            | 6 characters used: diffusion batch sequence number                                                                                                                                                                                                                                                                                                                                                                             |

| Line B2 (optional) | 6 characters used: assembly ID number                                                                                                                                                                                                                                                                                                                                                                                          |

| Line C             | 7 characters used: manufacturing code including:  • diffusion center code:  - Z: SSMC  - S: Powerchip (PTCT)  • assembly center code:  - S: ATKH  • RoHS compliancy indicator:  - D: Dark Green; fully compliant RoHS and no halogen and antimony  • manufacturing year and week, 3 digits:  - Y: year  - WW: week code  • product life cycle status code:  - X: means not qualified product  - nothing means released product |

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

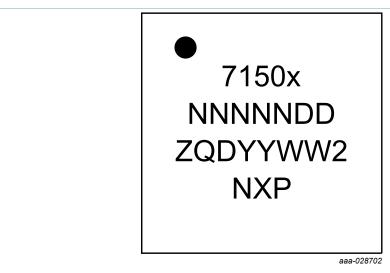

### 9 Marking WLCSP42

Figure 4. WLCSP42

Table 4. WLCSP package marking (top view)

| Line number | Marking code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line 1      | Product identification • Product name: 7150x; where x is the variant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Line 2      | Diffusion batch sequence number  Diffusion fabrication code: NNNNN Wafer ID: DD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Line 3      | <ul> <li>Manufacturing code including:</li> <li>Diffusion center code: <ul> <li>Z: SSMC</li> <li>s: Global Foundry</li> <li>S: Power chip (PTCT)</li> </ul> </li> <li>Assembly center code: <ul> <li>Q: ASE-CL</li> </ul> </li> <li>RoHS compliancy indicator: <ul> <li>D: Dark Green; fully compliant RoHS and no halogen and antimony</li> </ul> </li> <li>Manufacturing year and week; 4 digits: <ul> <li>YY: year</li> <li>WW: week code</li> </ul> </li> <li>Mask layout version</li> <li>Product life cycle status code: <ul> <li>X: not qualified product</li> <li>Nothing means released product</li> </ul> </li> </ul> |

| Line 4      | NXP logo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

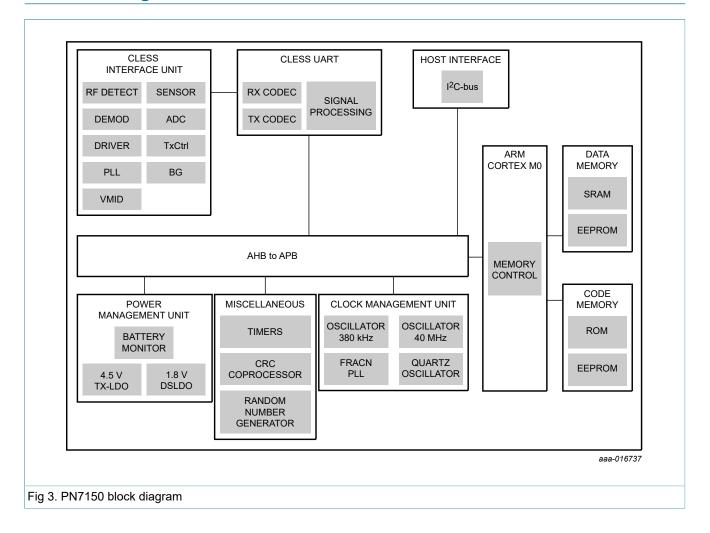

### 10 Block diagram

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

### 11 Pinning information

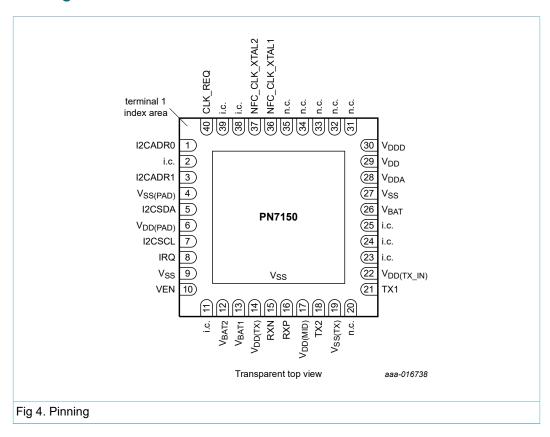

### 11.1 Pinning HVQFN40

Table 5. Pin description

| Symbol               | Pin | Type <sup>[1]</sup> | Refer                | Description                                                   |

|----------------------|-----|---------------------|----------------------|---------------------------------------------------------------|

| I2CADR0              | 1   | I                   | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus address 0                                |

| i.c.                 | 2   | -                   | -                    | internally connected; must be connected to GND                |

| I2CADR1              | 3   | I                   | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus address 1                                |

| V <sub>SS(PAD)</sub> | 4   | G                   | n/a                  | pad ground                                                    |

| I2CSDA               | 5   | I/O                 | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus data line                                |

| $V_{DD(PAD)}$        | 6   | Р                   | n/a                  | pad supply voltage                                            |

| I2CSCL               | 7   | I                   | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus clock line                               |

| IRQ                  | 8   | 0                   | V <sub>DD(PAD)</sub> | interrupt request output                                      |

| V <sub>SS</sub>      | 9   | G                   | n/a                  | ground                                                        |

| VEN                  | 10  | I                   | $V_{BAT}$            | reset pin. Set the device in Hard Power Down                  |

| i.c.                 | 11  | -                   | -                    | internally connected; leave open                              |

| $V_{BAT2}$           | 12  | Р                   | n/a                  | battery supply voltage; must be connected to V <sub>BAT</sub> |

| V <sub>BAT1</sub>    | 13  | Р                   | n/a                  | TXLDO input supply voltage                                    |

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

| Symbol                 | Pin | Type <sup>[1]</sup> | Refer                | Description                                                                |

|------------------------|-----|---------------------|----------------------|----------------------------------------------------------------------------|

| $V_{DD(TX)}$           | 14  | Р                   | n/a                  | transmitter supply voltage                                                 |

| RXN                    | 15  | I                   | $V_{DD}$             | negative receiver input                                                    |

| RXP                    | 16  | I                   | $V_{DD}$             | positive receiver input                                                    |

| $V_{DD(MID)}$          | 17  | Р                   | n/a                  | receiver reference input supply voltage                                    |

| TX2                    | 18  | 0                   | $V_{DD(TX)}$         | antenna driver output                                                      |

| V <sub>SS(TX)</sub>    | 19  | G                   | n/a                  | contactless transmitter ground                                             |

| n.c.                   | 20  | -                   | -                    | not connected                                                              |

| TX1                    | 21  | 0                   | $V_{DD(TX)}$         | antenna driver output                                                      |

| V <sub>DD(TX_IN)</sub> | 22  | Р                   | n/a                  | transmitter input supply voltage; must be connected to V <sub>DD(TX)</sub> |

| i.c.                   | 23  | -                   | -                    | internally connected; leave open                                           |

| i.c.                   | 24  | -                   | -                    | internally connected; leave open                                           |

| i.c.                   | 25  | -                   | -                    | internally connected; leave open                                           |

| $V_{BAT}$              | 26  | Р                   | n/a                  | battery supply voltage                                                     |

| V <sub>SS</sub>        | 27  | G                   | n/a                  | ground                                                                     |

| $V_{DDA}$              | 28  | Р                   | n/a                  | analog supply voltage; must be connected to $V_{\text{DD}}$                |

| $V_{DD}$               | 29  | Р                   | n/a                  | supply voltage                                                             |

| $V_{DDD}$              | 30  | Р                   | n/a                  | digital supply voltage; must be connected to V <sub>DD</sub>               |

| n.c.                   | 31  | -                   | -                    | not connected                                                              |

| n.c.                   | 32  | -                   | -                    | not connected                                                              |

| n.c.                   | 33  | -                   | -                    | not connected                                                              |

| n.c.                   | 34  | -                   | -                    | not connected                                                              |

| n.c.                   | 35  | -                   | -                    | not connected                                                              |

| NFC_CLK_XTAL1          | 36  | I                   | $V_{DD}$             | oscillator input/PLL input                                                 |

| NFC_CLK_XTAL2          | 37  | 0                   | $V_{DD}$             | oscillator output                                                          |

| i.c.                   | 38  | -                   | -                    | internally connected; leave open                                           |

| i.c.                   | 39  | -                   | -                    | internally connected; leave open                                           |

| CLK_REQ                | 40  | 0                   | V <sub>DD(PAD)</sub> | clock request pin                                                          |

|                        | _   |                     | -                    | · ·                                                                        |

[1] P = power supply

G = ground

I = input

O = output

I/O = input/output

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

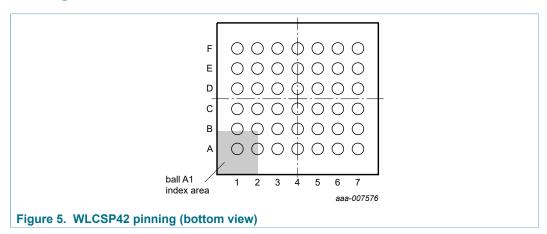

### 11.2 Pinning WLCSP42

Table 6. WLCSP package marking (top view)

| Symbol               | Pin | Type <sup>[1]</sup> | Refer         | Description                                                         |

|----------------------|-----|---------------------|---------------|---------------------------------------------------------------------|

| $V_{BAT2}$           | A1  | Р                   | n/a           | battery supply voltage; to be connected to V <sub>BAT</sub>         |

| i.c.                 | A2  | -                   | -             | internally connected; leave open                                    |

| V <sub>BAT1</sub>    | А3  | Р                   | n/a           | TXLDO input supply voltage                                          |

| RXN                  | A4  | I                   | $V_{DD}$      | negative receiver input                                             |

| $V_{DD(MID)}$        | A5  | Р                   | n/a           | receiver reference input supply voltage                             |

| TX2                  | A6  | 0                   | $V_{DD(TX)}$  | antenna driver output                                               |

| TX1                  | A7  | 0                   | $V_{DD(TX)}$  | antenna driver output                                               |

| V <sub>SS</sub>      | B1  | G                   | n/a           | ground                                                              |

| V <sub>SS</sub>      | B2  | G                   | n/a           | ground                                                              |

| $V_{DD(TX)}$         | В3  | Р                   | n/a           | transmitter supply voltage                                          |

| RXP                  | B4  | I                   | $V_{DD}$      | positive receiver input                                             |

| V <sub>SS</sub>      | B5  | G                   | n/a           | ground                                                              |

| V <sub>SS(TX)</sub>  | B6  | G                   | n/a           | contactless transmitter ground                                      |

| $V_{DD(TX\_IN)}$     | В7  | Р                   | n/a           | transmitter input supply voltage; must be connected to $V_{DD(TX)}$ |

| IRQ                  | C1  | 0                   | $V_{DD(PAD)}$ | interrupt request output                                            |

| V <sub>DD(PAD)</sub> | C2  | Р                   | n/a           | pad supply voltage                                                  |

| VEN                  | СЗ  | I                   | $V_{BAT}$     | reset pin. Set the device in Hard Power Down                        |

| V <sub>SS</sub>      | C4  | G                   | n/a           | power ball. Shall be connected to ground for dissipation            |

| V <sub>SS</sub>      | C5  | G                   | n/a           | power ball. Shall be connected to ground for dissipation            |

| i.c.                 | C6  | -                   | -             | internally connected; leave open                                    |

| i.c.                 | C7  | -                   | -             | internally connected; leave open                                    |

| I2CSCL               | D1  | I                   | $V_{DD(PAD)}$ | I <sup>2</sup> C-bus clock line                                     |

| I2CSDA               | D2  | I/O                 | $V_{DD(PAD)}$ | I <sup>2</sup> C-bus data line                                      |

| CLK_REQ              | D3  | 0                   | $V_{DD(PAD)}$ | clock request pin                                                   |

| i.c.                 | D4  | -                   | -             | internally connected; leave open                                    |

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

| Symbol               | Pin | Type <sup>[1]</sup> | Refer                | Description                                                  |

|----------------------|-----|---------------------|----------------------|--------------------------------------------------------------|

| i.c.                 | D5  | -                   | -                    | internally connected; leave open                             |

| $V_{DDD}$            | D6  | Р                   | n/a                  | digital supply voltage; must be connected to V <sub>DD</sub> |

| V <sub>BAT</sub>     | D7  | Р                   | n/a                  | battery supply voltage                                       |

| V <sub>SS(PAD)</sub> | E1  | G                   | n/a                  | pad ground                                                   |

| I2CADR1              | E2  | I                   | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus address 1                               |

| i.c.                 | E3  | -                   | -                    | internally connected; leave open                             |

| NFC_CLK_XTAL1        | E4  | I                   | $V_{DD}$             | oscillator input/PLL input                                   |

| i.c.                 | E5  | -                   | -                    | internally connected; leave open                             |

| i.c.                 | E6  | -                   | -                    | internally connected; leave open                             |

| $V_{DD}$             | E7  | Р                   | n/a                  | LDO output supply voltage                                    |

| I2CADR0              | F1  | I                   | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus address 0                               |

| i.c.                 | F2  | -                   | -                    | internally connected; must be connected to GND               |

| NFC_CLK_XTAL2        | F3  | 0                   | $V_{DD}$             | oscillator output                                            |

| i.c.                 | F4  | -                   | -                    | internally connected; leave open                             |

| i.c.                 | F5  | -                   | -                    | internally connected; must be connected to GND               |

| i.c.                 | F6  | -                   | -                    | internally connected; leave open                             |

| i.c.                 | F7  | -                   | -                    | internally connected; leave open                             |

<sup>[1]</sup> P = power supply

G = ground

I = input

O = output

I/O = input/output

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

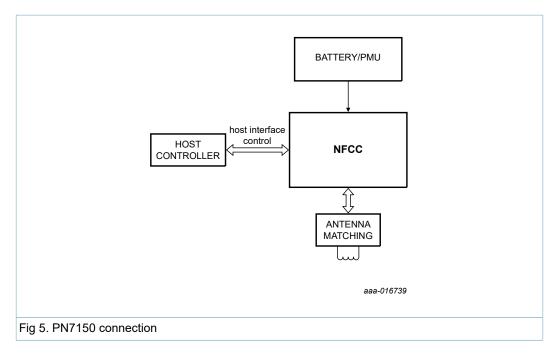

### 12 Functional description

PN7150 can be connected on a host controller through I<sup>2</sup>C-bus. The logical interface towards the host baseband is NCI-compliant [2] with additional command set for NXPspecific product features. This IC is fully user controllable by the firmware interface described in [5].

Moreover, PN7150 provides flexible and integrated power management unit in order to preserve energy supporting Power Off mode.

In the following chapters you will find also more details about PN7150 with references to very useful application note such as:

- PN7150 User Manual ([5]): User Manual describes the software interfaces (API) based on the NFC forum NCI standard. It does give full description of all the NXP NCI extensions coming in addition to NCI standard ([2]).

- PN7150 Hardware Design Guide ([6]): Hardware Design Guide provides an overview on the different hardware design options offered by the IC and provides guidelines on how to select the most appropriate ones for a given implementation. In particular, this document highlights the different chip power states and how to operate them in order to minimize the average NFC-related power consumption so to enhance the battery lifetime.

- PN7150 Antenna and Tuning Design Guide ([7]): Antenna and Tuning Design Guide provides some guidelines regarding the way to design an NFC antenna for the PN7150 chip. It also explains how to determine the tuning/matching network to place between this antenna and the PN7150. Standalone antenna performances evaluation and final RF system validation (PN7150 + tuning/matching network + NFC antenna within its final environment) are also covered by this document.

- PN7150 Low-Power Mode Configuration ([10]): Low-Power Mode Configuration documentation provides guidance on how PN7150 can be configured in order to reduce current consumption by using Low-power polling mode

317440

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

**Important:** To avoid data corruption inside the EEPROM memory, make sure to follow these rules:

- Prevent re-applying RF settings configuration when not required (different possibilities

of implementation exist depending on the integration environment, please contact NXP

support for more details).

- Insure RF settings configuration is not interrupted (no interruption between related CORE\_SET\_CONFIG\_CMD and CORE\_SET\_CONFIG\_RSP).

- Split the RF settings configuration into several CORE\_SET\_CONFIG\_CMD to limit

the time for the FW to treat this command. Only one transferred RF parameter via

the CORE\_SET\_CONFIG\_CMD takes approximately 2.7ms. 5.4ms in the specific

case where the RF parameter resides in two separated Flash memory blocks, which

increase the probability for an interruption between CORE\_SET\_CONFIG\_CMD and

CORE\_SET\_CONFIG\_RSP.

- It must be ensured that the RF settings configuration will not be interrupted due to a power off or hardware reset. Once the memory is corrupted, the IC cannot recover from this stage and cannot be used anymore.

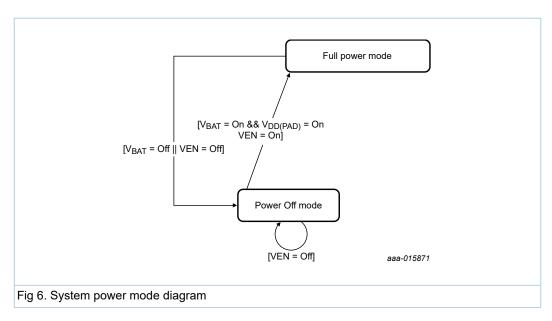

#### 12.1 System modes

#### 12.1.1 System power modes

PN7150 is designed in order to enable the different power modes from the system.

2 power modes are specified: Full power mode and Power Off mode.

Table 7. System power modes description

| System power mode Description |                                                                                                                                  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Full power mode               | the main supply ( $V_{BAT}$ ) as well as the host interface supply ( $V_{DD(PAD)}$ ) is available, all use cases can be executed |  |  |  |  |

| Power Off mode                | the system is kept Hard Power Down (HPD)                                                                                         |  |  |  |  |

PN7150

All information provided in this document is subject to legal disclaimers

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Table 6 summarizes the system power mode of the PN7150 depending on the status of the external supplies available in the system:

Table 8. System power modes configuration

| V <sub>BAT</sub> | VEN | Power mode      |

|------------------|-----|-----------------|

| Off              | X   | Power Off mode  |

| On               | Off | Power Off mode  |

| On               | On  | Full power mode |

Depending on power modes, some application states are limited:

Table 9. System power modes description

| System power mode | Allowed communication modes              |

|-------------------|------------------------------------------|

| Power Off mode    | no communication mode available          |

| Full power mode   | Reader/Writer, Card Emulation, P2P modes |

#### **12.1.2 PN7150 power states**

Next to system power modes defined by the status of the power supplies, the power states include the logical status of the system thus extend the power modes.

4 power states are specified: Monitor, Hard Power Down (HPD), Standby, Active.

Table 10. PN7150 power states

| Power state name | Description                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Monitor          | The PN7150 is supplied by $V_{BAT}$ which voltage is below its programmable critical level, VEN voltage > 1.1 V and the Monitor state is enabled. The system power mode is Power Off mode. |

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

| Power state name | Description                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hard Power Down  | The PN7150 is supplied by $V_{BAT}$ which voltage is above its programmable critical level when Monitor state is enabled and PN7150 is kept in Hard Power Down (VEN voltage is kept low by host or SW programming) to have the minimum power consumption. The system power mode is in Power Off.                                                                          |

| Standby          | The PN7150 is supplied by $V_{BAT}$ which voltage is above its programmable critical level when the Monitor state is enabled, VEN voltage is high (by host or SW programming) and minimum part of PN7150 is kept supplied to enable configured wake-up sources which allow to switch to Active state; RF field, Host interface. The system power mode is Full power mode. |

| Active           | The PN7150 is supplied by $V_{BAT}$ which voltage is above its programmable critical level when Monitor state is enabled, VEN voltage is high (by host or SW programming) and the PN7150 internal blocks are supplied. 3 functional modes are defined: Idle, Target and Initiator. The system power mode is Full power mode.                                              |

At application level, the PN7150 will continuously switch between different states to optimize the current consumption (polling loop mode). Refer to Table 1 for targeted current consumption in here described states.

The PN7150 is designed to allow the host controller to have full control over its functional states, thus of the power consumption of the PN7150 based NFC solution and possibility to restrict parts of the PN7150 functionality.

#### 12.1.2.1 Monitor state

In Monitor state, the PN7150 will exit it only if the battery voltage recovers over the critical level. Battery voltage monitor thresholds show hysteresis behavior as defined in Table 27

#### 12.1.2.2 Hard Power Down (HPD) state

The Hard Power Down state is entered when  $V_{DD(PAD)}$  and  $V_{BAT}$  are high by setting VEN voltage < 0.4 V. As these signals are under host control, the PN7150 has no influence on entering or exiting this state.

#### 12.1.2.3 Standby state

Active state is PN7150's default state after boot sequence in order to allow a quick configuration of PN7150. It is recommended to change the default state to Standby state after first boot in order to save power. PN7150 can switch to Standby state autonomously (if configured by host).

In this state, PN7150 most blocks including CPU are no more supplied. Number of wakeup sources exist to put PN7150 into Active state:

- I<sup>2</sup>C-bus interface wake-up event

- · Antenna RF level detector

- Internal timer event when using polling loop (380 kHz Low-power oscillator is enabled)

If wake-up event occurs, PN7150 will switch to Active state. Any further operation depends on software configuration and/or wake-up source.

PN7150

All information provided in this document is subject to legal disclaimers.

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

#### **12.1.2.4** Active state

Within the Active state, the system is acting as an NFC device. The device can be in 3 different functional modes: Idle, Poller and Target.

Table 11. Functional modes in active state

| Functional modes | Description                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------|

| Idle             | the PN7150 is active and allows host interface communication. The RF interface is not activated. |

| Listener         | the PN7150 is active and is configured for listening to external device.                         |

| Poller           | the PN7150 is active and is configured in Poller mode. It polls external device                  |

|  | Pol | ler | m | od | le |

|--|-----|-----|---|----|----|

|--|-----|-----|---|----|----|

In this mode, PN7150 is acting as Reader/Writer or NFC Initiator, searching for or communicating with passive tags or NFC target. Once RF communication has ended, PN7150 will switch to active battery mode (that is, switch off RF transmitter) to save energy. Poller mode shall be used with 2.7 V <  $\rm V_{BAT}$  < 5.5 V and VEN voltage > 1.1 V. Poller mode shall not be used with  $\rm V_{BAT}$  < 2.7 V.  $\rm V_{DD(PAD)}$  is within its operational range (see Table 1).

#### Listener mode

In this mode, PN7150 is acting as a card or as an NFC Target. Listener mode shall be used with 2.3 V <  $V_{BAT}$  < 5.5 V and VEN voltage > 1.1 V.

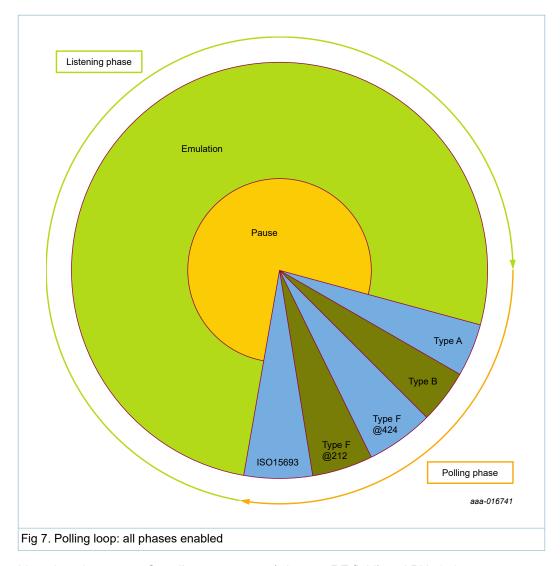

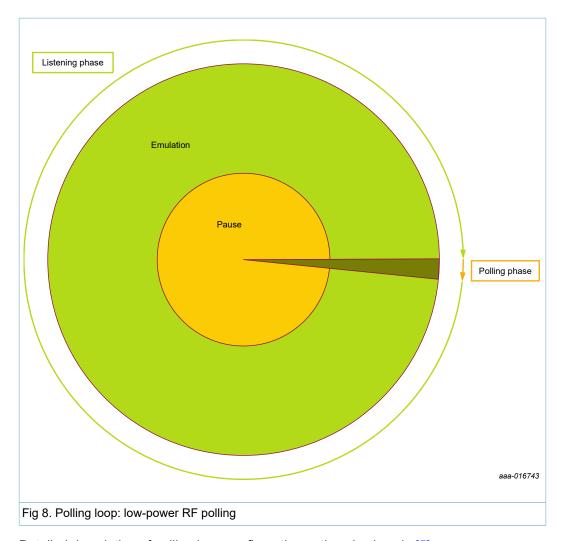

#### 12.1.2.5 Polling loop

The polling loop will sequentially set PN7150 in different power states (Active or Standby). All RF technologies supported by PN7150 can be independently enabled within this polling loop.

There are 2 main phases in the polling loop:

- Listening phase. The PN7150 can be in Standby power state or Listener mode

- Polling phase. The PN7150 is in Poller mode

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Listening phase uses Standby power state (when no RF field) and PN7150 goes to Listener mode when RF field is detected. When in Polling phase, PN7150 goes to Poller mode.

To further decrease the power consumption when running the polling loop, PN7150 features a low-power RF polling. When PN7150 is in Polling phase instead of sending regularly RF command, PN7150 senses with a short RF field duration if there is any NFC Target or card/tag present. If yes, then it goes back to standard polling loop. With 500 ms (configurable duration, see [5]) listening phase duration, the average power consumption is around 150  $\mu$ A.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Detailed description of polling loop configuration options is given in [5].

#### 12.2 Microcontroller

PN7150 is controlled via an embedded ARM Cortex-M0 microcontroller core.

PN7150 features integrated in firmware are referenced in [5].

#### 12.3 Host interface

PN7150 provides the support of an I<sup>2</sup>C-bus Slave Interface, up to 3.4 MBaud.

The host interface is waken-up on I<sup>2</sup>C-bus address.

To enable and ensure data flow control between PN7150 and host controller, additionally a dedicated interrupt line IRQ is provided which Active state is programmable. See [5] for more information.

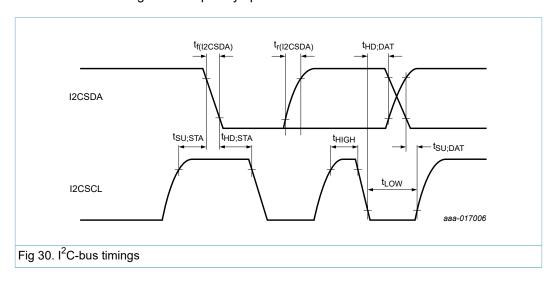

#### 12.3.1 I<sup>2</sup>C-bus interface

The I<sup>2</sup>C-bus interface implements a slave I<sup>2</sup>C-bus interface with integrated shift register, shift timing generation and slave address recognition.

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

$I^2$ C-bus Standard mode (100 kHz SCL), Fast mode (400 kHz SCL) and High-speed mode (3.4 MHz SCL) are supported.

The mains hardware characteristics of the I<sup>2</sup>C-bus module are:

- Support slave I<sup>2</sup>C-bus

- Standard, Fast and High-speed modes supported

- Wake-up of PN7150 on its address only

- Serial clock synchronization can be used by PN7150 as a handshake mechanism to suspend and resume serial transfer (clock stretching)

The  $I^2$ C-bus interface module meets the  $I^2$ C-bus specification [4] except General call, 10-bit addressing and Fast mode Plus (Fm+).

### 12.3.1.1 I<sup>2</sup>C-bus configuration

The I<sup>2</sup>C-bus interface shares four pins with I<sup>2</sup>C-bus interface also supported by PN7150. When I<sup>2</sup>C-bus is configured in EEPROM settings, functionality of interface pins changes to one described in Table 10.

Table 12. Functionality for I<sup>2</sup>C-bus interface

| Pin name              | Functionality                   |

|-----------------------|---------------------------------|

| I2CADR0               | I <sup>2</sup> C-bus address 0  |

| I2CADR1               | I <sup>2</sup> C-bus address 1  |

| I2CSCL <sup>[1]</sup> | I <sup>2</sup> C-bus clock line |

| I2CSDA <sup>[1]</sup> | I <sup>2</sup> C-bus data line  |

[1] I2CSCL and I2CSDA are not fail-safe and  $V_{DD(pad)}$  shall always be available when using the SCL and SDA lines connected to these pins.

PN7150 supports 7-bit addressing mode. Selection of the I<sup>2</sup>C-bus address is done by 2-pin configurations on top of a fixed binary header: 0, 1, 0, 1, 0, 12CADR1, I2CADR0, R/W.

Table 13. I<sup>2</sup>C-bus interface addressing

| I2CADR1 | I2CADR0 | I <sup>2</sup> C-bus address<br>(R/W = 0, write) | I <sup>2</sup> C-bus address<br>(R/W = 1, read) |

|---------|---------|--------------------------------------------------|-------------------------------------------------|

| 0       | 0       | 0x50                                             | 0x51                                            |

| 0       | 1       | 0x52                                             | 0x53                                            |

| 1       | 0       | 0x54                                             | 0x55                                            |

| 1       | 1       | 0x56                                             | 0x57                                            |

#### 12.4 PN7150 clock concept

There are 4 different clock sources in PN7150:

- 27.12 MHz clock coming either/or from:

- Internal oscillator for 27.12 MHz crystal connection

- Integrated PLL unit which includes a 1 GHz VCO, taking is reference clock on pin NFC\_CLK\_XTAL1

- 13.56 MHz RF clock recovered from RF field

- Low-power oscillator 40 MHz

PN7150

All information provided in this document is subject to legal disclaimers

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

• Low-power oscillator 380 kHz

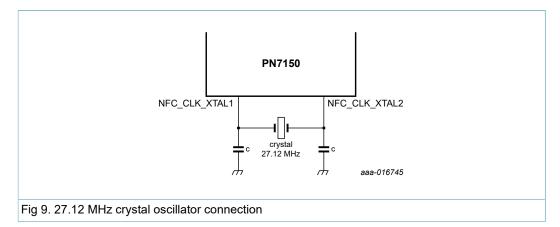

#### 12.4.1 27.12 MHz quartz oscillator

When enabled, the 27.12 MHz quartz oscillator applied to PN7150 is the time reference for the RF front end when PN7150 is behaving in Reader mode or NFCIP-1 initiator.

Therefore stability of the clock frequency is an important factor for reliable operation. It is recommended to adopt the circuit shown in Figure 9.

Table 12 describes the levels of accuracy and stability required on the crystal.

**Table 14. Crystal requirements**

| Symbol            | Parameter                    | Conditions                                        |     | Min  | Тур   | Max  | Unit |

|-------------------|------------------------------|---------------------------------------------------|-----|------|-------|------|------|

| f <sub>xtal</sub> | crystal frequency            | ISO/IEC and FCC compliancy                        |     | _    | 27.12 | -    | MHz  |

| $\Delta f_{xtal}$ | crystal frequency accuracy   | full operating range                              | [1] | -100 | -     | +100 | ppm  |

|                   |                              | all V <sub>BAT</sub> range;T = 20<br>°C           | [1] | -50  | _     | +50  | ppm  |

|                   |                              | all temperature<br>range;V <sub>BAT</sub> = 3.6 V | [1] | -50  | -     | +50  | ppm  |

| ESR               | equivalent series resistance |                                                   |     | _    | 50    | 100  | Ω    |

| C <sub>L</sub>    | load capacitance             |                                                   |     | -    | 10    | -    | pF   |

| P <sub>xtal</sub> | crystal power dissipation    |                                                   |     | -    | -     | 100  | μW   |

[1] This requirement is according to FCC regulations requirements. To meet only ISO/IEC 14443 and ISO/IEC 18092, then ± 14 kHz apply.

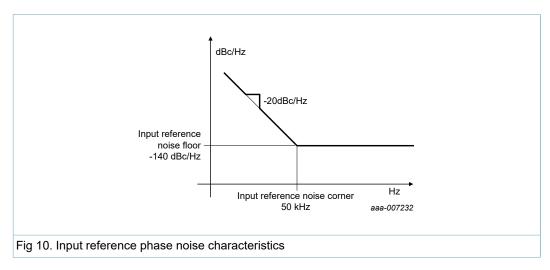

#### 12.4.2 Integrated PLL to make use of external clock

When enabled, the PLL is designed to generate a low noise 27.12 MHz for an input clock 13 MHz, 19.2 MHz, 24 MHz, 26 MHz, 38.4 MHz and 52 MHz.

The 27.12 MHz of the PLL is used as the time reference for the RF front end when PN7150 is behaving in Reader mode or ISO/IEC 18092 Initiator as well as in Target when configured in Active Communication mode.

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

The input clock on NFC\_CLK\_XTAL1 shall comply with the following phase noise requirements for the following input frequency: 13 MHz, 19.2 MHz, 24 MHz, 26 MHz, 38.4 MHz and 52 MHz:

This phase noise is equivalent to an RMS jitter of 6.23 ps from 10 Hz to 1 MHz. For configuration of input frequency, refer to [9]. There are 6 pre-programmed and validated frequencies for the PLL: 13 MHz, 19.2 MHz, 24 MHz, 26 MHz, 38.4 MHz and 52 MHz.

**Table 15. PLL input requirements** Coupling: single-ended, AC coupling;

| Symbol                 | Parameter                          | Conditions                                                                      |     | Min  | Тур  | Max | Unit      |

|------------------------|------------------------------------|---------------------------------------------------------------------------------|-----|------|------|-----|-----------|

| f <sub>clk</sub>       | clock frequency                    | ISO/IEC and FCC                                                                 |     | -    | 13   | -   | MHz       |

|                        |                                    | compliancy                                                                      |     | -    | 19.2 | -   | MHz       |

|                        |                                    |                                                                                 |     | -    | 24   | -   | MHz       |

|                        |                                    |                                                                                 |     | -    | 26   | -   | MHz       |

|                        |                                    |                                                                                 |     | -    | 38.4 | -   | MHz       |

|                        |                                    |                                                                                 |     | -    | 52   | -   | MHz       |

| f <sub>i(ref)acc</sub> | reference input frequency accuracy | full operating range;frequencies<br>typical values:13 MHz, 26 MHz and<br>52 MHz | [1] | -25  | -    | +25 | ppm       |

|                        |                                    | full operating range; frequencies typical values: 19.2 MHz, 24 MHz and 38.4 MHz | [1] | -50  | -    | +50 | ppm       |

| φn                     | phase noise                        | input noise floor at 50 kHz                                                     |     | -140 | -    | -   | dB/<br>Hz |

| Sinusoidal             | shape                              |                                                                                 |     |      |      |     |           |

| V <sub>i(p-p)</sub>    | peak-to-peak input voltage         |                                                                                 |     | 0.2  | -    | 1.8 | V         |

| V <sub>i(clk)</sub>    | clock input voltage                |                                                                                 |     | 0    | -    | 1.8 | V         |

| Square sh              | ape                                | 1                                                                               |     |      |      |     |           |

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

| Symbol       | Parameter           | Conditions | Min | Тур | Max        | Unit |

|--------------|---------------------|------------|-----|-----|------------|------|

| $V_{i(clk)}$ | clock input voltage |            | 0   | -   | 1.8 ± 10 % | V    |

[1] This requirement is according to FCC regulations requirements. To meet only ISO/IEC 14443 and ISO/IEC 18092, then ± 400 ppm limits apply.

For detailed description of clock request mechanisms, refer to [5] and [6].

#### 12.4.3 Low-power 40 MHz ± 2.5 % oscillator

Low-power OSC generates a 40 MHz internal clock. This frequency is divided by two to make the system clock.

#### 12.4.4 Low-power 380 kHz oscillator

A Low Frequency Oscillator (LFO) is implemented to drive a counter (WUC) waking-up PN7150 from Standby state. This allows implementation of low-power reader polling loop at application level. Moreover, this 380 kHz is used as the reference clock for write access to EEPROM memory.

#### 12.5 Power concept

#### 12.5.1 PMU functional description

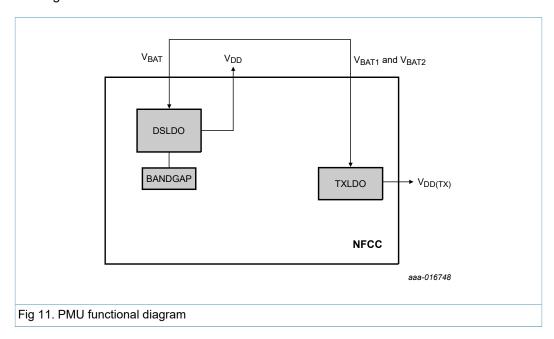

The Power Management Unit of PN7150 generates internal supplies required by PN7150 out of  $V_{BAT}$  input supply voltage:

- V<sub>DD</sub>: internal supply voltage

- V<sub>DD(TX)</sub>: output supply voltage for the RF transmitter

The Figure 11 describes the main blocks available in PMU:

PN7150

All information provided in this document is subject to legal disclaimers

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

#### 12.5.2 DSLDO: Dual Supply LDO

The input pin of the DSLDO is V<sub>BAT</sub>.

The Low drop-out regulator provides V<sub>DD</sub> required in PN7150.

#### 12.5.3 TXLDO

Transmitter voltage can be generated by internal LDO  $(V_{DD(TX)})$  or come from an external supply source  $V_{DD(TX)}$ .

The regulator has been designed to work in 2 configurations:

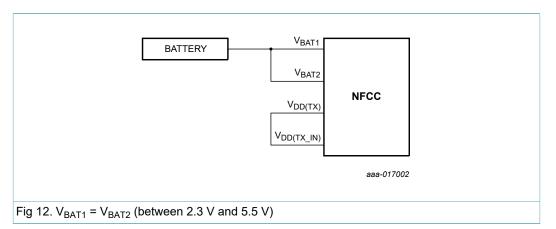

#### 12.5.3.1 Configuration 1: supply connection in case the battery is used to generate RF field

The Low drop Out Regulator has been designed to generate a 3.0 V, 3.3 V or 3.6 V supply voltage to a transmitter with a current load up to 180 mA.

The output is called  $V_{DD(TX)}$ . The input supply voltage of this regulator is a battery voltage connected to  $V_{BAT1}$  pin.

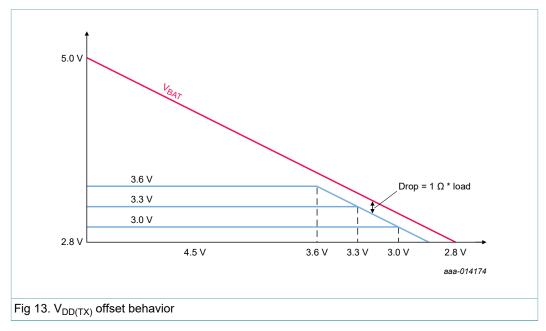

$V_{DD(TX)}$  value shall be chosen according to the minimum targeted  $V_{BAT}$  value for which reader mode shall work.

If V<sub>BAT</sub> is above 3.0 V plus the regulator voltage dropout, then V<sub>DD(TX)</sub> = 3.0 V shall be chosen:

$$V_{\text{BAT}} \ge (3.0\text{V} + 1\Omega \times \text{load}) \Rightarrow V_{\text{DD(TX)}} = 3.0\text{V}$$

$$3.0 \text{V} \ge V_{\text{BAT}} \ge 2.3 \text{V} \Rightarrow V_{\text{DD(TX)}} = V_{\text{BAT}} - 1\Omega \times \text{load}$$

• If  $V_{BAT}$  is above 3.3 V plus the regulator voltage dropout, then  $V_{DD(TX)}$  = 3.3 V shall be chosen:

$$V_{\text{BAT}} \ge (3.3\text{V} + 1\Omega \times \text{load}) \Rightarrow V_{\text{DD(TX)}} = 3.3\text{V}$$

$$3.3\text{V} \ge V_{\text{BAT}} \ge 2.3\text{V} \Rightarrow V_{\text{DD(TX)}} = V_{\text{BAT}} - 1\Omega \times \text{load}$$

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

• If  $V_{BAT}$  is above 3.6 V plus the regulator voltage dropout, then  $V_{DD(TX)}$  = 3.6 V shall be chosen:

$$V_{\text{BAT}} \ge (3.6\text{V} + 1\Omega \times \text{load}) \Rightarrow V_{\text{DD(TX)}} = 3.6\text{V}$$

$$3.6V \ge V_{\text{BAT}} \ge 2.3V \Rightarrow V_{\text{DD(TX)}} = V_{\text{BAT}} - 1\Omega \times \text{load}$$

Figure 13 shows  $V_{DD(TX)}$  offset disabled behavior for both cases of  $V_{DD(TX)}$  programmed for 3.0 V, 3.3 V or 3.6 V.

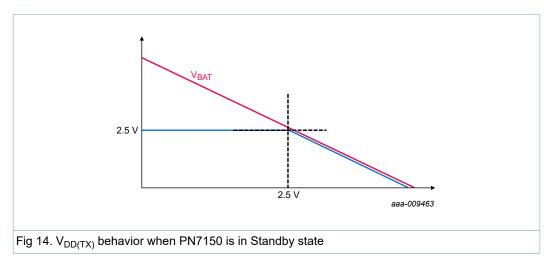

In Standby state, whenever  $V_{DD(TX)}$  is configured for 3.0 V, 3.3 V or 3.6 V,  $V_{DD(TX)}$  is regulated at 2.5 V.

Figure 14 shows the case where the PN7150 is in standby state.

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

**Product data sheet**

**COMPANY PUBLIC**

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

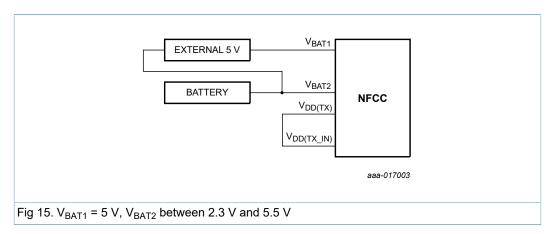

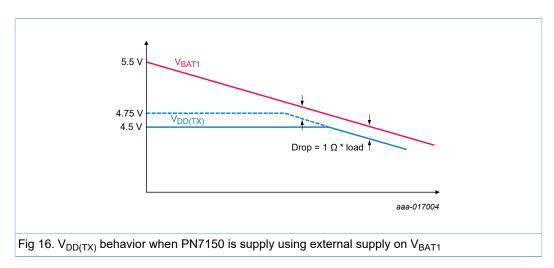

# 12.5.3.2 Configuration 2: supply connection in case a 5 V supply is used to generate RF field with the use of TXLDO

TXLDO has also the possibility to generate 4.75 V or 4.5 V supply in case the supply of this regulator is an external 5 V supply.

Figure 16 shows the behavior of  $V_{DD(TX)}$  depending on  $V_{BAT1}$  value.

#### 12.5.3.3 TXLDO limiter

The TXLDO includes a current limiter to avoid too high current within TX1, TX2 when in reader or initiator modes.

The current limiter block compares an image of the TXLDO output current to a reference. Once the reference is reached, the output current gets limited which is equivalent to a typical output current of 220 mA whatever  $V_{BAT}$  or  $V_{BAT1}$  value in the range of 2.3 V to 5.5 V.

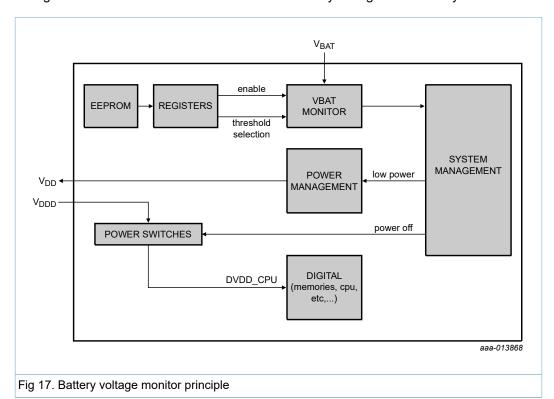

#### 12.5.4 Battery voltage monitor

The PN7150 features low-power  $V_{BAT}$  voltage monitor which protects mobile device battery from being discharged below critical levels. When  $V_{BAT}$  voltage goes below

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

$V_{BATcritical}$  threshold, then the PN7150 goes in Monitor state. Refer to Figure 17 for principle schematic of the battery monitor.

The battery voltage monitor is enabled via an EEPROM setting.

At the first start-up, V<sub>BAT</sub> voltage monitor functionality is OFF and then enabled if properly configured in EEPROM. The PN7150 monitors battery voltage continuously.

The value of the critical level can be configured to 2.3 V or 2.75 V by an EEPROM setting. This value has a typical hysteresis around 150 mV.

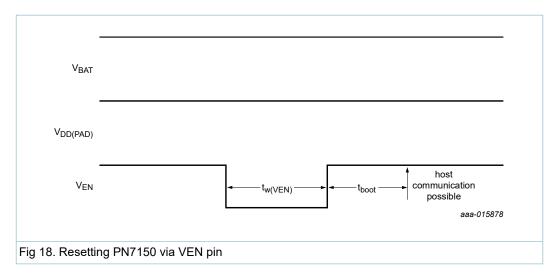

#### 12.6 Reset concept

#### 12.6.1 Resetting PN7150

To enter reset, there are 2 ways:

- Pulling VEN voltage low (Hard Power Down state)

- if V<sub>BAT</sub> monitor is enabled: lowering V<sub>BAT</sub> below the monitor threshold (Monitor state, if VEN voltage is kept above 1.1 V)

Reset means resetting the embedded FW execution and the registers values to their default values. Part of these default values is defined from EEPROM data loaded values, others are hardware defined. See [5] to know which ones are accessible to tune PN7150 to the application environment.

To get out of reset:

• Pulling VEN voltage high with  $V_{BAT}$  above  $V_{BAT}$  monitor threshold if enabled Figure 18 shows reset done via VEN pin.

PN7150

All information provided in this document is subject to legal disclaimers

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

See <u>Section 16.2.2</u> for the timings values.

#### 12.6.2 Power-up sequences

There are 2 different supplies for PN7150. PN7150 allows these supplies to be set up independently, therefore different power-up sequences have to be considered.

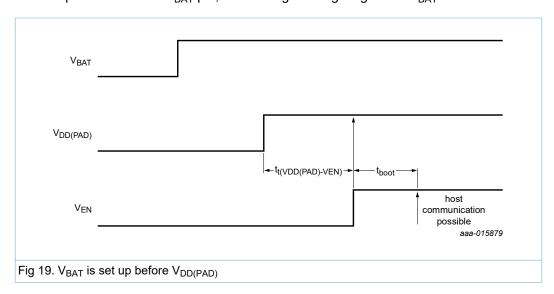

#### 12.6.2.1 V<sub>BAT</sub> is set up before V<sub>DD(PAD)</sub>

This is at least the case when  $V_{BAT}$  pin is directly connected to the battery and when PN7150  $V_{BAT}$  is always supplied as soon the system is supplied.

As VEN pin is referred to V<sub>BAT</sub> pin, VEN voltage shall go high after V<sub>BAT</sub> has been set.

See Section 16.2.3 for the timings values.

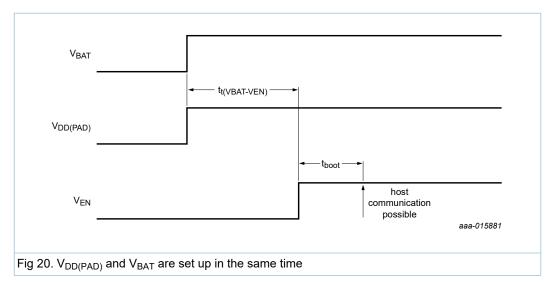

#### 12.6.2.2 $V_{DD(PAD)}$ and $V_{BAT}$ are set up in the same time

It is at least the case when  $V_{BAT}$  pin is connected to a PMU/regulator which also supply  $V_{DD(PAD)}$ .

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

See <u>Section 16.2.3</u> for the timings values.

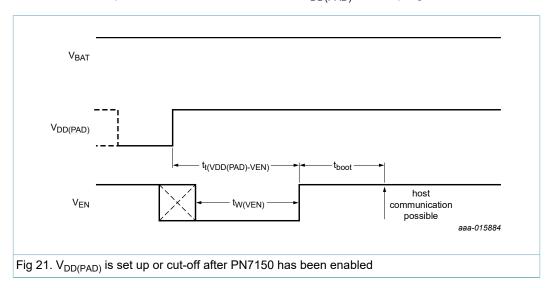

#### 12.6.2.3 PN7150 has been enabled before V<sub>DD(PAD)</sub> is set up or before V<sub>DD(PAD)</sub> has been cut

This can be the case when V<sub>BAT</sub> pin is directly connected to the battery and when V<sub>DD(PAD)</sub> is generated from a PMU. When the battery voltage is too low, then the PMU might no more be able to generate V<sub>DD(PAD)</sub>. When the device gets charged again, then V<sub>DD(PAD)</sub> is set up again.

As the pins to select the interface are biased from  $V_{\text{DD(PAD)}}$ , when  $V_{\text{DD(PAD)}}$  disappears the pins might not be correctly biased internally and the information might be lost. Therefore it is required to make the IC boot after V<sub>DD(PAD)</sub> is set up again.

See Section 16.2.3 for the timings values.

High performance NFC controller with integrated firmware, supporting all NFC Forum modes

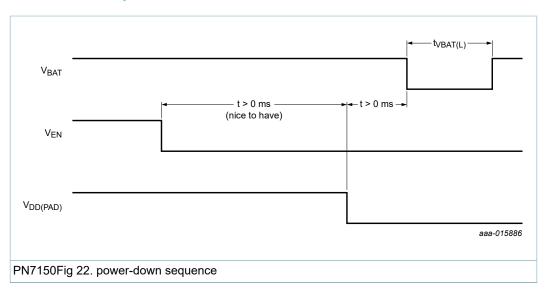

#### 12.6.3 Power-down sequence

#### 12.7 Contactless Interface Unit

PN7150 supports various communication modes at different transfer speeds and modulation schemes. The following chapters give more detailed overview of selected communication modes.

**Remark:** all indicated modulation index and modes in this chapter are system parameters. This means that beside the IC settings a suitable antenna tuning is required to achieve the optimum performance.

#### 12.7.1 Reader/Writer communication modes

Generally 5 Reader/Writer communication modes are supported:

- PCD Reader/Writer for ISO/IEC 14443 type A and for MIFARE Classic

- PCD Reader/Writer for Jewel/Topaz

- PCD Reader/Writer for FeliCa

- PCD Reader/Writer for ISO/IEC 14443B

- VCD Reader/Writer for ISO/IEC 15693/ICODE

# 12.7.1.1 Communication mode for ISO/IEC 14443 type A, MIFARE Classic and Jewel/Topaz PCD

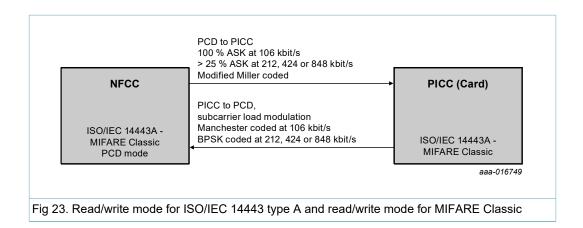

The ISO/IEC 14443A and MIFARE Classic PCD communication mode is the general reader to card communication scheme according to the ISO/IEC 14443A specification. This modulation scheme is as well used for communications with Jewel/Topaz cards.

Figure 23 describes the communication on a physical level, the communication table describes the physical parameters (the numbers take the antenna effect on modulation depth for higher data rates).

PN7150

All information provided in this document is subject to legal disclaimers.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Table 16. Communication overview for ISO/IEC 14443 type A and read/write mode for MIFARE Classic

| Communication direction               |                           | ISO/IEC 14443A/<br>MIFARE<br>Classic/<br>Jewel/ Topaz | ISO/IEC 14443A             | higher transfer sp            | peeds                      |

|---------------------------------------|---------------------------|-------------------------------------------------------|----------------------------|-------------------------------|----------------------------|

|                                       | Transfer speed            | 106 kbit/s                                            | 212 kbit/s                 | 424 kbit/s                    | 848 kbit/s                 |

|                                       | Bit length                | (128/13.56) µs                                        | (64/13.56) μs              | (32/13.56) μs                 | (16/13.56) µs              |

| PN7150 → PICC                         |                           |                                                       | 1                          | '                             |                            |

| (data sent by PN7150 to a card)       | modulation on PN7150 side | 100 % ASK                                             | > 25 % ASK                 | > 25 % ASK                    | > 25 % ASK                 |

|                                       | bit coding                | Modified Miller                                       | Modified Miller            | Modified Miller               | Modified Miller            |

| PICC → PN7150                         |                           |                                                       | 1                          | ,                             |                            |

| (data received by PN7150 from a card) | modulation on PICC side   | subcarrier load<br>modulation                         | subcarrier load modulation | subcarrier load<br>modulation | subcarrier load modulation |

|                                       | subcarrier<br>frequency   | 13.56 MHz/16                                          | 13.56 MHz/16               | 13.56 MHz/16                  | 13.56 MHz/16               |

|                                       | bit coding                | Manchester                                            | BPSK                       | BPSK                          | BPSK                       |

The contactless coprocessor and the on-chip CPU of PN7150 handle the complete ISO/IEC 14443A and MIFARE Classic RF-protocol, nevertheless a dedicated external host has to handle the application layer communication.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

#### 12.7.1.2 FeliCa PCD communication mode

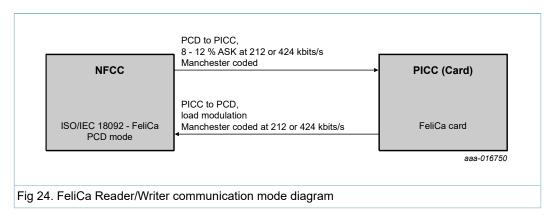

The FeliCa communication mode is the general Reader/Writer to card communication scheme according to the FeliCa specification. Figure 24 describes the communication on a physical level, the communication overview describes the physical parameters.

Table 17. Overview for FeliCa Reader/Writercommunication mode

| Communication direction               |                           | FeliCa          | FeliCa higher transfer speeds |

|---------------------------------------|---------------------------|-----------------|-------------------------------|

|                                       | Transfer speed            | 212 kbit/s      | 424 kbit/s                    |

|                                       | Bit length                | (64/13.56) μs   | (32/13.56) μs                 |

| PN7150 → PICC                         |                           |                 | ,                             |

| (data sent by PN7150 to a card)       | modulation on PN7150 side | 8 % - 12 % ASK  | 8 % - 12 % ASK                |

|                                       | bit coding                | Manchester      | Manchester                    |

| PICC → PN7150                         |                           | '               | ,                             |

| (data received by PN7150 from a card) | modulation on PICC side   | load modulation | load modulation               |

|                                       | subcarrier frequency      | no subcarrier   | no subcarrier                 |

|                                       | bit coding                | Manchester      | Manchester                    |

The contactless coprocessor of PN7150 and the on-chip CPU handle the FeliCa protocol. Nevertheless a dedicated external host has to handle the application layer communication.

#### 12.7.1.3 ISO/IEC 14443B PCD communication mode

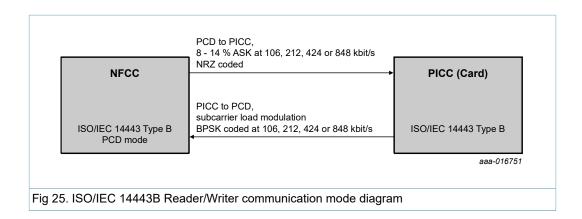

The ISO/IEC 14443B PCD communication mode is the general reader to card communication scheme according to the ISO/IEC 14443B specification. Figure 25 describes the communication on a physical level, the communication table describes the physical parameters.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Table 18. Overview for ISO/IEC 14443B Reader/Writer communication mode

| Communication                         |                           | ISO/IEC 14443B             | ISO/IEC 14443B I              | B higher transfer speeds   |                               |  |

|---------------------------------------|---------------------------|----------------------------|-------------------------------|----------------------------|-------------------------------|--|

| direction                             | Transfer speed            | 106 kbit/s                 | 212 kbit/s                    | 424 kbit/s                 | 848 kbit/s                    |  |

|                                       | Bit length                | (128/13.56) µs             | (64/13.56) μs                 | (32/13.56) µs              | (16/13.56) µs                 |  |

| PN7150 → PICC                         |                           |                            |                               |                            | ,                             |  |

| (data sent by PN7150 to a card)       | modulation on PN7150 side | 8 % - 14 % ASK             | 8 % - 14 % ASK                | 8 % - 14 % ASK             | 8 % - 14 % ASK                |  |

|                                       | bit coding                | NRZ                        | NRZ                           | NRZ                        | NRZ                           |  |

| PICC → PN7150                         |                           |                            |                               |                            | ,                             |  |

| (data received by PN7150 from a card) | modulation on PICC side   | subcarrier load modulation | subcarrier load<br>modulation | subcarrier load modulation | subcarrier load<br>modulation |  |

|                                       | subcarrier<br>frequency   | 13.56 MHz/16               | 13.56 MHz/16                  | 13.56 MHz/16               | 13.56 MHz/16                  |  |

|                                       | bit coding                | BPSK                       | BPSK                          | BPSK                       | BPSK                          |  |

The contactless coprocessor and the on-chip CPU of PN7150 handles the complete ISO/IEC 14443B RF-protocol, nevertheless a dedicated external host has to handle the application layer communication.

#### 12.7.1.4 R/W mode for NFC forum Type 5 Tag

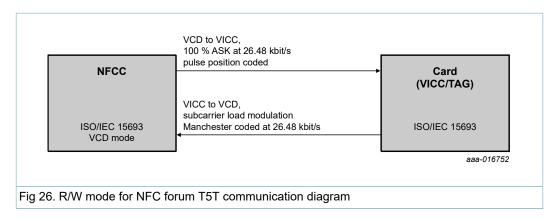

The R/W mode for NFC forum Type 5 Tag (T5T) is the general reader to card communication scheme according to the ISO/IEC 15693 specification. PN7150 will communicate with VICC (Type 5 Tag) using only the 26.48 kbit/s with single subcarrier data rate of the VICC.

#### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Figure 26 and Table 17 show the communication schemes used.

Table 19. Communication overview for NFC forum T5T R/W mode

| transfer speed            | 26.48 kbit/s                                                                                                            |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------|

| bit length                | (512/13.56) µs                                                                                                          |

| modulation on PN7150 side | 100 % ASK                                                                                                               |

| bit coding                | pulse position modulation 1 out of 4 mode                                                                               |

|                           |                                                                                                                         |

| transfer speed            | 26.48 kbit/s                                                                                                            |

| bit length                | (512/13.56) µs                                                                                                          |

| modulation on VICC side   | subcarrier load modulation                                                                                              |

| subcarrier frequency      | single subcarrier                                                                                                       |

| bit coding                | Manchester                                                                                                              |

|                           | bit length modulation on PN7150 side bit coding  transfer speed bit length modulation on VICC side subcarrier frequency |

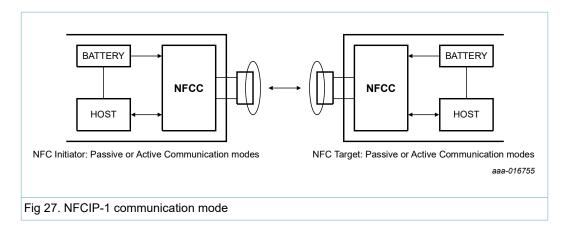

#### 12.7.2 ISO/IEC 18092, Ecma 340 NFCIP-1 communication modes

An NFCIP-1 communication takes place between 2 devices:

- NFC Initiator: generates RF field at 13.56 MHz and starts the NFCIP-1 communication.

- NFC Target: responds to NFC Initiator command either in a load modulation scheme in Passive communication mode or using a self-generated and self-modulated RF field for Active communication mode.

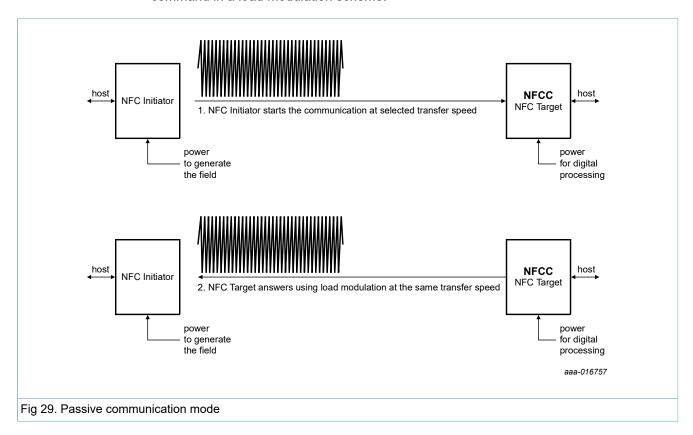

The NFCIP-1 communication differentiates between Active and Passive communication modes.

- Active communication mode means both the NFC Initiator and the NFC Target are using their own RF field to transmit data

- Passive communication mode means that the NFC Target answers to an NFC Initiator command in a load modulation scheme. The NFC Initiator is active in terms of generating the RF field.

PN7150 supports the Active Target, Active Initiator, Passive Target and Passive Initiator communication modes at the transfer speeds 106 kbit/s, 212 kbit/s and 424 kbit/s as defined in the NFCIP-1 standard.

PN7150

All information provided in this document is subject to legal disclaimers.

### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Nevertheless a dedicated external host has to handle the application layer communication.

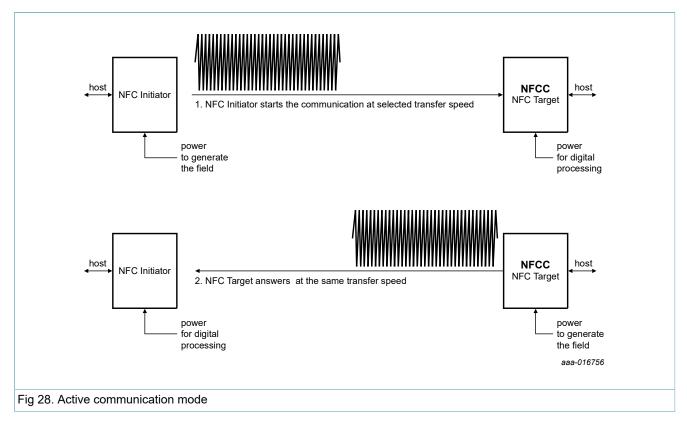

#### 12.7.2.1 ACTIVE communication mode

Active communication mode means both the NFC Initiator and the NFC Target are using their own RF field to transmit data.

The following table gives an overview of the Active communication modes:

PN7150

317440

### High performance NFC controller with integrated firmware, supporting all NFC Forum modes

Table 20. Overview for Active communication mode

| <b>Communication direction</b> |            | ISO/IEC 18092, Ecm | a 340, NFCIP-1                |                               |

|--------------------------------|------------|--------------------|-------------------------------|-------------------------------|

|                                | Baud rate  | 106 kbit/s         | 212 kbit/s                    | 424 kbit/s                    |

|                                | Bit length | (128/13.56) μs     | (64/13.56) μs                 | (32/13.56) μs                 |

| NFC Initiator → NFC Target     |            | 1                  |                               |                               |

|                                | modulation | 100 % ASK          | 8 % - 30 % ASK <sup>[1]</sup> | 8 % - 30 % ASK <sup>[1]</sup> |

|                                | bit coding | Modified Miller    | Manchester                    | Manchester                    |