# Flash-Erasable Reprogrammable CMOS PAL® Device

#### **Features**

- · Active pull-up on data input pins

- Low power version (16V8L)

- 55 mA max. commercial (10, 15, 25 ns)

- 65 mA max. industrial (10, 15, 25 ns)

- 65 mA military (15 and 25 ns)

- Standard version has low power

- 90 mA max. commercial (10, 15, 25 ns)

- 115 mA max. commercial (7 ns)

- 130 mA max. military/industrial (10, 15, 25 ns)

- CMOS Flash technology for electrical erasability and reprogrammability

- PCI-compliant

- User-programmable macrocell

- Output polarity control

- Individually selectable for registered or combinatorial operation

- Up to 16 input terms and eight outputs

- 7.5 ns com'l version 5 ns t<sub>CO</sub>

5 ns t<sub>S</sub> 7.5 ns t<sub>PD</sub>

125-MHz state machine

• 10 ns military/industrial versions

7 ns t<sub>CO</sub>

10 ns t<sub>S</sub>

10 ns t<sub>PD</sub>

62-MHz state machine

- · High reliability

- Proven Flash technology

- 100% programming and functional testing

#### **Functional Description**

The Cypress PALCE16V8 is a CMOS Flash Electrical Erasable second-generation programmable array logic device. It is implemented with the familiar sum-of-product (AND-OR) logic structure and the programmable macrocell.

#### **Selection Guide**

|                     | t <sub>PD</sub> ns |     | t <sub>S</sub> | ns  | t <sub>co</sub> | ns  | I <sub>cc</sub> | mA      |

|---------------------|--------------------|-----|----------------|-----|-----------------|-----|-----------------|---------|

| Generic Part Number | Com'l/Ind          | Mil | Com'l/Ind      | Mil | Com'l/Ind       | Mil | Com'l           | Mil/Ind |

| PALCE16V8-5         | 5                  |     | 3              |     | 4               |     | 115             |         |

| PALCE16V8-7         | 7.5                |     | 7              |     | 5               |     | 115             |         |

| PALCE16V8-10        | 10                 | 10  | 10             | 10  | 7               | 10  | 90              | 130     |

| PALCE16V8-15        | 15                 | 15  | 12             | 12  | 10              | 10  | 90              | 130     |

| PALCE16V8-25        | 25                 | 25  | 15             | 20  | 12              | 12  | 90              | 130     |

| PALCE16V8L-15       | 15                 | 15  | 12             | 12  | 10              | 12  | 55              | 65      |

| PALCE16V8L-25       | 25                 | 25  | 15             | 20  | 12              | 20  | 55              | 65      |

Shaded areas contain preliminary information.

#### **Functional Description**

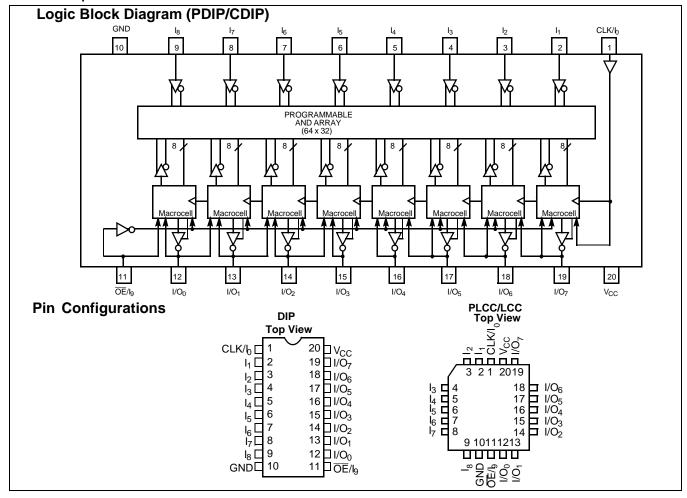

The PALCE16V8 is executed in a 20-pin 300-mil molded DIP, a 300-mil cerdip, a 20-lead square ceramic leadless chip carrier, and a 20-lead square plastic leaded chip carrier.

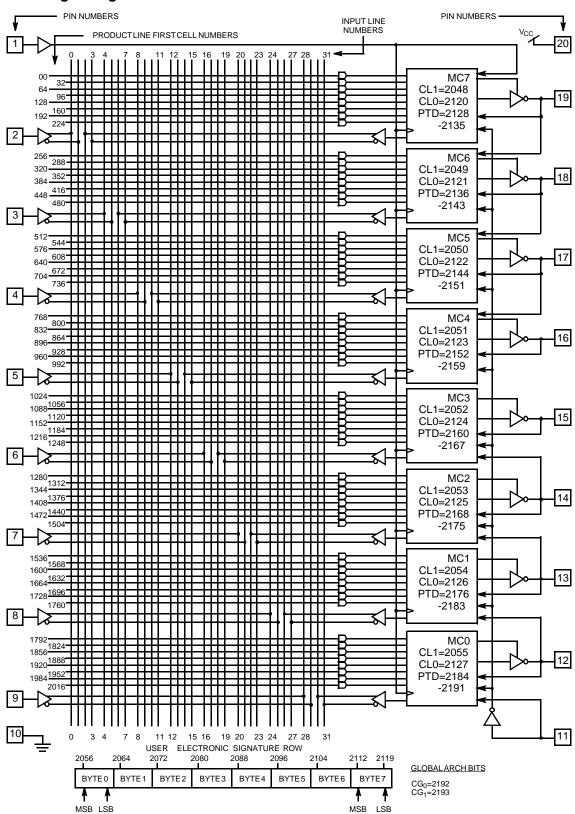

The device provides up to 16 inputs and 8 outputs. The PALCE16V8 can be electrically erased and reprogrammed. The programmable macrocell enables the device to function as a superset to the familiar 20-pin PLDs such as 16L8, 16R8, 16R6, and 16R4.

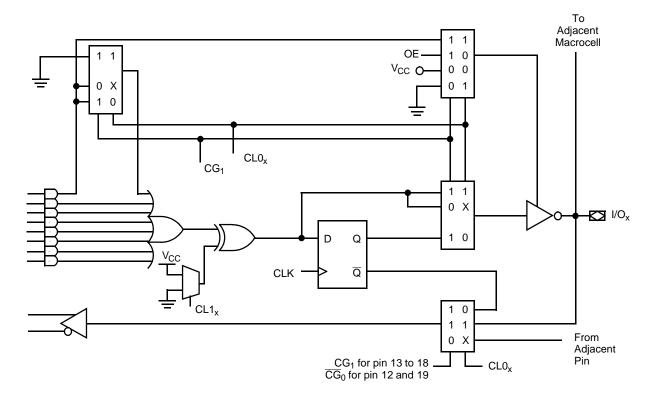

The PALCE16V8 features 8 product terms per output and 32 input terms into the AND array. The first product term in a macrocell can be used either as an internal output enable control or as a data product term.

There are a total of 18 architecture bits in the PALCE16V8 macrocell; two are global bits that apply to all macrocells and 16 that apply locally, two bits per macrocell. The architecture bits determine whether the macrocell functions as a register or combinatorial with inverting or noninverting output. The output enable control can come from an external pin or internally from a product term. The output can also be permanently enabled, functioning as a dedicated output or permanently disabled, functioning as a dedicated input. Feedback paths are selectable from either the input/output pin associated with the

macrocell, the input/output pin associated with an adjacent pin, or from the macrocell register itself.

#### Power-Up Reset

All registers in the PALCE16V8 power-up to a logic LOW for predictable system initialization. For each register, the associated output pin will be HIGH due to active-LOW outputs.

#### **Electronic Signature**

An electronic signature word is provided in the PALCE16V8 that consists of 64 bits of programmable memory that can contain user-defined data.

#### **Security Bit**

A security bit is provided that defeats the readback of the internal programmed pattern when the bit is programmed.

#### **Low Power**

The Cypress PALCE16V8 provides low-power operation through the use of CMOS technology, and increased testability with Flash reprogrammability.

#### **Product Term Disable**

Product Term Disable (PTD) fuses are included for each product term. The PTD fuses allow each product term to be individually disabled.

#### **Configuration Table**

| CG <sub>0</sub> | CG <sub>1</sub> | CL0 <sub>x</sub> | Cell Configuration   | Devices Emulated    |

|-----------------|-----------------|------------------|----------------------|---------------------|

| 0               | 1               | 0                | Registered Output    | Registered Med PALs |

| 0               | 1               | 1                | Combinatorial I/O    | Registered Med PALs |

| 1               | 0               | 0                | Combinatorial Output | Small PALs          |

| 1               | 0               | 1                | Input                | Small PALs          |

| 1               | 1               | 1                | Combinatorial I/O    | 16L8 only           |

Document #: 38-03025 Rev. \*A Page 2 of 13

#### Macrocell

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature .....-65°C to +150°C Ambient Temperature with Power Applied.......55°C to +125°C Supply Voltage to Ground Potential

DC Voltage Applied to Outputs in High-Z State ......-0.5V to +7.0V

| DC Input Voltage                  | 0.5V to +7.0V |

|-----------------------------------|---------------|

| Output Current into Outputs (LOW) |               |

| DC Programming Voltage            | 12.5V         |

| Latch-Up Current                  | > 200 mA      |

#### Operating Range

| Range                   | Ambient Temperature | V <sub>CC</sub> |

|-------------------------|---------------------|-----------------|

| Commercial              | 0°C to +75°C        | 5V ±5%          |

| Military <sup>[1]</sup> | -55°C to +125°C     | 5V ±10%         |

| Industrial              | -40°C to +85°C      | 5V ±10%         |

#### Electrical Characteristics Over the Operating Range<sup>[2]</sup>

| Parameter                      | Description                          | 7                                                           | Test Conditions               |                               | Min. | Max. | Unit |

|--------------------------------|--------------------------------------|-------------------------------------------------------------|-------------------------------|-------------------------------|------|------|------|

| V <sub>OH</sub>                | Output HIGH Voltage                  | V <sub>CC</sub> = Min.,                                     | $I_{OH} = -3.2 \text{ mA}$    | Com'l                         | 2.4  |      | V    |

|                                |                                      | $V_{IN} = V_{IH}$ or $V_{IL}$                               | $I_{OH} = -2 \text{ mA}$      | Mil/Ind                       |      |      |      |

| $V_{OL}$                       | Output LOW Voltage                   | V <sub>CC</sub> = Min.,                                     | I <sub>OL</sub> = 24 mA       | Com'l                         |      | 0.5  | V    |

|                                |                                      | $V_{IN} = V_{IH}$ or $V_{IL}$                               | I <sub>OL</sub> = 12 mA       | Mil/Ind                       |      |      |      |

| $V_{IH}$                       | Input HIGH Level                     | Guaranteed Input Lo                                         | for All Inputs <sup>[3]</sup> | 2.0                           |      | V    |      |

| V <sub>IL</sub> [4]            | Input LOW Level                      | Guaranteed Input Lo                                         | ogical LOW Voltage            | for All Inputs <sup>[3]</sup> | -0.5 | 0.8  | V    |

| I <sub>IH</sub>                | Input or I/O HIGH Leakage<br>Current | $3.5V \le V_{IN} \le V_{CC}$                                |                               |                               | 10   | μА   |      |

| I <sub>IL</sub> <sup>[5]</sup> | Input or I/O LOW Leakage<br>Current  | $0V \le V_{IN} \le V_{IN}$ (Max                             | (.)                           |                               |      | -100 | μА   |

| I <sub>SC</sub>                | Output Short Circuit Current         | V <sub>CC</sub> = Max., V <sub>OUT</sub> =                  | = 0.5V <sup>[6, 7]</sup>      |                               | -30  | -150 | mA   |

| I <sub>CC</sub>                | Operating Power Supply               | V <sub>CC</sub> = Max.,                                     | 5, 7 ns                       | Com'l                         |      | 115  | mA   |

|                                | Current                              | V <sub>IL</sub> = 0V, V <sub>IH</sub> = 3V,<br>Output Open, | 10, 15, 25 ns                 |                               |      | 90   | mA   |

|                                |                                      | f = 15 MHz                                                  | 15L, 25L ns                   |                               |      | 55   | mA   |

|                                |                                      | (counter)                                                   | 10, 15, 25 ns                 | Mil/Ind                       |      | 130  | mA   |

|                                |                                      |                                                             | 15L, 25L ns                   | Mil.                          |      | 65   | mA   |

|                                |                                      |                                                             | 15L, 25L ns                   | Ind.                          |      | 65   | mA   |

#### Capacitance<sup>[7]</sup>

| Parameter        | Description        | Test Conditions                     | Тур. | Unit |

|------------------|--------------------|-------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 2.0V @ f = 1 MHz  | 5    | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 2.0V @ f = 1 MHz | 5    | pF   |

#### **Endurance Characteristics**[7]

| Parameter | Description                  | Test Conditions               | Min. | Max. | Unit   |

|-----------|------------------------------|-------------------------------|------|------|--------|

| N         | Minimum Reprogramming Cycles | Normal Programming Conditions | 100  |      | Cycles |

#### Notes:

- 1.  $T_A$  is the "instant on" case temperature.

- Y<sub>IL</sub> (Min.) is equal to –3.0V for pulse durations less than 20 ns.

- 5. The leakage current is due to the internal pull-up resistor on all pins.

- Not more than one output should be tested at a time. Duration of the short circuit should not be more than one second. V<sub>OUT</sub> = 0.5V has been chosen to avoid test problems caused by tester ground degradation.

Tested initially and after any design or process changes that may affect these parameters.

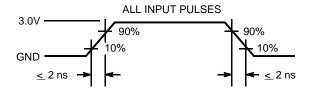

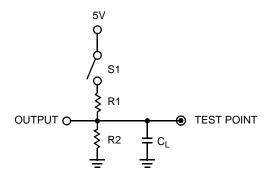

#### **AC Test Loads and Waveforms**

|                                    |                              |       | Comn           | nercial        | Military       |                |                                                                |

|------------------------------------|------------------------------|-------|----------------|----------------|----------------|----------------|----------------------------------------------------------------|

| Specification                      | S <sub>1</sub>               | CL    | R <sub>1</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>2</sub> | Measured Output Value                                          |

| t <sub>PD</sub> , t <sub>CO</sub>  | Closed                       | 50 pF | 200Ω           | 390Ω           | 390Ω           | 750Ω           | 1.5V                                                           |

| t <sub>PZX</sub> , t <sub>EA</sub> | Z · H: Open<br>Z · L: Closed |       |                |                |                |                | 1.5V                                                           |

| t <sub>PXZ</sub> , t <sub>ER</sub> | H · Z: Open<br>L · Z: Closed | 5 pF  |                |                |                |                | H · Z: V <sub>OH</sub> – 0.5V<br>L · Z: V <sub>OL</sub> + 0.5V |

#### Commercial and Industrial Switching Characteristics [2]

|                  |                                                              | 16\  | /8-5 | 16\  | <b>/</b> 8-7 | 16V  | 8-10 | 16V       | 8-15 | 16V8-25 |      |      |

|------------------|--------------------------------------------------------------|------|------|------|--------------|------|------|-----------|------|---------|------|------|

| Parameter        | Description                                                  | Min. | Max. | Min. | Max.         | Min. | Max. | Min. Max. |      | Min.    | Max. | Unit |

| t <sub>PD</sub>  | Input to Output<br>Propagation Delay <sup>[8, 9]</sup>       | 1    | 5    | 3    | 7.5          | 3    | 10   | 3         | 15   | 3       | 25   | ns   |

| t <sub>PZX</sub> | OE to Output Enable                                          | 1    | 6    |      | 6            |      | 10   |           | 15   |         | 20   | ns   |

| t <sub>PXZ</sub> | OE to Output Disable                                         | 1    | 5    |      | 6            |      | 10   |           | 15   |         | 20   | ns   |

| t <sub>EA</sub>  | Input to Output<br>Enable Delay <sup>[7]</sup>               | 1    | 6    |      | 9            |      | 10   |           | 15   |         | 25   | ns   |

| t <sub>ER</sub>  | Input to Output<br>Disable Delay <sup>[7, 10]</sup>          | 1    | 5    |      | 9            |      | 10   |           | 15   |         | 25   | ns   |

| t <sub>CO</sub>  | Clock to Output Delay[8, 9]                                  | 1    | 4    | 2    | 5            | 2    | 7    | 2         | 10   | 2       | 12   | ns   |

| t <sub>S</sub>   | Input or Feedback<br>Set-up Time                             | 3    |      | 5    |              | 7.5  |      | 12        |      | 15      |      | ns   |

| t <sub>H</sub>   | Input Hold Time                                              | 0    |      | 0    |              | 0    |      | 0         |      | 0       |      | ns   |

| t <sub>P</sub>   | External Clock<br>Period (t <sub>CO</sub> + t <sub>S</sub> ) | 7    |      | 10   |              | 14.5 |      | 22        |      | 27      |      | ns   |

Shaded areas contain preliminary information.

#### Notes:

- Min. times are tested initially and after any design or process changes that may affect these parameters.

This specification is guaranteed for all device outputs changing state in a given access cycle.

This parameter is measured as the time after OE pin or internal disable input disables or enables the output pin. This delay is measured to the point at which a previous HIGH level has fallen to 0.5 volts below V<sub>OH</sub> min. or a previous LOW level has risen to 0.5 volts above V<sub>OL</sub> max.

This specification indicates the guaranteed maximum frequency at which a state machine configuration with external feedback can operate.

- 12. This specification indicates the guaranteed maximum frequency at which the device can operate in data path mode.

- 13. This specification indicates the guaranteed maximum frequency at which a state machine configuration with internal only feedback can operate.

- 14. This parameter is calculated from the clock period at f<sub>MAX</sub> internal (1/f<sub>MAX3</sub>) as measured (see Note 7 above) minus t<sub>S</sub>.

# Commercial and Industrial Switching Characteristics (continued)<sup>[2]</sup>

|                   |                                                                                                      | 16\  | /8-5 | 16\  | /8-7 | 16V  | 8-10 | 16V8-15 |      | 16V8-25 |      |      |

|-------------------|------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|---------|------|---------|------|------|

| Parameter         | Description                                                                                          | Min. | Max. | Min. | Max. | Min. | Max. | Min.    | Max. | Min.    | Max. | Unit |

| t <sub>WH</sub>   | Clock Width HIGH <sup>[7]</sup>                                                                      | 3    |      | 4    |      | 6    |      | 8       |      | 12      |      | ns   |

| t <sub>WL</sub>   | Clock Width LOW <sup>[7]</sup>                                                                       | 3    |      | 4    |      | 6    |      | 8       |      | 12      |      | ns   |

| f <sub>MAX1</sub> | External Maximum<br>Frequency (1/(t <sub>CO</sub> + t <sub>S</sub> )) <sup>[7, 11]</sup>             | 143  |      | 100  |      | 69   |      | 45.5    |      | 37      |      | MHz  |

| f <sub>MAX2</sub> | Data Path Maximum<br>Frequency (1/(t <sub>WH</sub> + t <sub>WL</sub> )) <sup>[7, 12]</sup>           | 166  |      | 125  |      | 83   |      | 62.5    |      | 41.6    |      | MHz  |

| f <sub>MAX3</sub> | Internal Feedback<br>Maximum Frequency<br>(1/(t <sub>CF</sub> + t <sub>S</sub> )) <sup>[7, 13]</sup> | 166  |      | 125  |      | 74   |      | 50      |      | 40      |      | MHz  |

| t <sub>CF</sub>   | Register Clock to Feedback Input <sup>[7, 14]</sup>                                                  |      | 3    |      | 3    |      | 6    |         | 8    |         | 10   | ns   |

| t <sub>PR</sub>   | Power-Up Reset Time <sup>[7]</sup>                                                                   | 1    |      | 1    |      | 1    |      | 1       |      | 1       |      | μS   |

# Military Switching Characteristics<sup>[7]</sup>

|                   |                                                                                                   | 16V  | <b>/8-10</b> | 16V8-15 |      | 16V8-25 |      |      |

|-------------------|---------------------------------------------------------------------------------------------------|------|--------------|---------|------|---------|------|------|

| Parameter         | Description                                                                                       | Min. | Max.         | Min.    | Max. | Min.    | Max. | Unit |

| t <sub>PD</sub>   | Input to Output<br>Propagation Delay <sup>[8, 9]</sup>                                            | 3    | 10           | 3       | 15   | 3       | 25   | ns   |

| t <sub>PZX</sub>  | OE to Output Enable                                                                               |      | 10           |         | 15   |         | 20   | ns   |

| t <sub>PXZ</sub>  | OE to Output Disable                                                                              |      | 10           |         | 15   |         | 20   | ns   |

| t <sub>EA</sub>   | Input to Output Enable Delay <sup>[7]</sup>                                                       |      | 10           |         | 15   |         | 25   | ns   |

| t <sub>ER</sub>   | Input to Output Disable Delay <sup>[7, 10]</sup>                                                  |      | 10           |         | 15   |         | 25   | ns   |

| t <sub>CO</sub>   | Clock to Output Delay <sup>[8, 9]</sup>                                                           | 2    | 7            | 2       | 10   | 2       | 12   | ns   |

| t <sub>S</sub>    | Input or Feedback Set-up Time                                                                     | 10   |              | 12      |      | 15      |      | ns   |

| t <sub>H</sub>    | Input Hold Time                                                                                   | .5   |              | .5      |      | .5      |      | ns   |

| t <sub>P</sub>    | External Clock Period (t <sub>CO</sub> + t <sub>S</sub> )                                         | 17   |              | 22      |      | 27      |      | ns   |

| t <sub>WH</sub>   | Clock Width HIGH <sup>[7]</sup>                                                                   | 6    |              | 8       |      | 12      |      | ns   |

| $t_{WL}$          | Clock Width LOW <sup>[7]</sup>                                                                    | 6    |              | 8       |      | 12      |      | ns   |

| f <sub>MAX1</sub> | External Maximum Frequency $(1/(t_{CO} + t_S)^{[7, 11]}$                                          | 58   |              | 45.5    |      | 37      |      | MHz  |

| f <sub>MAX2</sub> | Data Path Maximum Frequency $(1/(t_{WH} + t_{WL}))^{[7, 12]}$                                     | 83   |              | 62.5    |      | 41.6    |      | MHz  |

| f <sub>MAX3</sub> | Internal Feedback Maximum<br>Frequency (1/(t <sub>CF</sub> + t <sub>S</sub> )) <sup>[7, 13]</sup> | 62.5 |              | 50      |      | 40      |      | MHz  |

| t <sub>CF</sub>   | Register Clock to<br>Feedback Input <sup>[7, 14]</sup>                                            |      | 6            |         | 8    |         | 10   | ns   |

| t <sub>PR</sub>   | Power-Up Reset Time <sup>[7]</sup>                                                                | 1    |              | 1       |      | 1       |      | μS   |

Document #: 38-03025 Rev. \*A Page 6 of 13

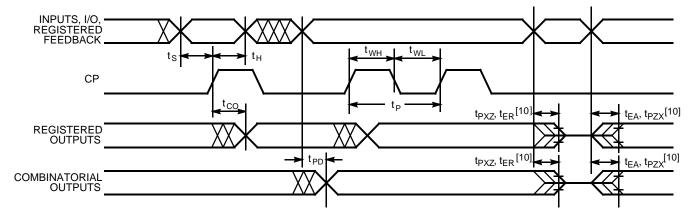

## **Switching Waveform**

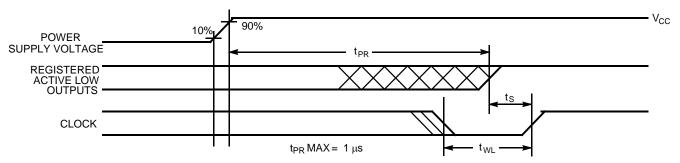

# **Power-Up Reset Waveform**

#### **Functional Logic Diagram for PALCE16V8**

# **Ordering Information**

| I <sub>CC</sub><br>(mA) | t <sub>PD</sub><br>(ns) | t <sub>S</sub><br>(ns) | t <sub>CO</sub><br>(ns) | Ordering Code    | Package<br>Name | Package Type                        | Operating<br>Range |

|-------------------------|-------------------------|------------------------|-------------------------|------------------|-----------------|-------------------------------------|--------------------|

| 115                     | 5                       | 3                      | 4                       | PALCE16V8-5JC    | J61             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

| 115                     | 7.5                     | 5                      | 5                       | PALCE16V8-7JC    | J61             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALCE16V8-7PC    | P5              | 20-Lead (300-Mil) Molded DIP        | 7                  |

| 90                      | 10                      | 7.5                    | 7                       | PALCE16V8-10JC   | J61             | 20-Lead Plastic Leaded Chip Carrier |                    |

|                         |                         |                        |                         | PALCE16V8-10PC   | P5              | 20-Lead (300-Mil) Molded DIP        |                    |

| 130                     | 10                      | 7.5                    | 7                       | PALCE16V8-10JI   | J61             | 20-Lead Plastic Leaded Chip Carrier | Industrial         |

|                         |                         |                        |                         | PALCE16V8-10PI   | P5              | 20-Lead (300-Mil) Molded DIP        |                    |

| 130                     | 10                      | 10                     | 7                       | PALCE16V8-10DMB  | D6              | 20-Lead (300-Mil) CerDIP            | Military           |

|                         |                         |                        |                         | PALCE16V8-10LMB  | L61             | 20-Pin Square Leadless Chip Carrier |                    |

| 90                      | 15                      | 12                     | 10                      | PALCE16V8-15JC   | J61             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALCE16V8-15PC   | P5              | 20-Lead (300-Mil) Molded DIP        | 7                  |

| 130                     | 15                      | 12                     | 10                      | PALCE16V8-15PI   | P5              | 20-Lead(300Mil) Molded DIP          | Industrial         |

|                         |                         |                        |                         | PALCE16V8-15DMB  | D6              | 20-Lead (300-Mil) CerDIP            | Military           |

|                         |                         |                        |                         | PALCE16V8-15LMB  | L61             | 20-Pin Square Leadless Chip Carrier | 7                  |

| 90                      | 25                      | 15                     | 12                      | PALCE16V8-25JC   | J61             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALCE16V8-25PC   | P5              | 20-Lead (300-Mil) Molded DIP        | 7                  |

| 130                     | 25                      | 15                     | 12                      | PALCE16V8-25JI   | J61             | 20-Lead Plastic Leaded Chip Carrier | Industrial         |

|                         |                         |                        |                         | PALCE16V8-25DMB  | D6              | 20-Lead (300-Mil) CerDIP            | Military           |

|                         |                         |                        |                         | PALCE16V8-25LMB  | L61             | 20-Pin Square Leadless Chip Carrier |                    |

| 55                      | 10                      | 7.5                    | 7                       | PALCE16V8L-10JC  | J61             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALCE16V8L-10PC  | P5              | 20-Lead (300-Mil) Molded DIP        | 7                  |

| 65                      | 10                      | 10                     | 7                       | PALCE16V8L-10JI  | J61             | 20-Lead Plastic Leaded Chip Carrier | Industrial         |

|                         |                         |                        |                         | PALCE16V8L-10PI  | P5              | 20-Lead (300-Mil) Molded DIP        |                    |

| 55                      | 15                      | 12                     | 10                      | PALCE16V8L-15JC  | J61             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALCE16V8L-15PC  | P5              | 20-Lead (300-Mil) Molded DIP        | 7                  |

| 65                      | 15                      | 12                     | 10                      | PALCE16V8L-15DMB | D6              | 20-Lead (300-Mil) CerDIP            | Military           |

|                         |                         |                        |                         | PALCE16V8L-15LMB | L61             | 20-Pin Square Leadless Chip Carrier |                    |

| 55                      | 25                      | 15                     | 12                      | PALCE16V8L-25JC  | J61             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALCE16V8L-25PC  | P5              | 20-Lead (300-Mil) Molded DIP        |                    |

| 65                      | 25                      | 15                     | 12                      | PALCE16V8L-25DMB | D6              | 20-Lead (300-Mil) CerDIP            | Military           |

|                         |                         |                        |                         | PALCE16V8L-25LMB | L61             | 20-Pin Square Leadless Chip Carrier |                    |

Shaded areas contain preliminary information.

Document #: 38-03025 Rev. \*A

### MILITARY SPECIFICATIONS Group A Subgroup Testing DC Characteristics

| Parameter       | Subgroups |  |

|-----------------|-----------|--|

| V <sub>OH</sub> | 1, 2, 3   |  |

| V <sub>OL</sub> | 1, 2, 3   |  |

| V <sub>IH</sub> | 1, 2, 3   |  |

| V <sub>IL</sub> | 1, 2, 3   |  |

| I <sub>IX</sub> | 1, 2, 3   |  |

| I <sub>OZ</sub> | 1, 2, 3   |  |

| I <sub>CC</sub> | 1, 2, 3   |  |

# **Switching Characteristics**

| Parameter       | Subgroups |

|-----------------|-----------|

| t <sub>PD</sub> | 9, 10, 11 |

| t <sub>co</sub> | 9, 10, 11 |

| t <sub>S</sub>  | 9, 10, 11 |

| t <sub>H</sub>  | 9, 10, 11 |

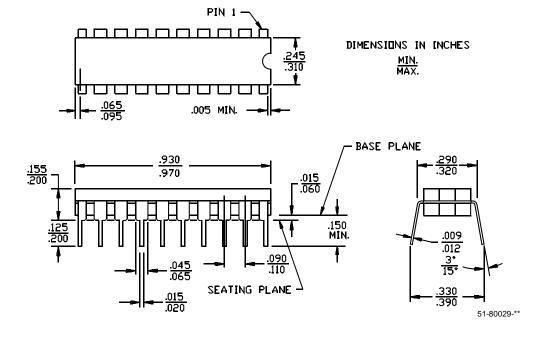

# **Package Diagrams**

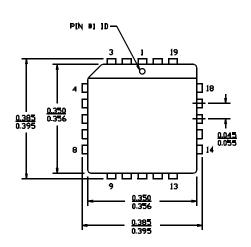

#### 20-Lead (300-Mil) CerDIP D6

MIL-STD-1835 D-8 Config. A

# Package Diagrams (continued)

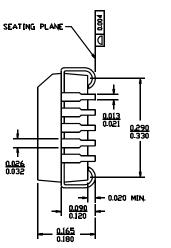

#### 20-Lead Plastic Leaded Chip Carrier J61

DIMENSIONS IN INCHES MIN. MAX.

51-85000-\*A

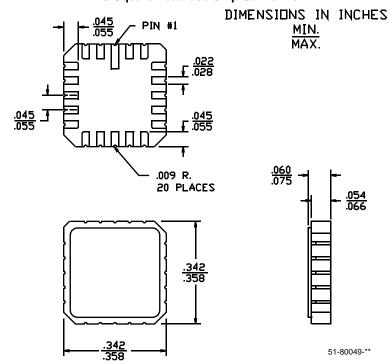

#### 20-Square Leadless Chip Carrier L61

#### Package Diagrams (continued)

# 20-Lead (300-Mil) Molded DIP P5 DIMENSIONS IN INCHES MIN. 0.009 0.015 0.060 0.01<u>5</u> 0.020 51-85011-\*A

Ultra37000 is a trademark of Cypress Semiconductor Corporation. PAL is a registered trademark of Advanced Micro Devices, Inc. All products and company names mentioned in this document may be the trademarks of their respective holders.

# **Document History Page**

| Document Title: PALCE16V8 Flash Erasable Reprogrammable CMOS PAL® Device Document Number: 38-03025 |         |            |                    |                                                                |  |

|----------------------------------------------------------------------------------------------------|---------|------------|--------------------|----------------------------------------------------------------|--|

| REV.                                                                                               | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change                                          |  |

| **                                                                                                 | 106370  | 07/11/01   | SZV                | Change from Spec Number: 38-00364 to 38-03025                  |  |

| *A                                                                                                 | 213375  | See ECN    | FSG                | Added note to title page: "Use Ultra37000 For All New Designs" |  |

Document #: 38-03025 Rev. \*A