# onsemi

# mWSaver<sup>®</sup> Integrated Power Switcher with 800 V SJ MOSFET for Offline SMPS

# NCP11184, NCP11185, NCP11187

NCP1118x integrates a peak current mode PWM controller employing mWSaver technology and a highly robust 800 V SJ MOSFET providing especially enhanced performance in flyback converters. The mWSaver technology reduces switching frequency and operating current of the controller at light–load condition, which helps avoid acoustic–noise problems and even meet international power conservation standards, such as Energy Star<sup>®</sup>.

Additionally, NCP1118x includes a high–voltage startup circuit, frequency–hopping function, slope compensation, constant output power limit, and highly reliable and various protections, which allows easy design, less BOM counts, smaller PCB size and designing cost–effective off–line power supply. The protections feature a protection of a feedback pin open–loop, current–sense resistor short, brown–out and line over–voltage using an line voltage sensing pin, which operate with auto–recovery operation.

#### Features

- Integrated 800 V Super Junction MOSFET

- Built-in High Voltage Start-up, Soft-Start, and Slope Compensation

- mWSaver Technology Provides Industry's Best-in-Class Standby Power

- Switching Frequency Option: 65/100/130 kHz

- Proprietary Asynchronous Frequency Hopping Technique for Low EMI

- Programmable Constant Output Power Limit for Entire Input Voltage Range

- Precise Brown-out Protection and Line Over-voltage Protection (LOVP) with Hysteresis

- Current Sense Short Protection (CSSP) and Abnormal Over-Current Protection (AOCP)

- Thermal Shutdown (TSD) with Hysteresis

- All Protections Operated by Auto-recovery: VCC Under-voltage Lockout (UVLO), Feedback Open-Loop Protection (OLP), VCC Over-Voltage Protection (OVP)

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

- Industrial Auxiliary Power Supplies, E-metering SMPS

- Power Supplies for White Good Applications and Consumer Electronics

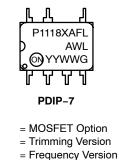

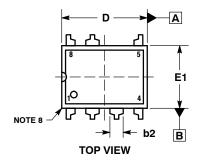

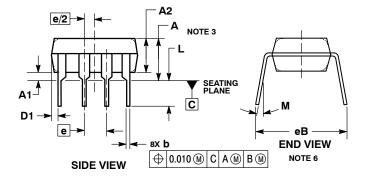

PDIP-7 (PDIP-8 LESS PIN 6) CASE 626A

#### MARKING DIAGRAM

- = Lead Forming Version

- = Plant Code

- WL = Wafer Lot

Х

А

F

L.

Α

- YY = Year of Production

- WW = Work Week

- G = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 22 of this data sheet.

#### **PRODUCTS INFORMATION & INDICATIVE MAXIMUM OUTPUT POWER**

|                |         |           |                         | Output Power Table (W) (Note 2) |                     |

|----------------|---------|-----------|-------------------------|---------------------------------|---------------------|

|                |         | Switching | R <sub>DS(ON)</sub> (Ω) | Open                            | Frame               |

| Part Number    | Package | Frequency | (Note 1)                | 85 ~ 265 V <sub>AC</sub>        | 230 V <sub>AC</sub> |

| NCP11184A065PG | PDIP7   | 65 kHz    | 2.25                    | 35                              | 45                  |

| NCP11185A065PG | 1       |           | 1.3                     | 40                              | 55                  |

| NCP11187A065PG |         |           | 0.87                    | 50                              | 65                  |

| NCP11184A100PG |         | 100 kHz   | 2.25                    | 33                              | 40                  |

| NCP11187A100PG |         |           | 0.87                    | 45                              | 60                  |

| NCP11184A130PG | 1       | 130 kHz   | 2.25                    | 30                              | 36                  |

| NCP11185A130PG | 1       |           | 1.3                     | 37                              | 52                  |

1. Maximum value at  $T_J = 25^{\circ}C$ .

2. Estimated maximum output power rating at  $T_A = 50^{\circ}$ C not exceeding  $T_C$  of 110°C assuming DRAIN pin surrounding with a thermal relief pad 150 mm<sup>2</sup> in single layer PCB with 1oz. The actual output power could be varied depending on particular designs.

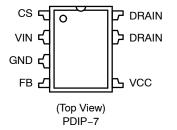

# PIN CONFIGURATION

#### **PIN FUNCTION DESCRIPTION**

| PIN # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CS    | Sensing the drain current using a resistor. The sensed voltage is used for peak current mode control and cycle-by-cycle current limit. This pin also connects to a source of the integrated MOSFET                                                                                                                                                                                                 |

| 2     | VIN   | Detecting line input voltage. The sensed line input voltage is used for brown-out protection with hysteresis.<br>Besides, constant output power limit is controlled with the sensed voltage. It is recommended to add<br>a low-pass filter with this pin in parallel to reject high frequency noise and line ripple on the bulk capacitor.<br>Pulling this pin up triggers auto-restart protection |

| 3     | GND   | Ground of the controller                                                                                                                                                                                                                                                                                                                                                                           |

| 4     | FB    | Control compensation. The PWM duty cycle is determined in response of comparing the signal on this pin<br>and the sensed drain signal on the CS pin. Typically, an opto-coupler and capacitor are connected to this<br>pin                                                                                                                                                                         |

| 5     | VCC   | Power supply for the internal circuit operations                                                                                                                                                                                                                                                                                                                                                   |

| 6, 7  | DRAIN | This pin connects to an internal high voltage startup circuit and a drain of the integrated MOSFET. Typically, this pin is directly connected to one of terminals of the transformer. At initial startup or restart mode, operating voltage is powered through this pin                                                                                                                            |

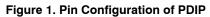

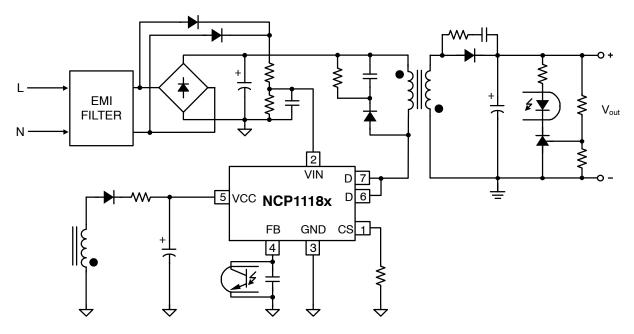

**TYPICAL APPLICATION**

Figure 2. Typical Application (Detecting DC Voltage on Bulk-capacitor)

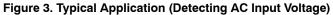

# **BLOCK DIAGRAM**

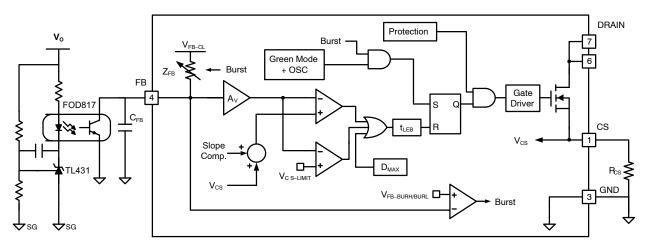

Figure 4. Simplified Internal Circuit Block Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                                                             | Symbol             | Value             | Unit |

|-------------------------------------------------------------------------------------------------------|--------------------|-------------------|------|

| VCC Supply Voltage                                                                                    | V <sub>CC</sub>    | -0.3 to 30        | V    |

| FB Pin Input Voltage                                                                                  | V <sub>FB</sub>    | -0.3 to 5.5       | V    |

| CS Pin Input Voltage                                                                                  | V <sub>CS</sub>    | -0.3 to 5.5       | V    |

| VIN Pin Input Voltage                                                                                 | V <sub>VIN</sub>   | -0.5 to 5.5       | V    |

| DRAIN Pin Input Voltage                                                                               | V <sub>DRAIN</sub> | -0.3 to 800       | V    |

| Pulsed Drain Current (Note 3)<br>NCP11184<br>NCP11185<br>NCP11187                                     | Идм                | 4.2<br>5.4<br>6.8 | A    |

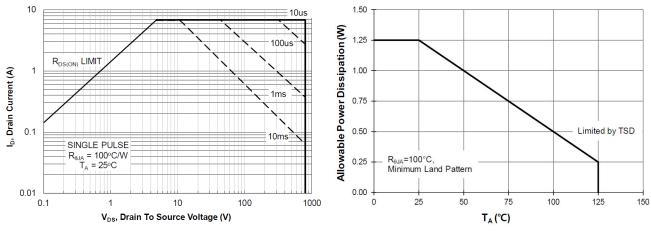

| Power Dissipation                                                                                     | PD                 | 1.25              | W    |

| Junction Temperature (Note 4)                                                                         | TJ                 | -40 to +150       | °C   |

| Storage Temperature                                                                                   | T <sub>STG</sub>   | -40 to +150       | °C   |

| Lead Temperature, Wave Soldering or IT, 10 seconds                                                    | ΤL                 | 260               | °C   |

| ESD Capability HBM, JESD22–A114<br>All Pins Except DRAIN Pin<br>DRAIN Pin<br>NCP11184 / 5<br>NCP11187 |                    | 4.0<br>1.5<br>2.0 | kV   |

| ESD Capability CDM, JESD22-C101                                                                       |                    | 1.0               | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

3. Repetitive rating. Pulse width is limited by maximum junction temperature. T<sub>A</sub> =  $25^{\circ}$ C.

4. Although this parameter guarantees IC operation, it does not guarantee all electrical characteristics.

#### THERMAL CHARACTERISTICS

| Rating                                                                       | Symbol                | Value     | Unit |

|------------------------------------------------------------------------------|-----------------------|-----------|------|

| Junction-to-Ambience Thermal Impedance<br>PDIP-7 (Note 5)<br>PDIP-7 (Note 6) | $R_{	heta JA}$        | 100<br>70 | °C/W |

| Junction-to-Case (Top-side) Thermal Impedance<br>PDIP-7 (Note 6)             | $R_{	extsf{	heta}JC}$ | 11        | °C/W |

5. JEDEC recommended environment in JESD51-2 and test board with minimum land pad in JESD51-3.

6. Estimated in soldering a copper thermal relief pad with 200 mm<sup>2</sup> (0.31 sq. inch) and 2 oz. to the drain pin.

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C unless otherwise noted)

| Parameter                                                                                             | Test Conditions                                                                                                                                                               | Symbol               | Min         | Тур                  | Max                 | Unit |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|----------------------|---------------------|------|

| MOSFET SECTION                                                                                        |                                                                                                                                                                               |                      |             | -                    |                     |      |

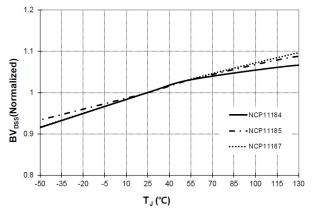

| Drain-to-Source Breakdown Voltage                                                                     | $V_{GS}$ = 0 V, $V_{CS}$ = 0 V, $I_{DRAIN}$ = 1 mA, $T_{J}$ = 25°C                                                                                                            | BV <sub>DSS</sub>    | 800         | -                    | -                   | V    |

| Off-state Drain-to-Source Leakage<br>Current                                                          | $\label{eq:VCC} \begin{array}{l} V_{CC} \geq V_{CC-OVP}, V_{CS} = 0 \text{ V}, \\ V_{DRAIN} = 800 \text{ V} \\ T_J = 25^\circ\text{C} \\ T_J = 125^\circ\text{C} \end{array}$ | I <sub>DSS</sub>     |             | 2.05<br>4.57         | 25<br>250           | μΑ   |

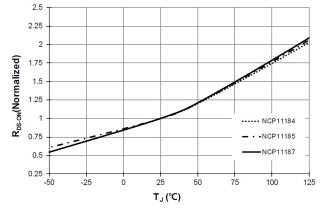

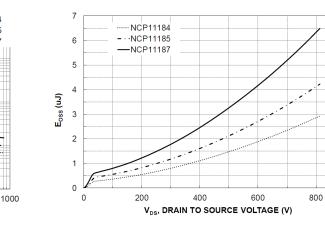

| Static Drain-to-Source On<br>Resistance (Note 7)                                                      | V <sub>CC</sub> = 15 V, T <sub>J</sub> = 25°C<br>NCP11184, I <sub>DRAIN</sub> = 0.3 A<br>NCP11185, I <sub>DRAIN</sub> = 0.4 A<br>NCP11187, I <sub>DRAIN</sub> = 0.6 A         | R <sub>DS(ON)</sub>  | _<br>_<br>_ | 1.87<br>1.05<br>0.70 | 2.25<br>1.3<br>0.87 | Ω    |

| Static Drain-to-Source On<br>Resistance (Note 7)                                                      | $V_{VCC} = 15 V, T_J = 125^{\circ}C$<br>NCP11184, I <sub>DRAIN</sub> = 0.3 A<br>NCP11185, I <sub>DRAIN</sub> = 0.4 A<br>NCP11187, I <sub>DRAIN</sub> = 0.6 A                  | R <sub>DS(ON)</sub>  |             | 3.74<br>2.10<br>1.40 | 4.5<br>2.6<br>1.74  | Ω    |

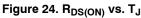

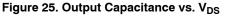

| Effective Output Capacitance<br>Time-related                                                          | V <sub>DS</sub> = 0 to 400 V, V <sub>GS</sub> = 0 V<br>NCP11184<br>NCP11185<br>NCP11187                                                                                       | C <sub>OSS(tr)</sub> | -<br>-<br>- | 65<br>97<br>151      |                     | pF   |

| Effective Output Capacitance<br>Energy-related                                                        | V <sub>DS</sub> = 0 to 400 V, V <sub>GS</sub> = 0 V<br>NCP11184<br>NCP11185<br>NCP11187                                                                                       | C <sub>OSS(er)</sub> |             | 14<br>20<br>30       |                     | pF   |

| Fall Time (Note 8)                                                                                    | V <sub>CC</sub> = 15 V, V <sub>DS</sub> = 400 V, falling 90→10%<br>NCP11184<br>NCP11185<br>NCP11187                                                                           | t <sub>f</sub>       | -<br>-<br>- | 22<br>24<br>20       |                     | ns   |

| Rise Time (Note 8)                                                                                    | V <sub>CC</sub> = 15 V, V <sub>DS</sub> = 400 V, rising 10→90%<br>NCP11184<br>NCP11185<br>NCP11187                                                                            | t <sub>r</sub>       | _<br>_<br>_ | 25<br>16<br>20       | _<br>_<br>_         | ns   |

| HV STARTUP SECTION                                                                                    |                                                                                                                                                                               |                      |             |                      |                     |      |

| VCC Threshold Voltage Switching<br>Startup Current from I <sub>START1</sub> to<br>I <sub>START2</sub> |                                                                                                                                                                               | V <sub>CC-SSC</sub>  | 1.0         | 2.1                  | 3.0                 | V    |

| Startup Charging Current                                                                              | $V_{DRAIN}$ > 40 V, $V_{CC}$ = 0 V                                                                                                                                            | I <sub>START1</sub>  | 0.2         | 0.5                  | 0.8                 | mA   |

| Startup Charging Current                                                                              | $V_{DRAIN}$ > 40 V, $V_{CC}$ = $V_{CC-ON}$ – 0.5 V                                                                                                                            | I <sub>START2</sub>  | 2.7         | 4.5                  | 6.3                 | mA   |

| Minimum Required Drain Voltage for<br>Startup (Note 9)                                                |                                                                                                                                                                               | V <sub>D-STR</sub>   | 25          | -                    | -                   | V    |

# VCC SUPPLY SECTION

| VCC Turn-on Threshold Voltage               |                                                                                                                                                                                                                 | V <sub>CC-ON</sub>   | 14  | 16                                            | 18  | V  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|-----------------------------------------------|-----|----|

| VCC Turn-off Threshold Voltage              |                                                                                                                                                                                                                 | V <sub>CC-OFF</sub>  | 6.8 | 7.8                                           | 8.8 | V  |

| Operating Current before V <sub>CC-ON</sub> | $V_{CC} = V_{CC-ON} - 0.5 V$                                                                                                                                                                                    | I <sub>CC-INIT</sub> | -   | 30                                            | -   | μΑ |

| Operating Supply Current                    | V <sub>CC</sub> = 15 V, V <sub>FB</sub> = 4.5 V,<br>Open DRAIN pin,<br>65-kHz Version<br>NCP11184<br>NCP11185<br>NCP11187<br>100-kHz Version<br>NCP11184<br>NCP11187<br>130-kHz Version<br>NCP11184<br>NCP11185 | I <sub>CC-OP1</sub>  |     | 1.6<br>2.0<br>2.6<br>1.9<br>3.3<br>2.2<br>3.0 |     | mA |

| Operating Supply Current without Switching  | $V_{CC}$ = 15 V, $V_{FB}$ = 0 V                                                                                                                                                                                 | I <sub>CC-OP2</sub>  | _   | 500                                           | _   | μΑ |

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C unless otherwise noted) (continued)

| Parameter                                                                                 | Test Conditions                                                                                                               | Symbol                | Min                   | Тур                 | Max                    | Unit  |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|---------------------|------------------------|-------|

| VCC SUPPLY SECTION                                                                        |                                                                                                                               |                       |                       |                     |                        |       |

| Soft-start Time                                                                           | V <sub>FB</sub> = V <sub>FB-CL</sub><br>65/130 kHz Version<br>100 kHz Version                                                 | t <sub>SS</sub>       | 4.0<br>5.2            | 5.5<br>7.15         | 7.0<br>9.1             | ms    |

| V <sub>CC</sub> Threshold Voltage Switching<br>Operating Current after Protection<br>Mode |                                                                                                                               | V <sub>CC-SOP</sub>   | 9                     | 10.2                | 11.4                   | V     |

| Operating Current after Protection                                                        | V <sub>CC-AR</sub> + 0.2 V                                                                                                    | I <sub>CC-OP3</sub>   | 60                    | 100                 | 140                    | μA    |

| Protection Reset V <sub>CC</sub> Threshold Voltage                                        |                                                                                                                               | V <sub>CC-AR</sub>    | 6.4                   | 7.4                 | 8.4                    | V     |

| OSCILLATOR SECTION                                                                        |                                                                                                                               | •                     |                       |                     |                        |       |

| Switching Frequency                                                                       | V <sub>FB</sub> = 4.5 V (V <sub>FB-OLP</sub> ), T <sub>J</sub> = 25°C<br>65 kHz Version<br>100 kHz Version<br>130 kHz Version | fosc                  | 62<br>95<br>124       | 65<br>100<br>130    | 68<br>105<br>136       | kHz   |

| Frequency Variation vs. Temperature<br>Deviation (Note 9)                                 | $V_{FB} = 4.5 \text{ V}$<br>$T_A = T_J = -40 \text{ to } 125^{\circ}\text{C}$                                                 | fdt                   | -                     | -                   | 7.5                    | %     |

| Frequency Modulation Range                                                                | V <sub>FB</sub> = 4.5 V (V <sub>FB-OL</sub> P)<br>65 kHz Version<br>100 kHz Version<br>130 kHz Version                        | f <sub>M</sub>        | ±5.1<br>±7.8<br>±10.5 | ±6<br>±9.2<br>±12.5 | ±6.9<br>±10.6<br>±14.5 | kHz   |

| Hopping Period                                                                            | $T_J = 25^{\circ}C$                                                                                                           | t <sub>HOP</sub>      | 7                     | 14.5                | 22                     | ms    |

| PWM CONTROL SECTION                                                                       |                                                                                                                               |                       |                       |                     |                        |       |

| Feedback(FB) Voltage Attenuation<br>(Note 9)                                              | V <sub>FB</sub> = 2~2.2 V                                                                                                     | A <sub>V</sub>        | 1/4.5                 | 1/4.0               | 1/3.5                  | -     |

| FB Impedance                                                                              | V <sub>FB</sub> = 4 V                                                                                                         | Z <sub>FB</sub>       | 10.4                  | 15.65               | 20.9                   | kΩ    |

| FB Clamp Voltage                                                                          | FB Pin Open                                                                                                                   | V <sub>FB-CL</sub>    | 4.75                  | 5.1                 | 5.4                    | V     |

| Maximum Duty Cycle                                                                        |                                                                                                                               | D <sub>MAX</sub>      | 70                    | 80                  | 90                     | %     |

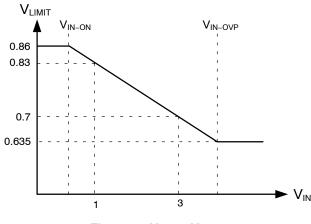

| Current Limit Threshold Voltage                                                           | $V_{IN} = 1 V$<br>$V_{IN} = 3 V$                                                                                              | V <sub>CS-LIMIT</sub> | 0.77<br>0.64          | 0.83<br>0.70        | 0.89<br>0.76           | V     |

| Current Limit Delay Time                                                                  | $T_J = 25^{\circ}C$                                                                                                           | t <sub>CLD</sub>      | -                     | 330                 | 450                    | ns    |

| Leading Edge Blanking Time (Note 9)                                                       | Steady State                                                                                                                  | t <sub>LEB</sub>      | 255                   | 305                 | 355                    | ns    |

| Slope Compensation Generation<br>Delay Time (Note 9)                                      | 65 kHz Version<br>100 kHz Version<br>130 kHz Version                                                                          | t <sub>D-SE</sub>     |                       | 6<br>4<br>2.99      | -<br>-<br>-            | μs    |

| Slope Compensation (Note 9)                                                               | Normalized to CS Signal<br>65 kHz Version<br>100 kHz Version<br>130 kHz Version                                               | S <sub>E</sub>        |                       | 30<br>46<br>60      |                        | mV/μs |

| <b>GREEN/BURST MODE SECTION</b>                                                           |                                                                                                                               |                       |                       |                     |                        |       |

| Green-mode Start Threshold Voltage                                                        | $T_J = 25^{\circ}C$                                                                                                           | V <sub>FB-SG</sub>    | -                     | 3.0                 | -                      | V     |

| Green-mode End Threshold Voltage                                                          | $T_J = 25^{\circ}C$                                                                                                           | V <sub>FB-EG</sub>    | -                     | 2.4                 | -                      | V     |

| Green-mode Start Frequency                                                                | V <sub>FB</sub> = V <sub>FB-SG</sub><br>65 kHz Version<br>100 kHz Version<br>130 kHz Version                                  | fosc-sg               | -<br>-                | 58.5<br>90<br>117   |                        | kHz   |

| Green-mode End Frequency                                                                  | V <sub>FB</sub> = V <sub>FB–EG</sub><br>65 kHz Version<br>100 kHz Version<br>130 kHz Version                                  | f <sub>OSC-EG</sub>   |                       | 25.6<br>28<br>29    | _<br>_<br>_            | kHz   |

| Burst-mode Start Threshold Voltage                                                        |                                                                                                                               | V <sub>FB-BURL</sub>  | 1.3                   | 1.6                 | 1.9                    | V     |

| Burst-mode End Voltage                                                                    |                                                                                                                               | V <sub>FB-BURH</sub>  | 1.5                   | 1.8                 | 2.1                    | V     |

#### **ELECTRICAL CHARACTERISTICS** ( $T_J = -40^{\circ}C$ to $+125^{\circ}C$ unless otherwise noted) (continued)

| Parameter                                                          | Test Conditions                                                                                       | Symbol                 | Min                 | Тур               | Max                 | Unit   |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------|---------------------|-------------------|---------------------|--------|

| GREEN/BURST MODE SECTION                                           |                                                                                                       |                        |                     |                   |                     |        |

| Burst-mode Hysteresis Voltage                                      | V <sub>FB-BURH</sub> – V <sub>FB-BURL</sub>                                                           | V <sub>BUR-HYS</sub>   | -                   | 0.2               | -                   | V      |

| Frequency Before Burst-mode                                        | V <sub>FB</sub> = V <sub>FB-BURL</sub>                                                                | fosc-bur               | 20                  | 23                | 26                  | kHz    |

| FB Impedance in Burst-mode                                         | V <sub>FB</sub> < V <sub>FB-BURL</sub> , V <sub>CC</sub> > V <sub>CC-ZFB</sub>                        | Z <sub>FB-BUR</sub>    | 55                  | 70                | 85                  | kΩ     |

| FB Impedance Switching Time from $Z_{FB-BUR}$ to $Z_{FB}$          | $T_J = 25^{\circ}C$                                                                                   | t <sub>ZFB</sub>       | 3.6                 | 6.2               | 8.8                 | ms     |

| $V_{CC}$ Threshold Voltage to Force $Z_{FB}$ Reset                 | V <sub>FB</sub> < V <sub>FB-BURL</sub> , V <sub>CC</sub> Decrease                                     | V <sub>CC-ZFB</sub>    | 9                   | 10                | 11                  | V      |

| PROTECTION SECTION                                                 |                                                                                                       |                        |                     |                   |                     |        |

| V <sub>CC</sub> Over-Voltage Protection (OVP)                      |                                                                                                       | V <sub>CC-OVP</sub>    | 24.5                | 26                | 27.5                | V      |

| V <sub>CC</sub> OVP Debounce Counting<br>Number                    | 65 kHz Version<br>100/130 kHz Version                                                                 | N <sub>VCCOVP</sub>    | 5<br>11             | 6<br>12           |                     | pulse  |

| Brown-in Threshold Voltage                                         | V <sub>CC</sub> = V <sub>CC-ON</sub> during HV start-up                                               | V <sub>IN-ON</sub>     | 0.85                | 0.9               | 0.95                | V      |

| Brown-out Threshold Voltage                                        |                                                                                                       | V <sub>IN-OFF</sub>    | 0.66                | 0.70              | 0.74                | V      |

| Brown-out Debounce Time                                            | V <sub>FB</sub> = V <sub>FB-CL</sub> , T <sub>J</sub> = 25°C<br>65/130 kHz Version<br>100 kHz Version | t <sub>D-VINOFF</sub>  | 45.0<br>58.5        | 62.5<br>81.2      | 70.0<br>91.0        | ms     |

| V <sub>IN</sub> Over-voltage Protection (OVP)<br>Threshold Voltage |                                                                                                       | V <sub>IN-OVP</sub>    | 3.65                | 3.85              | 4.05                | V      |

| VIN OVP Release Hysteresis                                         |                                                                                                       | V <sub>IN-OVPHYS</sub> | _                   | 0.2               | -                   | V      |

| VIN OVP Debounce Counting Number                                   | 65 kHz Version<br>100/130 kHz Version                                                                 | N <sub>VINOVP</sub>    | 5<br>11             | 6<br>12           |                     | pulse  |

| FB Open-loop Protection (OLP)<br>Threshold Voltage                 |                                                                                                       | V <sub>FB-OLP</sub>    | 4.1                 | 4.5               | 4.9                 | V      |

| FB OLP Debounce Time                                               | V <sub>FB</sub> = V <sub>FB-CL</sub> , T <sub>J</sub> = 25°C<br>65/130 kHz Version<br>100 kHz Version | t <sub>D-OLP</sub>     | 47<br>58            | 60<br>75          | 73<br>92            | ms     |

| Abnormal Over-current Protection<br>(AOCP) Threshold Voltage       | Default: Enable after t <sub>SS</sub>                                                                 | V <sub>CS-AOCP</sub>   | 1.15                | 1.25              | 1.35                | V      |

| Abnormal Over-current Blanking Time<br>(Note 9)                    |                                                                                                       | t <sub>ON-AOCP</sub>   | 75                  | 110               | 145                 | ns     |

| AOCP Debounce Counting Number                                      | Counting GATE Pulses                                                                                  | N <sub>AOCP</sub>      | -                   | 3                 | -                   | Pulses |

| Current Sensing Short Protection<br>(CSSP) Threshold Voltage       | V <sub>IN</sub> = 1 V<br>V <sub>IN</sub> = 3 V                                                        | V <sub>CS-CSSP</sub>   | 70<br>145           | 95<br>175         | 120<br>205          | mV     |

| PWM On-time to Trigger CSSP                                        | 65 kHz Version<br>100kHz Version<br>130kHz Version                                                    | t <sub>ON-CSSP</sub>   | 4.05<br>2.35<br>1.6 | 4.6<br>3.0<br>2.0 | 5.15<br>3.62<br>2.4 | μs     |

| CSSP Debounce Counting Number                                      | Counting GATE Pulses                                                                                  | N <sub>CSSP</sub>      | -                   | 2                 | -                   | Pulses |

| Thermal Shutdown (TSD) Junction<br>Temperature (Note 9)            |                                                                                                       | T <sub>SD</sub>        | 130                 | 140               | 150                 | °C     |

| TSD Release Hysteresis (Note 9)                                    |                                                                                                       | T <sub>SD-HYS</sub>    | _                   | 50                | -                   | °C     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

7. The parameter, although guaranteed, is fully tested in wafer test process.

8. Evaluated in a typical flyback converter with T<sub>A</sub> = 25°C.

9. This parameter is not tested in production, but verified by design or characterization.

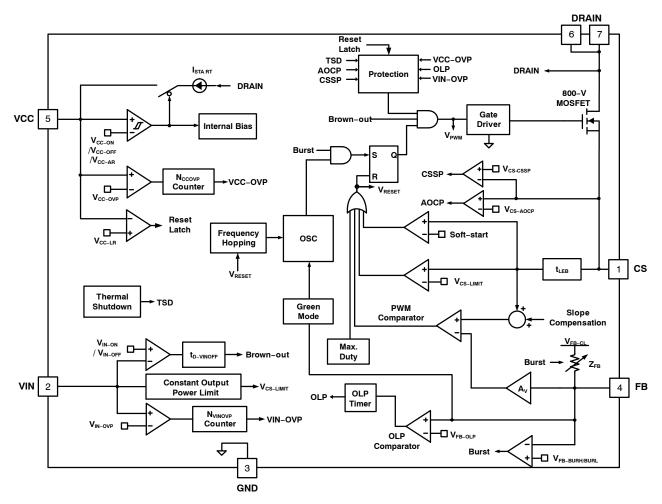

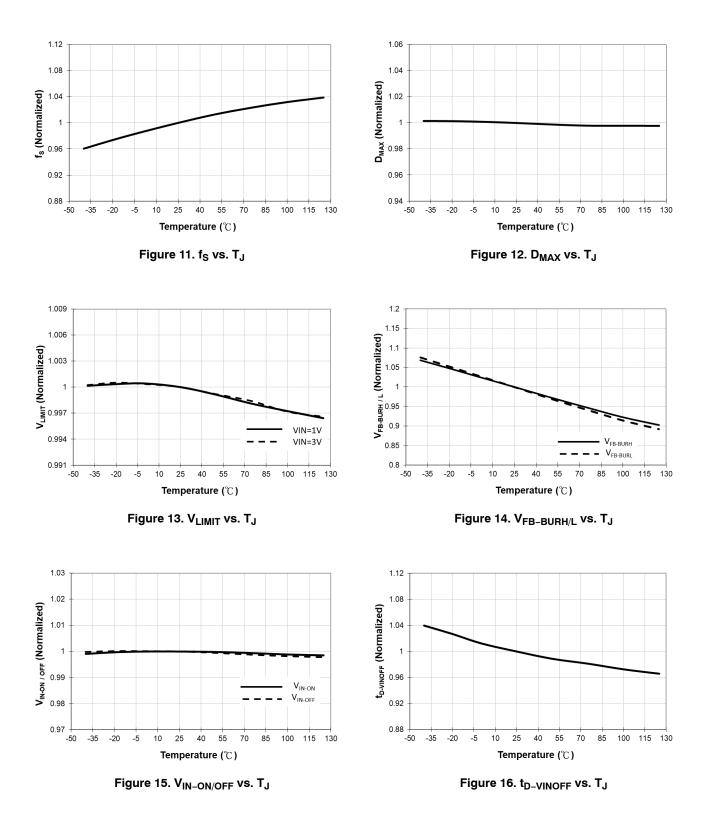

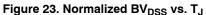

# **TYPICAL CHARACTERISTICS**

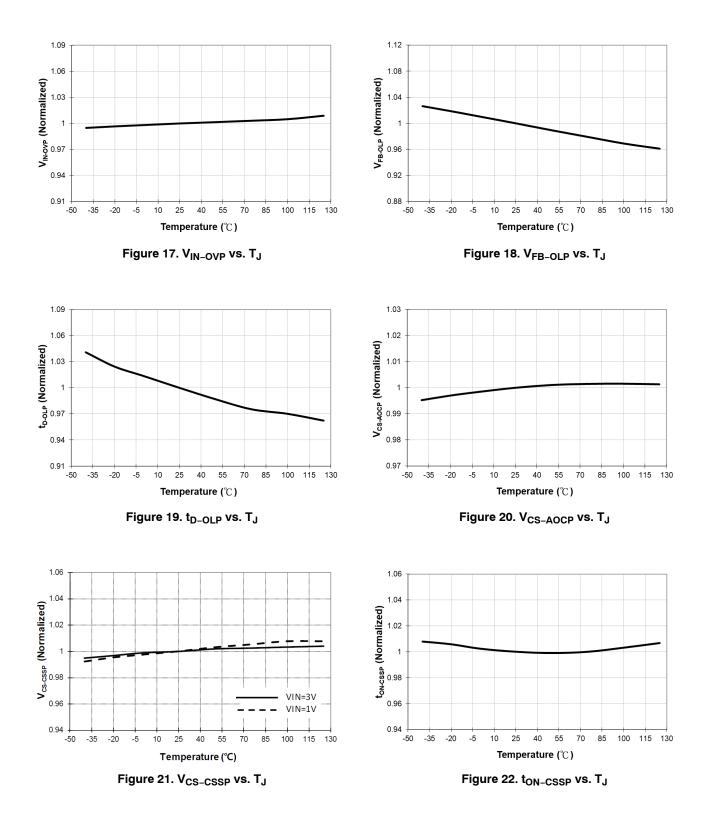

### TYPICAL CHARACTERISTICS (Continued)

### TYPICAL CHARACTERISTICS (Continued)

## TYPICAL CHARACTERISTICS (Continued)

····· NCP11184

- · ·NCP11185

NCP11187

- - -

100

10000

1000

100

10

1

0.1

f = 1MHz

$V_{GS} = 0V$

1

C<sub>oss</sub> (pF)

10

V<sub>DS</sub>, DRAIN TO SOURCE VOLTAGE (V)

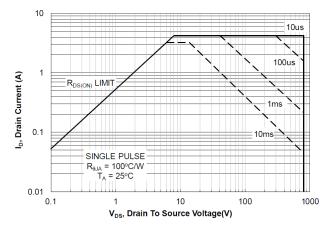

Figure 27. Safe Operating Area, NCP11184

Figure 26. Energy Loss in C<sub>OSS</sub> vs. V<sub>DS</sub>

Figure 28. Safe Operating Area, NCP11185

# TYPICAL CHARACTERISTICS (Continued)

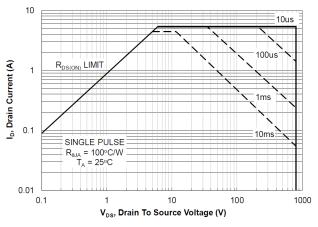

Figure 29. Safe Operating Area, NCP11187

Figure 30. Allowable Power Dissipation vs. T<sub>A</sub>

#### FUNCTIONAL DESCRIPTION

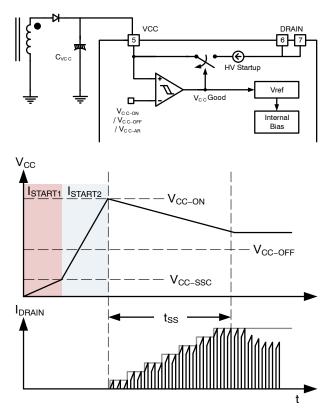

#### Startup & Soft-Start

At startup, an internal high–voltage(HV) startup circuit connecting the DRAIN pin supplies a constant startup current to internal circuits while charging the rest of current the external capacitor  $C_{VCC}$  as shown in Figure 31. While  $V_{CC}$  is lower than  $V_{CC-SSC}$ , the startup charging current is as small as ISTART1 to avoid NCP1118x damage when  $V_{CC}$ is shorted to the ground. Whereas, once  $V_{CC}$  exceeds  $V_{CC-SSC}$ , the startup charging current becomes I<sub>START2</sub>, which allows being fast startup.

After V<sub>CC</sub> reaches V<sub>CC-ON</sub>, the HV startup circuit is deactivated and NCP1118x begins soft-startup with increasing step-wise drain currents of the MOSFET to minimize an inrush current and reduce an output voltage overshoot during internal soft-start time t<sub>SS</sub>. Meanwhile, during this time, NCP1118x operates by the only supply current from C<sub>VCC</sub> until the auxiliary winding of main transformer provides sufficient operating current. Selecting sufficient C<sub>VCC</sub> is required. Otherwise, V<sub>CC</sub> could be decreased to V<sub>CC-OFF</sub> and V<sub>CC</sub> under-voltage lockout protection is triggered.

Figure 31. HV Startup Circuit and Soft Start

#### **Auto Restart Operation**

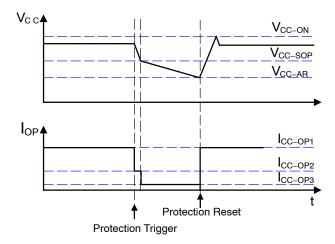

NCP1118x offers auto restart mode for the protections like feedback open-loop protection (OLP), VCC over-voltage protection (VCC OVP), and thermal shutdown (TSD) by over-temperature. Once one of the protections is triggered, the IC stops switching operation immediately and V<sub>CC</sub> starts decreasing by the internal operating current I<sub>DD-OP2</sub>. Then, after V<sub>CC</sub> decreases lower than V<sub>CC-SOP</sub>, V<sub>CC</sub> is discharged by I<sub>DD-OP3</sub>. As soon as V<sub>CC</sub> decreases to V<sub>CC-AR</sub>, all of protections is reset and the IC restart up, which secure a long enough restart time after a protection.

Figure 32. V<sub>CC</sub> Behavior in Auto Restart Mode

#### Latch Operation

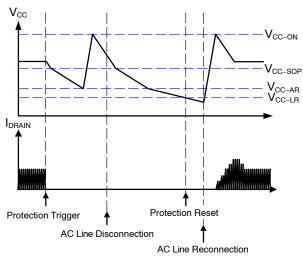

Protections with latch mode are available in latch–version products optionally. When any protections is triggered in the product, the switching is stopped immediately and  $V_{CC}$  decreases. Once  $V_{CC}$  touches  $V_{CC-AR}$ , the internal HV startup circuit restarts to supply operating current. However, no switching operation will be taken place until  $V_{CC}$  decreases to  $V_{CC-LR}$  and a protection is reset. In addition,  $V_{CC}$  is discharged by  $I_{DD-OP4}$  in this  $V_{CC}$  range. In the end, this latch–protection reset can happen only when an input voltage is disconnected and the HV startup circuit cannot supply an operating current any longer. Next reconnection of an input voltage can make IC restart.

Figure 33. VCC Behavior in Latch Mode

Figure 34. PWM Control Block

#### **PWM Control Operation**

NPC1118x employs peak-current mode pulse width modulation (PWM) control method to regulate output voltage. As shown in Figure 34, an opto-coupler and shunt regulator are typically used for the feedback network, which controls a feedback voltage  $V_{FB}$ . A sensing resistor is connected to CS pin and used to detect a drain current when the integrated MOSFET turns on.

Meanwhile,  $V_{FB}$  is attenuated by the internal amplifier with a gain of  $A_V$ , that becomes  $(A_V \times (V_{FB} - V_F))$  where  $V_F$ is forward voltage drop of an series–connected diode at FB pin inside node. Simply comparing the attenuated voltage from the feedback voltage  $V_{FB}$  with a sensed drain current  $V_{CS}$  makes it possible to control the switching duty cycle. When  $V_{CS}$  reaches the attenuated voltage, the PWM comparator generates turn–off signal to the MOSFET immediately. In case, an output voltage  $V_O$  increase makes a current of the photo–diode increase, which leads  $V_{FB}$  to decrease and duty cycle is reduced as well. Accordingly, an output power transferred to the secondary side is limited.

In addition, whenever the integrated MOSFET turns on, a leading edge current occurs on the sense resistor  $R_{CS}$ , which could lead premature termination of the gate turn-on signal. To avoid it, a leading-edge blanking time  $t_{LEB}$  is employed. During the  $t_{LEB}$ , PWM comparator output is blocked so that turn-on signal to the gate can be maintained.

#### **Frequency Hopping**

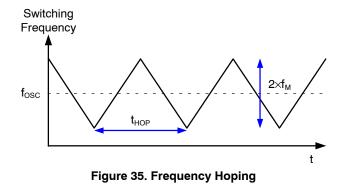

Asynchronous frequency-hopping function built-in the oscillator generates consistent jittering in switching frequency. This frequency jittering prevents switching noises from being concentrated in its switching frequency band and distributes them to alleviate quasi-peak noises. The frequency is varied with period of  $t_{HOP}$  and amplitude of double of  $f_M$  as can be seen in Figure 35.

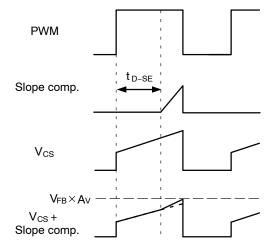

#### Slope Compensation

A slope compensation is employed to prevent sub-harmonic oscillator and improve stability. A sawtooth signal is generated and added  $V_{CS}$  after pulse width of PWM signal exceeds  $t_{D-SE}$  which is around 40% of duty cycle to an switching frequency  $f_{OSC}$ . The amount of signals is compared with the internal feedback signal, which determines PWM on time.

Figure 36. Slope Compensation

Slope of the sawtooth signal and  $t_{D-SE}$  are 30 mV/µs & 6 µs for 65 kHz of  $f_{OSC}$ , 46 mV/µs & 3.9 µs for 100 kHz of  $f_{OSC}$  and 60 mV/µs & 3 µs for 130 kHz of  $f_{OSC}$ . The delay time  $t_{D-SE}$  is 6 µs for 65–kHz version, 3.9 µs for 100–kHz version, and 3 µs for 130–kHz version, respectively.

#### **Constant Over-power Limit**

For constant output power limit at the entire input voltage range, a peak current limit threshold level  $V_{LIMIT}$  is controlled by the voltage of VIN pin  $V_{IN}$ . As can be seen in Figure 37,  $V_{LIMIT}$  is decreased as  $V_{IN}$  increases and maximum output power is limited automatically.

VIN pin is typically connected to the rectified AC line input voltage through the resistors divider.

Figure 37. V<sub>IN</sub> vs. V<sub>LIMIT</sub>

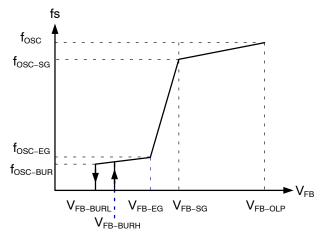

#### Green-mode & Burst-mode Operation

To improve efficiency while reducing power dissipation, the proprietary green-mode function reduces switching frequency as load is decreased and forces PWM operation to stop at light load condition. The switching frequency depends on  $V_{FB}$  as illustrated in Figure 38.

Figure 38. PWM Frequency vs. V<sub>FB</sub>

After V<sub>FB</sub> is lower than V<sub>FB-SG</sub>, the switching frequency is steeply decreased from the green–mode start frequency  $f_{OSC-SG}$  to the green–mode end frequency  $f_{OSC-EG}$  until V<sub>FB</sub> touches the green–mode end level V<sub>FB-EG</sub>. When V<sub>FB</sub> is lower than the burst–mode start level V<sub>FB-BURL</sub>, the PWM controller is halted and starts entering the burst–mode operation. In this mode, the most of internal circuits are disabled so that internal operating current consumption is drastically decreased, thereby standby power figure can be improved as well. Meanwhile, all of internal circuits is enabled and the PWM switching is resumed as soon as V<sub>FB</sub> is higher than the burst–mode end level V<sub>FB-BURH</sub>.

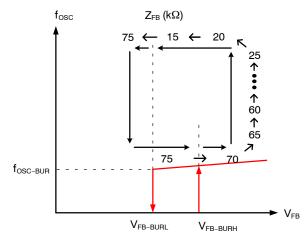

#### Feedback Impedance Switching in Burst-mode

To minimize power consumption in no–load condition especially, a method to switch FB–pin impedance  $Z_{FB}$  in burst–mode is implemented. Figure 39 illustrates  $Z_{FB}$ variation depending on  $V_{FB}$ . By increasing  $Z_{FB}$ , amount of current consumed by the feedback network including the opto–coupler can be reduced. When  $V_{FB}$  touches  $V_{FB-BURL}$ ,  $Z_{FB}$  is switched from 15 k $\Omega$  to  $Z_{FB-BUR}$  of typical 70 k $\Omega$  immediately. Whereas, when  $V_{FB}$  increases and gets higher than  $V_{FB-BURH}$ ,  $Z_{FB}$  decreases stepwise and is back to normal  $Z_{FB}$  of 15 k $\Omega$ .

Figure 39. Z<sub>FB</sub> Switching

Meanwhile, when  $V_{CC}$  decreases to  $V_{CC-ZFB}$  while  $Z_{FB}$  switches to  $Z_{FB-BUR}$ , the  $Z_{FB}$  of 70 k $\Omega$  is forced to back to normal  $Z_{FB}$  to prevent  $V_{CC-UVLO}$  by touching  $V_{CC-OFF}$ .

#### VCC Over–Voltage Protection (V<sub>CC–OVP</sub>)

To prevent damage from over–voltage to V<sub>CC</sub> pin, VCC over–voltage protection (OVP) is included. Once V<sub>CC</sub> is over the over–voltage protection voltage V<sub>CC–OVP</sub> which lasts for fixed time duration corresponding to the V<sub>CC</sub> OVP debounce counting number N<sub>VCCOVP</sub> the PWM will be disabled immediately. This protection can be reset only when V<sub>CC</sub> is lower than V<sub>CC–AR</sub> in the auto–restart mode.

#### FB Open Loop Protection (OLP)

When the output voltage drops below a regulation voltage or FB pin is open circuit, FB Voltage  $V_{FB}$  will settle  $V_{FB-OLP}$  because a shunt regulator such as NCP431 no longer draws the opto-coupler current down. This is regarded as FB OL situation. If it lasts longer than  $t_{D-OLP}$  FB OLP is triggered and PWM operation is stopped immediately. This protection can be reset when  $V_{CC}$  is below than  $V_{CC-OFF}$ .

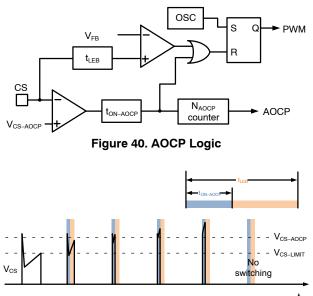

#### Abnormal Over-current Protection (AOCP)

The AOCP stops PWM switching to prevent any damage of NCP1118x from excessive drain current caused by either of the secondary–side rectifier diode or the transformer is shorted. It has blanking time  $t_{ON-AOCP}$  and doubouncing counting number  $N_{AOCP}$  to prevent AOCP activation prematurely from a leading edge current at an instance of turn–on of the main MOSFET in normal operation. When extreme current flows above the abnormal over–current threshold level  $V_{CS-AOCP}$  which lasts over  $t_{ON-AOCP}$  in abnormal conditions, the main MOSFET turns off immediately and the internal counter counts up the number of occurrence. Once this situation occurs the number of  $N_{AOCP}$  consecutively, then AOCP is triggered and PWM switching stops immediately until  $V_{CC}$  decreases to  $V_{CC-LR}$ .

Figure 41. AOCP Operation

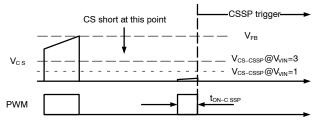

#### **Current–Sense Short Protection**

When CS pin is shorted to GND pin due to soldering defect or some dust, a drain current– cannot be sensed properly. It causes excessive drain current and ends up the switcher damage. If PWM on–time is longer than  $t_{ON-CSSP}$  while  $V_{CS}$  is less than  $V_{CS-CSSP}$ , the CSSP circuit regards as a situation of CS pin short and turns off PWM switching immediately. If this state persists consecutively NCSSP times, then PWM switching operation stops permanently. This protection cannot be reset until unplugging the input

voltage. Meanwhile,  $V_{CS-CSSP}$  is varied depending on VIN level to avoid abnormal detection of CSSP at low input voltage.  $N_{CSSP}$  is different in either of startup or normal operation as well.

Figure 42. CSSP Waveform

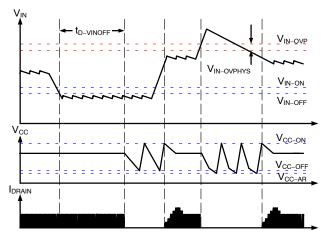

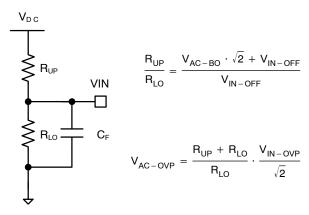

#### Brown-out/Line Over-voltage Protection (Line OVP)

Brown-out and Line-OVP are performed by detecting line input voltage through VIN pin. VIN pin is typically connected to a resistive divider. They can connect to either of the ac rectifier or dc-link capacitor as can be seen in Figure 2 and Figure 3.

As for Brown-in operation, if a sensed V<sub>IN</sub> is above V<sub>IN-ON</sub> and V<sub>CC</sub> is higher than V<sub>CC-ON</sub>, then NCP1118x starts up and operates. Whereas, Brown-out is triggered when V<sub>IN</sub> is kept less than V<sub>IN-OFF</sub> for a debounce time t<sub>D-VINOFF</sub>, the PWM switching stop. The protection is not released until V<sub>IN</sub> is higher than V<sub>IN-ON</sub>.

Meanwhile, when  $V_{IN}$  is higher than  $V_{IN-OVP}$  and the number of PWM switching last longer than Line–OVP debouncing counting number  $N_{VINOVP}$ . Line–OVP is triggered and PWM switching stops. Whereas, this protection can be released and allows NCP1118x to restart with soft–start when  $V_{IN}$  decreases by  $V_{IN-OVPHYS}$  lower and  $V_{CC}$  is higher than  $V_{CC-ON}$ .

An ac input voltage for brown-out and Line–OVP can be simply set up by equations shown in Figure 43. Since it, a brown-in level is naturally determined by  $V_{IN-ON}$ . Additionally, it is recommended to add a capacitor of tens nano–farad to decouple switching noise and sense a voltage stably.

Figure 43. Brown-in/out & Line-OVP

Figure 44. Line Voltage Detection

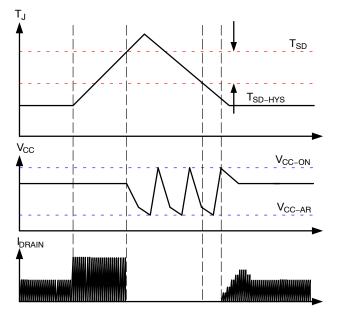

#### **Thermal Shutdown (TSD)**

TSD limits total power dissipation of NCP1118x by detecting temperature. When the junction temperature  $T_J$  exceeds  $T_{SD}$ , this switcher shuts down immediately. It can be recovery when  $T_J$  reduces by below  $T_{TSD-HYS}$ . During this TSD status, HV startup circuit performs on and off repeatedly.

Figure 45. Thermal Shutdown

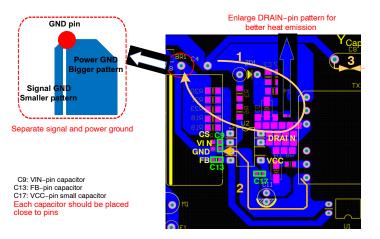

# PCB LAYOUT RECOMMENDATIONS

This section introduces some PCB design tips for designers to minimize EMI (Electromagnetic Interference) and make robust switched mode power supplies using NCP1118x.

- High-frequency switching current/voltage makes PCB layout a very important design issue. Good PCB layout minimizes excessive EMI and helps the power supply survive during surge/ESD (Electro Static Discharge) tests.

- To improve EMI performance and reduce line frequency ripples, the output of the bridge rectifier should connect to bulk capacitor as close as possible.

- As indicated by 1 in Figure 46, the high-frequency current loop is formed by beginning of the bridge rectifier, bulk capacitor, a power transformer to return to bulk capacitor. The area enclosed by this current loop should be designed as small as possible to reduce conduction and radiation noise. Keep the traces short, direct, and wide. High-voltage traces related the drain of MOSFET and RCD snubber should be kept far away from control circuits to prevent noise interference affecting low voltage signal paths at the control part.

- As indicated by 2, the ground of control circuits should be connected first, then to other circuitry.

- Place  $C_{VCC}$  as close to VCC pin of the NCP1118x as possible for good decoupling. It is recommended to use a few of micro-farad capacitor and 100 nF ceramic capacitor for high frequency noise decoupling as well.  $C_{VIN}$  pin and  $C_{FB}$  pin capacitor are also recommended to place as close as possible to VIN and FB pin.

There are some suggestions for grounding connection.

- GND: There are two kinds of GND in power conversion board and should be separated for avoiding interference and better performance.

- Generally, lightning surge could pass through stray capacitance of the transformer from the primary side to the secondary side or vice-versa. Regard with that, some points should be taken into account when designing PCB, such as placing control circuit parts, EMI filters and an Y-capacitor.

- 3 could be a point-discharger route to bypass the static electricity energy. It is suggested to map out this discharge route and not to place any low voltage components on the route.

- Should a Y-cap be required between primary and secondary, connect this Y-cap to the positive terminal of bulk capacitor. If this Y-cap is connected to primary GND, it should be connected to the negative terminal of bulk capacitor (GND) directly. Point discharge of this Y-cap helps for ESD; however, the creepage between these two pointed ends should be at least 5 mm according to safety requirements.

- Thermal Considerations:

Power MOSFET dissipates heats during switching operation. If chip temperature exceeds TSD, thermal shutdown would be triggered and NCP1118x stops operating to protect itself from damage. The path of lowest thermal impedance from NCP1118x chip to externals is from DRAIN pin. It is recommended to increase area of connected copper to DRAIN pin as much as possible.

Figure 46. Layout Considerations

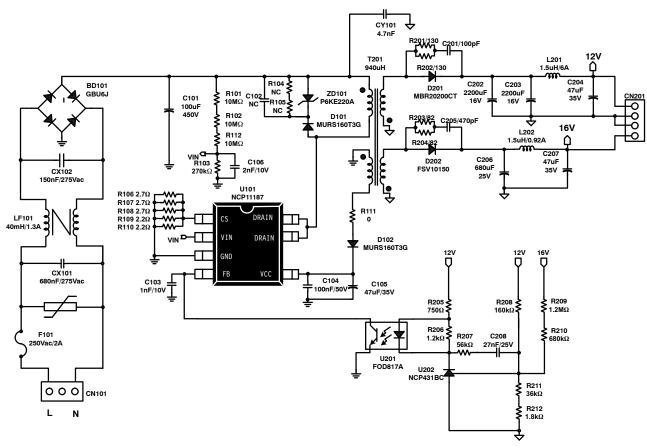

# **DESIGN EXAMPLE**

This is a design example of 45 W isolated flyback converter using NCP1118765. For further detail information, go to the webpage of NCP1118x.

#### EVB No: NCP11187A65F45GEVB

| Devices             | Applications                                 | Topology                            | Output Power                                 |

|---------------------|----------------------------------------------|-------------------------------------|----------------------------------------------|

| NCP11187A65         | White Goods and Industrial<br>Power Supplies | Isolated Flyback                    | 45 W                                         |

| Input Voltage       | Output Spec.                                 | Efficiency                          | Standby Power                                |

| 85–265 Vac          | 12 V/3.5 A &<br>16 V/0.2 A                   | > 88%<br>@ Full-load                | < 50 mW<br>@ 230 Vac                         |

| Package Temperature | Operating Temperature                        | Cooling Method                      | Board Size                                   |

| 90°C @ $T_A = 50°C$ | 0~50°C                                       | Natural Convection<br>In Open Frame | 145 x 60 x 30 mm<br>2.83 W/inch <sup>3</sup> |

# REFERENCES

For more specific designs, refer to the links below:

- AN-4148 Audible Noise Reduction Technique for FPS Applications <u>https://www.onsemi.com/pub/Collateral/AN-4148.pdf</u>

- AN-4137 Design Guidelines for Off-line Flyback Converters Using Power Switch <u>https://www.onsemi.com/pub/Collateral/AN-4137.pdf</u>

- AN-4140 Transformer Design Consideration for Offline Flyback Converters Using Power Switch <u>https://www.onsemi.com/pub/Collateral/AN-4140.pdf</u>

- NCP1118x Family Simplis Behavior Model

- <u>NCP1118x Family Excel-based Design Tool</u>

# **ORDERING INFORMATION**

#### **ORDERING INFORMATION**

| Device         | R <sub>DS(ON)</sub> (Ω) | f <sub>OSC</sub> (kHz) | Package   | Shipping        |

|----------------|-------------------------|------------------------|-----------|-----------------|

| NCP11184A065PG | 2.25                    | 65                     | PDIP-7    | 50 Units / Rail |

| NCP11185A065PG | 1.3                     | 65                     | (Pb-Free) |                 |

| NCP11187A065PG | 0.87                    | 65                     | 1         |                 |

| NCP11184A100PG | 2.25                    | 100                    | 1         |                 |

| NCP11187A100PG | 0.87                    | 100                    | 1         |                 |

| NCP11184A130PG | 2.25                    | 130                    | 1         |                 |

| NCP11185A130PG | 1.3                     | 130                    | 1         |                 |

mWSaver is a registered trademark of Semiconductor Components Industries, LLC. Energy Star is a registered trademark of the U.S. Environmental Protection Agency

#### PACKAGE DIMENSIONS

#### PDIP-7 (PDIP-8 LESS PIN 6) CASE 626A

ISSUE C

WITH LEADS CONSTRAINED NOTE 5

NOTES

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 3.

- DIMENSIONING AND TOLEHANCING PEH ASME Y14.5M, 1994 CONTROLLING DIMENSION: INCHES. DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACK-AGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3. DIMENSIONS D, D1 AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE 4

- NOT TO EXCEED 0.10 INCH. DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM 5

- PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR TO DATUM C.

- DIMENSION 68 IS MEASURED AT THE LEAD TIPS WITH THE LEADS UNCONSTRAINED. 6

- DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE LEADS, WHERE THE LEADS EXIT THE BODY. 7

- PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE 8. CORNERS)

|     | INC   | HES   | MILLIMETERS |       |  |

|-----|-------|-------|-------------|-------|--|

| DIM | MIN   | MAX   | MIN         | MAX   |  |

| Α   |       | 0.210 |             | 5.33  |  |

| A1  | 0.015 |       | 0.38        |       |  |

| A2  | 0.115 | 0.195 | 2.92        | 4.95  |  |

| b   | 0.014 | 0.022 | 0.35        | 0.56  |  |

| b2  | 0.060 | ) TYP | 1.52        | TYP   |  |

| С   | 0.008 | 0.014 | 0.20        | 0.36  |  |

| D   | 0.355 | 0.400 | 9.02        | 10.16 |  |

| D1  | 0.005 |       | 0.13        |       |  |

| E   | 0.300 | 0.325 | 7.62        | 8.26  |  |

| E1  | 0.240 | 0.280 | 6.10        | 7.11  |  |

| е   | 0.100 | BSC   | 2.54 BSC    |       |  |

| eB  |       | 0.430 |             | 10.92 |  |

| L   | 0.115 | 0.150 | 2.92        | 3.81  |  |

| М   |       | 10°   |             | 10°   |  |

onsemi. OnSemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries. LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### Email Requests to: orderlit@onsemi.com

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Phone: 011 421 33 790 2910

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

٥