#### **General Description**

The MAX488A/MAX4889A high-speed passive switches route PCI Express® (PCIe) data between two possible destinations. The MAX4888A is a quad single-pole/double-throw (4 x SPDT) switch ideally suited for switching two half lanes of PCIe data between two destinations. The MAX4889A is an octal single-pole/double-throw (8 x SPDT) switch ideal for switching four half lanes of PCIe data between four destinations. The MAX4888A/ MAX4889A feature a single digital control input (SEL) to switch signal paths.

The MAX488A/MAX4889A are fully specified to operate from a single +3.0V to +3.6V power supply<sup>††</sup>. The MAX4888A is available in a 3.5mm x 5.5mm, 28-pin TQFN package. The MAX4889A is available in a 3.5mm x 9.0mm, 42-pin TQFN package. Both devices operate over the -40°C to +85°C temperature range.

#### **Features**

- ♦ Single +3.0V to +3.6V Power-Supply Voltage

- ♦ Low Same-Pair Skew of 7ps

- ♦ Low 120µA (Max) Quiescent Current

- ♦ Supports PCIe Gen I and Gen II Data Rates

- **♦** Flow-Through Pin Configuration for Ease of Layout

- **♦ Industry-Compatible Pinout**

- **♦ Lead-Free Packaging**

**Applications**

**Desktop Computers** Servers/Storage Area Networks Laptops

### **Ordering Information/Selector Guide**

| PART         | TEMP RANGE     | PIN-PACKAGE | CONFIGURATION   |  |  |

|--------------|----------------|-------------|-----------------|--|--|

| MAX4888AETI+ | -40°C to +85°C | 28 TQFN-EP* | Two Half Lanes  |  |  |

| MAX4889AETO+ | -40°C to +85°C | 42 TQFN-EP* | Four Half Lanes |  |  |

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

††Contact factory if operating at +2.5V or +1.8V. PCI Express is a registered trademark of PCI-SIG Corp. Typical Application Circuit appears at end of data sheet.

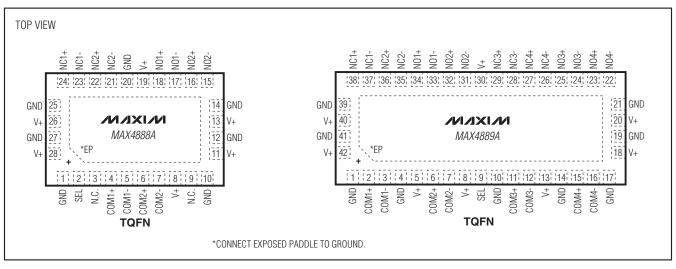

### Pin Configurations

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unless otherwise noted.) |

|-----------------------------------------------------------|

| V+0.3V to +4V                                             |

| SEL, COM, NO, NC (Note 1)0.3V to (V+ + 0.3V)              |

| COM NO  ,   COM NC   (Note 1) 0 to +2V                    |

| Continuous Current (COM_ to NO/NC)±70mA                   |

| Peak Current (COM to NO/NC)                               |

| (pulsed at 1ms, 10% duty cycle)±70mA                      |

| Continuous Current (SEL)±30mA                             |

| Peak Current (SEL)                                        |

| (pulsed at 1ms, 10% duty cycle)±150mA                     |

| Continuous Power Dissipation (T <sub>A</sub> = |                       |

|------------------------------------------------|-----------------------|

| 28-Pin TQFN (derate 20.8mW/°C a                | above +70°C) 1666.7mW |

| 42-Pin TQFN (derate 35.7mW/°C a                | above +70°C)2857.1mW  |

| Operating Temperature Range                    | 40°C to +85°C         |

| Storage Temperature Range                      | 65°C to +150°C        |

| Lead Temperature (soldering, 10s)              | +300°C                |

| Junction Temperature                           | +150°C                |

|                                                |                       |

Note 1: Signals on SEL, NO\_\_, NC\_\_ or COM\_\_ exceeding V+ or GND are clamped by internal diodes. Limit forward-diode current to maximum current rating.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V + = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V + = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                         | SYMBOL                                                                                       | CONDITIONS                                                                                                        | MIN | TYP  | MAX        | UNITS |

|---------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|------|------------|-------|

| ANALOG SWITCH                                     |                                                                                              |                                                                                                                   |     |      |            |       |

| Analog-Signal Range                               | V <sub>COM_</sub> ,<br>V <sub>NO_</sub> , V <sub>NC_</sub>                                   |                                                                                                                   |     |      | (V+ - 1.2) | V     |

| Voltage Between COM and NO/NC                     | V <sub>COM_</sub> -<br>  V <sub>NO_</sub>   ,<br>  V <sub>COM_</sub> -<br>  V <sub>NC_</sub> |                                                                                                                   | 0   |      | 1.8        | V     |

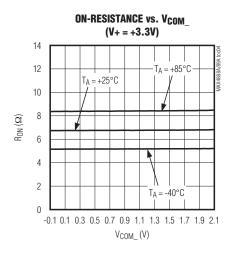

| On-Resistance                                     | Ron                                                                                          | V+ = +3.0V, I <sub>COM</sub> _ = 15mA,<br>V <sub>NO</sub> _ or V <sub>NC</sub> _ = 0V, +1.8V                      |     | 7    |            | Ω     |

| On-Resistance Match Between Pairs of Same Channel | R <sub>ON</sub>                                                                              | V+ = +3.0V, I <sub>COM</sub> _ = 15mA,<br>V <sub>NO</sub> _ or V <sub>NC</sub> _ = 0V (Notes 3, 4)                |     | 0.1  | 1          | Ω     |

| On-Resistance Match<br>Between Channels           | R <sub>ON</sub>                                                                              | V+ = +3.0V, I <sub>COM</sub> _ = 15mA,<br>V <sub>NO</sub> _ or V <sub>NC</sub> _ = 0V (Notes 3, 4)                |     | 0.6  | 2          | Ω     |

| On-Resistance Flatness                            | RFLAT(ON)                                                                                    | V+ = +3.0V, I <sub>COM</sub> _ = 15mA<br>V <sub>NO</sub> _ or V <sub>NC</sub> _ = 0V, +1.8V (Notes 4, 5)          |     | 0.06 | 2          | Ω     |

| NO_ or NC_ Off-Leakage<br>Current                 | INO_(OFF) INC_(OFF)                                                                          | V+ = +3.6V, V <sub>COM</sub> _ = 0V, +1.8V,<br>V <sub>NO</sub> _ or V <sub>NC</sub> _ = +1.8V, 0V                 | -1  |      | +1         | μΑ    |

| COM_ On-Leakage<br>Current                        | ICOM_(ON)                                                                                    | V+ = +3.6V, V <sub>COM</sub> = 0V, +1.8V,<br>V <sub>NO</sub> or V <sub>NC</sub> = V <sub>COM</sub> or unconnected | -1  |      | +1         | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V + = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V + = +3.3V, T_A = +25^{\circ}\text{C}.)$  (Note 2)

|                                  |                       |                                                       |                                         |      |      |           | T     |

|----------------------------------|-----------------------|-------------------------------------------------------|-----------------------------------------|------|------|-----------|-------|

| PARAMETER                        | SYMBOL                | CON                                                   | DITIONS                                 | MIN  | TYP  | MAX       | UNITS |

| DYNAMIC                          |                       | <u> </u>                                              |                                         |      |      |           |       |

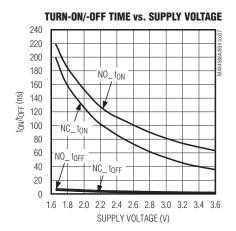

| Turn-On Time                     | ton                   |                                                       | $DV$ , $R_L = 50Ω$ , Figure 1           |      | 90   | 250       | ns    |

| Turn-Off Time                    | toff                  |                                                       | OV, $R_L = 50\Omega$ , Figure 1         |      | 10   | 50        | ns    |

| Propagation Delay                | tpD                   | $R_S = R_L = 50\Omega$ , unk                          |                                         |      | 50   |           | ps    |

| Output Skew Between Pairs        | t <sub>SK1</sub>      | $R_S = R_L = 50\Omega$ , unb<br>any two pairs, Figure | alanced; skew between<br>e 2            |      | 50   |           | ps    |

| Output Skew Between Same<br>Pair | t <sub>SK2</sub>      | $R_S = R_L = 50\Omega$ , unb<br>two lines on same p   | alanced; skew between<br>pair, Figure 2 |      | 10   |           | ps    |

| On-Loss                          | GLOS                  | $R_S = R_L = 50\Omega$ , unbalanced,                  | 1MHz < f < 100MHz                       |      | -0.5 |           | - dB  |

| OII-LOSS                         | GLUS                  | Figure 3                                              | 500MHz < f < 1.25GHz                    |      | -1.4 |           |       |

| Crosstalk                        | V <sub>CT1</sub>      | Crosstalk between any two pairs,                      | f = 50MHz                               |      | -53  |           | - dB  |

| Clossiain                        | VCII                  | $R_S = R_L = 50\Omega$ , unbalanced, Figure 3         | f = 1.25GHz                             |      | -32  |           | ub    |

| Signaling Data Rate              | BR                    | $R_S = R_L = 50\Omega$                                |                                         |      | 5.0  |           | Gbps  |

|                                  |                       | Signal = 0dBm,                                        | f = 10MHz                               |      | -56  |           |       |

| Off-Isolation                    | V <sub>ISO</sub>      | $R_S = R_L = 50\Omega$ ,<br>Figure 3                  | f = 1.25GHz                             |      | -26  |           | dB    |

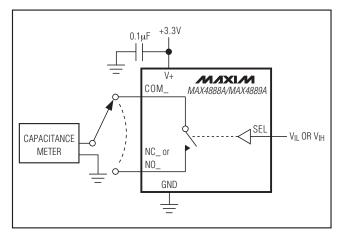

| NO_/NC_ Off-Capacitance          | CNO_/NC_(OFF)         | Figure 4                                              |                                         |      | 1    |           | pF    |

| COM_ On-Capacitance              | C <sub>COM</sub> (ON) | Figure 4                                              |                                         |      | 2    |           | pF    |

| LOGIC INPUT                      | _(-,                  |                                                       |                                         |      |      |           |       |

| Input-Logic Low                  | VIL                   |                                                       |                                         |      |      | 0.5       | V     |

| Input-Logic High                 | VIH                   |                                                       |                                         | 1.4  |      |           | V     |

| Input-Logic Hysteresis           | VHYST                 |                                                       |                                         |      | 100  |           | mV    |

| Input Leakage Current            | I <sub>IN</sub>       | V <sub>SEL</sub> = 0V or V+                           |                                         | -1   |      | +1        | μΑ    |

| POWER SUPPLY                     |                       | _                                                     | l                                       |      |      |           |       |

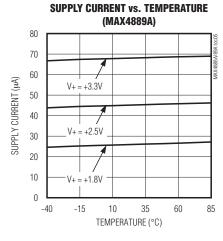

| Power-Supply Range               | V+                    |                                                       |                                         | 1.65 |      | 3.60      | V     |

| V+ Supply Current                | I+                    | V <sub>SEL</sub> = 0V or V+                           | MAX4888A<br>MAX4889A                    |      |      | 60<br>120 | μΑ    |

| Input Leakage Current            | I <sub>IN</sub>       | V <sub>SEL</sub> = 0V or V+                           |                                         | -1   |      | +1        | μA    |

| ESD PROTECTION                   | 1 '114                | 1.055 0.0                                             |                                         | •    |      |           | ] Pr. |

| COM_+, COM                       |                       | Human Body Model                                      |                                         |      | ±6   |           | kV    |

|                                  |                       | · -                                                   |                                         |      |      |           |       |

- **Note 2:** All units are 100% production tested at  $T_A = +85^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization and are not production tested.

- **Note 3:**  $\Delta R_{ON} = R_{ON(MAX)} R_{ON(MIN)}$ .

- Note 4: Guaranteed by design. Not production tested.

- **Note 5:** Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the specified analog signal range.

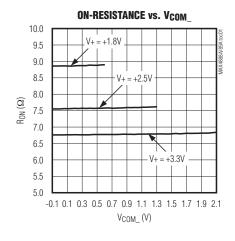

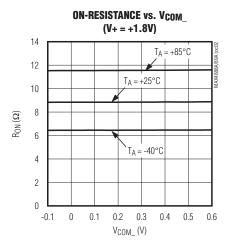

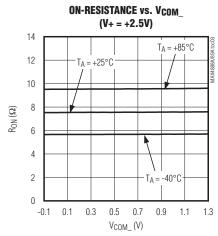

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

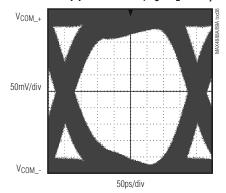

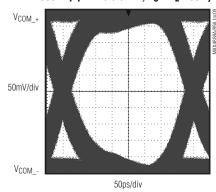

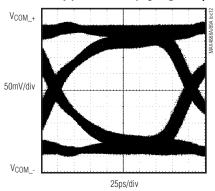

# EYE DIAGRAM (V+ = +1.8V, f = 1.25GHz, 600mVp-p PRBS SIGNAL, $R_S = R_L = 50\Omega$ )†

\*PRBS = PSEUDORANDOM BIT SEQUENCE † = GEN 1, 2.5Gbps; U1 = 400ps

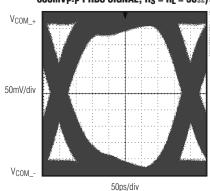

# EYE DIAGRAM $(V+=+2.5V, f=1.25GHz, \\ 600mV_{P-P} PRBS SIGNAL, R_S=R_L=50\Omega) \dagger$

\*PRBS = PSEUDORANDOM BIT SEQUENCE † = GEN 1, 2.5Gbps; U1 = 400ps

# EYE DIAGRAM $(V+=+3.3V, \ f=1.25 GHz, \\ 600mV_{P-}PRBS SIGNAL, \ R_S=R_L=50\Omega)^{\dagger}$

\*PRBS = PSEUDORANDOM BIT SEQUENCE † = GEN 1, 2.5Gbps; U1 = 400ps

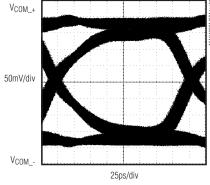

# $\label{eq:constraint} \begin{aligned} & \text{EYE DIAGRAM} \\ & \text{(V+ = +1.8V, f = 2.5GHz,} \\ & \text{600mVp-p PRBS SIGNAL, } R_S = R_L = 50 \Omega) \\ \end{aligned}$

\*PRBS = PSEUDORANDOM BIT SEQUENCE †† = GEN 11, 5.0Gbps; U1 = 200ps

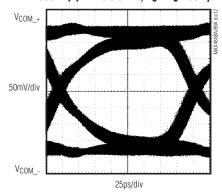

# EYE DIAGRAM (V+ = +2.5V, f = 2.5GHz, 600mVp-p PRBS SIGNAL, $R_S = R_L = 50\Omega$ )††

\*PRBS = PSEUDORANDOM BIT SEQUENCE †† = GEN 11, 5.0Gbps; U1 = 200ps

# EYE DIAGRAM $(V+=+3.3V, f=2.5 GHz, \\ 600mV_{P-P} PRBS SIGNAL, R_S=R_L=50\Omega) \dagger\dagger$

\*PRBS = PSEUDORANDOM BIT SEQUENCE †† = GEN 11, 5.0Gbps; U1 = 200ps

### \_Pin Description

| PIN                          |                                     |       |                                                                                                                                                                                                        |  |

|------------------------------|-------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX4888A MAX4889A            |                                     | NAME  | FUNCTION                                                                                                                                                                                               |  |

| 1, 10, 12, 14,<br>20, 25, 27 | 1, 4, 10, 14, 17,<br>19, 21, 39, 41 | GND   | Ground                                                                                                                                                                                                 |  |

| 2                            | 9                                   | SEL   | gital Control Input                                                                                                                                                                                    |  |

| 3, 9                         | _                                   | N.C.  | No Connection. Not internally connected.                                                                                                                                                               |  |

| 4                            | 2                                   | COM1+ | Analog Switch 1. Common Positive Terminal.                                                                                                                                                             |  |

| 5                            | 3                                   | COM1- | Analog Switch 1. Common Negative Terminal.                                                                                                                                                             |  |

| 6                            | 6                                   | COM2+ | Analog Switch 2. Common Positive Terminal.                                                                                                                                                             |  |

| 7                            | 7                                   | COM2- | Analog Switch 2. Common Negative Terminal.                                                                                                                                                             |  |

| 8, 11, 13, 19,<br>26, 28     | 5, 8, 13, 18,<br>20, 30,<br>40, 42  | V+    | Positive-Supply Voltage Input. Connect V+ to a +3.0V to +3.6V supply voltage. Bypass V+ to GND with a 0.1µF capacitor placed as close to the device as possible (See the <i>Board Layout</i> section). |  |

| 15                           | 31                                  | NO2-  | Analog Switch 2. Normally Open Negative Terminal.                                                                                                                                                      |  |

| 16                           | 32                                  | NO2+  | Analog Switch 2. Normally Open Positive Terminal.                                                                                                                                                      |  |

| 17                           | 33                                  | NO1-  | Analog Switch 1. Normally Open Negative Terminal.                                                                                                                                                      |  |

| 18                           | 34                                  | NO1+  | Analog Switch 1. Normally Open Positive Terminal.                                                                                                                                                      |  |

| 21                           | 35                                  | NC2-  | Analog Switch 2. Normally Closed Negative Terminal.                                                                                                                                                    |  |

| 22                           | 36                                  | NC2+  | Analog Switch 2. Normally Closed Positive Terminal.                                                                                                                                                    |  |

| 23                           | 37                                  | NC1-  | Analog Switch 1. Normally Closed Negative Terminal.                                                                                                                                                    |  |

| 24                           | 38                                  | NC1+  | Analog Switch 1. Normally Closed Positive Terminal.                                                                                                                                                    |  |

| _                            | 11                                  | COM3+ | Analog Switch 3. Common Positive Terminal.                                                                                                                                                             |  |

| _                            | 12                                  | COM3- | Analog Switch 3. Common Negative Terminal.                                                                                                                                                             |  |

| _                            | 15                                  | COM4+ | Analog Switch 4. Common Positive Terminal.                                                                                                                                                             |  |

| _                            | 16                                  | COM4- | Analog Switch 4. Common Negative Terminal.                                                                                                                                                             |  |

| _                            | 22                                  | NO4-  | Analog Switch 4. Normally Open Negative Terminal.                                                                                                                                                      |  |

| _                            | 23                                  | NO4+  | Analog Switch 4. Normally Open Positive Terminal.                                                                                                                                                      |  |

| _                            | 24                                  | NO3-  | Analog Switch 3. Normally Open Negative Terminal.                                                                                                                                                      |  |

| _                            | 25                                  | NO3+  | Analog Switch 3. Normally Open Positive Terminal.                                                                                                                                                      |  |

| _                            | 26                                  | NC4-  | Analog Switch 4. Normally Closed Negative Terminal.                                                                                                                                                    |  |

| _                            | 27                                  | NC4+  | Analog Switch 4. Normally Closed Positive Terminal.                                                                                                                                                    |  |

| _                            | 28                                  | NC3-  | Analog Switch 3. Normally Closed Negative Terminal.                                                                                                                                                    |  |

| _                            | 29                                  | NC3+  | 3+ Analog Switch 3. Normally Closed Positive Terminal.                                                                                                                                                 |  |

| _                            | _                                   | EP    | Exposed Paddle. Connect EP to GND.                                                                                                                                                                     |  |

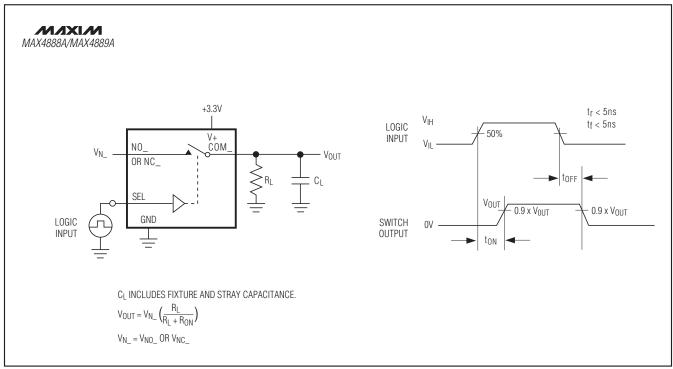

### **Test Circuits/Timing Diagrams**

Figure 1. Switching Time

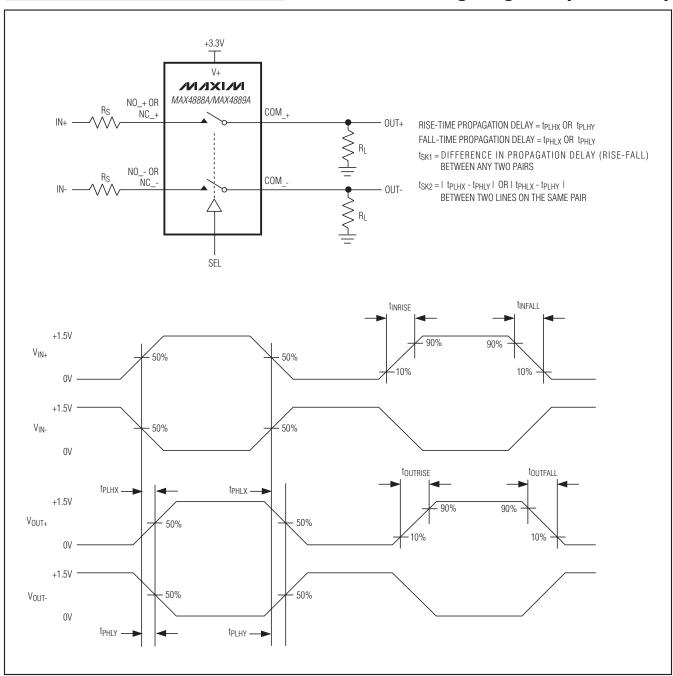

### Test Circuits/Timing Diagrams (continued)

Figure 2. Propagation Delay and Output Skew

3 \_\_\_\_\_\_*NIXI/*M

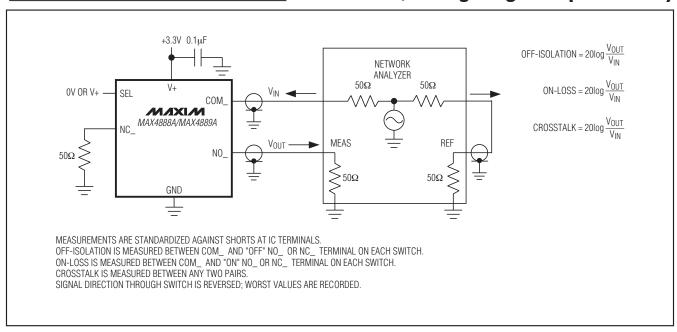

#### **Test Circuits/Timing Diagrams (continued)**

Figure 3. On-Loss, Off-Isolation, and Crosstalk

Figure 4. Channel Off-/On-Capacitance

#### **Detailed Description**

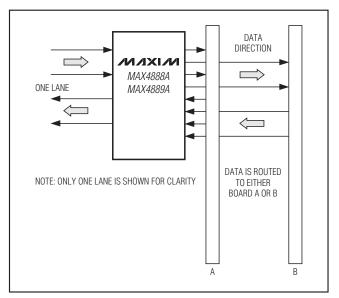

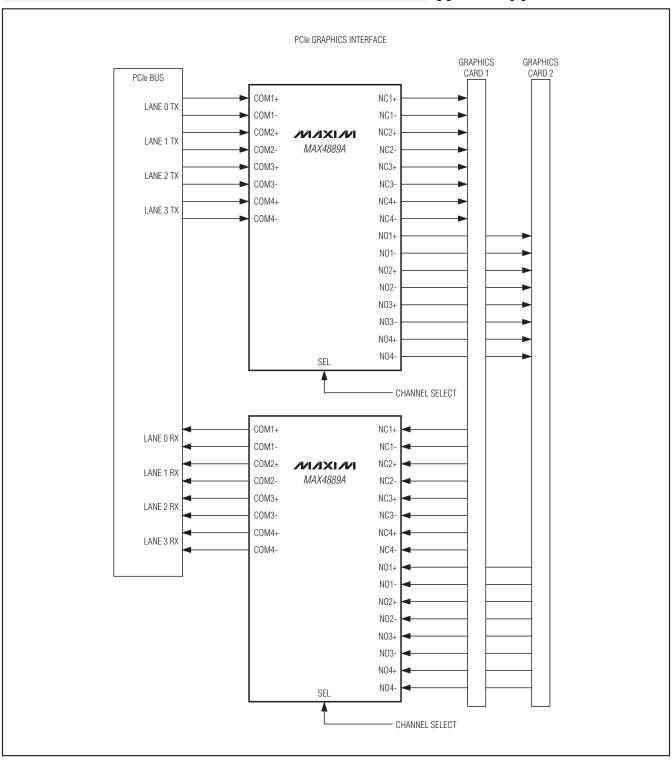

The MAX488A/MAX4889A high-speed passive switches route PCle data between two possible destinations. The MAX4888A/MAX4889A are ideal for routing PCle signals to change the system configuration. For example, in a graphics application, the MAX488A/MAX4889A create

two sets of eight lanes from a single 16-lane bus. The MAX4888A/MAX4889A feature a single digital control input (SEL) to switch signal paths.

The MAX4888A/MAX4889A are fully specified to operate from a single +3.0V to +3.6V power supply<sup>††</sup>.

#### **Digital Control Input (SEL)**

The MAX488A/MAX4889A provide a single digital control input (SEL) to select the signal path between the COM\_ and NO\_/NC\_ channels. The truth tables for the MAX4888A/MAX4889A are depicted in the Functional Diagrams/Truth Table section. Drive SEL rail-to-rail to minimize power consumption.

#### **Analog Signal Levels**

The MAX4888A/MAX4889A accept standard PCIe signals to a maximum of V+ - 1.2V. Signals on the COM\_+ channels are routed to either the NO\_+ or NC\_+ channels, and signals on the COM\_- channels are routed to either the NO\_- or NC\_- channels. The MAX4888A/MAX4889A are bidirectional switches, allowing COM\_\_, NO\_\_, and NC\_\_ to be used as either inputs or outputs.

††Contact factory if operating at +2.5V or +1.8V.

#### **Functional Diagrams/Truth Table** V+ MIXIM MIXIM MAX4888A MAX4889A COM1+ COM1+ NC1+ - NC1+ COM1-NC1-COM1-NC1-N01+ N01-N01-COM2+ NC2+ COM2+ NC2+ COM2-COM2-NC2-NC2-N02+ N02-N02-SEL COM3+ - NC3+ COM3-NC3-GND N03+ N03-COM\_TO COM\_TO COM4+ NC4+ SEL NC NO COM4-- NC4-0 0FF 1 ON N04+ - NO4-SEL GND

### **Applications Information**

#### **PCIe Switching**

The MAX488A/MAX4889A primary applications are aimed at reallocating PCIe lanes (see Figure 5). For example, in graphics applications, several manufacturers have found that it is possible to improve performance by a factor of nearly two by splitting a single 16-lane PCIe bus into two 8-lane buses. Two of the more prominent examples are SLI<sup>TM</sup> (Scaled Link Interface) and CrossFire<sup>TM</sup>. The MAX4889A permits a computer motherboard to operate properly with a single 16-lane graphics card, and can later be updated to dual cards. The same motherboard can be used with dual cards where the user sets a jumper or a bit through software to switch between single- or dual-card operation. Common mode below 1V operation requirement.

#### **Board Layout**

High-speed switches require proper layout and design procedures for optimum performance. Keep design-controlled impedance PCB traces as short as possible or follow impedance layouts per the PCle specification. Ensure that power-supply bypass capacitors are placed as close to the device as possible. Multiple bypass capacitors are recommended. Connect all grounds and the exposed pad to large ground planes. Common mode below 1V operation requirement.

Figure 5. The MAX4888A/MAX4889A Used as a Single-Lane Switch

CrossFire is a trademark of ATI Technologies, Inc. SLI is a trademark of NVIDIA Corporation.

#### **ESD Protection**

As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The COM\_+ and COM\_- lines have extra protection against static electricity. Maxim's engineers have developed state-of-the-art structures to protect these pins against ESD of ±6kV without damage. The ESD structures withstand ±6kV of ESD in all states: normal operation, state output mode, and powered down.

#### **Human Body Model**

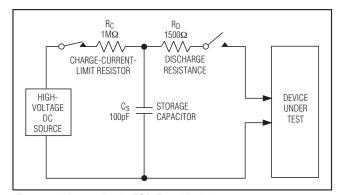

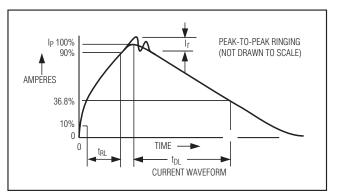

The MAX4889A COM\_+ and COM\_- pins are characterized for ±6kV ESD protection using the Human Body Model (MIL-STD-883, Method 3015). Figure 6 shows the Human Body Model and Figure 7 shows the current waveform it generates when discharged into low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a resistor.

Figure 6. Human Body ESD Test Model

Figure 7. Human Body Model Current Waveform

\_\_Chip Information

PROCESS: CMOS

### Typical Application Circuit

### Package Information

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 28 TQFN-EP   | T283555-1    | <u>21-0184</u> |

| 42 TQFN-EP   | T423590M-1   | <u>21-0181</u> |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                         | PAGES CHANGED        |  |  |

|--------------------|------------------|-------------------------------------|----------------------|--|--|

| 0                  | 4/07             | Initial release                     | _                    |  |  |

| 2                  | 5/09             | Updated voltage range, style edits. | 1, 2, 3, 5–9, 13, 14 |  |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

14 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600