#### Le79228

# Quad Intelligent Subscriber Line Audio-processing Circuit VE790 Series

#### A (Legerity Voice Solution

#### **APPLICATIONS**

- Voice over IP/DSL Integrated Access Devices (IAD), Smart Residential Gateways (SRG), Home Gateway/ Router

- Cable Telephony NIU, Set-Top Box, Home Side Box, Cable Modem, Cable PC

- Fiber Fiber in the Loop (FITL), Fiber to the Home (FTTH)

- Wireless Local Loop, Intelligent PBX

- DLC-MUX

- CO

#### **FEATURES**

- High performance digital signal processor provides programmable control of all major line card functions

- A-law/μ-law and linear codec/filter

- Transmit and receive gain

- Two-wire AC impedance

- Transhybrid balance

- Equalization

- DC loop feeding

- Smooth or abrupt polarity reversal

- Loop supervision

- Off-hook debounce circuit

- Ground-key and ring-trip filters

- Internal ringing generation and integrated ring-trip detection

- Adaptive hybrid balance

- Line and circuit testing

- Meets GR-909 and GR-844 test requirements

- Tone generation (DTMF, FSK, random noise, and arbitrary tone)

- Metering generation at 12 kHz and 16 kHz

- Envelope shaping and level control

- Modem Tone Detection

- Selectable PCM/MPI or GCI digital interfaces

- Supports most available master clock frequencies from 512 kHz to 8.192 MHz

- General purpose I/O pins

- +3.3 V DC operation

- **■** Exceeds LSSGR and ITU requirements

- Supports external ringing with on-chip ring-trip circuit

- Automatic or manual ring-trip modes

- Supports CallerNumber Identification (CID) tone generation

#### ORDERING INFORMATION

| Device       | Package <sup>1</sup> | Packing <sup>2</sup> |

|--------------|----------------------|----------------------|

| Le79Q2281DVC | 64-pin TQFP (Green)  | Tray                 |

| Le79Q2284MVC | 80-pin LQFP (Green)  | Tray                 |

- The green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

- For delivery using a tape and reel packing system, add a "T" suffix to the OPN (Ordering Part Number) when placing an order.

#### DESCRIPTION

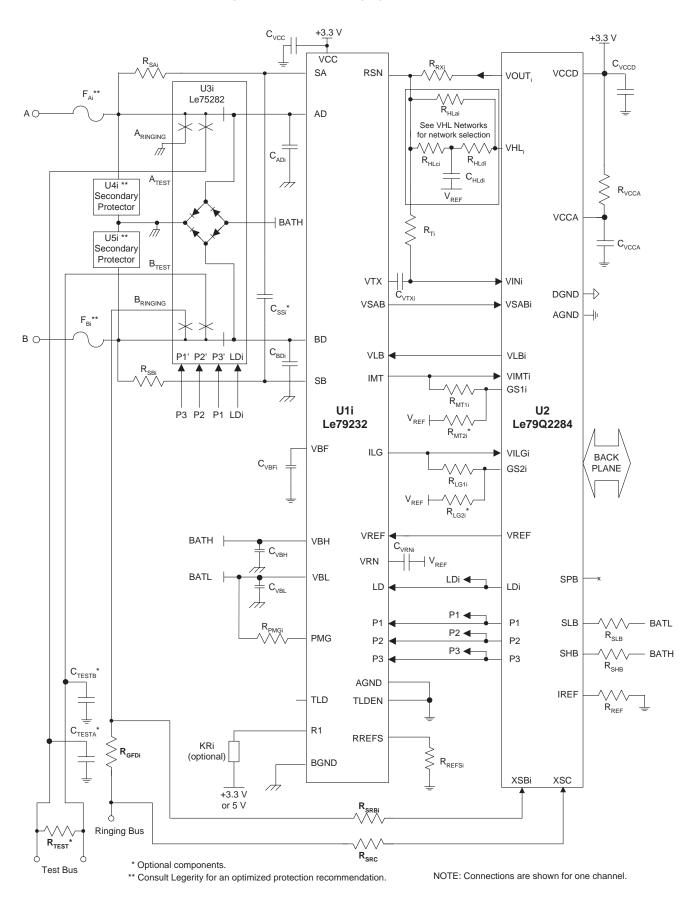

The Le79228 Quad Intelligent Subscriber Line Audio-processing Circuit (ISLAC™) device, in combination with a VE790 series ISLIC™ device, implements a four-channel universal telephone line interface. This enables the design of a single, low cost, high performance, fully software programmable line interface for multiple country applications. All AC, DC, and signaling parameters are fully programmable via microprocessor or GCI interfaces. Additionally, the Le79228 Quad ISLAC device has integrated self-test and line-test capabilities to resolve faults to the line or line circuit. The integrated test capability is crucial for remote applications where dedicated test hardware is not cost effective.

#### **RELATED LITERATURE**

- 081237 Le79232 Dual ISLIC™ Device Data Sheet

- 081152 Le79242 Dual ISLIC™ Device Data Sheet

- 081185 Le79252 Dual ISLIC™ Device Data Sheet

- 081191 Le75282 Dual LCAS Device Data Sheet

- 080923 Le792x2 Le79228 Chip Set User's Guide

- 081151 Le79112 VCP Device Data Sheet

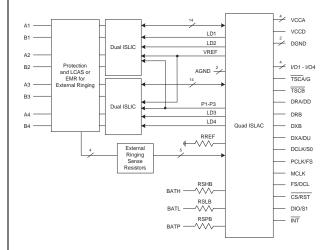

#### **BLOCK DIAGRAM**

NOTE: On August 3, 2007, Zarlink Semiconductor acquired the products and technology of Legerity Holdings.

#### **TABLE OF CONTENTS**

| Applications                                                    |    |

|-----------------------------------------------------------------|----|

| Features                                                        | 1  |

| Ordering Information                                            | 1  |

| Description                                                     | 1  |

| Related Literature                                              | 1  |

| Block Diagram                                                   | 1  |

| Product Description                                             | 3  |

| Optional VCP Features                                           |    |

| Le79228 Quad ISLAC™ Device Internal Block Diagram (80-Pin LQFP) |    |

| Features of the Le79228 Quad ISLAC™ Chip Set                    |    |

| Connection Diagrams                                             |    |

| Pin Descriptions                                                |    |

| Electrical Characteristics                                      |    |

| Absolute Maximum Ratings                                        |    |

| Operating Ranges                                                |    |

| DC Specifications                                               |    |

| Transmission Specifications                                     |    |

| Transmit and Receive Paths                                      |    |

| Attenuation Distortion                                          |    |

| Group Delay Distortion                                          |    |

| Single Frequency Distortion.                                    |    |

| Gain Linearity                                                  |    |

| Total Distortion Including Quantizing Distortion                |    |

| Overload Compression                                            |    |

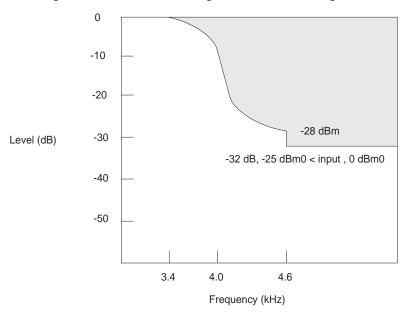

| Discrimination Against Out-of-Band Input Signals                |    |

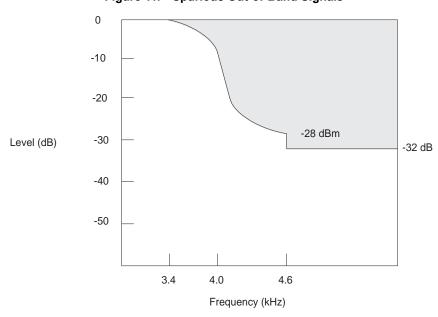

| Spurious Out-of-Band Signals at the Analog Output               |    |

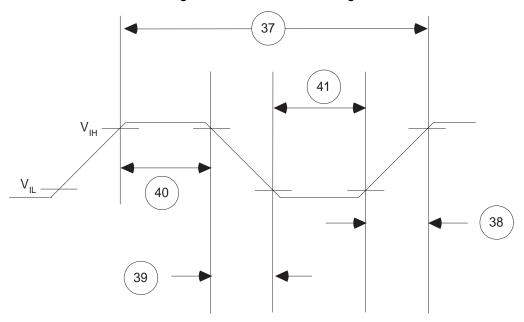

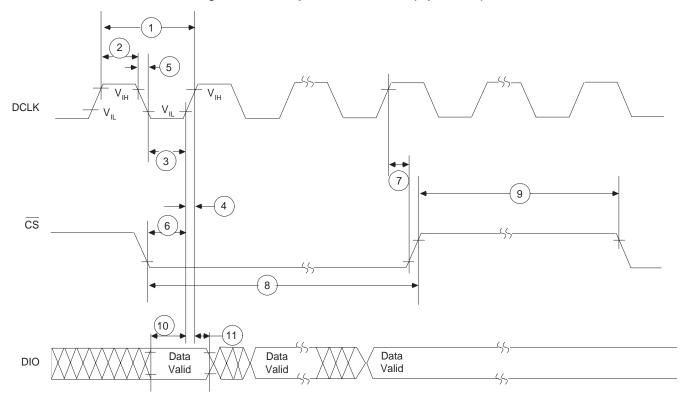

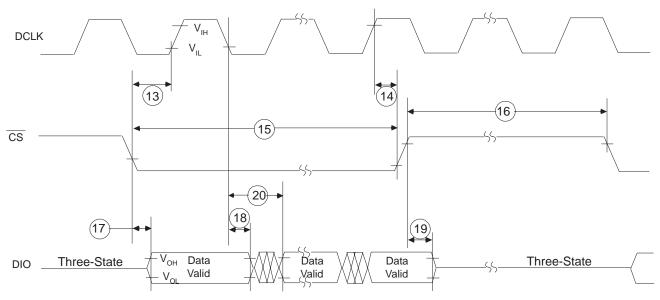

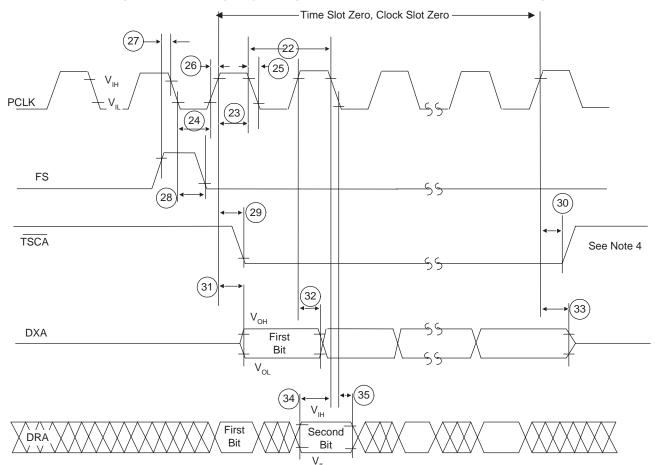

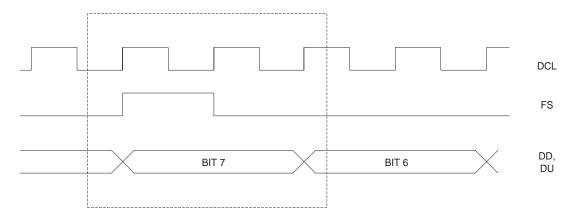

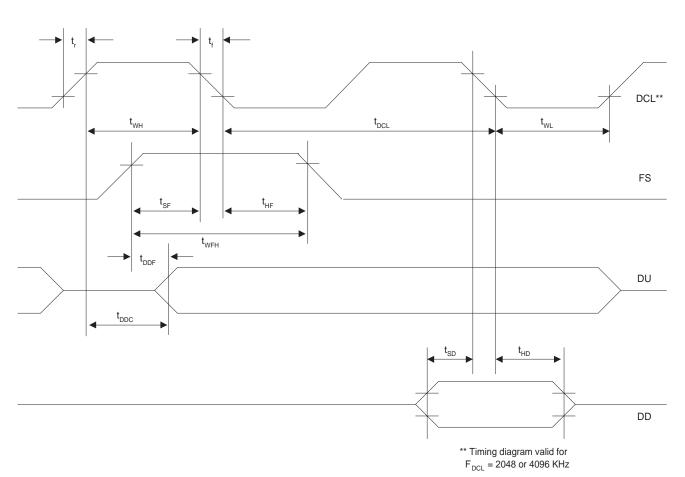

| Switching Characteristics                                       |    |

| Microprocessor Interface                                        |    |

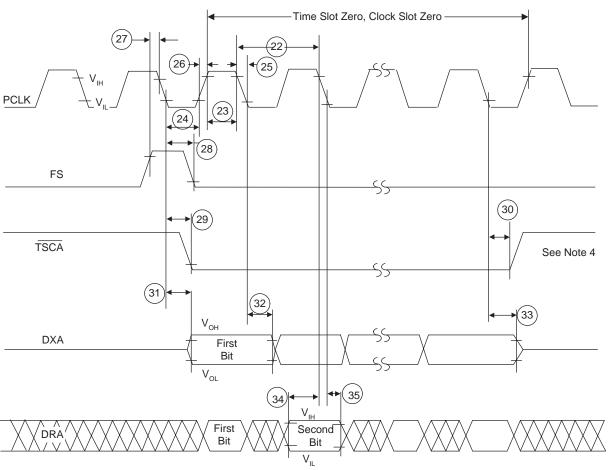

| PCM Interface                                                   |    |

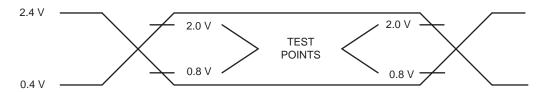

| Waveforms                                                       |    |

| GCI Timing Specifications                                       |    |

| ISLIC Device Timing Specifications                              |    |

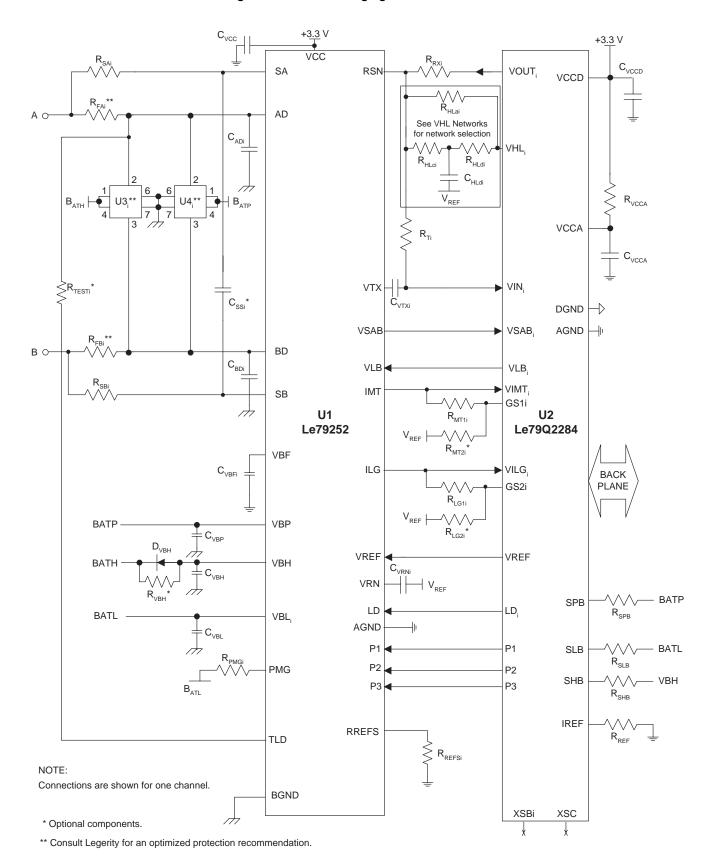

| Application Circuits                                            |    |

| Line card Parts List- INTERNAL RINGING                          |    |

| Line card Parts List - EXTERNAL RINGING                         |    |

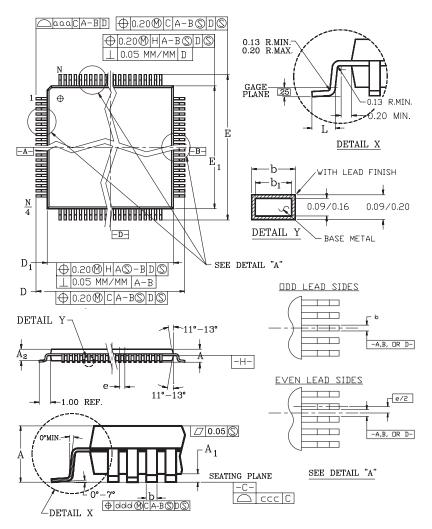

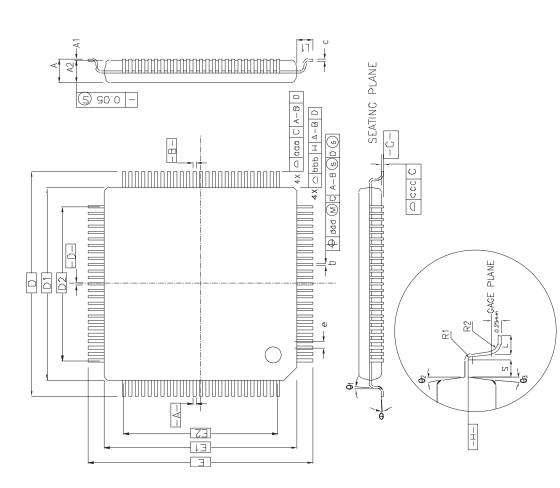

| Physical Dimensions                                             |    |

|                                                                 |    |

| 64-Pin Thin Quad Flat Pack (TQFP)                               |    |

| 80-Pin Low-Profile Quad Flat Pack (LQFP)                        |    |

| Revision History                                                |    |

|                                                                 |    |

| Revision B1 to C1                                               |    |

| Revision C1 to D1                                               |    |

| Revision D1 to E1                                               |    |

| Revision E1 to F1                                               |    |

| Revision F1 to G1                                               |    |

| Revision G1 to G2                                               | 37 |

#### PRODUCT DESCRIPTION

The VE790 series voice chip sets integrate all functions of the subscriber line for four subscriber lines. One or more of two chip types are used to implement the line card; a VE790 series ISLIC device and a Le79228 Quad ISLAC device. These provide the following basic functions:

- 1. The VE790 series ISLIC device: A high voltage, bipolar IC that drives the subscriber line, maintains longitudinal balance and senses line conditions.

- 2. The Le79228 Quad ISLAC device: A low voltage CMOS IC that provides conversion and DSP functions for all four channels. Complete schematics of line cards using the Le79228 Quad ISLAC device for internal and external ringing are shown in *Application Circuits*, on page 28.

The VE790 series ISLIC device uses reliable, bipolar technology to provide the power necessary to drive a wide variety of subscriber lines. It can be programmed by the Quad ISLAC device to operate in eight different modes that control power consumption and signaling. This enables it to have full control over the subscriber loop. The VE790 series ISLIC device is designed to be used exclusively with the Le79228 Quad ISLAC device as part of a multiple-line chip set.

The VE790 series ISLIC device implements a linear loop-current feeding method with the enhancement of intelligent thermal management in a controlled manner. This limits the amount of power dissipated on the VE790 series ISLIC chip by dissipating excess power in external resistors.

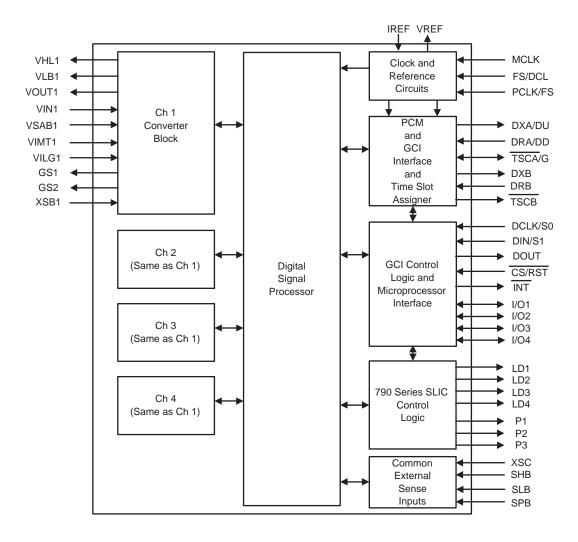

Each Le79228 Quad ISLAC device contains high-performance analog circuits that provide A/D and D/A conversion for voice (codec/filter), DC-feed and supervision signals for four subscriber channels. The Le79228 Quad ISLAC device contains a DSP core that handles signaling, DC-feed, supervision and line diagnostics for all four channels.

The DSP core selectively interfaces with three types of backplanes:

- Standard PCM/MPI

- Standard GCI

- Modified GCI with a single analog line per GCI channel

The Le79228 Quad ISLAC device provides a complete software configurable solution to the BORSCHT functions as well as complete programmable control over subscriber line DC-feed characteristics, such as current limit and feed resistance. In addition, these chip sets provide system level solutions for the loop supervisory functions and metering. In total, they provide a programmable solution that can satisfy worldwide line card requirements by software configuration.

Software programmed filter coefficients, DC-feed data and supervision data are easily calculated with the WinSLAC™ software. This PC software is provided free of charge and allows the designer to enter a description of system requirements. WinSLAC then computes the necessary coefficients and plots the predicted system results.

The VE790 series ISLIC device interface unit inside the Le79228 Quad ISLAC device processes information regarding the line voltages, loop currents and battery voltage levels. These inputs allow the Le79228 Quad ISLAC device to place several key VE790 series ISLIC device performance parameters under software control.

The main functions that can be observed and/or controlled through the Le79228 Quad ISLAC device backplane interface are:

- · DC-feed characteristics

- Ground-key detection

- · Off-hook detection

- Metering signal

- · Longitudinal operating point

- Subscriber line voltage and currents

- Ring-trip detection

- Abrupt and smooth reversal

- Subscriber line matching

- Ringing generation

- Sophisticated line and circuit tests

To accomplish these functions, the VE790 series ISLIC device collects the following information and feeds it, in analog form, to the Le79228 Quad ISLAC device:

- The metallic (IMT) and longitudinal (ILG) loop currents

- The AC (VTX) and DC (VSAB) loop voltages

The outputs supplied by the Le79228 Quad ISLAC device to the VE790 series ISLIC device are then:

- A voltage (VHL<sub>i</sub>\*) that provides control for the following high-level VE790 series ISLIC device outputs:

- DC loop current

Le79228 Data Sheet

- Internal ringing signal

- 12- or 16-kHz metering signal

- A low-level voltage proportional to the voice signal (VOUT<sub>i</sub>)

- A voltage that controls longitudinal offset for test purposes (VLB<sub>i</sub>)

The Le79228 Quad ISLAC device performs the codec and filter functions associated with the four-wire section of the subscriber line circuitry in a digital switch. These functions involve converting an analog voice signal into digital PCM samples and converting digital PCM samples back into an analog signal. During conversion, digital filters are used to band-limit the voice signals.

The user-programmable filters set the receive and transmit gain, perform the transhybrid balancing function, permit adjustment of the two-wire termination impedance and provide frequency attenuation adjustment (equalization) of the receive and transmit paths. Transhybrid balancing is also included. All programmable digital filter coefficients can be calculated using WinSLAC<sup>TM</sup> software. The PCM codes can be either 16-bit linear two's-complement or 8-bit companded A-law or  $\mu$ -law.

Besides the codec/filter functions, the Le79228 Quad ISLAC device provides all the sensing, feedback, and clocking necessary to completely control VE790 series ISLIC device functions with programmable parameters. System-level parameters under programmable control include active loop current limits, feed resistance, and feed mode voltages.

The Le79228 Quad ISLAC device supplies complete mode control to the VE790 series ISLIC device using the control bus and (P1-P3) tri-level load signal (LD<sub>i</sub>).

The Le79228 Quad ISLAC device provides extensive loop supervision capability including off-hook, ring-trip and ground-key detection. Detection thresholds for these functions are programmable. A programmable debounce timer is available that eliminates false detection due to contact bounce.

For subscriber line diagnostics, AC and DC line conditions can be monitored using built in test tools. Measured parameters can be compared to programmed threshold levels to set a pass/fail bit. The user can choose to send the actual PCM measurement data directly to a higher level processor by way of the voice channel. Both longitudinal and metallic resistance and capacitance can be measured, which allows leakage resistance, line capacitance, and telephones to be identified.

#### \*Note:

"i" denotes channel number

#### **OPTIONAL VCP FEATURES**

Optional Voice Control Processor (VCP) features provide the following solutions to the VE790 series intelligent chip sets:

- · Integrated test software routines

- DTMF detection

- Aggregated codec/filter control

#### Le79228 Quad ISLAC™ Device Internal Block Diagram (80-Pin LQFP)

#### Features of the Le79228 Quad ISLAC™ Chip Set

- Performs all battery feed, ringing, signaling, hybrid and test (BORSCHT) functions

- Two chip solution supports high density, multi-channel architecture

- Single hardware design meets multiple country requirements through software programming of:

- Ringing waveform and frequency (for balanced ringing)

- DC loop-feed characteristics and current-limit

- Loop-supervision detection thresholds

- -Off-hook debounce circuit

- -Ground-key and ring-trip filters

- Off-hook detect de-bounce interval

- Two-wire AC impedance

- Transhybrid balance impedance

- Transmit and receive gains

- Equalization

- Digital I/O pins

- A-law/μ-law and linear selection

- Supports internal and external battery-backed or earthbacked ringing

- Self-contained ringing generation and control

- Supports external ringing generator and ring relay

- Ring relay operation synchronized to zero crossings of ringing voltage and current

- Integrated ring-trip filter and software enabled manual or automatic ring-trip mode

- · Supports metering generation with envelope shaping

- · Smooth or abrupt polarity reversal

- Adaptive transhybrid balance

- Continuous or adapt and freeze

- · Supports both loop-start and ground-start signaling

- · Exceeds LSSGR and CCITT central office requirements

- Selectable PCM or GCI interface

- Supports most available master clock frequencies from 512 kHz to 8.192 MHz

- On-hook transmission

- · Power/service denial mode

- Line-feed characteristics independent of battery voltage

- Only 5 V, 3.3 V and battery supplies needed

- Low idle-power per line

- Linear power-feed with intelligent power-management feature

- Compatible with inexpensive protection networks;

Accommodates low-tolerance fuse resistors while maintaining longitudinal balance

- Monitors two-wire interface voltages and currents for subscriber line diagnostics

- Tone generation

- DTMF

- FSK

- Random noise

- Arbitrary tone

- · Built-in voice path test modes

- Power-cross, fault, and foreign voltage detection

- Meets GR-909 and GR-844 test requirements

- Integrated line-test features

- Leakage

- Line and ringer capacitance

- Loop resistance

- Integrated self-test features

- Echo gain, distortion, and noise

- · Small physical size

- Up to three relay drivers per VE790 series ISLIC device

- Configurable as test load switches

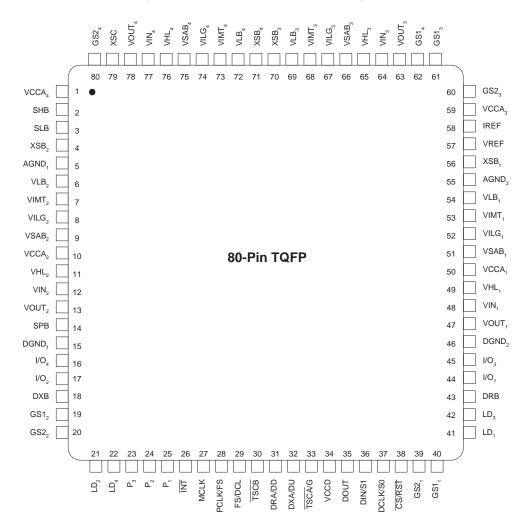

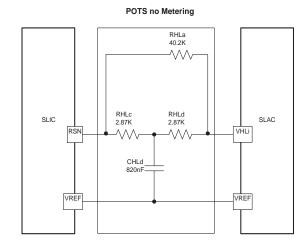

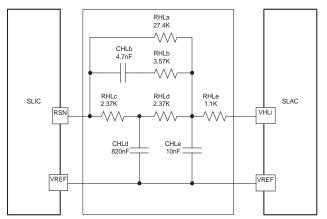

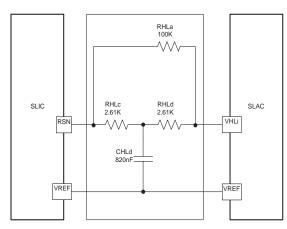

#### **CONNECTION DIAGRAMS**

Figure 1. 64-Pin TQFP Connection Diagram

Figure 2. 80-Pin LQFP Connection Diagram

#### **PIN DESCRIPTIONS**

| Pin Name                                                                           | Type             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND <sub>1</sub> ,                                                                | Ground           | Analog circuitry ground returns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AGND <sub>2</sub>                                                                  | Ground           | Arialog circulity ground returns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CS/RST                                                                             | Input            | For PCM backplane operation, a logic Low on this pin for 16 or more DCLK cycles resets the sequential logic in the Le79228 Quad ISLAC device into a known mode. A logic low placed on this pin for less than 15 DCLK cycles is a chip select and enables serial data transmission into or out of the DIO port. For GCI operation, a logic low on this pin for 1 µs or longer resets the sequential logic into a known mode. This pin is 5-V tolerant.                                                                                                                                                                                                                                                                                                                              |

| DCLK/S0                                                                            | Input            | Provides data control for MPI interface control. For GCI operation, this pin is device address bit 0. This pin is 5-V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DGND <sub>1</sub> ,<br>DGND <sub>2</sub>                                           | Ground           | Digital ground returns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DIN/S1                                                                             | Input            | For PCM backplane operation, control data is serially written into the Le79228 Quad ISLAC device via the DIN pin with the MSB first. The data clock (DCLK) determines the data rate. For GCI operation, this pin is device address bit 1. This pin is 5 V tolerant. DIN/S1 is available only on the 80-pin LQFP package.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO/S1                                                                             | Input/<br>Output | For PCM backplane operation, control data is serially written into and read out of the Le79228 Quad ISLAC device via the DIO pin with the MSB first. The data clock (DCLK) determines the data rate. DIO is high impedance except when data is being transmitted from the Le79228 Quad ISLAC device under control of CS/RST. For GCI operation, this pin is device address bit 1. This pin is 5-V tolerant. DIO/S1 is available only on the 64-pin TQFP package.                                                                                                                                                                                                                                                                                                                   |

| DOUT                                                                               | Output           | For PCM backplane operation, control data is serially read out of the Le79228 Quad ISLAC device via the DOUT pin with the MSB first. The data clock (DCLK) determines the data rate. DOUT is high impedance except when data is being transmitted from the Le79228 Quad ISLAC device under control of CS/RST. This pin is 5-V tolerant. DOUT is available only on the 80-pin LQFP package.                                                                                                                                                                                                                                                                                                                                                                                         |

| DRA/DD,<br>DRB                                                                     | Input            | For the PCM highway, the receive PCM data is input serially through the DRA or DRB pins. The data input is received every 125 µs and is shifted in, MSB first, in 8-bit PCM or 16-bit linear bursts at the PCLK rate. The receive port can receive information for direct control of the VE790 series ISLIC device. This mode is selected in Device Configuration Register 2 (RTSEN=1, RTSMD=1). When selected, this data is received in an independently programmable timeslot from the PCM data. For the GCI mode, downstream receive and control data is accepted on this pin. This pin is 5 V tolerant. The DRB pin is available only on the 80-pin LQFP package.                                                                                                              |

| DXA/DU,<br>DXB                                                                     | Output           | For the PCM highway, the transmit PCM data is transmitted serially through the DXA or DXB pins. The transmission data output is available every 125 µs and is shifted out, MSB first, in 8-bit PCM or 16-bit linear bursts at the PCLK rate. DXA and DXB are high impedance between bursts and while the device is in the inactive mode. Can also select a mode (RTSEN= 1, RTSMD=1 or 0 in Device Configuration Register 2) that transmits the Signaling Register MSB contents first, in an independently programmable timeslot from the PCM data. This data is transmitted in all modes except disconnect. For the GCI mode, upstream transmit and signaling data is transferred on this pin. This pin is 5 V tolerant. The DXB pin is available only on the 80-pin LQFP package. |

| FS/DCL                                                                             | Input            | For PCM operation, pin is Frame Sync. PCM operation is selected by the presence of an 8 kHz Frame Sync signal on this pin in conjunction with the PCLK on the PCLK/FS pin (see below). This 8 kHz pulse identifies the beginning of a frame. The Le79228 Quad ISLAC device references individual timeslots with respect to this input, which must be synchronized to PCLK. GCI operation is selected by the presence of the downstream clock DCL, on this pin in conjunction with the presence of a FS on the PCLK/FS pin. In GCI mode, the data rate is 2 MHz and DCL must be either 2 or 4 MHz. This pin is 5-V tolerant.                                                                                                                                                        |

| GS1 <sub>1</sub> -<br>GS1 <sub>4</sub> ,<br>GS2 <sub>1</sub> -<br>GS2 <sub>4</sub> | Output           | Gain select nodes for VILG and VIMT inputs. This node provides a switched tie point to VREF. The GS pins are available only on the 80-pin LQFP package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VILG <sub>1</sub> –<br>VILG <sub>4</sub>                                           | Input            | Longitudinal current input from ISLIC device. Voltage generated by RLG is sensed by this pin. Tie pin to VREF if channel unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VIMT <sub>1</sub> -                                                                | Input            | Metallic current input from ISLIC device. Voltage generated by RMT is sensed by this pin. Tie pin to VREF if channel unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ĪNT                                                                                | Output           | For PCM operation, when a subscriber line requires service, this pin goes to a logic 0 to interrupt a higher level processor. Several registers work together to control operation of the interrupt: Signaling and Global Interrupt Registers with their associated Mask Registers, and the Interrupt Register. See the description at channel configuration register 6 (Mask) for operation. Logic drive is selectable between open drain and TTL-compatible outputs.                                                                                                                                                                                                                                                                                                             |

| I/O <sub>1</sub> –I/O <sub>4</sub>                                                 | Input/<br>Output | General purpose, logic input/output connection for each of 4 channels. These control lines can be programmed as an input or output in the Global I/O Direction Register. When programmed as outputs, they can control an external logic device. When programmed as inputs, they can monitor external logic circuits. Data for these pins can be written or read individually (from the channel specific I/O Register) or as a group (from the Global I/O Data Register). The I/O pins are available only on the 80-pin LQFP package.                                                                                                                                                                                                                                               |

| IREF                                                                               | Input            | External resistor (R <sub>REF</sub> ) connected between this pin and analog ground generates an accurate, on-chip reference current for the A/D's and D/A's on the Le79228 Quad ISLAC device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Name                                 | Туре                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LD <sub>1</sub> –LD <sub>4</sub>         | Output                         | The LD pins output 3-level voltages. When LD <sub>i</sub> is a logic 0 (< 0.4 V), the destination of the code on $P_1$ – $P_3$ is the relay control latches in the VE790 series ISLIC device control register. When LD <sub>i</sub> is a logic 1 (>V <sub>CC</sub> –0.4 V), the destination of $P_1$ – $P_3$ is the mode control latches. LD <sub>i</sub> is driven to VREF when the contents of the VE790 series ISLIC device control register must not change.                                                                                                                                                                                                                                                                                 |

| MCLK                                     | Input                          | For PCM backplane operation, the DSP master clock may connect here. A signal is required only for PCM backplane operation when PCLK is not used as the master clock. MCLK can be a wide variety of frequencies, but must be synchronous to FS. Upon initialization, the MCLK input is disabled, and relevant circuitry is driven by a connection to PCLK. This pin is 5-V tolerant.                                                                                                                                                                                                                                                                                                                                                              |

| PCLK/FS                                  | Input                          | For PCM operation, this is PCM Clock. PCM operation is selected by the presence of a PCLK signal on this pin in conjunction with the FS on the FS/DCL pin (see above). For PCM backplane operation, connect a data clock, which determines the rate at which PCM data is serially shifted into or out of the PCM ports. PCLK can be any integer multiple of the FS frequency. The minimum clock frequency for linear/ companded data plus signaling data is 256 kHz. For GCI operation, this pin is Frame Sync. The FS signal is an 8 kHz pulse that identifies the beginning of a frame. The Le79228 Quad ISLAC device references individual timeslots with respect to this input, which must be synchronized to DCL. This pin is 5-V tolerant. |

| P <sub>1</sub> –P <sub>3</sub>           | Output                         | Control the operating modes of the VE790 series ISLIC devices connected to the Le79228 Quad ISLAC device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SHB,<br>SLB, SPB                         | Input                          | Resistors that sense the high, low and positive battery voltages connect here. If only one negative battery is used, connect both negative battery resistors to the same supply. If two negative batteries are used, SHB must be connected to the battery intended to supply on-hook voltage, whether BATH or BATL. If the positive battery is not used, leave the SPB pin unconnected. These pins are current inputs whose voltage is held at VREF.                                                                                                                                                                                                                                                                                             |

| TSCA/G                                   | Output<br>(PCM)<br>Input (GCI) | For PCM backplane operation, TSCA is active low when PCM data is output on the DXA or DXB pins, respectively. The outputs are open-drain and are normally inactive (high impedance). Pull-up loads should be connected to VCCD. When GCI mode is selected, one of two GCI modes may be selected by connecting TSCA/G to DGND or VCCD.                                                                                                                                                                                                                                                                                                                                                                                                            |

| TSCB                                     | Output                         | For PCM backplane operation, TSCA or TSCB is active low when PCM data is output on the DXA or DXB pins, respectively. The outputs are open-drain and are normally inactive (high impedance). Pull-up loads should be connected to VCCD. TSCB is only available on the 80 pin LQFP package. When GCI mode is selected, one of two GCI modes may be selected by connecting TSCA/G to DGND or VCCD. TSCB is available only on the 80-pin LQFP package.                                                                                                                                                                                                                                                                                              |

| VCCA <sub>1</sub> -<br>VCCA <sub>4</sub> | Supply                         | +3.3 VDC supplies to the analog sections in each of the four channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VCCD                                     | Supply                         | +3.3 VDC supply to all digital sections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VHL <sub>1</sub> –<br>VHL <sub>4</sub>   | Output                         | High-level loop control. Voltages on these pins are used to control DC-feed, internal ringing, metering and polarity reversal for each VE790 series ISLIC device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VIN <sub>1</sub> -<br>VIN <sub>4</sub>   | Input                          | Analog transmit signals (VTX) from each VE790 series ISLIC device connect to these pins. The Le79228 Quad ISLAC device converts these signals to digital words and processes them. After processing, they are multiplexed into serial time slots and sent out of the DXA/DU or DXB pin. Tie pin to VREF if channel unused.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VOUT <sub>1</sub> -<br>VOUT <sub>4</sub> | Output                         | Analog receive voltage signals are sent out of the Le79228 Quad ISLAC device from these pins. A resistor converts these signals to currents which drive the VE790 series ISLIC device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VLB <sub>1</sub> –<br>VLB <sub>4</sub>   | Output                         | Normally connected to VCCA internally. They supply longitudinal reference voltages to the VE790 series ISLIC devices during certain test procedures. These outputs are connected internally to VCCA during VE790 series ISLIC Active, Standby, Ringing, and Disconnect modes. During test modes, it can be connected to the receive D/A.                                                                                                                                                                                                                                                                                                                                                                                                         |

| VREF                                     | Output                         | This pin provides a 1.4-V, single-ended reference to the VE790 series ISLIC devices to which the Le79228 Quad ISLAC device is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VSAB <sub>1</sub> -<br>VSAB <sub>4</sub> | Input                          | Connect to the VSAB pins of four VE790 series ISLIC device channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XSB <sub>1</sub> -<br>XSB <sub>4</sub>   | Input                          | External ringing sense pin. This pin senses the current through R <sub>SRB</sub> to measure the ringing voltage on the line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XSC                                      | Input                          | External ring generator sense. This pin senses the current R <sub>SRC</sub> to measure the ringing bus voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                         | Packaç    | је Туре |

|-------------------------------------------------------------------------|-----------|---------|

| Pin Options                                                             | 80 pin    | 64 pin  |

| I/O <sub>1</sub> –I/O <sub>4</sub>                                      | $\sqrt{}$ | х       |

| DRB, DXB, TSCB                                                          | V         | х       |

| DIN/S1                                                                  | V         | х       |

| DOUT                                                                    | V         | х       |

| DIO/S1                                                                  | х         | √       |

| GS1 <sub>1</sub> -GS1 <sub>4</sub> , GS2 <sub>1</sub> -GS2 <sub>4</sub> | V         | х       |

Note: For the 80-pin LQFP package, DOUT and DIN/S1 can be connected together.

#### **ELECTRICAL CHARACTERISTICS**

#### **Absolute Maximum Ratings**

Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability.

| Storage Temperature                                  | $-60^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ |

|------------------------------------------------------|------------------------------------------------------------------------|

| Ambient Temperature, under Bias                      | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ +85°C                            |

| Ambient relative humidity (non condensing)           | 5 to 95%                                                               |

| V <sub>CCA</sub> with respect to (AGND or DGND)      | -0.4 to + 4.0 V                                                        |

| V <sub>CCD</sub> with respect to (AGND or DGND)      | -0.4 to + 4.0 V                                                        |

| V <sub>CCA</sub> with respect to V <sub>CCD</sub>    | ±0.4V                                                                  |

| VIN, VIMT, VILG, VSAB with respect to (AGND or DGND) | -0.4 to (V <sub>CCA</sub> + 0.4 V)                                     |

| 5-V tolerant pins                                    | -0.4 to (V <sub>CCD</sub> + 2.37) or 5.5 V, whichever is less          |

| AGND                                                 | DGND ± 0.4 V                                                           |

| Latch up immunity, 25°C (any pin)                    | ±100 mA                                                                |

| Latch up immunity, 85°C (pin I/O <sub>4</sub> )      | ±50 mA                                                                 |

| Latch up immunity, 85°C (all other pins)             | ±100 mA                                                                |

| Any other pin with respect to DGND                   | -0.4 V to V <sub>CC</sub>                                              |

#### **Package Assembly**

The green package devices are assembled with enhanced environmental compatible lead (Pb), halogen, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. The peak soldering temperature should not exceed 245°C during printed circuit board assembly. Refer to IPC/JEDEC J-Std-020B Table 5-2 for the recommended solder reflow temperature profile.

#### **Operating Ranges**

Legerity guarantees the performance of this device over commercial (0° to 70°C) and industrial (–40° to 85°C) temperature ranges by conducting electrical characterization over each range and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with section 4.6.2 of Bellcore TR-TSY-000357 Component Reliability Assurance Requirements for Telecommunications Equipment.

#### **Environmental Ranges**

| Ambient Temperature       | -40 to +85°C |

|---------------------------|--------------|

| Ambient Relative Humidity | 15 to 85%    |

#### **Electrical Ranges**

| Analog Supply V <sub>CCA</sub>         | +3.3 V + 5%, - 10% |

|----------------------------------------|--------------------|

| Digital Supply V <sub>CCD</sub>        | +3.3 V ± 5%        |

| DGND                                   | 0 V                |

| AGND                                   | DGND ±10 mV        |

| 5-V tolerant pins with respect to DGND | DGND to 5.25V      |

#### **DC Specifications**

| No. | Item                                                                                                                                                                                                                                                       | Condition                                           | Min                  | Тур   | Max                  | Unit | Note      |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------|-------|----------------------|------|-----------|

|     | Input Low Voltage, I/O <sub>1</sub> –I/O <sub>4</sub>                                                                                                                                                                                                      |                                                     | -0.05                | _     | 1.36 V               | V    |           |

| 1   | All other digital inputs                                                                                                                                                                                                                                   |                                                     | -0.50                |       | 0.80 V               | - V  |           |

|     | Digital input capacitance                                                                                                                                                                                                                                  |                                                     |                      |       | 4                    | pF   | <u>2.</u> |

| 2   | Input High Voltage, I/O <sub>1</sub> –I/O <sub>4</sub>                                                                                                                                                                                                     |                                                     | 2.46                 |       | V <sub>CC</sub> +0.4 | V    |           |

| 2   | All other digital inputs                                                                                                                                                                                                                                   |                                                     | 2.0                  | _     | 5.25                 | - V  |           |

|     | Input Leakage Current, I/O <sub>1</sub> –I/O <sub>4</sub>                                                                                                                                                                                                  | 0 to V <sub>CC</sub>                                | -10                  |       | +10                  |      |           |

| 3   | All other digital inputs                                                                                                                                                                                                                                   | 0 to 5.25 V                                         | -120                 | _     | +180                 | μΑ   |           |

| 4   | Input hysteresis (PCLK/FS, FS/DCL, MCLK, DIO, DRA, DRB)                                                                                                                                                                                                    |                                                     | 0.15                 | 0.225 | 0.30                 | V    | <u>2.</u> |

|     | Input hysteresis (I/O <sub>1</sub> –I/O <sub>4</sub> )                                                                                                                                                                                                     |                                                     | 0.16                 | 0.25  | 0.34                 |      |           |

|     | Ternary output voltages, LD <sub>1</sub> –LD <sub>4</sub>                                                                                                                                                                                                  |                                                     |                      |       |                      |      |           |

| 5   | High voltage                                                                                                                                                                                                                                               | lout = 1 mA                                         | V <sub>CC</sub> 4    | _     | _                    | V    |           |

| 3   | Low voltage                                                                                                                                                                                                                                                | lout = 2 mA                                         | _                    | _     | 0.4                  | _    |           |

|     | Medium voltage                                                                                                                                                                                                                                             | ±10 μA                                              | _                    | VREF  | _                    |      |           |

| 6   | Output Low Voltage (DXA/DU, DIO, I/O <sub>1</sub> -I/O <sub>4</sub> , INT, TSCA, TSCB, DXB)                                                                                                                                                                | IoI = 10mA                                          | _                    | _     | 0.4                  |      |           |

| 7   | Output Low Voltage (P <sub>1</sub> -P <sub>3</sub> )                                                                                                                                                                                                       | IoI = 5 mA                                          | _                    | _     | 0.4                  | V    |           |

| 8   | Output High Voltage (All digital outputs except INT in open drain mode and TSCA, TSCB)                                                                                                                                                                     | loh = 400 μA                                        | V <sub>CC</sub> -0.4 | _     | _                    | -    |           |

| 9   | Input Leakage Current (VIN <sub>1</sub> -VIN <sub>4</sub> , VSAB <sub>1</sub> -VSAB <sub>4</sub> , VILG <sub>1</sub> -VILG <sub>4</sub> , VIMT <sub>1</sub> -VIMT <sub>4</sub> , GS1 <sub>1</sub> -GS1 <sub>4</sub> , GS2 <sub>1</sub> -GS2 <sub>4</sub> ) |                                                     | <b>–</b> 1           | ±0.2  | 1                    | μА   |           |

|     | Full scale input voltage (VIN <sub>1</sub> –VIN <sub>4</sub> )                                                                                                                                                                                             | l                                                   |                      |       |                      |      |           |

| 10  | μ-law                                                                                                                                                                                                                                                      | 3.205 dBm0                                          |                      | VREF  |                      |      |           |

|     | A-law                                                                                                                                                                                                                                                      | 3.14 dBm0                                           | _                    | ±1.02 | _                    | V    |           |

| 11  | Input Voltage (VSAB <sub>1</sub> –VSAB <sub>4</sub> or VIMT <sub>1</sub> –VIMT <sub>4</sub> or VILG <sub>1</sub> –VILG <sub>4</sub> )                                                                                                                      | Vov–VREF  where Vov<br>is input overload<br>voltage | _                    | 1.02  | _                    |      |           |

| 12  | Offset voltage allowed on VIN <sub>1</sub> –VIN <sub>4</sub>                                                                                                                                                                                               |                                                     | -50                  | _     | +50                  |      |           |

|     | VOLIT VOLIT -#4-V-14                                                                                                                                                                                                                                       | DISN off                                            | -40                  | _     | +40                  | mV   | <u>4.</u> |

| 13  | VOUT <sub>1</sub> –VOUT <sub>4</sub> offset Voltage                                                                                                                                                                                                        | DISN on                                             | -80                  | _     | +80                  |      |           |

| 14  | VHL <sub>1</sub> –VHL <sub>4</sub> D/A absolute error                                                                                                                                                                                                      | % of D/A code                                       | -15 -2%              |       | +15 +2%              | mV   |           |

| 15  | Output voltage, VREF                                                                                                                                                                                                                                       | Load current = 0 to 10<br>mA, Source or Sink        | 1.32                 | 1.4   | 1.48                 | V    |           |

| 16  | Capacitance load on VREF and GS1 <sub>1</sub> –GS1 <sub>4</sub> , GS2 <sub>1</sub> –GS2 <sub>4</sub> or VOUT <sub>1</sub> –VOUT <sub>4</sub>                                                                                                               |                                                     | 0                    | _     | 200                  | pF   | <u>2.</u> |

| 17  | Output drive current, VOUT <sub>1</sub> -VOUT <sub>4</sub> or VLB <sub>1</sub> -VLB <sub>4</sub>                                                                                                                                                           | Source or Sink                                      | <b>–</b> 1           | _     | +1                   | mA   |           |

| 18  | Maximum output voltage, VOUT <sub>1</sub> – VOUT <sub>4</sub>                                                                                                                                                                                              | VOUT–VREF  with peak digital input                  | _                    | 1.02  | _                    |      |           |

| 19  | VLB <sub>1</sub> –VLB <sub>4</sub> operating voltage                                                                                                                                                                                                       | Source current < 250μA<br>Sink current < 25 μA.     | VREF<br>-1.02        | _     | VREF<br>+1.02        | V    | <u>8.</u> |

| 20  | Maximum output voltage on VHL                                                                                                                                                                                                                              | VHL-VREF  with peak<br>digital input, VFD = 0       | _                    | 1.02  | _                    |      |           |

| 21  | VSAB <sub>1</sub> –VSAB <sub>4</sub> , VIMT <sub>1</sub> –VIMT <sub>4</sub> ,<br>VILG <sub>1</sub> –VILG <sub>4</sub> A/D absolute error                                                                                                                   | % of input voltage                                  | -5 -2%               | _     | +5 +2%               | mV   | <u>9.</u> |

| 22  | Battery read A/D absolute error                                                                                                                                                                                                                            | % of input voltage                                  | -2 -6%               | _     | +2 +6%               | V    | <u>9.</u> |

Le79228 Data Sheet

| No. | Item                                                                                                            | Condition                                                                                                                                                          | Min         | Тур        | Max  | Unit | Note      |

|-----|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|------|------|-----------|

| 23  | Gain from VSAB <sub>1</sub> –VSAB <sub>4</sub> to VHL <sub>1</sub> –<br>VHL <sub>4</sub> (KRFB)                 | VFD = 1                                                                                                                                                            | -4.8        | <b>–</b> 5 | -5.2 | V/V  |           |

| 24  | VSAB <sub>1</sub> –VSAB <sub>4</sub> to VHL <sub>1</sub> –VHL <sub>4</sub> output offset (KRFB)                 |                                                                                                                                                                    | <b>–</b> 50 | 0          | 50   | mV   |           |

| 25  | Gain from VSAB <sub>1</sub> –VSAB <sub>4</sub> to VHL <sub>1</sub> –<br>VHL <sub>4</sub>                        | VFD = 0, hook bit feedback                                                                                                                                         | -           | -0.128     | -    | V/V  |           |

| 26  | % error of VLB <sub>1</sub> –VLB <sub>4</sub> voltage (For VLB equation, see the <i>Chip Set User's Guide</i> ) | % of input voltage                                                                                                                                                 | -5          | 0          | +5   | %    |           |

| 27  | Capacitance load on VLB <sub>1</sub> –VLB <sub>4</sub>                                                          |                                                                                                                                                                    | 0           | _          | 120  | pF   | <u>2.</u> |

| 28  | Capacitance load on XSB <sub>1</sub> –XSB <sub>4</sub> , XSC                                                    |                                                                                                                                                                    | 0           | _          | 400  |      |           |

|     | Power Dissipation                                                                                               | One channel active<br>(VE790 series ISLIC<br>state register set to<br>active); three channels<br>inactive (VE790 series<br>ISLIC state register set<br>to Standby) | _           | 183        | 235  |      |           |

| 29  |                                                                                                                 | All channels active<br>(VE790 series ISLIC<br>state register set to<br>Active)                                                                                     | _           | 264        | 340  | mW   |           |

|     |                                                                                                                 | All channels inactive<br>(VE790 series ISLIC<br>state register set to<br>Standby)                                                                                  | _           | 143        | 188  |      |           |

#### **Transmission Specifications**

Table 1. 0 dBm0 Voltage Definitions with Unity Gain in X, R, GX, GR, AX, and AR

| Signal at Digital Interface             | Transmit | Receive | Unit |

|-----------------------------------------|----------|---------|------|

| A-law digital mW or equivalent (0 dBm0) | 0.5026   | 0.5026  |      |

| μ-law digital mW or equivalent (0 dBm0) | 0.4987   | 0.4987  | Vrms |

| ±5,800 peak linear coded sine wave      | 0.5026   | 0.5025  |      |

Note: Expressed voltage levels on VOUT or input to VIN are equivalent to a digital milliwatt on the digital interface.

| No. | Item                                                     | Condition                                                                               | Min        | Тур  | Max      | Unit    | Note          |

|-----|----------------------------------------------------------|-----------------------------------------------------------------------------------------|------------|------|----------|---------|---------------|

| 1   | Insertion Loss<br>A-D, D-A                               | Input: 1014Hz, 0dBm0<br>AR = AX = GR = GX = 0 dB,<br>DISN, R, X, B and Z disabled       | -0.25      | 0    | +0.25    |         |               |

|     | A-D + D-A                                                | Temperature = 25°C                                                                      | -0.15      | 0    | +0.15    |         |               |

|     | A-D   D-A                                                | Variation over temperature                                                              | -0.1       | 0    | +0.1     | dB      | <u>3., 7.</u> |

| 2   | Level set error (Error between setting and actual value) | A-D AX + GX<br>D-A AR + GR                                                              | -0.1       | 0    | 0.1      |         | <u> </u>      |

| 3   | DR to DX gain in full digital loopback mode              | DR Input: 1014 Hz, –10 dBm0<br>AR=AX=GR=GX=0 dB, DISN,<br>R, X, B and Z filters default | -0.3       | 0    | +0.3     |         |               |

| 4   | Idle Channel Noise,                                      | A-D (PCM output)                                                                        | _          | _    | -69      | dBm0p   |               |

| 4   | Psophometric Weighted (A-law)                            | D-A (V <sub>OUT</sub> )                                                                 | _          | _    | -78      | ивтюр   | <u>5.</u>     |

| 5   | Idle Channel Noise,                                      | A-D (PCM output)                                                                        | _          | _    | +19      | dBrnC0  | <u>J.</u>     |

|     | C Message weighted (µ-law)                               | D-A (V <sub>OUT</sub> )                                                                 | _          | _    | +12      | dbilled |               |

| 6   | Coder Offset decision value, Xn                          | A-D, Input signal = 0 V                                                                 | <b>-</b> 7 | 0    | +7       | Bits    | <u>2.</u>     |

| 7   | PSRR Image frequency (VCC)<br>A-D                        | Input: 4.8 to 7.8 kHz,<br>200 mVp-p                                                     | 37         | _    | _        | dB      |               |

| 8   | PSRR Image frequency (VCC)<br>D-A                        | Measure at:<br>8000 Hz – Input frequency                                                | 37         | _    | _        | ub      | 1             |

| 9   | DISN gain accuracy                                       | Gdisn = -0.9375 to 0.9375<br>Vin = 0 dBm0                                               |            | +0.2 |          | dB      |               |

| 10  | End-to-end group delay                                   | 1014Hz; –10dBm0<br>B = Z = 0; X = R = 1                                                 | _          | _    | 525      | μS      | 2., 6.,<br>8. |

| 14  | Crosstalk TX to RX                                       | 0 dBm0 300 Hz to 3400 Hz                                                                | _          | _    | 7.5      | -ID0    |               |

| 11  | same channel RX to TX                                    | 0 dBm0 300 Hz to 3400 Hz                                                                | _          | _    | <u> </u> | dBm0    |               |

| 12  | Crosstalk TX or RX to TX                                 | 0 dBm0 1014 Hz                                                                          | _          | _    | -76      | dPm0    | <u>2.</u>     |

| 14  | other channel TX or RX to RX                             | 0 dBm0 1014 Hz                                                                          | _          | _    | -78      | dBm0    |               |

#### Notes:

- 1. Not tested or partially tested in production. This parameter is guaranteed by characterization or correlation to other tests.

- 2. Guaranteed by design.

- 3. Overall 1.014 kHz insertion loss error of the Le79228 Quad ISLAC device is guaranteed to be 0.34 dB

- 4. These voltages are referred to VREF.

- 5. When relative levels (dBm0) are used, the specification holds for any setting of (AX + GX) gain from 0 to 12 dB or (AR + GR) from 0 to -12 dB

- 6. Group delay spec valid only when Channels 1–4 occupy consecutive slots in the frame. Programming channels in non-consecutive timeslots can add up to 1 frame delay in the Group delay measurements. The Group delay specification is defined as the sum of the minimum values of the group delays for transmit and the receive paths when the B, X, R, and Z filters are disabled with null coefficients. See Figure 5, on page 16.

- 7. Requires that the calibration command (7Ch) must be performed to achieve this performance.

- 8. An additional frame of delay can be added if PCLK frequencies less than 1.536 MHz are used.

- In the absence of any error, the analog level of VREF + 1.02 V represents a digital code of 7FFFh, and the analog level of VREF 1.02 V represents a digital code of 8000h.

#### **Transmit and Receive Paths**

In this section, the transmit path is defined as the analog input to the Le79228 Quad ISLAC device  $(VIN_n)$  to the PCM voice output of the Le79228 Quad ISLAC device A-law/ $\mu$ -law speech compressor. The receive path is defined as the PCM voice input to the Le79228 Quad ISLAC device speech expander to the analog output of the Le79228 Quad ISLAC device  $(VOUT_n)$ . All limits defined in this section are tested with B = 0, Z = 0 and X = R = GR = 1.

When AR is enabled, a nominal gain of -6.02 dB is added to the analog section of the receive path.

When AX is enabled, a nominal gain of +6.02 dB is added to the analog section of the transmit path.

When relative levels (dBm0) are used in any of the following transmission characteristics, the specification holds for any setting of (AX + GX) gain from 0 to 12 dB or (AR + GR) from 0 to –12 dB.

These transmission characteristics are valid for 0 to 70° C.

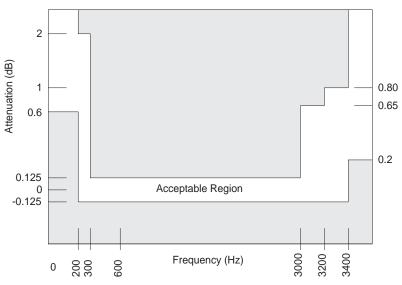

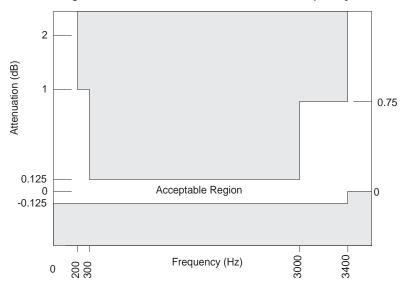

#### **Attenuation Distortion**

The attenuation of the signal in either path is nominally independent of the frequency. The deviations from nominal attenuation will stay within the limits shown in Figure 3 and Figure 4. The reference signal level is –10 dBm0. The minimum transmit attenuation at 60 Hz is 24 dB.

Figure 3. Transmit Path Attenuation vs. Frequency

Figure 4. Receive Path Attenuation vs. Frequency

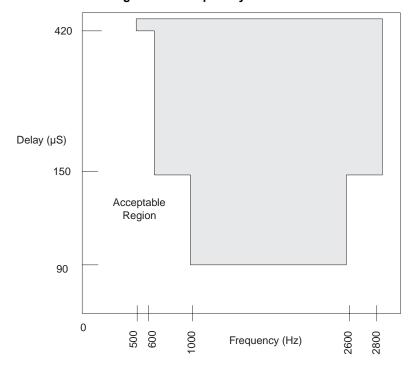

#### **Group Delay Distortion**

For either transmission path, the group delay distortion is within the limits shown in Figure 5. The minimum value of the group delay is taken as the reference. The signal level is –10 dBm0.

Figure 5. Group Delay Distortion

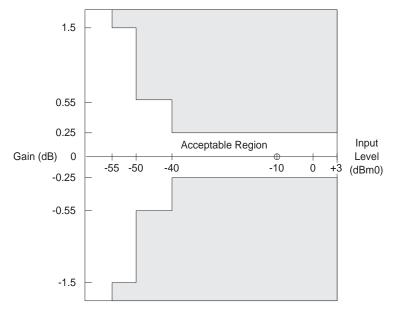

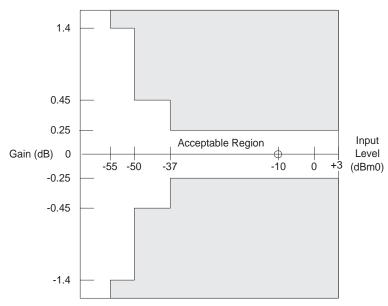

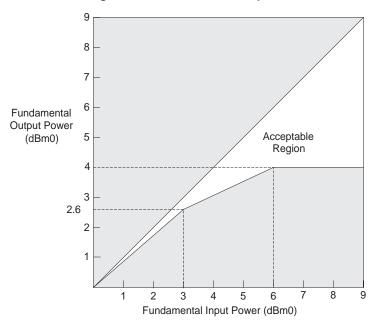

#### **Single Frequency Distortion**