# 16Mx32, 32Mx16, 64Mx8 512Mb DDR SDRAM

#### **MAY 2015**

#### **FEATURES**

- VDD and VDDQ: 2.5V ± 0.2V (-6)

- VDD and VDDQ: 2.6V ± 0.1V (-5)

- SSTL\_2 compatible I/O

- Double-data rate architecture; two data transfers per clock cycle

- Bidirectional, data strobe (DQS) is transmitted/ received with data, to be used in capturing data at the receiver

- DQS is edge-aligned with data for READs and centre-aligned with data for WRITEs

- Differential clock inputs (CK and  $\overline{CK}$ )

- DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Four internal banks for concurrent operation

- Data Mask for write data. DM masks write data at both rising and falling edges of data strobe

- Burst Length: 2, 4 and 8

- Burst Type: Sequential and Interleave mode

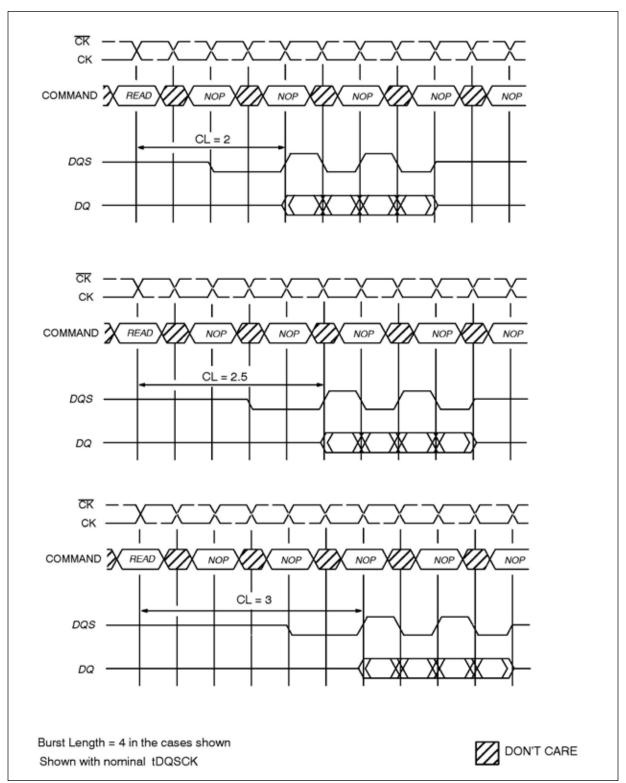

- Programmable CAS latency: 2, 2.5 and 3

- Auto Refresh and Self Refresh Modes

- Auto Precharge

- T<sub>BAS</sub> Lockout Supported (t<sub>BAP</sub> = t<sub>BCD</sub>)

#### **OPTIONS**

- Configuration(s): 16Mx32, 32Mx16, and 64Mx8

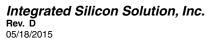

- Package(s): 144 Ball BGA (x32), 66-pin TSOP-II (x8, x16), and 60 Ball BGA (x8, x16)

- Lead-free package

- Temperature Range: Commercial (0°C to +70°C) Industrial (-40°C to +85°C) Automotive, A1 (-40°C to +85°C) Automotive, A2 (-40°C to +105°C)

#### **DEVICE OVERVIEW**

ISSI's 512-Mbit DDR SDRAM achieves high speed data transfer using pipeline architecture and two data word accesses per clock cycle. The 536,870,912-bit memory array is internally organized as four banks of 128Mb to allow concurrent operations. The pipeline allows Read and Write burst accesses to be virtually continuous, with the option to concatenate or truncate the bursts. The programmable features of burst length, burst sequence and CAS latency enable further advantages. The device is available in 8-bit, 16-bit and 32-bit data word size Input data is registered on the I/O pins on both edges of Data Strobe signal(s), while output data is referenced to both edges of Data Strobe and both edges of CLK.

An Auto Refresh mode is provided, along with a Self Refresh mode. All I/Os are SSTL\_2 compatible.

#### ADDRESS TABLE

| Parameter                           | 16M x 32               | 32M x 16               | 64M x 8                |

|-------------------------------------|------------------------|------------------------|------------------------|

| Configuration                       | 4M x 32 x 4<br>banks   | 8M x 16 x 4<br>banks   | 16M x 8 x 4<br>banks   |

| Bank Address<br>Pins                | BA0, BA1               | BA0, BA1               | BA0, BA1               |

| Autoprecharge<br>Pins               | A8/AP                  | A10/AP                 | A10/AP                 |

| Row Address                         | 8K(A0 – A12)           | 8K(A0 – A12)           | 8K(A0 – A12)           |

| Column<br>Address                   | 512(A0 – A7,<br>A9)    | 1K(A0 – A9)            | 2K(A0 – A9,<br>A11)    |

| Refresh Count<br>Com./Ind./A1<br>A2 | 8K / 64ms<br>8K / 16ms | 8K / 64ms<br>8K / 16ms | 8K / 64ms<br>8K / 16ms |

#### **KEY TIMING PARAMETERS**

| Speed Grade      | -5  | -6  | Units |

|------------------|-----|-----|-------|

| Fcк Max CL = 3   | 200 | 167 | MHz   |

| Fск Max CL = 2.5 | 167 | 167 | MHz   |

| Fcк Max CL = 2   | 133 | 133 | MHz   |

Copyright © 2015 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

Integrated Silicon Solution, Inc. Rev. D 05/18/2015

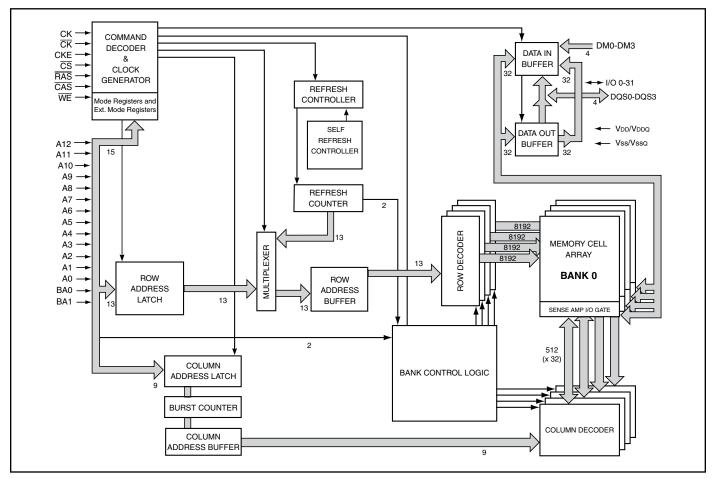

#### FUNCTIONAL BLOCK DIAGRAM (x32)

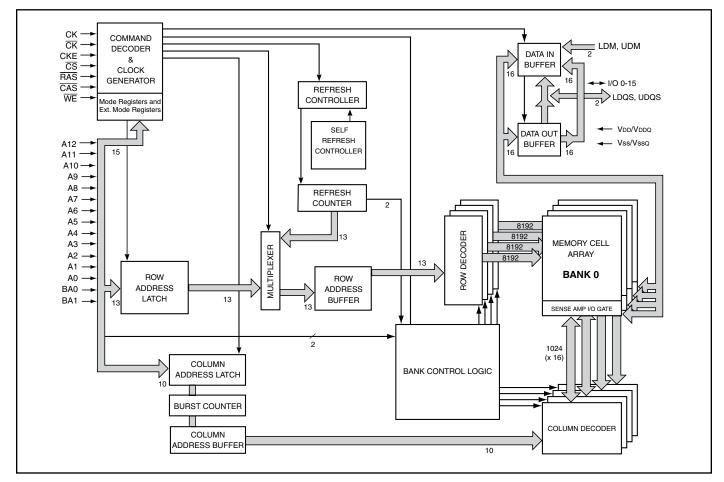

#### FUNCTIONAL BLOCK DIAGRAM (x16)

#### PIN CONFIGURATIONS 66 pin TSOP - Type II for x8

| 100 |  |

|-----|--|

|     |  |

|     |  |

| VDD I   | 1 • 66 | □ Vss   |

|---------|--------|---------|

|         |        |         |

|         |        |         |

|         |        |         |

|         |        |         |

| VssQ [[ |        |         |

|         |        |         |

|         |        |         |

| VddQ [  |        | UssQ    |

|         |        |         |

| DQ3 🔳   | 11 56  | DQ4     |

| VssQ [  |        | VDDQ    |

| NC 🎞    | 13 54  |         |

|         | 14 53  |         |

| ναα 🗌   | 15 52  | TT Vssq |

| NC 🔲    |        |         |

| NC [[   |        |         |

|         |        |         |

| NC [[   |        | T vss   |

|         |        | DM DM   |

| WE      |        |         |

|         |        | Пск     |

| RAS [   |        | ПСКЕ    |

|         |        |         |

|         |        | A12     |

| ВАО 🛄   |        | A11     |

| BA1 III |        | A9      |

| A10/AP  |        | A8      |

| A0 [[]  |        | A7      |

|         |        |         |

| A2 [[   |        | A5      |

|         |        |         |

|         | 33 34  |         |

|         |        |         |

| A0-A12            | Row Address Input                |

|-------------------|----------------------------------|

| A0-A9, A11        | Column Address Input             |

| BA0, BA1          | Bank Select Address              |

| DQ0 – DQ7         | Data I/O                         |

| CK, <del>CK</del> | System Clock Input               |

| CKE               | Clock Enable                     |

| CS                | Chip Select                      |

| CAS               | Column Address Strobe<br>Command |

| RAS               | Row Address Strobe<br>Command    |

| WE                | Write Enable                     |

| DM   | Data Write Mask           |

|------|---------------------------|

| DQS  | Data Strobe               |

| VDD  | Power                     |

| VDDQ | Power Supply for I/O Pins |

| VSS  | Ground                    |

| VSSQ | Ground for I/O Pins       |

| VREF | SSTL_2 reference voltage  |

| NC   | No Connection             |

#### **PIN CONFIGURATION**

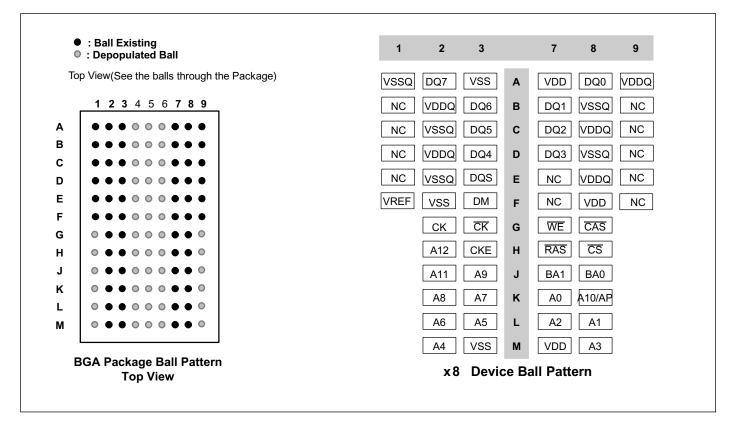

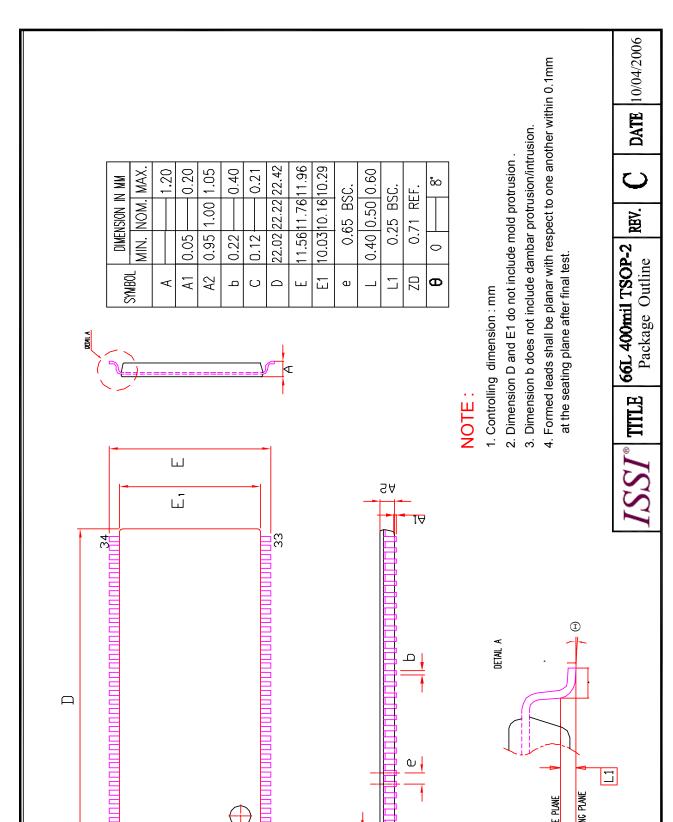

#### Package Code B: 60-ball FBGA (top view) for x8

(8mm x 13mm Body, 0.8mm Ball Pitch)

#### **Top View**

(Balls seen through the Package)

| A0-A12     | Row Address Input                |

|------------|----------------------------------|

| A0-A9, A11 | Column Address Input             |

| BA0, BA1   | Bank Select Address              |

| DQ0 – DQ7  | Data I/O                         |

| CK, CK     | System Clock Input               |

| CKE        | Clock Enable                     |

| CS         | Chip Select                      |

| CAS        | Column Address Strobe<br>Command |

| RAS        | Row Address Strobe Command       |

| WE         | Write Enable                     |

| DM         | Data Write Mask                  |

| DQS  | Data Strobe               |

|------|---------------------------|

| VDD  | Power                     |

| VDDQ | Power Supply for I/O Pins |

| VSS  | Ground                    |

| VSSQ | Ground for I/O Pins       |

| VREF | SSTL_2 reference voltage  |

| NC   | No Connection             |

#### PIN CONFIGURATIONS 66 pin TSOP - Type II for x16

|        | 1 • 66 |        |

|--------|--------|--------|

|        |        |        |

|        |        | DQ15   |

|        |        |        |

|        |        | DQ14   |

|        |        | DQ13   |

| VssQ   |        |        |

|        |        | DQ12   |

|        |        | DQ11   |

|        |        |        |

|        |        | DQ10   |

|        |        |        |

| VssQ   |        |        |

|        |        |        |

|        |        |        |

|        |        | Vssq   |

|        |        |        |

|        |        |        |

|        |        |        |

|        |        | T vss  |

|        |        |        |

|        |        |        |

|        |        | Пск    |

|        |        | ]] CKE |

|        |        |        |

|        |        | A12    |

| вао 🎞  |        | A11    |

| ВА1 🎞  |        | A9     |

| A10/AP |        | A8     |

| A0 🎞   |        | A7     |

| A1 🎞   |        | A6     |

| A2 🗖   |        | A5     |

| АЗ 🎞   |        | A4     |

| VDD [[ | 33 34  | T vss  |

| I      |        |        |

| A0-A12     | Row Address Input                |

|------------|----------------------------------|

| A0-A9      | Column Address Input             |

| BA0, BA1   | Bank Select Address              |

| DQ0 – DQ15 | Data I/O                         |

| CK, CK     | System Clock Input               |

| CKE        | Clock Enable                     |

| CS         | Chip Select                      |

| CAS        | Column Address Strobe<br>Command |

| RAS        | Row Address Strobe<br>Command    |

| WE         | Write Enable                     |

| LDM, UDM   | Data Write Mask           |

|------------|---------------------------|

| LDQS, UDQS | Data Strobe               |

| VDD        | Power                     |

| VDDQ       | Power Supply for I/O Pins |

| VSS        | Ground                    |

| VSSQ       | Ground for I/O Pins       |

| VREF       | SSTL_2 reference voltage  |

| NC         | No Connection             |

#### **PIN CONFIGURATION**

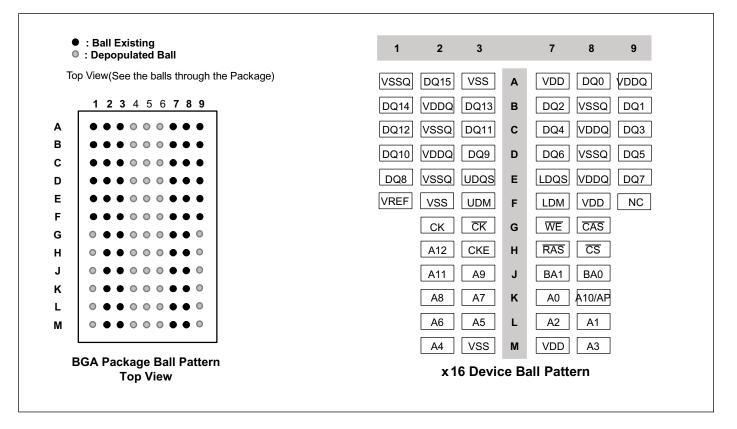

#### Package Code B: 60-ball FBGA (top view) for x16

(8mm x 13mm Body, 0.8mm Ball Pitch)

#### **Top View**

(Balls seen through the Package)

| A0-A12     | Row Address Input                |

|------------|----------------------------------|

| A0-A9      | Column Address Input             |

| BA0, BA1   | Bank Select Address              |

| DQ0 – DQ15 | Data I/O                         |

| CK, CK     | System Clock Input               |

| CKE        | Clock Enable                     |

| CS         | Chip Select                      |

| CAS        | Column Address Strobe<br>Command |

| RAS        | Row Address Strobe Command       |

| WE         | Write Enable                     |

| LDM, UDM   | Data Write Mask                  |

| LDQS, UDQS | Data Strobe               |

|------------|---------------------------|

| VDD        | Power                     |

| VDDQ       | Power Supply for I/O Pins |

| VSS        | Ground                    |

| VSSQ       | Ground for I/O Pins       |

| VREF       | SSTL_2 reference voltage  |

| NC         | No Connection             |

# **PIN CONFIGURATION**

Г

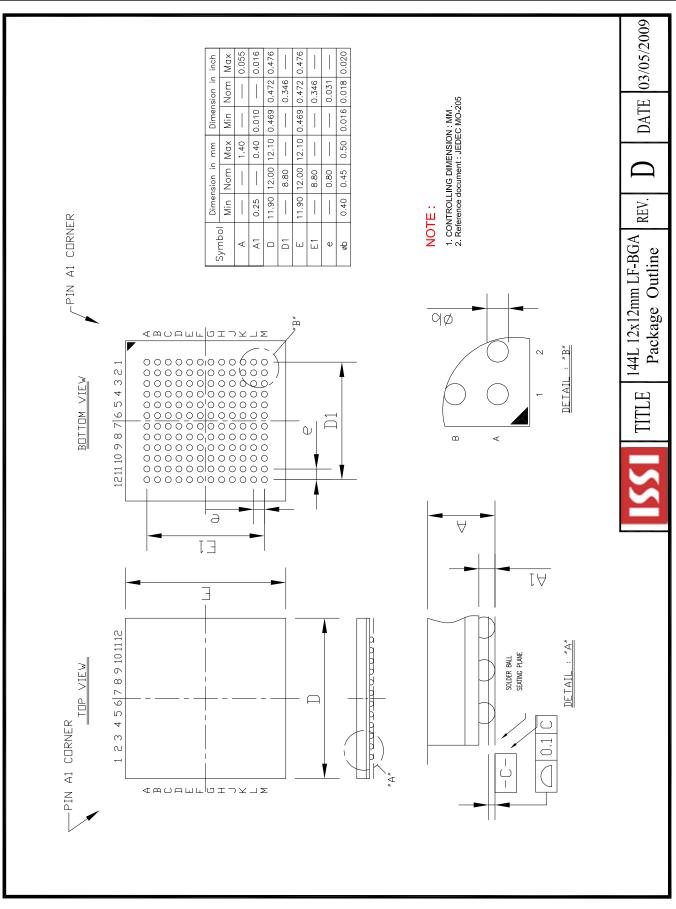

Package Code B: 144-ball FBGA (top view)

(12mm x 12mm Body, 0.8mm Ball Pitch)

Top View (Balls seen through the package)

| _ | 1          | 2          | 3          | 4          | 5                         | 6          | 7                   | 8          | 9          | 10         | 11         | 12         |

|---|------------|------------|------------|------------|---------------------------|------------|---------------------|------------|------------|------------|------------|------------|

| A |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| в |            |            | VSSQ       |            | DQ2                       |            | DQ31                | DQ29       | DQ28       | VSSQ       |            | DQS3       |

| C | DQ4        | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$                | $\bigcirc$ | $\bigcirc$          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$ |

| D |            | $\bigcirc$ | $\bigcirc$ | VSSQ       | $\bigcirc$                | $\bigcirc$ | $\bigcirc$          | $\bigcirc$ | $\bigcirc$ | VSSQ       | $\bigcirc$ | $\bigcirc$ |

| E | Ô          |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ |                     | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            | Ő          |

| F | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | VSSQ       | $\bigcirc$                | VSS        | VSS                 | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$ | $\bigcirc$ |

| G | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | VSSQ       |                           | $\bigcirc$ | VSS                 | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$ | $\bigcirc$ |

| н |            | $\bigcirc$ |            | VSSQ       | $\left  \bigcirc \right $ | VSS        | VSS                 | $\bigcirc$ |            |            | $\bigcirc$ |            |

| J | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | VSSQ       | $\bigcirc$                | $\bigcirc$ | $\bigcirc$          | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$ | $\bigcirc$ |

| K | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$                |            |                     | $\bigcirc$ | $\bigcirc$ |            | DQ9        |            |

| L |            |            |            |            | A10                       |            |                     | A12        | VSS        |            |            |            |

| Μ |            |            |            | BA1<br>A0  | $\bigcirc^{A2}_{A1}$      | A11<br>A3  | $\bigcap_{A4}^{A9}$ | A5<br>A6   | NC<br>A7   |            | Ó          |            |

Note: Vss balls inside the dotted box are optional for purposes of thermal dissipation.

#### **PIN DESCRIPTION: for x32**

| A0-A12            | Row Address Input                |

|-------------------|----------------------------------|

| A0-A7, A9         | Column Address Input             |

| BA0, BA1          | Bank Select Address              |

| DQ0 – DQ31        | Data I/O                         |

| CK, <del>CK</del> | System Clock Input               |

| CKE               | Clock Enable                     |

| CS                | Chip Select                      |

| CAS               | Column Address Strobe<br>Command |

| RAS               | Row Address Strobe<br>Command    |

| WE        | Write Enable              |

|-----------|---------------------------|

| DM0-DM3   | Data Write Mask           |

| DQS0-DQS3 | Data Strobe               |

| VDD       | Power                     |

| VDDQ      | Power Supply for I/O Pins |

| VREF      | SSTL_2 reference voltage  |

| VSS       | Ground                    |

| VSSQ      | Ground for I/O Pins       |

| NC        | No Connection             |

#### **PIN FUNCTIONAL DESCRIPTIONS**

| Symbol                                               | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, <del>CK</del>                                    | Input  | Clock: CK and CK are differential clock inputs. All address and control input signals are sampled                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      |        | on the crossing of the positive edge of CK and negative edge of CK. Input and output data is                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                      |        | referenced to the crossing of CK and $\overline{CK}$ (both directions of crossing). Internal clock signals are                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                      |        | derived from CK/ CK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CKE                                                  | Input  | Clock Enable: CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers and output drivers. Taking CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWERDOWN (row ACTIVE in any bank). CKE is synchronous for all functions except for SELF REFRESH EXIT, which is achieved asynchronously. Input buffers, excluding CK, CK and CKE, are disabled during power-down and self refresh mode which are contrived for low standby power consumption. |

| CS                                                   | Input  | Chip Select: CS enables (registered LOW) and disables (registered HIGH) the command                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                      |        | decoder. All commands are masked when CS is registered HIGH. CS provides for external bank                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                      |        | selection on systems with multiple banks. CS is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RAS, CAS,<br>WE                                      | Input  | Command Inputs: $\overline{RAS}$ , $\overline{CAS}$ and $\overline{WE}$ (along with $\overline{CS}$ ) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                          |

| DM: x8;<br>LDM, UDM:<br>x16;                         | Input  | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input-only, the DM loading matches the DQ and DQS loading.                                                                                                                                                                                                                                                   |

| DM0-DM3:<br>x32                                      |        | For x16 devices, LDM corresponds to the data on DQ0-DQ7, UDM corresponds to the data on DQ8-DQ15.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      |        | For x32 devices, DM0 corresponds to the data on DQ0-DQ7, DM1 corresponds to the data on DQ8-DQ15, DM2 corresponds to the data on DQ16-DQ23, and DM3 corresponds to the data on DQ24-DQ31.                                                                                                                                                                                                                                                                                                                                        |

| BA0, BA1                                             | Input  | Input Bank Address Inputs: BA0 and BA1 define to which bank an ACTIVE, READ, WRITE or PRECHARGE command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                        |

| A [12:0]                                             | Input  | Address Inputs: provide the row address for ACTIVE commands, and the column address and AUTO PRECHARGE bit for READ / WRITE commands, to select one location out of the memory array in the respective bank. The address inputs also provide the opcode during a MODE REGISTER SET command.                                                                                                                                                                                                                                      |

| DQ:                                                  | I/O    | Data Bus: Input / Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DQ0-DQ7: x8;<br>DQ0-DQ15:<br>x16<br>DQ0-DQ31:<br>x32 |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DQS: x8:                                             | I/O    | Data Strobe: Output with read data, input with write data. Edge-aligned with read data, centered                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LDQS, UDQS                                           |        | with write data. Used to capture write data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| x16:<br>DQS0-DQS3:                                   |        | For x16 device, LDQS corresponds to the data on DQ0-DQ7, UDQS corresponds to the data on DQ8-DQ15.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| x32                                                  |        | For x32 device, DQS0 corresponds to the data on DQ0-DQ7, DQS1 corresponds to the data on DQ8-DQ15, DQS2 corresponds to the data on DQ16-DQ23, and DQS3 corresponds to the data on DQ24-DQ31.                                                                                                                                                                                                                                                                                                                                     |

| NC                                                   |        | No Connect: Should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VREF                                                 | Supply | SSTL_2 reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDDQ                                                 | Supply | I/O Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VSSQ                                                 | Supply | I/O Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDD                                                  | Supply | Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VSS                                                  | Supply | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### **COMMANDS TRUTH TABLES**

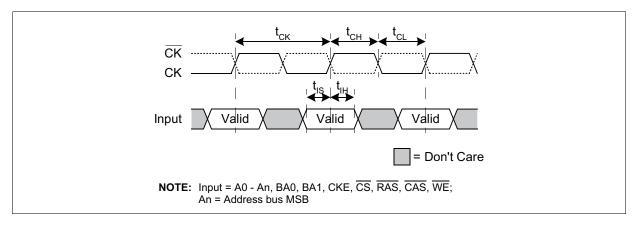

All commands (address and control signals) are registered on the positive edge of clock (crossing of CK going high and CK going low). Truth Table shows basic timing parameters for all commands.

#### TRUTH TABLE - COMMANDS

| NAME (FUNCTION)                                      | CS | RAS | CAS | WE | BA    | AP | Address | Notes |

|------------------------------------------------------|----|-----|-----|----|-------|----|---------|-------|

| DESELECT (NOP)                                       | Н  | Х   | Х   | Х  | Х     | Х  | Х       | 2     |

| NO OPERATION (NOP)                                   | L  | Н   | Н   | Н  | Х     | Х  | Х       | 2     |

| ACTIVE (select bank and activate row)                | L  | L   | Н   | Н  | Valid | Х  | Row     |       |

| READ (select bank and column and start read burst)   | L  | H   | L   | I  | Valid | L  | Column  |       |

| READ with AP (read burst with Auto Precharge)        | L  | Н   | L   | Н  | Valid | Н  | Column  | 3     |

| WRITE (select bank and column and start write burst) | L  | H   | L   | L  | Valid | L  | Column  |       |

| WRITE with AP (write burst with Auto Precharge)      | L  | H   | L   | L  | Valid | Н  | Column  | 3     |

| BURST TERMINATE                                      | L  | Н   | Н   | L  | Х     | Х  | Х       | 4     |

| PRECHARGE (deactivate row in selected bank)          | L  | L   | Н   | L  | Valid | L  | X       | 5     |

| PRECHARGE ALL (deactivate rows in all banks)         | L  | L   | Н   | L  | Х     | Н  | х       | 5     |

| AUTO REFRESH or enter SELF REFRESH                   | L  | L   | L   | Н  | Х     | Х  | Х       | 6,7,8 |

| MODE REGISTER SET                                    | L  | L   | L   | L  | Valid | Op | -code   | 9     |

Notes:

1. All states and sequences not shown are illegal or reserved.

- 2. DESELECT and NOP are functionally interchangeable.

- 3. Autoprecharge is non-persistent. AP High enables Auto Precharge, while AP Low disables Autoprecharge.

- 4. Burst Terminate applies to only Read bursts with Auto Precharge disabled. This command is undefined and should not be used for Read with Auto Precharge enabled, and for Write bursts.

- 5. If AP is Low, bank address determines which bank is to be precharged. If AP is High, all banks are precharged and BA0-BA1are don't care.

- 6. This command is AUTO REFRESH if CKE is High, and SELF REFRESH if CKE is low.

- 7. All address inputs and I/O are 'don't care' except for CKE. Internal refresh counters control bank and row addressing.

- 8. All banks must be precharged before issuing an AUTO-REFRESH or SELF REFRESH command.

- 9. BA0 and BA1 value select between MRS and EMRS.

- 10. CKE is HIGH for all commands shown except SELF REFRESH.

#### **TRUTH TABLE - DM Operations**

| FUNCTION      | DM | DQ    |

|---------------|----|-------|

| Write Enable  | L  | Valid |

| Write Inhibit | Н  | Х     |

Note: Used to mask write data, provided coincident with the corresponding data.

#### ADDRESSING

|                     | x32          | x16    | x8            |

|---------------------|--------------|--------|---------------|

| Auto Precharge (AP) | A8           | A10    | A10           |

| Row Address (RA)    | A0-A12       | A0-A12 | A0-A12        |

| Column Address (CA) | A0-A7,<br>A9 | A0-A9  | A0-A9,<br>A11 |

#### TRUTH TABLE - CKE

| CKE n-1 | CKE n | Current State  | COMMAND n        | ACTION n                   | NOTES |

|---------|-------|----------------|------------------|----------------------------|-------|

| L       | L     | Power Down     | Х                | Maintain Power Down        |       |

| L       | L     | Self Refresh   | Х                | Maintain Self Refresh      |       |

| L       | Н     | Power Down     | NOP or DESELECT  | Exit Power Down            | 6     |

| L       | Н     | Self Refresh   | NOP or DESELECT  | Exit Self Refresh          | 6, 7  |

| Н       | L     | All Banks Idle | NOP or DESELECT  | Precharge Power Down Entry | 6     |

| Н       | L     | Bank(s) Active | NOP or DESELECT  | Active Power Down Entry    | 6     |

| Н       | L     | All Banks Idle | AUTO REFRESH     | Self Refresh entry         |       |

| Н       | Н     |                | See Truth Tables | - Commands                 |       |

Notes:

1. CKEn is the logic state of CKE at clock edge n; CKEn-1 was the state of CKE at the previous clock edge.

2. Current state is the state of DDR immediately prior to clock edge n.

3. COMMANDn is the command registered at clock edge n, and ACTIONn is the result of COMMANDn.

4. All states and sequences not shown are illegal or reserved.

5. CKE must not go LOW during a Read or Write, and must stay HIGH until after tRPST or tWR, respectively.

6. DESELECT and NOP are functionally interchangeable.

7. NOPs or Deselects must be issued for at least tsNR after Self-Refresh exit before any other command. After DLL Reset, at least txSRD must elapse before any Read commands occur.

#### **Basic Timing Parameters for Commands**

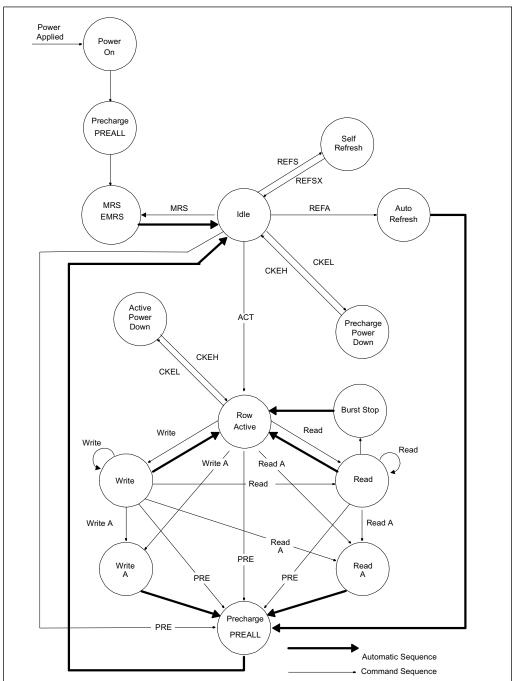

#### SIMPLIFIED STATE DIAGRAM

PREALL = Precharge All Banks CKEL = Enter Power Down MRS = Mode Register Set CKEH = Exit Power Down EMRS = Extended Mode Register Set ACT = Active REFS = Enter Self Refresh Write A = Write with Autoprecharge REFSX = Exit Self Refresh Read A = Read with Autoprecharge REFA = Auto Refresh PRE = Precharge

#### FUNCTIONAL DESCRIPTION

The DDR SDRAM is a high speed CMOS, dynamic random-access memory internally configured as a quad-bank DRAM. The 512Mb devices contains: 536,870,912 bits.

The DDR SDRAM uses double data rate architecture to achieve high speed operation. The double data rate architecture is essentially a 2n prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the DDR SDRAM effectively consists of a single 2n-bit wide, one clock cycle data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins. Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the READ or WRITE command are used to select the bank and the row to be accessed. The address bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access.

Prior to normal operation, the DDR SDRAM must be initialized. The following section provides detailed information covering device initialization, register definition, command description and device operation

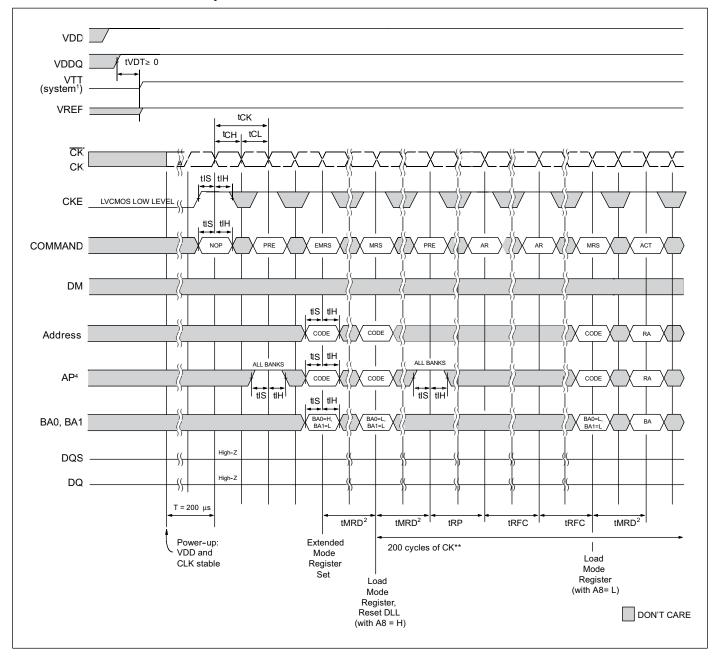

#### INITIALIZATION

DDR SDRAMs must be powered up and initialized in a predefined manner. Operations procedures other than those specified may result in undefined operation. If there is any interruption to the device power, the initialization routine should be followed. The steps to be followed for device initialization are listed below. The Initialization Flow diagram and the Initialization Flow sequence are shown in the following figures.

The Mode Register and Extended Mode Register do not have default values. If they are not programmed during the initialization sequence, it may lead to unspecified operation. The clock stop feature is not available until the device has been properly initialized from Step 1 through 13.

- Step 1: Apply VDD before or at the same time as VDDQ.

- Step 2: CKE must maintain LVCMOS Low until VREF is stable. Apply VDDQ before applying VTT and VREF.

- Step 3: There must be at least 200 µs of valid clocks before any command may be given to the DRAM. During this time NOP or DESELECT commands must be issued on the command bus and CKE should be brought HIGH.

- Step 4: Issue a PRECHARGE ALL command.

- Step 5: Provide NOPs or DESELECT commands for at least tRP time.

- Step 6: Issue EMRS command

- Step 7: Issue MRS command, load the base mode register and to reset the DLL. Set the desired operating modes.

- Step 8: Provide NOPs or DESELECT commands for at least tMRD time.

- Step 9: Issue a PRECHARGE ALL command

- Step 10: Issue 2 or more AUTO REFRESH cycles

- Step 11: Issue MRS command with the reset DLL bit deactivated to program operating parameters without resetting the DLL

- Step 12: Provide NOP or DESELECT commands for at least tMRD time.

- Step 13: The DRAM has been properly initialized and is ready for any valid command.

#### **Initialization Waveform Sequence**

Notes:

- 1. VTT is not applied directly to the device, however tVTD must be greater than or equal to zero to avoid device latch--up.

- 2. tMRD is required before any command can be applied, and 200 cycles of CK are required before any executable command can be applied

- 3. The two Auto Refresh commands may be moved to follow the first MRS but precede the second PRECHARGE ALL command.

- 4. AP is A8 for x32, and A10 for x8/x16. Address is A0 to A12 except AP.

Address Bus (Ax)

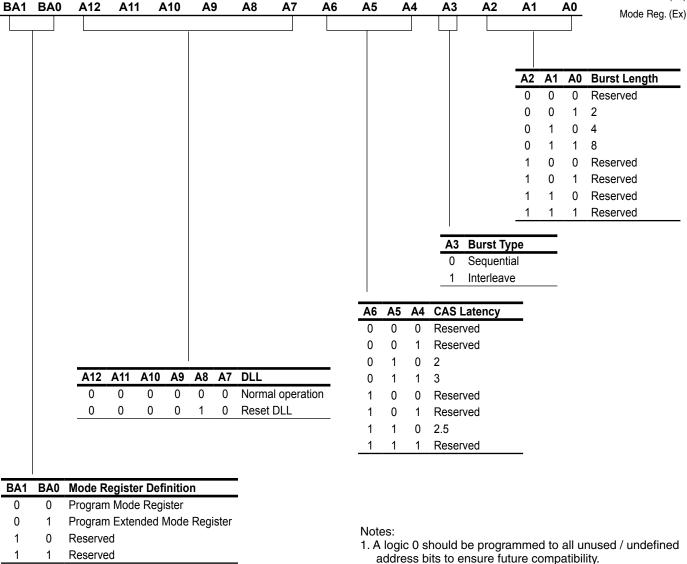

#### **MODE REGISTER (MR) DEFINITION**

The Mode Register is used to define the specific mode of operation of the DDR SDRAM. This definition includes the definition of a burst length, a burst type, and a CAS latency. The Mode Register is programmed via the MODE REGISTER SET command (with BA0=0 and BA1=0) and will retain the stored information until it is reprogrammed, or the device loses power. Mode Register bits A0-A2 specify the burst length, A3 the type of burst (sequential or interleave), A4-A6 the CAS latency, and A8 DLL reset. A logic 0 should be programmed to all the undefined addresses bits to ensure future compatibility. The Mode Register must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time tMRD before initiating any subsequent operation. Violating either of these requirements will result in unspecified operation. Reserved states should not be used, as unknown operation or incompatibility with future versions may result

# MODE REGISTER BA1 BA0 A12 A11 A10 A

#### **BURST LENGTH**

Read and write accesses to the DDR SDRAM are burst oriented, with the burst length being set and the burst order as in Burst Definition. The burst length determines the maximum number of column locations that can be accessed for a given READ or WRITE command. Burst lengths of 2, 4, or 8 locations are available for both the sequential and the interleaved burst types.

#### **BURST DEFINITION**

| Burst  | Startin | ig Column | Address | Order of Access   | es Within a Burst  |

|--------|---------|-----------|---------|-------------------|--------------------|

| Length |         |           |         | Type = Sequential | Type = Interleaved |

|        |         |           | A 0     |                   |                    |

| 2      |         |           | 0       | 0-1               | 0-1                |

|        |         |           | 1       | 1-0               | 1-0                |

|        |         | A 1       | A 0     |                   |                    |

|        |         | 0         | 0       | 0-1-2-3           | 0-1-2-3            |

| 4      |         | 0         | 1       | 1-2-3-0           | 1-0-3-2            |

|        |         | 1         | 0       | 2-3-0-1           | 2-3-0-1            |

|        |         | 1         | 1       | 3-0-1-2           | 3-2-1-0            |

|        | A 2     | A 1       | A 0     |                   |                    |

|        | 0       | 0         | 0       | 0-1-2-3-4-5-6-7   | 0-1-2-3-4-5-6-7    |

|        | 0       | 0         | 1       | 1-2-3-4-5-6-7-0   | 1-0-3-2-5-4-7-6    |

|        | 0       | 1         | 0       | 2-3-4-5-6-7-0-1   | 2-3-0-1-6-7-4-5    |

| 8      | 0       | 1         | 1       | 3-4-5-6-7-0-1-2   | 3-2-1-0-7-6-5-4    |

|        | 1       | 0         | 0       | 4-5-6-7-0-1-2-3   | 4-5-6-7-0-1-2-3    |

|        | 1       | 0         | 1       | 5-6-7-0-1-2-3-4   | 5-4-7-6-1-0-3-2    |

|        | 1       | 1         | 0       | 6-7-0-1-2-3-4-5   | 6-7-4-5-2-3-0-1    |

|        | 1       | 1         | 1       | 7-0-1-2-3-4-5-6   | 7-6-5-4-3-2-1-0    |

Notes:

1. For a burst length of two, A1-An selects the two data element block; A0 selects the first access within the block.

2. For a burst length of four, A2-An selects the four data element block; A0-A1 selects the first access within the block.

3. For a burst length of eight, A3-An selects the eight data element block; A0-A2 selects the first access within the block.

4. Whenever a boundary of the block is reached within a given sequence, the following access wraps within the block.

When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within the block, meaning that the burst will wrap within the block if a boundary is reached.

The block is uniquely selected by A1-An when the burst length is set to two, by A2-An when the burst length is set to 4, by A3-An when the burst length is set to 8. An is the most significant column address bit, which depends if the device is x8, x16 or x32. The programmed burst length applies to both read and write bursts.

#### **BURST TYPE**

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the burst type and is selected via bit A3.

The ordering of accesses within a burst is determined by the burst length, the burst type and the starting column address.

#### **READ LATENCY**

The READ latency, or CAS latency, is the delay between the registration of a READ command and the availability of the first piece of output data.

If a READ command is registered at a clock edge n and the latency is 3 clocks, the first data element will be valid at n + 2tCK + tAC. If a READ command is registered at a clock edge n and the latency is 2 clocks, the first data element will be valid at n + tCK + tAC.

#### **OPERATING MODE**

The normal operating mode is selected by issuing a Mode Register Set command with bits A7 to A12 each set to zero, and bits A0 to A6 set to the desired values. A DLL reset is initiated by issuing a Mode Register Set command with bits A7 and A9 to A12 each set to zero, bit A8 set to one, and bits A0 to A6 set to the desired values. A Mode Register Set command issued to reset the DLL must always be followed by a Mode Register Set command to select normal operating mode (A8=0).

All other combinations of values for A7 to A12 are reserved for future use and/or test modes. Test modes and reserved states should not be used because unknown operation or incompatibility with future versions may result.

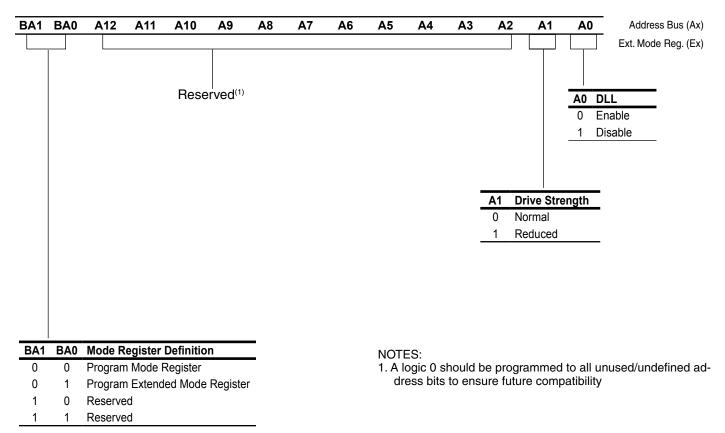

#### **EXTENDED MODE REGISTER (EMR) DEFINITION**

The Extended Mode Register controls functions beyond those controlled by the Mode Register; these additional functions include DLL enable/disable, and output drive strength selection. The Extended Mode Register is programmed via the MODE REGISTER SET command (with BA1=0 and BA0=1) and will retain the stored information until it is reprogrammed, or the device loses power. The Extended Mode Register must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time tMRD before initiating any subsequent operation. Violating either of these requirements will result in unspecified operation. Reserved states should not be used, as unknown operation or incompatibility with future versions may result.

#### **DLL Enable/Disable**

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization, and upon returning to normal operation after having disabled the DLL for the purpose of debug or evaluation (upon exiting Self Refresh Mode, the DLL is enabled automatically). Any time the DLL is enabled a DLL Reset must follow and 200 clock cycles must occur before any executable command can be issued.

#### **OUTPUT DRIVE STRENGTH (DS)**

The normal drive strength for all outputs is specified to be SSTL\_2, Class II. This DRAM also supports a reduced driver strength option, intended for lighter load and/or point-to-point environments.

#### **EXTENDED MODE REGISTER**

Integrated Silicon Solution, Inc. Rev. D 05/18/2015

#### Absolute Maximum Rating

| Parameter                                    | Symbol    | Value      | Unit |

|----------------------------------------------|-----------|------------|------|

| Voltage on any pin relative to VSS           | Vin, Vout | -1.0 ~ 3.6 | V    |

| Voltage on VDD & VDDQ supply relative to VSS | Vdd, Vddq | -1.0 ~ 3.6 | V    |

| Storage temperature                          | Тѕтс      | -55 ~ +150 | °C   |

| Power dissipation                            | PD        | 1.5        | W    |

| Short circuit current                        | los       | 50         | mA   |

Note:

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommend operation condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability

#### AC/DC Electrical Characteristics and Operating Conditions

Recommended operating conditions (Voltage referenced to VSS=0V; TA=0 to 70°C for Commercial, TA = -40°C to +85°C for Industrial and A1, TA = -40°C to +105°C for A2)

| Parameter                                                         | Symbol    | Min       | Мах       | Unit | Note |

|-------------------------------------------------------------------|-----------|-----------|-----------|------|------|

| Supply voltage (with a nominal VDD of 2.5V for -6)                | Vdd       | 2.3       | 2.7       | V    |      |

| Supply voltage (with a nominal VDD of 2.6V for -4, -5)            | Vdd       | 2.5       | 2.7       | V    |      |

| I/O Supply voltage (with a nominal VDD of 2.5V for -6)            | Vddq      | 2.3       | 2.7       | V    |      |

| I/O Supply voltage (with a nominal VDD of 2.6V for -4, -5)        | Vddq      | 2.5       | 2.7       | V    |      |

| I/O Reference voltage                                             | VREF      | 0.49*VDDQ | 0.51*VDDQ | V    | 1    |

| I/O Termination voltage (system)                                  | Vtt       | VREF-0.04 | VREF+0.04 | V    | 2    |

| Input logic high voltage                                          | Vih(dc)   | VREF+0.15 | VDDQ+0.3  | V    |      |

| Input logic low voltage                                           | VIL(DC)   | -0.3      | VREF-0.15 | V    |      |

| Input Voltage Level, CLK and CLK inputs                           | Vin(dc)   | -0.3      | VDDQ+0.3  | V    |      |

| Input Differential Voltage, CLK and CLK inputs                    | Vid(dc)   | 0.36      | VDDQ+0.6  | V    | 3    |

| V-I Matching: Pullup to Pulldown Current Ratio                    | Vı(Ratio) | 0.71      | 1.4       | -    | 4    |

| Input leakage current                                             | ١L        | -2        | 2         | uA   |      |

| Output leakage current                                            | loz       | -5        | 5         | uA   |      |

| Output High Current (Normal strength driver) ; VOUT = VTT + 0.84V | Іон       | -16.8     | _         | mA   |      |

| Output Low Current (Normal strength driver) ; VOUT = VTT - 0.84V  | lol       | 16.8      | _         | mA   |      |

| Output High Current (Half strength driver); VOUT = VTT + 0.45V    | Іонг      | -9        | _         | mA   |      |

| Output Low Current (Half strength driver); VOUT = VTT - 0.45V     | Iolr      | 9         | _         | mA   |      |

| Ambient Operating Temperature                                     |           |           |           |      |      |

| Commercial                                                        | Ta        | 0         | +70       | °C   |      |

| Industrial                                                        | TA        | -40       | +85       | °C   |      |

| A1                                                                | TA        | -40       | +85       | °C   |      |

| A2                                                                | TA        | -40       | +105      | °C   |      |

Note :

1. VREF is expected to be equal to 0.5\*VDDQ of the transmitting device, and to track variations in the dc level of same. Peak-to peak noise on VREF may not exceed +/-2% of the dc value.

2. VTT is not applied directly to the device. VTT is a system supply for signal termination resistors, is expected to be set equal to VREF, and must track variations in the DC level of VREF

3. VID is the magnitude of the difference between the input level on CLK and the input level on CLK.

4. The ratio of the pullup current to the pulldown current is specified for the same temperature and voltage, over the entire temperature and voltage range, for device drain to source voltages from 0.25V to 1.0V. For a given output, it represents the maximum difference between pullup and pulldown drivers due to process variation. The full variation in the ratio of the maximum to minimum pullup and pulldown current will not exceed 1.7 for device drain to source voltages from 0.1 to 1.0.

#### CAPACITANCE CHARACTERISTICS<sup>(1)</sup>

$(V_{DD} = V_{DDQ} = 2.5V + 0.2V (-6), V_{DD} = V_{DDQ} = 2.6V + 0.1V (-5), V_{SS} = V_{SSQ} = 0V, unless otherwise noted)$

| Symbol | Parameter                         | Test Condition | Limits |     | Units |

|--------|-----------------------------------|----------------|--------|-----|-------|

|        |                                   |                | Min    | Max |       |

| CI(A)  | Input Capacitance, address pin    | VI=1.25v       | 1.3    | 3   | pF    |

| CI(C)  | Input Capacitance, control pin    | f=100MHz       | 1.3    | 3   | pF    |

| CI(K)  | Input Capacitance, CLK pin        | VI=25mVrms     | 1.3    | 3   | pF    |

| CI/O   | I/O Capacitance, I/O, DQS, DM pin |                | 3      | 5   | pF    |

Note:

1. This parameter is characterized.

#### THERMAL RESISTANCE

| Package   | Substrate | Theta-ja<br>(Airflow = 0m/s) | Theta-ja<br>(Airflow = 1m/s) | Theta-ja<br>(Airflow = 2m/s) | Theta-jc | Units |

|-----------|-----------|------------------------------|------------------------------|------------------------------|----------|-------|

| TSOP2(66) | 4-layer   | 52.5                         | 49.9                         | 46.9                         | 7.7      | C/W   |

| BGA(60)   | 4-layer   | 32.3                         | 29.1                         | 26.9                         | 5.5      | C/W   |

| BGA(144)  | 4-layer   | 28.1                         | 23.4                         | 20.7                         | 3.4      | C/W   |

#### IDD Specification Parameters and Test Conditions: x8, x16

$(V_{DD} = V_{DDQ} = 2.5V \pm 0.2V (-6), V_{DD} = V_{DDQ} = 2.6V \pm 0.1V (-5), V_{SS} = V_{SSQ} = 0V, Output Open, unless otherwise noted)$

| Symbol | Parameter/Test Condition                                                                                                                                                                                                                                                       | -5  | -6  | Units |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| IDD0   | Operating current for one bank active-precharge; tRC = tRC(min);<br>tCK = tCK(min); DQ, DM and DQS inputs changing once per clock<br>cycle; address and control inputs changing once every two clock<br>cycles; CS = high between valid commands                               |     | 130 | mA    |

| IDD1   | Operating current for one bank operation; one bank open; BL = 4;<br>tRC = tRC(min); tCK = tCK(min); lout=0mA; Address and control<br>inputs changing once per clock cycle;                                                                                                     | 155 | 140 | mA    |

| IDD2P  | Precharge power-down standby current; all banks idle; power-down mode; CKE VIL(max); tCK = tCK(min); VIN = VREF for DQ, DQS and DM                                                                                                                                             | 30  | 30  | mA    |

| IDD2F  | Precharge floating standby current; CS VIH(min); all banks idle; CKE VIH(min); tCK = tCK(min); address and other control inputs changing once per clock cycle; VIN = VREF for DQ, DQS and DM                                                                                   | 65  | 65  | mA    |

| IDD3P  | Active power-down standby current; one bank active; power-down mode; CKE VIL(max); tCK = tCK(min); VIN = VREF for DQ, DQS and DM                                                                                                                                               | 35  | 35  | mA    |

| IDD3N  | Active standby current; CS VIH(min); CKE VIH(min); one bank<br>active; tRC = tRAS(max); tCK = tCK(min); DQ, DQS and DM inputs<br>changing twice per clock cycle; address and other control inputs<br>changing once per clock cycle                                             | 85  | 85  | mA    |

| IDD4R  | Operating current for burst read; burst length = 2; reads; continuous<br>burst; one bank active; address and control inputs changing once per<br>clock cycle; tCK = tCK(min); 50% of data changing on every transfer;<br>IOUT = 0mA                                            | 330 | 280 | mA    |

| IDD4W  | Operating current for burst write; burst length = 2; writes; continuous burst; one bank active address and control inputs changing once per clock cycle; $tCK = tCK(min)$ ; DQ, DM and DQS inputs changing twice per clock cycle, 50% of input data changing at every transfer | 340 | 290 | mA    |

| IDD5   | Auto refresh current; tRC = tRFC(min)                                                                                                                                                                                                                                          | 180 | 180 | mA    |

| IDD6   | Self refresh current; CKE 0.2V                                                                                                                                                                                                                                                 | 8   | 8   | mA    |

| IDD7   | Operating current for four bank operation; four bank interleaving<br>READs (BL=4) with auto precharge; tRC = tRC(min), tCK = tCK(min);<br>Address and control inputs change only during ACTIVE, READ, or<br>WRITE commands; 50% of data changing on every transfer             | 430 | 370 | mA    |

#### IDD Specification Parameters and Test Conditions: x32

$(V_{DD} = V_{DDQ} = 2.5V \pm 0.2V (-6), V_{DD} = V_{DDQ} = 2.6V \pm 0.1V (-5) V_{SS} = V_{SSQ} = 0V, Output Open, unless otherwise noted)$

| Symbol | Parameter/Test Condition                                                                                                                                                                                                                                                    | -5  | -6  | Units |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| IDD0   | Operating current for one bank active-precharge; $tRC = tRC(min)$ ; $tCK = tCK(min)$ ; DQ, DM and DQS inputs changing once per clock cycle; address and control inputs changing once every two clock cycles; $CS =$ high between valid commands.                            | 170 | 150 | mA    |

| IDD1   | Operating current for one bank operation; one bank open, $BL = 4$ , $tRC = tRC(min)$ , $tCK = tCK(min)$ , lout=0mA, Address and control inputs changing once per clock cycle.                                                                                               | 195 | 170 | mA    |

| IDD2P  | Precharge power-down standby current; all banks idle; power-down mode; CKE VIL(max); tCK = tCK(min); VIN = VREF for DQ, DQS and DM                                                                                                                                          | 35  | 30  | mA    |

| IDD2F  | Precharge floating standby current; CS VIH(min); all banks idle; CKE VIH(min); tCK = tCK(min); address and other control inputs changing once per clock cycle; VIN = VREF for DQ, DQS and DM                                                                                | 75  | 60  | mA    |

| IDD3P  | Active power-down standby current; one bank active; power-down mode; CKE VIL(max); tCK = tCK(min); VIN = VREF for DQ, DQS and DM                                                                                                                                            | 35  | 35  | mA    |

| IDD3N  | Active standby current; CS VIH(min); CKE VIH(min); one bank<br>active; tRC = tRAS(max); tCK = tCK(min); DQ, DQS and DM inputs<br>changing twice per clock cycle; address and other control inputs<br>changing once per clock cycle                                          | 95  | 80  | mA    |

| IDD4R  | Operating current for burst read; burst length = 2; reads; continuous<br>burst; one bank active; address and control inputs changing once per<br>clock cycle; tCK = tCK(min); 50% of data changing on every transfer;<br>IOUT = 0mA                                         | 480 | 420 | mA    |

| IDD4W  | Operating current for burst write; burst length = 2; writes; continuous burst; one bank active address and control inputs changing once per clock cycle; tCK = tCK(min); DQ, DM and DQS inputs changing twice per clock cycle, 50% of input data changing at every transfer | 490 | 430 | mA    |

| IDD5   | Auto refresh current; tRC = tRFC(min);                                                                                                                                                                                                                                      | 230 | 230 | mA    |

| IDD6   | Self refresh current; CKE 0.2V;                                                                                                                                                                                                                                             | 4   | 4   | mA    |

| IDD7   | Operating current for four bank operation; four bank interleaving<br>READs (BL=4) with auto precharge; tRC = tRC(min), tCK = tCK(min);<br>Address and control inputs change only during ACTIVE, READ, or<br>WRITE commands; 50% of data changing on every transfer          | 590 | 560 | mA    |

#### AC TIMING REQUIREMENTS

Absolute Specifications (VDD, VDDQ = +2.5V ±0.2 V@-6; VDD, VDDQ = +2.6V ±0.1 V@-5)

| PARAMETER                                               | SYMBOL   | -5               |        | -6               |         | UNITS |  |

|---------------------------------------------------------|----------|------------------|--------|------------------|---------|-------|--|

|                                                         |          | MIN              | MAX    | MIN              | MAX     |       |  |

| DQ output access time for CLK,/CLK                      | tAC      | -0.7             | 0.7    | -0.7             | 0.7     | ns    |  |

| DQS output access time for CLK,/CLK                     | tDQSCK   | -0.6             | 0.6    | -0.6             | 0.6     | ns    |  |

| CLK high-level width                                    | tCH      | 0.45             | 0.55   | 0.45             | 0.55    | tCK   |  |

| CLK low-level width                                     | tCL      | 0.45             | 0.55   | 0.45             | 0.55    | tCK   |  |

| CLK half period                                         | tHP      | min<br>(tCL,tCH) | _      | min<br>(tCL,tCH) | -       | ns    |  |

| CLK cycle time CL=3                                     | tCK(3)   | 5                | 12     | 6                | 12      | ns    |  |

| CL=2.5                                                  | tCK(2.5) | 6                | 12     | 6                | 12      | ns    |  |

| CL=2                                                    | tCK(2)   | 7.5              | 12     | 7.5              | 12      | ns    |  |

| DQ and DM input hold time                               | tDH      | 0.4              | _      | 0.45             | -       | ns    |  |

| DQ and DM input setup time                              | tDS      | 0.4              | _      | 0.45             | _       | ns    |  |

| Control & Address input pulse width (for each input)    | tIPW     | 2.2              | _      | 2.2              | -       | ns    |  |

| DQ and DM input pulse width (for each input)            | tDIPW    | 1.75             | -      | 1.75             | —       | ns    |  |

| DQ & DQS high-impedance time from CLK,/CLK              | tHZ      | -                | 0.7    | -                | 0.7     | ns    |  |

| DQ & DQS lowimpedance time from CLK,/CLK                | tLZ      | -0.7             | -      | -0.7             | —       | ns    |  |

| DQSDQ Skew, DQS to last DQ valid, per group, per access | tDQSQ    | _                | 0.4    | -                | 0.45    | ns    |  |

| DQ/DQS output hold time from DQS                        | tQH      | tHP-tQHS         | -      | tHP-<br>tQHS     | -       | ns    |  |

| Data Hold Skew Factor                                   | tQHS     | -                | 0.5    | -                | 0.55    | ns    |  |

| Write command to first DQS latching transition          | tDQSS    | 0.72             | 1.28   | 0.75             | 1.28    | tCK   |  |

| DQS input high pulse width                              | tDQSH    | 0.35             | -      | 0.35             | —       | tCK   |  |

| DQS input low pulse width                               | tDQSL    | 0.35             | -      | 0.35             | -       | tCK   |  |

| DQS falling edge to CLK setup time                      | tDSS     | 0.2              | -      | 0.2              | —       | tCK   |  |

| DQS falling edge hold time from CLK                     | tDSH     | 0.2              | -      | 0.2              | _       | tCK   |  |

| MODE REGISTER SET command cycle time                    | tMRD     | 2                | -      | 2                | _       | tCK   |  |

| Write preamble setup time                               | tWPRES   | 0                | -      | 0                | _       | ns    |  |

| Write postamble                                         | tWPST    | 0.4              | 0.6    | 0.4              | 0.6     | tCK   |  |

| Write preamble                                          | tWPRE    | 0.25             | _      | 0.25             | -       | tCK   |  |

| Address and Control input hold time (fast slew rate)    | tIHF     | 0.6              | _      | 0.75             | -       | ns    |  |

| Address and Control input setup time (fast slew rate)   | tISF     | 0.6              | -      | 0.75             | _       | ns    |  |

| Address and Control input hold time (slow slew rate)    | tIH      | 0.7              | -      | 0.8              |         | ns    |  |

| Address and Control input setup time (slow slew rate)   | tIS      | 0.7              | _      | 0.8              | -       | ns    |  |

| Read preamble                                           | tRPRE    | 0.9              | 1.1    | 0.9              | 1.1     | tCK   |  |

| Read postamble                                          | tRPST    | 0.4              | 0.6    | 0.4              | 0.6     | tCK   |  |

| ACTIVE to PRECHARGE command                             | tRAS     | 40               | 70,000 | 42               | 120,000 | ns    |  |

#### **AC TIMING REQUIREMENTS**

Absolute Specifications (VDD, VDDQ = +2.5 V ±0.2 V@-6; VDD, VDDQ = +2.6 V ±0.1 V@-5)

| PARAMETER                           |                                        | SYMBOL | -5      |      | -6      |      | UNITS |

|-------------------------------------|----------------------------------------|--------|---------|------|---------|------|-------|

|                                     |                                        |        | MIN     | МАХ  | MIN     | МАХ  |       |

| ACTIVE to ACTIVE/Auto Refresh co    | ommand                                 | tRC    | 55      | -    | 60      | Ι    | ns    |

| Auto Refresh to Active/Auto         |                                        | tRFC   | 70      | _    | 72      | -    | ns    |

| ACTIVE to READ or WRITE delay       |                                        | tRCD   | 15      | -    | 15      | -    | ns    |

| PRECHARGE command period            |                                        | tRP    | 15      | -    | 15      | -    | ns    |

| Active to Autoprecharge Delay       | Active to Autoprecharge Delay          |        | 15      | -    | 15      | -    | ns    |

| ACTIVE bank A to ACTIVE bank B      | ACTIVE bank A to ACTIVE bank B command |        | 10      | -    | 12      | -    | ns    |

| Write recovery time                 |                                        | tWR    | 15      | -    | 15      | -    | ns    |

| Auto Precharge write recovery + pre | echarge time                           | tDAL   | tWR+tRP | -    | tWR+tRP | -    | tCK   |

| Internal Write to Read Command D    | elay                                   | tWTR   | 2       | -    | 1       | -    | tCK   |

| Exit self refresh to non-READ       | Exit self refresh to non-READ          |        | 70      | -    | 70      | -    | ns    |

| Exit self refresh to READ command   |                                        | tXSRD  | 200     | -    | 200     | -    | tCK   |

| Average Periodic Refresh Interval   | $T_A \le 85 \ ^{o}C$                   | tREFI  | -       | 7.8  | _       | 7.8  | μs    |

| Average Periodic Refresh Interval   | TA > 85 °C,<br>A2 only                 | tREFI  | _       | 1.95 | _       | 1.95 | μs    |

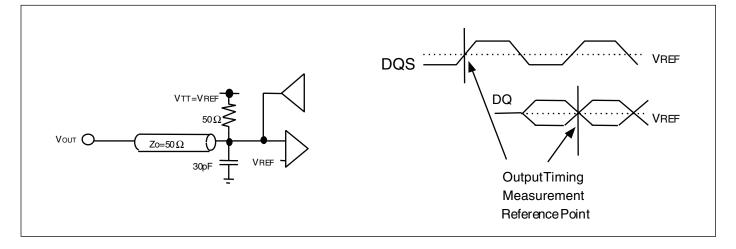

#### **Output Load Condition**

Notes

- 1. All voltages referenced to Vss.

- 2. Tests for AC timing, IDD, and electrical, AC and DC characteristics, may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

- 3. AC timing and IDD tests may use a VIL to VIH swing of up to 1.5V in the test environment, but input timing is still referenced to VREF (or to the crossing point for CK//CK), and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals is 1V/ns in the range between VIL(AC) and VIH(AC).

- 4. The AC and DC input level specifications are as defined in the SSTL\_2 Standard (i.e. the receiver will effectively switch as a result of the signal crossing the AC input level, and will remain in that state as long as the signal does not ring back above (below) the DC input LOW (HIGH) level.

- 5. VREF is expected to be equal to 0.5\*VddQ of the transmitting device, and to track variations in the DC level of the same. Peak-to-peak noise on VREF may not exceed +2% of the DC value.

- 6. VTT is not applied directly to the device. VTT is a system supply for signal termination resistors, is expected to be set equal to VREF, and must track variations in the DC level of VREF.

- 7. VID is the magnitude of the difference between the input level on CLK and the input level on /CLK.

- 8. The value of VIX is expected to equal 0.5\*VddQ of the transmitting device and must track variations in the DC level of the same.

- 9. Enables on-chip refresh and address counters.

- 10. IDD specifications are tested after the device is properly initialized.

- 11. This parameter is sampled. VDDQ = 2.5V, VDD = 2.5V, f = 100 MHz, Ta = 25°C, VOUT(DC) = VddQ/2, VOUT(PEAK TO PEAK) = 25mV. DM inputs are grouped with I/O pins reflecting the fact that they are matched in loading (to facilitate trace matching at the board level).

- 12. The CLK//CLK input reference level (for timing referenced to CLK//CLK) is the point at which CLK and /CLK cross; the input reference level for signals other than CLK//CLK, is VREF.

- 13. Inputs are not recognized as valid until VREF stabilizes. Exception: during the period before VREF stabilizes, CKE< 0.3VddQ is recognized as LOW.

- 14. tHZ and tLZ transitions occur in the same access time windows as valid data transitions. These parameters are not referenced to a specific voltage level, but specify when the device output is no longer driving (HZ), or begins driving (LZ).

- 15. The maximum limit for this parameter is not a device limit. The device will operate with a greater value for this parameter, but system performance (bus turnaround) will degrade accordingly.

- 16. The specific requirement is that DQS be valid (HIGH, LOW, or at some point on a valid transition) on or before this CLK edge. A valid transition is defined as monotonic, and meeting the input slew rate specifications of the device. When no writes were previously in progress on the bus, DQS will be transitioning from High-Z to logic LOW. If a previous write was in progress, DQS could be HIGH, LOW, or transitioning from HIGH to LOW at this time, depending on tDQSS.

- 17. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM device.

- 18. tXPRD should be 200 tCLK in the condition of the unstable CLK operation during the power down mode.

- 19. For command/address and CK & /CK slew rate > 1.0V/ns.

- 20. Min (tCL,tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device.

#### **OUTPUT SLEW RATE CHARACTERISTICS**

| Slew Rate Characteristic | Typical Range<br>(V/ns) | Min<br>(V/ns) | Max<br>(V/ns) |  |

|--------------------------|-------------------------|---------------|---------------|--|

| Pullup Slew Rate         | 1.2-2.5                 | 0.7           | 5.0           |  |

| Pulldown Slew Rate       | 1.2-2.5                 | 0.7           | 5.0           |  |

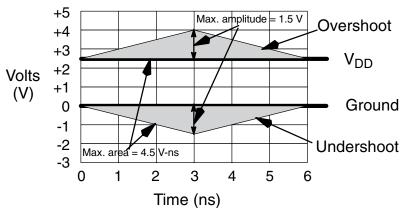

#### AC OVERSHOOT/UNDERSHOOT SPECIFICATION FOR ADDRESS AND CONTROL PINS

| Parameter                                                                                   | Max | Units |

|---------------------------------------------------------------------------------------------|-----|-------|

| Peak amplitude allowed for overshoot                                                        | 1.5 | V     |

| Peak amplitude allowed for undershoot                                                       | 1.5 | V     |

| Area between the overshoot signal and VDD must be less than or equal to (see figure below)  | 4.5 | V-ns  |

| Area between the undershoot signal and GND must be less than or equal to (see figure below) | 4.5 | V-ns  |

Address and Control AC Overshoot and Undershoot Definition

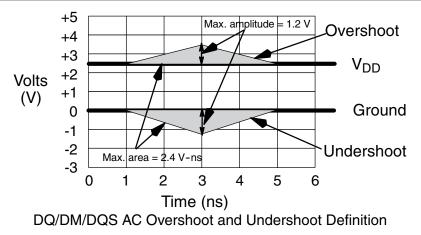

#### OVERSHOOT/UNDERSHOOT SPECIFICATION FOR DATA, STROBE, AND MASK PINS

| Parameter                                                                                   | Max | Units |

|---------------------------------------------------------------------------------------------|-----|-------|

| Peak amplitude allowed for overshoot                                                        | 1.2 | V     |

| Peak amplitude allowed for undershoot                                                       | 1.2 | V     |

| Area between the overshoot signal and VDD must be less than or equal to (see figure below)  | 2.4 | V-ns  |

| Area between the undershoot signal and GND must be less than or equal to (see figure below) | 2.4 | V-ns  |

# 64Mx8 ORDERING INFORMATION

#### Commercial Range: 0°C to +70°C

| Frequency    | Speed (ns)   | Order Part No.                                          | Package                                                            |  |

|--------------|--------------|---------------------------------------------------------|--------------------------------------------------------------------|--|

| 200 MHz      | 5            | IS43R86400D-5BL<br>IS43R86400D-5B                       | 60-ball BGA, Lead-free<br>60-ball BGA                              |  |

|              |              | IS43R86400D-5B<br>IS43R86400D-5TL                       | 66-pin TSOP-II, Lead-free                                          |  |

| 166 MHz      | 6            | IS43R86400D-6BL<br>IS43R86400D-6TL                      | 60-ball BGA, Lead-free<br>66-pin TSOP-II, Lead-free                |  |

| Industrial F | Range: -40°C | to +85°C                                                |                                                                    |  |

| Frequency    | Speed (ns)   | Order Part No.                                          | Package                                                            |  |