# ATCA-F125ATCA-F125 (6873M Artwork) Installation and Use

Installation and Use P/N: 6806800J94K August 2014

<sup>©</sup> Copyright 2014 Artesyn Embedded Technologies, Inc.

All rights reserved.

### Trademarks

Artesyn Embedded Technologies, Artesyn and the Artesyn Embedded Technologies logo are trademarks and service marks of Artesyn Embedded Technologies, Inc.<sup>©</sup> 2014 Artesyn Embedded Technologies, Inc. All other product or service names are the property of their respective owners.

Intel<sup>®</sup> is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

Java<sup>™</sup> and all other Java-based marks are trademarks or registered trademarks of Oracle America, Inc. in the U.S. and other countries.

Microsoft<sup>®</sup>, Windows<sup>®</sup> and Windows  $Me^{\mathbb{B}}$  are registered trademarks of Microsoft Corporation; and Windows  $XP^{\text{TM}}$  is a trademark of Microsoft Corporation.

PICMG<sup>®</sup>, CompactPCI<sup>®</sup>, AdvancedTCA<sup>™</sup> and the PICMG, CompactPCI and AdvancedTCA logos are registered trademarks of the PCI Industrial Computer Manufacturers Group.

UNIX<sup>®</sup> is a registered trademark of The Open Group in the United States and other countries.

### Notice

While reasonable efforts have been made to assure the accuracy of this document, Artesyn assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Artesyn reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Artesyn to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to an Artesyn website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Artesyn.

It is possible that this publication may contain reference to or information about Artesyn products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Artesyn intends to announce such Artesyn products, programming, or services in your country.

## Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Artesyn.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

## **Contact Address**

Artesyn Embedded Technologies Marketing Communications 2900 S. Diablo Way, Suite 190 Tempe, Arizona 85282 Artesyn Embedded Technologies Lilienthalstr. 17-19 85579 Neubiberg/Munich Germany

# Contents

| Ab | out th | nis Manual                          | , 11 |

|----|--------|-------------------------------------|------|

| 1  | Intro  | oduction                            | . 15 |

|    | 1.1    | Features                            | . 15 |

|    | 1.2    | Standard Compliances                |      |

|    | 1.3    | Mechanical Data                     |      |

|    | 1.4    | Ordering Information                |      |

|    |        | 1.4.1 Blade Accessories             |      |

|    | 1.5    | Product Identification              | . 21 |

| 2  | Harc   | Iware Preparation and Installation  | . 23 |

|    | 2.1    | Overview                            | .23  |

|    | 2.2    | Unpacking and Inspecting the Blade  |      |

|    | 2.3    | Requirements                        |      |

|    |        | 2.3.1 Environmental Requirements    |      |

|    |        | 2.3.2 Thermal Requirements          |      |

|    |        | 2.3.3 Power Requirements            |      |

|    | 2.4    | Rear Transition Modules             |      |

|    | 2.5    | Blade Configuration                 | . 30 |

|    |        | 2.5.1 SATA Drive Installation       | . 30 |

|    | 2.6    | Blade Installation and Removal      | . 30 |

|    |        | 2.6.1 Installing Blade              | . 31 |

|    |        | 2.6.2 Removing blade                | . 34 |

|    | 2.7    | AMC Module Installation and Removal | . 36 |

|    | 2.8    | Installing and Removing SFP Modules | . 39 |

|    |        | 2.8.1 Installing an SFP Module      | . 40 |

|    |        | 2.8.2 Removing an SFP Module        | . 43 |

| 3  | Cont   | trols, LEDs, and Connectors         | . 47 |

|    | 3.1    | Overview                            | . 47 |

|    | 3.2    | Blade Layout                        | . 47 |

|    | 3.3    | Faceplate LEDs                      | . 47 |

|    | 3.4    | Reset Switch                        | . 49 |

|    | 3.5    | Faceplate Connectors                | . 49 |

ATCA-F125 (6873M Artwork) Installation and Use (6806800J94K)

### Contents

|   | 3.6  | Backplane Connectors                          | 52 |

|---|------|-----------------------------------------------|----|

|   |      | 3.6.1 Zone 1                                  | 52 |

|   |      | 3.6.2 Zone 2                                  | 53 |

|   |      | 3.6.3 Zone 3                                  | 56 |

|   | 3.7  | Module Connectors                             | 58 |

|   |      | 3.7.1 AMC Connector                           | 59 |

|   |      | 3.7.2 SAS/SATA Connector                      | 61 |

|   |      | 3.7.3 Embedded USB Connector                  | 61 |

|   |      | 3.7.4 Processor COP Header                    | 62 |

|   |      | 3.7.5 H8S Console and Programming Header      | 63 |

|   | 3.8  | Switches                                      | 63 |

|   |      |                                               |    |

| 4 | Func | tional Description                            | 65 |

| 1 |      | -                                             |    |

|   | 4.1  | Block Diagram                                 |    |

|   | 4.2  | Processor                                     |    |

|   | 4.3  | Метогу                                        |    |

|   |      | 4.3.1 Memory Interface                        |    |

|   |      | 4.3.2 Memory Sockets                          |    |

|   |      | 4.3.3 Memory Modules                          |    |

|   |      | 4.3.4 Persistent Memory                       |    |

|   | 4.4  | IPMI                                          |    |

|   |      | 4.4.1 Temperature Sensors                     | 71 |

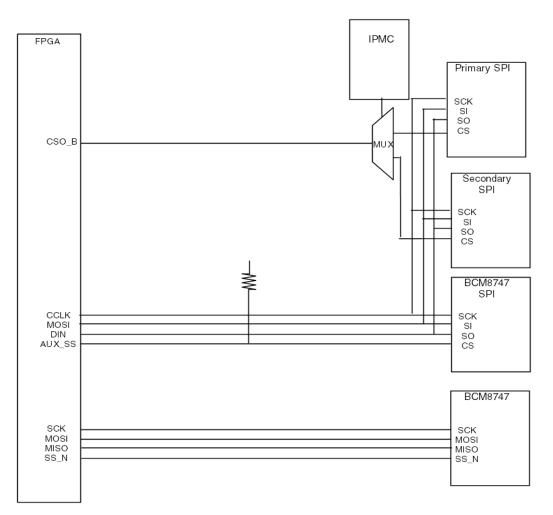

|   | 4.5  | FPGA                                          |    |

|   |      | 4.5.1 Serial Configuration PROM               | 72 |

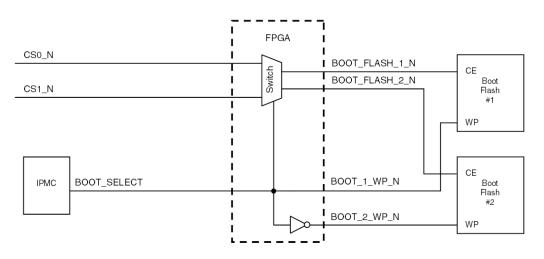

|   | 4.6  | Boot and User Flashes                         | 74 |

|   |      | 4.6.1 Boot Flash Backup Recovery              | 74 |

|   | 4.7  | Base Channel Interface                        | 75 |

|   |      | 4.7.1 Base Channel PHYs                       | 78 |

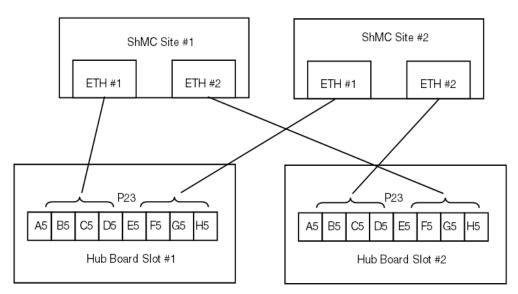

|   |      | 4.7.2 ShMC Cross-Connect                      | 79 |

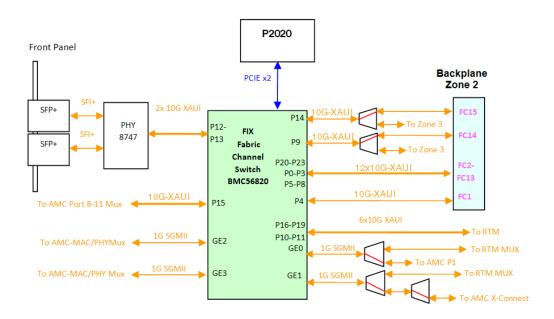

|   | 4.8  | Fabric Channel Interface                      | 79 |

|   | 4.9  | SFP+ Modules                                  | 82 |

|   | 4.10 | AMC Bay                                       | 84 |

|   |      | 4.10.1 BCM5709S Dual Gigabit Ethernet MAC/PHY |    |

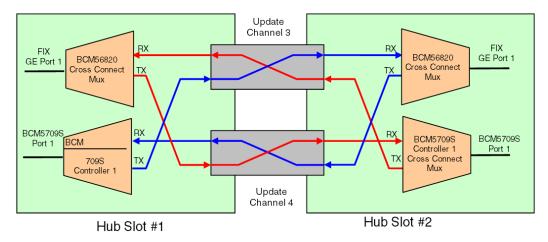

|   |      | 4.10.2 Channel Cross-Connect for BCM5709S.    | 87 |

|   |      | 4.10.3 Storage Hard Disk Drive                | 88 |

|   |      |                                               |    |

4

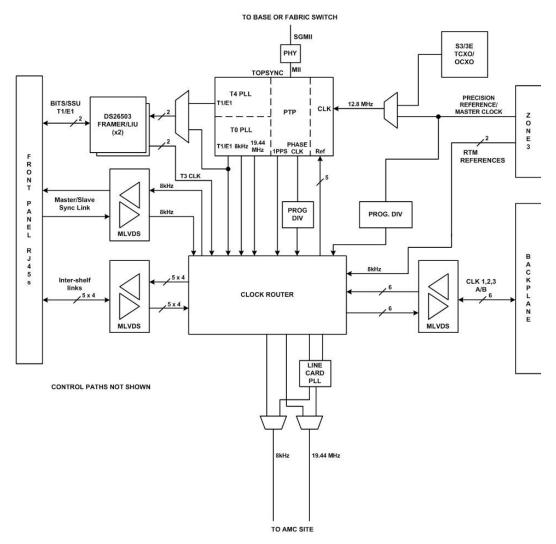

|   | 4.11 | Telecom Clocking                                      | 88              |

|---|------|-------------------------------------------------------|-----------------|

|   |      | 4.11.1 Telecom Clocking Subsystem                     | 90              |

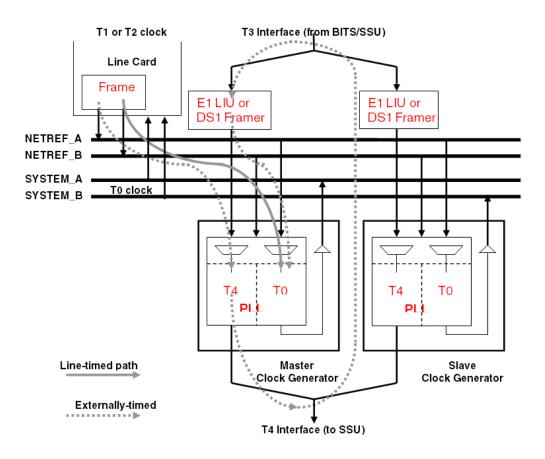

|   |      | 4.11.2 BITS/SSU Support                               | 91              |

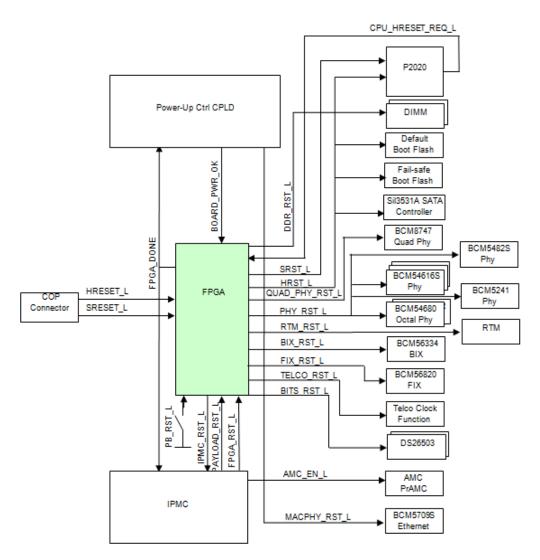

|   | 4.12 | Reset Structure                                       | 93              |

|   |      | 4.12.1 Service Processor Core Reset Domain            | 94              |

|   |      | 4.12.1.1 Service Processor                            | 94              |

|   |      | 4.12.1.2 Memory                                       | 95              |

|   |      | 4.12.1.3 Onboard Flash                                | 95              |

|   |      | 4.12.1.4 Persistent Memory                            | 95              |

|   |      | 4.12.2 Ethernet Switch Resets                         | 95              |

|   |      | 4.12.2.1 Broadcom BCM56334                            | 95              |

|   |      | 4.12.2.2 Broadcom BCM56820                            | 95              |

|   |      | 4.12.3 Physical Interconnect Devices                  |                 |

|   |      | 4.12.4 AMC Bay                                        | 96              |

|   |      | 4.12.5 Rear Transition Module                         | 96              |

|   | 4.13 | Interrupt Structure                                   | 97              |

|   |      |                                                       |                 |

| 5 | U-Bo | ot                                                    | 101             |

|   | 5.1  | Overview                                              | 101             |

|   | 5.2  | Accessing U-Boot                                      |                 |

|   | 5.3  | Configuring Boot Options                              |                 |

|   | 5.5  | 5.3.1 Configuring U-Boot for Network Boot.            |                 |

|   |      | 5.3.2       Configuring U-Boot to Boot from RAM Disk. |                 |

|   |      | 5.3.3 Configuring U-Boot to Boot from Flash           |                 |

|   | 5.4  | Selecting the Boot Flashes                            |                 |

|   | 5.5  | Using the Persistent Memory Feature                   |                 |

|   | 5.6  | Memory Map                                            |                 |

|   | 5.7  | Linux Devices                                         |                 |

|   | 5.8  | Power-On Self Test                                    |                 |

|   | 0.0  | 5.8.1 POST Routines                                   |                 |

|   |      | 5.8.2 Controlling the Execution of the POST           |                 |

|   | 5.9  | ATCA-F125 Specific U-Boot Commands                    |                 |

|   |      | ATCA-F125-Specific U-Boot Environment Variables       |                 |

|   |      | · · · · · · · · · · · · · · · · · · ·                 | · · · · · · · - |

|   | 5.11 | Updating U-Boot                                       |                 |

### Contents

| Α   | Batte               | ery Exchange11                                                                                                    | 7 |  |  |

|-----|---------------------|-------------------------------------------------------------------------------------------------------------------|---|--|--|

|     | A.1                 | Replacing the Battery11                                                                                           | 7 |  |  |

| B   | Relat               | ed Documentation                                                                                                  | 9 |  |  |

|     |                     | Artesyn Embedded Technologies - Embedded Computing Documentation       11         Related Specifications       12 |   |  |  |

| Saf | Safety Notes        |                                                                                                                   |   |  |  |

| Sic | Sicherheitshinweise |                                                                                                                   |   |  |  |

# List of Tables

| Table 1-1  | Standard Compliances                                          | 16 |

|------------|---------------------------------------------------------------|----|

| Table 1-2  | Mechanical Data                                               | 19 |

| Table 1-3  | Blade Variants - Ordering Information                         |    |

| Table 1-4  | Blade Accessories - Ordering Information                      |    |

| Table 2-1  | Environmental Requirements                                    |    |

| Table 2-2  | Power Requirements                                            |    |

| Table 3-1  | Faceplate LEDs                                                | 47 |

| Table 3-2  | Service Processor Ethernet RJ45 Connector Pin Assignment (J9) |    |

| Table 3-3  | Service Processor Serial RS232 RJ45 Connector (J1)            |    |

| Table 3-4  | Service Processor USB Connector (J10)                         |    |

| Table 3-5  | SFP+ Connectors Pin Assignment (J4-J7)                        |    |

| Table 3-6  | Master/Slave Sync Connector (J12-U1)                          | 51 |

| Table 3-7  | Inter-Shelf Connectors (J12-L1, L2, L3, U2, U3)               | 51 |

| Table 3-8  | T1/E1 Port Connectors (J12-L4 and J12-U4)                     | 51 |

| Table 3-9  | Zone 1 Connector P1 Pin Assignment                            |    |

| Table 3-10 | Connector P20 Pin Assignment                                  |    |

| Table 3-11 | Connector P21 Pin Assignment                                  |    |

| Table 3-12 | Connector P22 Pin Assignment                                  |    |

| Table 3-13 | Connector P23 Pin Assignment                                  |    |

| Table 3-14 | Connector P24 Pin Assignment                                  |    |

| Table 3-15 | Connector P32 Pin Assignment                                  |    |

| Table 3-16 | Connector P30 Pin Assignment                                  |    |

| Table 3-17 | Connector P31 Pin Assignment                                  |    |

| Table 3-18 | J8 AMC Bay Connector Pin Assignment                           |    |

| Table 3-19 | J11 SAS/SATA Connector Pin Assignment                         | 61 |

| Table 3-20 | P8 eUSB Header Pin Assignment                                 | 61 |

| Table 3-21 | P50 COP Header Pin Assignment                                 | 62 |

| Table 3-22 | P9 H8S Console Header Pin Assignment                          | 63 |

| Table 3-23 | Switch Settings                                               | 63 |

| Table 4-1  | Temperature Sensors                                           | 71 |

| Table 4-2  | Boot PROM Backup Recovery Operation                           | 75 |

| Table 4-3  | BCM56344 Base Channel Switch Connections                      |    |

| Table 4-4  | Fabric Channel Switch Connections                             |    |

| Table 4-5  | Tested SFP+ Modules                                           |    |

| Table 4-6  | AMC Bay Port Assignments                                      |    |

| Table 4-7  | Reset Signals                                                 |    |

ATCA-F125 (6873M Artwork) Installation and Use (6806800J94K)

### List of Tables

| Table 4-8 | Interrupt Mapping                                               | 97  |

|-----------|-----------------------------------------------------------------|-----|

| Table 5-1 | Physical Address Map                                            |     |

| Table 5-2 | Linux Devices                                                   |     |

| Table 5-3 | POST Result Format                                              | 108 |

| Table 5-4 | Post Results in SYS FW PROGRESS IPMI Sensor Reading Data        |     |

| Table 5-5 | SYS FW PROGRESS IPMI Sensor - POST Error Event Codes            | 109 |

| Table 5-6 | POST Routines                                                   |     |

| Table 5-7 | Environment Variable post_control                               |     |

| Table 5-8 | ATCA-F125 Specific U-Boot Commands                              |     |

| Table 5-9 | ATCA-F125 Specific U-Boot Environment Variables                 | 112 |

| Table B-1 | Artesyn Embedded Technologies - Embedded Computing Publications |     |

| Table B-2 | Specifications                                                  | 120 |

|           |                                                                 |     |

# List of Figures

| Declaration of Conformity                | . 18                      |

|------------------------------------------|---------------------------|

| Serial Number Locater                    | . 21                      |

| ATCA-F125 Face Plate                     | . 47                      |

| Module Connectors Location               | . 58                      |

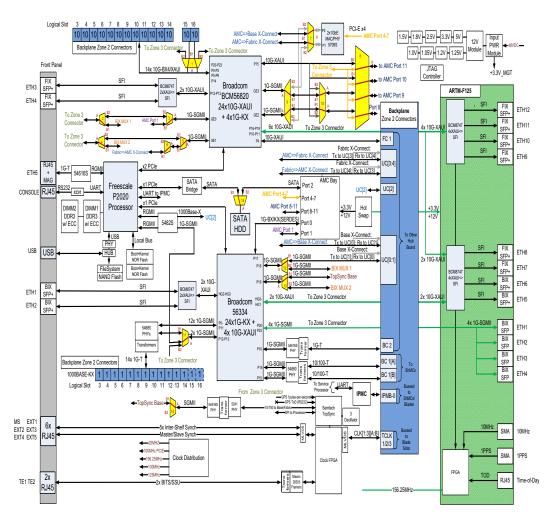

| Block Diagram                            | . 65                      |

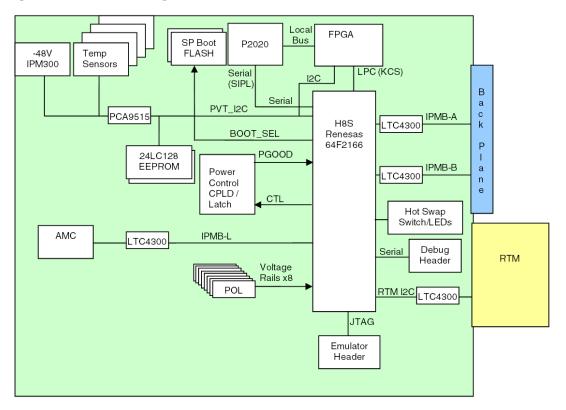

| IPMI Block Diagram                       | . 70                      |

| FPGA SPI ROM Configuration               | . 73                      |

| Boot PROM Backup Recovery                | . 74                      |

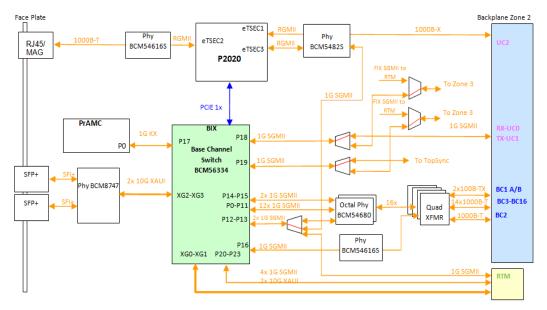

| Base Channel Block Diagram               | . 76                      |

|                                          |                           |

| Fabric Channel Block Diagram             | . 80                      |

| SFP+ Module Status and Control Interface | . 83                      |

| AMC Bay Connection Diagram               | . 85                      |

|                                          |                           |

| Fabric Channel Cross Connect             | . 88                      |

|                                          |                           |

| BITS/SSU Clock Flow                      | . 92                      |

| Reset Structure Block Diagram            | . 93                      |

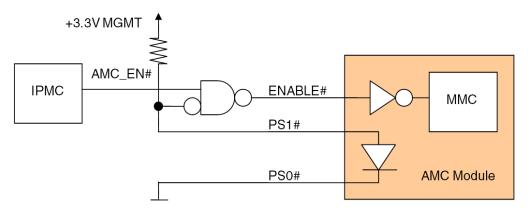

| AMC Enable Logic                         | . 96                      |

|                                          | Declaration of Conformity |

### **List of Figures**

# **About this Manual**

## **Overview of Contents**

This manual is divided into the following chapters and appendices.

- *Introduction* gives an overview of the features of the product, standard compliances, mechanical data, and ordering information.

- *Hardware Preparation and Installation* outlines the installation requirements, hardware accessories, and installation procedures.

- *Controls, LEDs, and Connectors* describes external interfaces of the board. This include connectors, LEDs, and mechanical switches.

- *Functional Description* includes a block diagram and functional description of major components of the product.

- *U-Boot* describes the boot firmware.

- Battery Exchange contains the procedures for replacing the battery.

- *Related Documentation* provides a listing of related product documentation, manufacturer's documents, and industry standard specifications.

- Safety Notes summarizes the safety instructions in the manual.

- Sicherheitshinweise is a German translation of the Safety Notes chapter.

# **Abbreviations**

This document uses the following abbreviations:

| Abbreviation | Definition                                 |

|--------------|--------------------------------------------|

| ATCA         | Advanced Telecom Computing Architecture    |

| AMC          | Advanced Mezzanine Card                    |

| IPMI         | Intelligent Platform Management Interface  |

| IPMC         | Intelligent Platform Management Controller |

| JTAG         | Joint Test Action Group                    |

| Abbreviation | Definition                                  |

|--------------|---------------------------------------------|

| PICMG        | PCI Industrial Computer Manufacturers Group |

| POST         | Power-on Self Test                          |

| PrAMC        | Processor Advanced Mezzanine Card           |

| RTM          | Rear Transition Module                      |

## Conventions

The following table describes the conventions used throughout this manual.

| Notation       | Description                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------|

| 0x0000000      | Typical notation for hexadecimal numbers (digits are 0 through F), for example used for addresses and offsets |

| 0Ь0000         | Same for binary numbers (digits are 0 and 1)                                                                  |

| bold           | Used to emphasize a word                                                                                      |

| Screen         | Used for on-screen output and code related elements or commands in body text                                  |

| Courier + Bold | Used to characterize user input and to separate it from system output                                         |

| Reference      | Used for references and for table and figure descriptions                                                     |

| File > Exit    | Notation for selecting a submenu                                                                              |

| <text></text>  | Notation for variables and keys                                                                               |

| [text]         | Notation for software buttons to click on the screen and parameter description                                |

|                | Repeated item for example node 1, node 2,, node 12                                                            |

| •              | Omission of information from example/command that is not necessary at the time being                          |

|                |                                                                                                               |

|                | Ranges, for example: 04 means one of the integers 0,1,2,3, and 4 (used in registers)                          |

| Notation | Description                                                                                    |

|----------|------------------------------------------------------------------------------------------------|

|          | Logical OR                                                                                     |

|          | Indicates a hazardous situation which, if not avoided, could result in death or serious injury |

|          | Indicates a hazardous situation which, if not avoided, may result in minor or moderate injury  |

|          | Indicates a property damage message                                                            |

|          | No danger encountered. Pay attention to important information                                  |

# **Summary of Changes**

This manual has been revised and replaces all prior editions.

| Part Number | Publication Date | Description                                                                                                                   |

|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 6806800J94A | December, 2009   | First edition                                                                                                                 |

| 6806800J94A | January, 2011    | GA Release.                                                                                                                   |

| 6806800J94A | June, 2011       | Added Figure "Declaration of Conformity" on<br>page 18.<br>Edited Table "Faceplate LEDs" on page 43.                          |

| 6806800J94B | March, 2012      | Updated Chapter 4, Functional Description, on page 61, Chapter P, EMC, on page 118, and Chapter P, Installation, on page 119. |

| Part Number | Publication Date | Description                                                                                                                                                                        |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6806800J94C | August, 2012     | Updated Ordering Information on page 18, Figure<br>"Serial Number Locator" on page 20, Figure<br>"Module Connectors Location" on page 54, and<br>Functional Description on page 61 |

| 6806800J94D | December 2012    | Updated Standard Compliances on page 16.                                                                                                                                           |

| 6806800J94E | October, 2013    | Updated Table 2-2 on page 28.                                                                                                                                                      |

| 6806800J94F | November, 2013   | Updated title as ATCA-F125 (6873M Artwork)<br>Table 1-3 on page 19, Table 2-1 on page 26.                                                                                          |

| 6806800J94G | December, 2013   | Replaced "Product Name Short" with ATCA-<br>F125.                                                                                                                                  |

| 6806800J94H | January, 2014    | Updated Table 3-3 on page 49.                                                                                                                                                      |

| 6806800J94J | April, 2014      | Re- branded to Artesyn template.                                                                                                                                                   |

| 6806800J94K | August 2014      | Removed instances of Stratum 3E and updated Declaration of Conformity.                                                                                                             |

## 1.1 Features

The ATCA-F125 is a hub board as defined in PICMG 3.0 Revision 3.0 Advanced TCA Base Specification and PICMG 3.1 Revision 1.0 Specification Ethernet/Fiber Channel for AdvancedTCA Systems. It supports several Base and Fabric Channel Ethernet interfaces to the Zone 2 backplane. It also supports 1 Gb and 10 Gb Ethernet uplinks to the front panel and to a Rear Transition Module (RTM) through the Zone 3 connector.

Broadcom Ethernet switches and PHYs are used for the base and fabric channels. The entire board is managed by a Freescale P2020 QorIQ Integrated Processor.

The ATCA-F125 has several optional features including a processor AMC, local storage and Telecom clocking.

See the list below for some of the key features of the ATCA-F125:

- Single slot ATCA form factor (280 mm x 322 mm)

- Freescale P2020 QorIQ Integrated Processor for the on board service processor functions

- Two DDR3 memory DIMM slots each of which can support up to 2 GB of DDR3 SDRAM with ECC

- 2 GB default configuration

- 2 GB embedded USB Flash module for User Flash memory

- Onboard SATA connector for an optional drive with selectable interface to either the service processor or the processor AMC

- Real time clock

- RJ-45 UART Console interface to service processor on front panel

- RJ-4510/100/1000 BaseTx Ethernet Management port on the front panel for P2020 QorlQ Integrated Processor

- Single USB port on front panel for P2020 processor

- Broadcom BCM56334 managed switch device for the Base Channel to provide 24 ports of Gigabit Ethernet and four 10G XAUI ports with two 10G uplink channels on the front panel

- Broadcom BCM56820 managed switch device for the Fabric Channel to provide 24 10G XAUI ports and four 1G SGMII ports with two 10G uplink channels on the front panel

- Multiple 1 GbE SGMII and 10 GbE XAUI ports routed to Zone 3 connectors for base and fabric uplink channels on RTM

- Stratum 3 Telecom clock options with master/slave sync and five inter-shelf sync connectors on front panel along with 2 BITS/SSU front panel connectors

- Synchronous Ethernet support

- One AMC bay for application processor support

- IPMC functionality for the board management by the Shelf Management Controller

## 1.2 Standard Compliances

This blade, when installed in a compliant shelf, meets the following standards.:

| Standard                                                                        | Description                                                                               |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| UL/CSA No. 60950-1<br>EN 60950-1<br>IEC 60950-1 CB Scheme<br>UL/CSA No. 60950-1 | Legal safety requirements                                                                 |

| ANSI T1.319-2002<br>NEBS GR-63-CORE                                             | ANSI Fire Spread Criteria                                                                 |

| AT&T Document ATT-TP-76200                                                      | Network Equipment Power, Grounding, Environmental,<br>and Physical Design Requirements    |

| ETSI Acoustic Noise ETS 300 753<br>Class 3.1                                    | ETSI acoustic noise requirements                                                          |

| ETSI Stationary Use: EN 300 019-2-3<br>Class 3.1                                | ETSI stationary use requirements (temperature-<br>controlled locations                    |

| ETSI Storage EN 300 019-2-1 Class<br>1.2                                        | ETSI storage requirements in system level (not temperature- controlled storage locations) |

| ETSI Transportation: EN 300 019-2-2<br>Class 2.3                                | ETSI public transportation requirement on system level                                    |

| Telcordia GR-1089                                                               | Ports and litra-building lightning for telecommunication port                             |

#### Table 1-1 Standard Compliances

### Table 1-1 Standard Compliances (continued)

| Standard                                                                                                                                                             | Description                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Telcordia GR-1089-CORE                                                                                                                                               | Electromagnetic Compatibility and Electrical Safety -<br>Generic Criteria for Network Telecommunications<br>Equipment |

| Telcordia GR-63-CORE                                                                                                                                                 | NEBS Requirements: Physical Protection                                                                                |

| Telcordia SR-3580                                                                                                                                                    | NEBSCriteria Level 3                                                                                                  |

| EN55022 Class A (EU)<br>EN 55024 (EU)<br>FCC 47 CFR Part 15 Subpart B (US),<br>Class A<br>AS/NZS CISPR 22 Class A<br>(Australia/New Zealand)<br>VCCI Class A (Japan) | EMC requirements (legal) on system level (predefined<br>Artesyn Embedded Technologies system)                         |

| Verizon Document<br>VZ.NEBS.TE.NPI.2004.015: NEBS<br>Checklist                                                                                                       | Telecommunications Carrier Group NEBS Checklist                                                                       |

To fulfill the requirements of Telcordia GR-1089,R4-14, use Shielded Twisted Pair (STP) cables grounded at both ends to connect to the Ethernet ports.

The product has been designed to meet the directive on the restriction of the use of certain hazardous substances in electrical and electronic equipment (RoHS) Directive 2011/65/EU.

### Figure 1-1 Declaration of Conformity

| EC Declaration of Conformity<br>According to EN 17050-1:2004                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manufacturer's Name:                                                                                                                                                                                                                                                                                                                                                                                              | Artesyn Embedded Technologies<br>Embedded Computing                                                                                                                                                             |

| Manufacturer's Address:                                                                                                                                                                                                                                                                                                                                                                                           | Zhongshan General Carton Box Factory Co. Ltd. No 62, Qi<br>Guan Road West, Shiqi District, 528400 Zhongshan City<br>Guangdong, PRC                                                                              |

| Declares that the following pro<br>2011/65/EU and their amendi                                                                                                                                                                                                                                                                                                                                                    | oduct, in accordance with the requirements of 2004/108/EC, 2006/95/EC, ng directives,                                                                                                                           |

| Product:                                                                                                                                                                                                                                                                                                                                                                                                          | ATCA-F125 Series Switch Blade & RTM-ATCA-F125 Series                                                                                                                                                            |

| Model Name/Number:                                                                                                                                                                                                                                                                                                                                                                                                | ATCA-F125, ATCA-F125-14S, ATCA-F125-14S-C10,<br>ATCA-F125-STD-01-L2, ATCA-F125-STD-02-L2, ATCA-F125-TCLK3,<br>ATCA-F125-TCLK3-C01, RTM-ATCA-F125, RTM-ATCA-F125-C01,<br>RTM-ATCA-F125-C10, RTM-ATCA-F125-STD-01 |

| has been designed and manu                                                                                                                                                                                                                                                                                                                                                                                        | factured to the following specifications:                                                                                                                                                                       |

| EN55022:2006 (A1: 2007) Cla                                                                                                                                                                                                                                                                                                                                                                                       | ass A                                                                                                                                                                                                           |

| EN55024: 1998 (A1: 2001 + A                                                                                                                                                                                                                                                                                                                                                                                       | A2: 2003)                                                                                                                                                                                                       |

| ETSI EN 300 386 V1.5.1 (201                                                                                                                                                                                                                                                                                                                                                                                       | 0-10)                                                                                                                                                                                                           |

| IEC 60950-1:2005 (2nd Editio                                                                                                                                                                                                                                                                                                                                                                                      | n), EN60950-1:2006+A11:2009                                                                                                                                                                                     |

| 2011/65/EU RoHS Directive                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                 |

| As manufacturer we hereby declare that the product named above has been designed to comply with the relevant sections of the above referenced specifications. This product complies with the essential health and safety requirements of the above specified directives. We have an internal production control system that ensures compliance between the manufactured products and the technical documentation. |                                                                                                                                                                                                                 |

| Tom Tuttle Manager P                                                                                                                                                                                                                                                                                                                                                                                              | Product Testing Services 08/28/2014 Date (MM/DD/YYYY)                                                                                                                                                           |

| CE                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                 |

# 1.3 Mechanical Data

The following table provides details about the blade's mechanical data, such as dimensions and weight.

#### Table 1-2 Mechanical Data

| Data       | Value                                    |

|------------|------------------------------------------|

| Dimensions | 30 mm x 351 mm x 312 mm (8U form factor) |

| Weight     | 2.3 kg                                   |

# 1.4 Ordering Information

The following table lists the blade variants that were available as of the time of writing this manual. Consult your local Artesyn Embedded Technologies sales representative for the availability of further variants.

#### Table 1-3 Blade Variants - Ordering Information

| Product Name    | Description                                                                                       | PWB Artwork/Assembly No.<br>(See NOTE) |

|-----------------|---------------------------------------------------------------------------------------------------|----------------------------------------|

| ATCA-F125-14S   | 10G ATCA switch blade with (1) AMC site and optional SATA storage, ETH between CPU/Base interface | 6873M / 0106873Mxxx                    |

| ATCA-F125       | 10G ATCA switch blade with one (1) AMC site and optional SATA storage                             | 6859G / 0106859Gxxx                    |

| ATCA-F125-TCLK3 | 10G ATCA switch blade with one (1) AMC<br>site, optional storage and telecom CLK<br>Stratum 3     | 6873M / 0106873Mxxx                    |

NOTE: This manual covers the ATCA-F125-14S product. It also covers ATCA-F125-TCLK3 product manufactured with 6873M PWB artwork.

For 6859G PWB artwork documentation, refer to *ATCA-F125 Installation & Use manual* 6806800/94B. The PWB artwork may be identified by the assembly number, which is marked near the serial number as shown in Figure 1-2 on page 21.

### 1.4.1 Blade Accessories

The following table lists the blade accessories that were available as of the time of writing this manual. Consult your local sales representative for the availability of further accessories.

| Accessory         | Description                                                              |

|-------------------|--------------------------------------------------------------------------|

| RTM-ATCA-F125     | RTM for the ATCA-F125 with SFP and SFPP receptacles                      |

| SFP-MM-SX-LC      | 1G Single Form Factor (SFP) module - 850NM, SX, LC connector             |

| SFP-CO-RJ-45      | 1G copper Single Form Factor (SFP) module - RJ-45 connector              |

| SFPP-MM-SR-LC     | 10 G Single Form Factor Plus (SFPP) module - 850NM, SR, LC connector     |

| SFPP-SM-LR-LC     | 10G Single Form Factor Plus (SFPP) module -1310NM, LR, LC connector      |

| SFPP-CO-RJ-45-3M  | 10G copper Single Form Factor Plus (SFPP) modules with molded cable - 3M |

| CABLE-OPT-F102-5M | Optical cable for multi-mode, SFP and SFPP connections (5M)              |

| PRAMC-7211        | AMC CPU blade with Intel© Core2Duo 64B @ 1.5GHZ, 2G DDR2 & mid-size      |

| SA-BBS-721X       | PRAMC-721X, BBS only, BINARY RPMS, PNE 2.X, CD                           |

| SA-BBS-WR2X-721X  | PrAMC-721x, BBS binary RPMs, Eval kernel+runtime, PNE LE 2.x, CD         |

### Table 1-4 Blade Accessories - Ordering Information

# 1.5 **Product Identification**

The following graphic shows the location of the serial number label.

### *Figure 1-2 Serial Number Locater*

### Introduction

# Hardware Preparation and Installation

## 2.1 Overview

This chapter provides the information that you need to install the ATCA-F125 and its accessories into your AdvancedTCA system. Removal procedures are also included.

To install the blade, follow these steps:

- 1. Unpack and inspect the blade.

- 2. Make sure that environmental, thermal, and power requirements are met.

- 3. If applicable, install the Rear Transition Module.

- 4. Configure the ATCA-F125.

- 5. Install the ATCA-F125.

- 6. If applicable, install the AMC module.

- 7. Configure the software.

# 2.2 Unpacking and Inspecting the Blade

## NOTICE

Damage of Circuits

- Electrostatic discharge and incorrect installation and removal of the blade can damage circuits or shorten its life.

- Before touching the product make sure that you are working in an ESD-safe environment or wearing an ESD wrist strap or ESD shoes. Hold the product by its edges and do not touch any components or circuits.

Damage to blade/Backplane or System Components

• Bent pins or loose components can cause damage to the blade, the backplane, or other system components. Therefore, carefully inspect the blade and the backplane for both pin and component integrity before installation.

### **Shipment Inspection**

- 1. Verify that you have received all items of your shipment:

- Safety Notes Summary

- ATCA-F125 blade

- Any optional items ordered

- 2. Check for damage and report any damage or differences to customer service.

The blade is thoroughly inspected before shipment. If any damage occurs during transportation or any items are missing, please contact customer service immediately.

3. Remove the desiccant bag shipped together with the blade.

## NOTICE

**Environmental Damage**

- Improper disposal of used products may harm the environment.

- Always dispose of used products according to your country's legislation and manufacturer's instructions.

# 2.3 Requirements

This section shows the environmental and power requirements of the ATCA-F125 (6873M Artwork).

## 2.3.1 Environmental Requirements

When operated in your particular system configuration, make sure that the blade meets the environmental requirements specified in this section.

Operating temperatures refer to the temperature of the air circulating around the blade, and not to component temperatures.

If you integrate the blade in your own non-Artesyn Embedded Technologies system, please contact your local sales representative for further safety information.

## NOTICE

Blade Damage

- High humidity and condensation on the blade surface may cause it to short circuit.

- Do not operate the blade outside the specified environmental limits. Make sure the blade is completely dry and there is no moisture on any surface before applying power.

- Do not operate the blade below -5°C.

### Table 2-1 Environmental Requirements

| Requirement          | Operating                                                                                                                                                                                                                                                                                                                                     | Non-Operating                                                                                                                                                                                                                                                                                                      |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature          | Normal Operation: +5 °C (41 °F) to +40<br>°C (104 °F) according to Telcordia GR-<br>63-CORE (NEBS) and ETSI EN 300 019-<br>1-3, Class 3.1<br>Exceptional Operation: -5 °C (23 °F) to<br>+55 °C (131 °F) according to Telcordia<br>GR-63-CORE (NEBS)<br>Note: this exceeds ETSI EN 300 019-1-<br>3, Class 3.1E requirements (-5°C to<br>+45°C) | -40 °C (-40 °F) to +70 °C (158 °F) according<br>Telcordia GR-63-CORE (NEBS) and ETSI EN<br>300 019-1-2, Class 2.3<br>Note: This exceeds ETSI EN 300 019-1-1,<br>Class 1.2 requirements (storage from -<br>25°C to +55°C<br>Note: This may be further limited by<br>installed accessories                           |

| Temp. Change         | +/- 0.25 °C/min according to Telcordia<br>GR-63-CORE                                                                                                                                                                                                                                                                                          | +/- 0.25 °C/min                                                                                                                                                                                                                                                                                                    |

| Relative<br>Humidity | Normal Operation: 5%rH to 85%rh non-<br>condensing<br>Exceptional Operation: 5%rH to 90%rh<br>non-condensing<br>According to Telcordia GR-63-CORE<br>(NEBS) and EN 300 019-1-3, Classes 3.1<br>and 3.1E                                                                                                                                       | 5%rH to 95%rH non-condensing<br>According to Telcordia GR-63-CORE<br>(NEBS) and EN 300 019-1-1, Classes 1.2<br>and 2.3                                                                                                                                                                                             |

| Vibration            | 1g from 5 to 200Hz and back to 5Hz at<br>a rate of 0.25 octave/minute (accord-<br>ing to Telcordia GR-63-core)                                                                                                                                                                                                                                | 5-20 Hz at 0.01 g <sup>2</sup> /Hz (according to<br>Telcordia GR-63-core and ETSI EN 300<br>019-2-2)<br>20-200 Hz at -3 dB/octave Hz (according<br>to Telcordia GR-63-core and ETSI EN 300<br>019-2-2)<br>Random 5-20Hz at 1 m <sup>2</sup> /s <sup>3</sup><br>Random 20-200Hz at 3 m <sup>2</sup> /s <sup>3</sup> |

| Shock                | Half-sine, 11 ms at 30 m/s <sup>2</sup>                                                                                                                                                                                                                                                                                                       | Blade level packaging<br>Half-sine, 6 ms at 180 m/s <sup>2</sup>                                                                                                                                                                                                                                                   |

| Free Fall            | -                                                                                                                                                                                                                                                                                                                                             | <ul> <li>1.2 m/ packaged (according to ETSI 300<br/>019-2-2)</li> <li>100 mm unpackaged (according to Tel-<br/>cordia GR-63-core)</li> </ul>                                                                                                                                                                       |

ATCA-F125 (6873M Artwork) Installation and Use (6806800J94K)

## 2.3.2 Thermal Requirements

In order for the ATCA-F125 to cool properly when the operating temperature is at the maximum (55C), the chassis must meet or exceed CP-TA B.3 ATCA Chassis Specification. CP-TA B.4 compliance is preferred.

Contact your Artesyn Embedded Technologies sales representative for current information on the detailed thermal information including airflow and resistance of the blade.

| NOTICE                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Overheating                                                                                                                                                                                                                             |

| Cooling Vents                                                                                                                                                                                                                                  |

| <ul> <li>Improper cooling can lead to system damage and can void the manufacturer's warranty.</li> </ul>                                                                                                                                       |

| <ul> <li>To ensure proper cooling and undisturbed airflow through the system, do not<br/>obstruct the ventilation openings of the system. Make sure that the fresh air supply<br/>is not mixed with hot exhaust from other devices.</li> </ul> |

|                                                                                                                                                                                                                                                |

| <b>A</b> CAUTION                                                                                                                                                                                                                               |

| Personal Injury                                                                                                                                                                                                                                |

- During operation, hot surfaces may be present on the heat sinks and the components of the product.

- To prevent injury from hot surface, do not touch any of the exposed components or heatsinks on the product when handing. Use the handle and face plate, where applicable, or the board edge when removing the product from the enclosure.

### 2.3.3 Power Requirements

The blade's power requirements depend on the installed hardware accessories. To install the accessories on the blade, the load of the respective accessory has to be added to that of the blade. The following table show typical examples of the power requirements, with and without accessories installed. For information on the accessories' power requirements, refer to the documentation delivered together with the respective accessory or consult your local Artesyn Embedded Technologies representative for further details.

The blade must be connected to a TNV-2 or a safety-extra-low-voltage (SELV) circuit. A TNV-2 circuit is a circuit whose normal operating voltages exceed the limits for a SELV circuit under normal operating conditions, and which is not subject to overvoltages from telecommunication networks.

| Characteristic                                                              | Value                                                    |

|-----------------------------------------------------------------------------|----------------------------------------------------------|

| Rated Voltage Exception in the US and Canada                                | -48 VDC to -60 VDC, US and -48 VDC,<br>Canada            |

| Operating Voltage Exception in the US and Canada                            | -39 VDC to -72 VDC, US and -39 VDC to<br>-60 VDC, Canada |

| Max. power consumption of ATCA-F125 with SATA drive and RTM-ATCA-F125       | 125 W (98 W typical)                                     |

| Max. power consumption of ATCA-F125 with SATA drive (without RTM-ATCA-F125) | 105 W (80 W typical)                                     |

#### Table 2-2 Power Requirements

# 2.4 Rear Transition Modules

If applicable, install a rear transition module. For more information, refer the RTM-ATCA-F125 documents listed in Appendix B, *Related Documentation*.

The RTMs are not hot-swappable. Before installation, make sure that no front blade is installed in its respective slot, or that the front blade is powered-down. For further details about the RTM installation, refer to the installation and use guide of the respective RTM.

## NOTICE

Damage of the Product and Additional Devices and Modules

- Incorrect installation or removal of additional devices or modules damages the product or the additional devices or modules.

- Before installing or removing additional devices or modules, read the respective documentation and use appropriate tools.

# 2.5 Blade Configuration

There are no configuration switch settings for normal operational mode. Switch changes are for activating various debug modes. Setting any switched to the ON state may cause unpredictable operation.

## NOTICE

**Product Malfunction**

- Switches marked as "reserved" may carry production-related functions and can cause the product to malfunction if the setting is changed.

- Do not change settings of switches marked as "reserved".

Product Damage

- Setting/resetting the switches during operation can cause damage to the product.

- Check and change switch settings before installing the product.

**Product Damage**

- Too much force may damage the reset switch.

- Use minimal force when pressing the reset switch.

### 2.5.1 SATA Drive Installation

An optional SATA drive may be installed on the ATCA-F125. An 80GB drive designed for extreme temperature and vibration environments has been test and approved for use on the ATCA-F125. Contact your Artesyn Embedded Technologies sales representative and order the HDD-80G-SATA kit which includes the hard drive, all the required mounting hardware, and the installation instructions.

# 2.6 Blade Installation and Removal

The blade is fully compatible to the AdvancedTCA standard and is designed to be used in AdvancedTCA shelves.

The blade must only be installed into the proper slot type of shelf, hub blades in hub slots, payload blades in blade slots. The proper slots may vary by system type. Refer to the system's documentation for information which slots these are in your particular configuration.

## NOTICE

Damage of Circuits

- Electrostatic discharge and incorrect blade installation and removal can damage circuits or shorten its life.

- Before touching the blade or electronic components, make sure that you are working in an ESD-safe environment.

Damage of the blade

- Incorrect installation of the blade can cause damage to the blade.

- Only use handles when installing/removing the blade to avoid damage/deformation to the face plate and/or PCB.

## 2.6.1 Installing Blade

To install the blade into an AdvancedTCA Shelf, proceed as follows.

### Installing the Blade

The following procedure describes the installation of the blade in a hub slot that does not have an RTM. It assumes that your system is powered. If your system is powered down, you can disregard the blue LED and thus skip its respective step. In this case it is a purely mechanical installation.

If there is a Rear Transition Module (RTM) to install, install and secure the RTM first as described in the RTM-ATCA-F125 Installation and Use Guide, then install the front blade. If an RTM is already installed, make sure that the RTM faceplate screws are fully tightened to secure the RTM to the shelf.

- 1. Visually inspect the blade and backplane connectors for damage or bent pins before attempting to insert a board. If any connector damage or pin damage in observed, stop before inserting the blade and send the damaged item through proper repair channels.

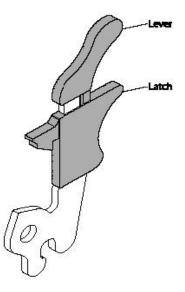

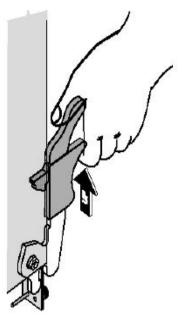

- 2. Ensure that the top and bottom ejector handles are in the outward position by squeezing the lever and the latch together.

- 3. Insert blade into the shelf by placing the top and bottom edges of the blade in the card guides of the shelf. Make sure that the guiding module of shelf and blade are aligned properly.

- 4. Apply equal and steady pressure to the blade to carefully slide the blade into the shelf until you feel resistance. Continue to gently push the blade until the blade connectors engage.

- 5. Squeeze the lever and the latch together and hook the lower and the upper handle into the shelf rail recesses.

6. Fully insert the blade and lock it to the shelf by squeezing the lever and the latch together and turning the handles towards the face plate.

If you feel that you need an abnormal amount of force during blade insertion to insert the blade into the slot, please extract the blade, then carefully inspect the blade and slot for problems to prevent damage.

If your shelf is powered, as soon as the blade is connected to the backplane power pins, the blue LED is illuminated.

When the blade is completely installed, the blue LED starts to blink. This indicates that the blade announces its presence to the shelf management controller.

If an RTM is connected to the front blade, make sure that the handles of both the RTM and the front blade are closed in order to power up the blade's payload.

- 7. Wait until the blue LED is switched off, then tighten the face plate screws which secure the blade to the shelf. When the blue LED is switched OFF and the green LED "OK" is switched ON, this indicates that the payload has been powered up and that the blade is active.

- 8. Connect cables to the face plate, if applicable.

## 2.6.2 Removing blade

This section describes how to remove the blade from an AdvancedTCA system.

|     | NOTICE                                                                                                         |

|-----|----------------------------------------------------------------------------------------------------------------|

| Dar | nage of circuits                                                                                               |

| •   | Electrostatic discharge and incorrect blade installation and removal can damage circuits or shorten its life.  |

| •   | Before touching the blade or electronic components, make sure that you are working in an ESD-safe environment. |

| Dar | nage of the blade                                                                                              |

| •   | Incorrect installation of the blade can cause damage of the blade.                                             |

| •   | Only use handles when installing/removing the blade to avoid damage/deformation to the face plate and/or PCB.  |

### **Removing the Blade**

The following procedure describes how to remove the blade from a system. It assumes that the system is powered. If the system is powered down, you can disregard the blue LED and skip the respective step. In that case it is a purely mechanical procedure.

1. Unlatch the lower handle from the face plate by squeezing the lever and the latch together and turning the handle outward. Do not rotate the handle fully outward. The blue LED blinks indicating that the blade power-down process is ongoing.

## NOTICE

Data Loss

- Removing the blade with the blue LED still blinking causes data loss.

- Wait until the blue LED is steadily lit before removing the blade.

- 2. Wait until the blue LED is illuminated permanently. Unfasten the screw of the faceplate, then unlatch the upper handle and rotate both handles fully outward until the blade is detached from the shelf.

If the LED continues to blink, it is possible that the upper layer software rejects the blade extraction request.

- 3. Remove the face plate cables, if applicable.

- 4. Remove the blade from the shelf.

# 2.7 AMC Module Installation and Removal

The blade comes with an AMC Bay. For more information, see AMC Bay, on page 84.

## NOTICE

Damage of Circuits

- Electrostatic discharge and incorrect installation and removal of the blade can damage circuits or shorten its life.

- Before touching the blade or electronic components, make sure that you are working in an ESD-safe environment.

AMC Module Damage

• The AMC bay supports only AMC modules that are officially supported by Artesyn Embedded Technologies. Installing and operating other AMC modules may damage the AMC bay and the blade.

Limitation of Operating Temperature Range

- Installing AMC modules with small operating temperature ranges into the ATCA-F125 may further restrict the operating temperature range of the ATCA-F125.

- Make sure that the operating temperature of any installed AMC modules and the ATCA-F125 as a bundle are within allowed limits.

Poor Shelf Cooling and EMC Compliance Violation

- An empty AMC bay may result in poor shelf cooling and strong EMC radiation and lead to EMC compliance violation.

- Always cover empty or unused AMC bays with a filler panel.

#### Installation Procedure

This procedure assumes that the AdvancedATCA system is powered. If your system is powered down, you can disregard the instructions regarding the blue LED.

- 1. If the AMC bay is occupied by an AMC filler panel, remove the filler panel.

- 2. Make sure that the AMC module handle is in the extracted position: pulled outward, away from the face plate.

- 3. Using your thumb, apply equal and steady pressure on the face plate as necessary to carefully slide the AMC module into the guide rails.

- 4. Continue pushing the module gently along the guide rails until the module is fully engaged with the connector. Avoid using excessive force.

- 5. Wait for the blue LED to glow. The blue LED glows when the AMC module is completely engaged with the connector.

- 6. Press module handle inwards towards the face plate to lock the AMC module on the AMC bay.

- 7. Wait for the blue LED to perform a series of long blinks. The blue LED blinks when the handle is locked in position indicating module detection and activation by the carrier board.

- 8. Observe blue LED status/activity. The module is fully installed when the blue LED stops blinking and stays OFF.

#### **Removal Procedure**

This procedure assumes that the AdvancedATCA system is powered. If your system is powered down, you can disregard the instructions regarding the blue LED.

- 1. Remove any cables that are connected to the AMC module face plate connectors.

- 2. Gently pull the module latch outwards, approximately 3 mm away from its locked position.

- 3. Wait for the blue LED to perform short blinks, and then glow steadily.

- NOTICE Data Loss Removing the blade with the blue LED still blinking causes data loss. Wait until the blue LED is steadily lit, before removing the blade.

- 4. Once the blue LED glows steadily, gently pull the AMC module handles outwards to disconnect the module from the AMC connectors. Continue to gently slide the module outwards along the guide rails.

- 5. Install the filler panel.

•

# 2.8 Installing and Removing SFP Modules

This section describes how to install and remove SFP modules.

| Eye Damage                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Optical SFP modules may emit laser radiation when no cable is connected.                                                                                                                                                                                             |

| • Avoid staring into open apertures to avoid damage to your eyes.                                                                                                                                                                                                      |

| Personal Injury and Damage of the RTM and SFP Modules                                                                                                                                                                                                                  |

| • Installing and using SFP modules which are not fully certified and which do not meet all relevant safety standards may damage the RTM and the SFP modules and may lead to personal injury.                                                                           |

| • Only use and install SFP modules which are fully certified and which meet all relevant safety standards.                                                                                                                                                             |

| Personal Injury                                                                                                                                                                                                                                                        |

| • Optical SFP modules may be classified as laser products. When installing and using any of these SFP modules, the regulations which correspond to the respective laser class apply to the whole RTM. Not complying to these regulations, may lead to personal injury. |

| • When installing and using optical SFP modules which are classified as laser products, make sure to comply to the respective regulations.                                                                                                                             |

SFP modules can be installed/removed while the RTM is both powered and or powered off. The presence and also the type of SFP modules is automatically detected.

The maximum power consumption of all installed SFP modules must not exceed 12 W.

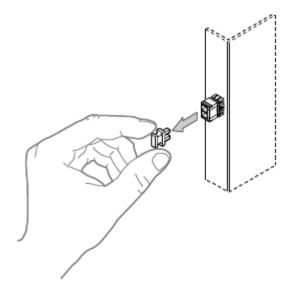

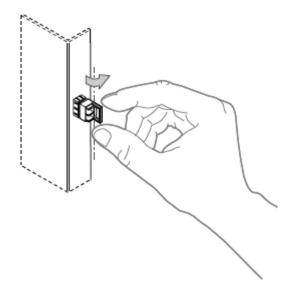

# 2.8.1 Installing an SFP Module

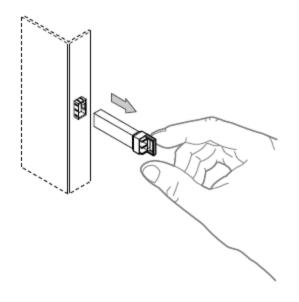

## Procedure

In order to install an SFP module, proceed as follows:

1. Slide the SFP module into the slot until it locks into position.

2. Remove the optical port plug.

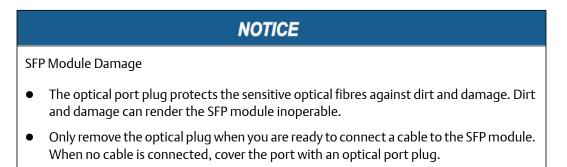

# NOTICE

#### SFP Module Damage

- The optical port plug protects the sensitive optical fibres against dirt and damage. Dirt and damage can render the SFP module inoperable.

- Only remove the optical plug when you are ready to connect a cable to the SFP module. When no cable is connected, cover the port with an optical port plug.

3. Connect the network cable to the SFP module

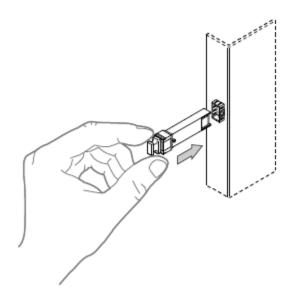

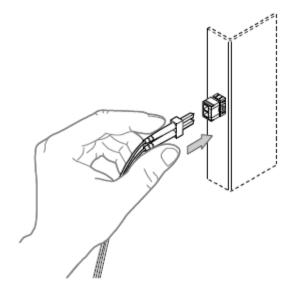

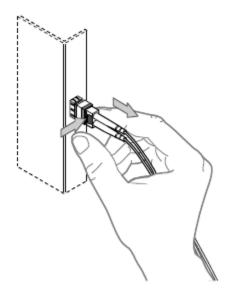

# 2.8.2 Removing an SFP Module

## Procedure

In order to remove an SFP module, proceed as follows.

1. Remove any connected cable from the SFP module.

2. Open the SFP latch. Note that the latch mechanism of your SFP module may be

slightly different compared to the latch shown in the following figure.

3. Grasp the SFP module and carefully slide it out of the slot.

4. Cover the optical port with the optical port plug.

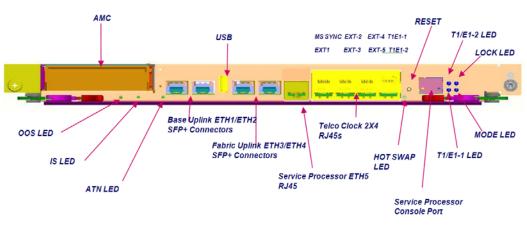

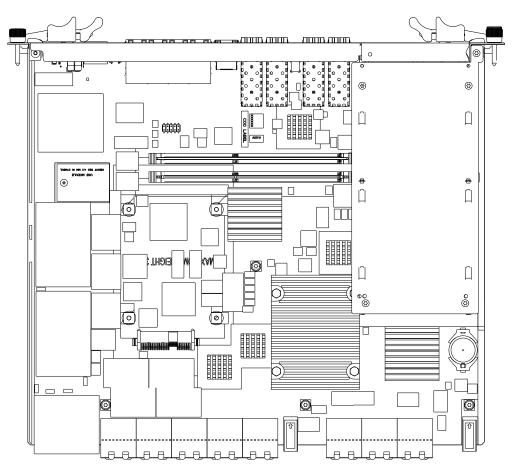

# 3.1 Overview

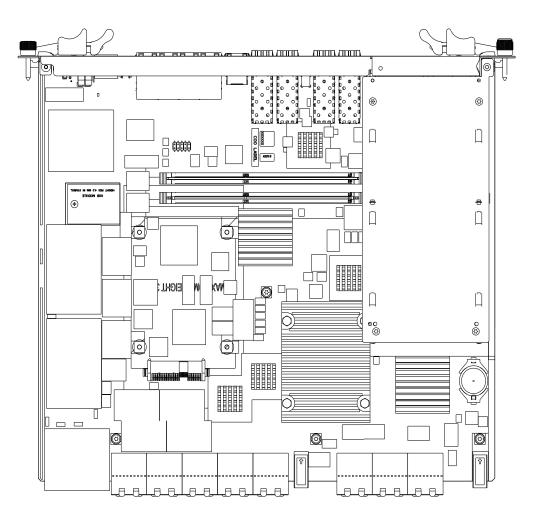

# 3.2 Blade Layout

The following figure shows the front panel face plate design.

# 3.3 Faceplate LEDs

This section describes the details of the ATCA-F125 faceplate LEDs.

| Table 3-1 | Facep  | late | LEDs |

|-----------|--------|------|------|

| Tuble 5 T | ruccpi | acc  |      |

| Label | LED            | Color | Function                                                                                                                        |

|-------|----------------|-------|---------------------------------------------------------------------------------------------------------------------------------|

| OOS   | Out of Service | Red   | This LED is enabled by the IPMC upon initially entering<br>the M4 state. Once the HPM Agent starts up, this LED<br>is disabled. |

| IS    | In Service     | Green | This LED is enabled by HPM Agent upon initialization.<br>This indicates that the payload software is up and<br>running.         |

| Label   | LED               | Color  | Function                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATN     | Attention         | Yellow | Blade attention required. This LED is controlled by higher layer software, such as middleware or applications                                                                                                                                                                                                                                                                                                                |

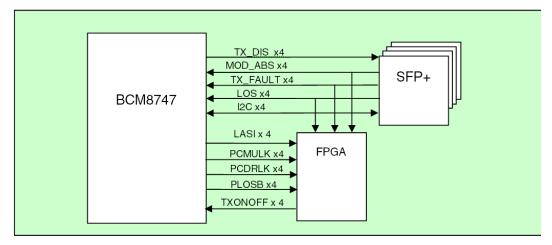

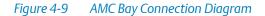

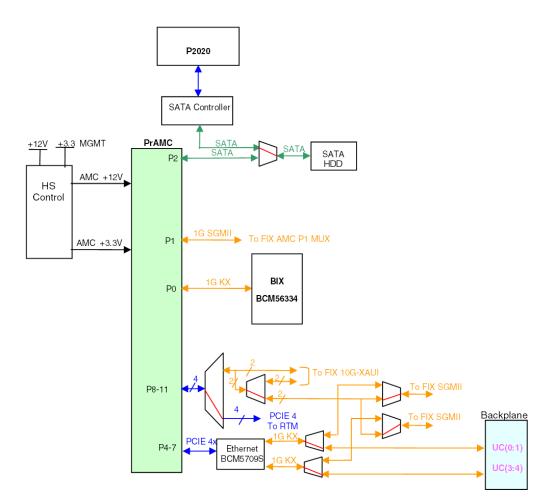

| H/S     | Hot Swap          | Blue   | <ul> <li>FRU State Machine</li> <li>During blade installation: <ul> <li>Permanently blue: On-board IPMC powered up</li> <li>Blinking blue: Blade communicating with shelf manager</li> <li>OFF: Blade is active</li> </ul> </li> <li>During blade removal: <ul> <li>Blinking blue: Blade notifies shelf manager of its desire to deactivate</li> <li>Permanently blue: Blade is ready to be extracted</li> </ul> </li> </ul> |