# Three-PLL General Purpose EPROM Programmable Clock Generator

#### **Features**

- Three integrated phase-locked loops

- EPROM programmability

- Factory-programmable (CY2291) or field-programmable (CY2291F) device options

- Low-skew, low-jitter, high-accuracy outputs

- Power-management options (Shutdown, OE, Suspend)

- Frequency select option

- Smooth slewing on CPUCLK

- Configurable 3.3 V or 5 V operation

- 20-pin SOIC Package

## **Functional Description**

The CY2291 is a third-generation family of clock generators. The CY2291 is upwardly compatible with the industry standard ICD2023 and ICD2028 and continues their tradition by providing a high level of customizable features to meet the diverse clock synchronous systems.

All parts provide a highly configurable set of close for PC motherboard applications. Each of four configurable clock outputs (CLKA-CLKD) can be assigned 1 of 30 frequencies in any combination. Multiple outputs configured for the same or related[3] frequencies have low (<500 ps) skew, in effect providing on-chip buffering for heavily loaded signals.

The CY2291 can be configured for either 5 V or 3.3 V operation. The internal ROM tables use EPROM technology, allowing full customization of output frequencies. The reference oscillator has been designed for 10 MHz to 25 MHz crystals, providing additional flexibility. No external components are required with this crystal. Alternatively, an external reference clock of frequency between 1 MHZ to 30 MHz can be used. Customers using the 32 kHz oscillator must connect a 10-M $\Omega$  resistor in parallel with the 32 kHz crystal.

For a complete list of related documentation, click here.

#### Selection Guide

Downloaded from Arrow.com.

| Part Number | t Number Outputs Input Frequency Range |     | Output Frequency Range | Specifics                                    |

|-------------|----------------------------------------|-----|------------------------|----------------------------------------------|

| CY2291      |                                        | ` , |                        | Factory programmable Commercial temperature  |

| CY2291F     | 8                                      | ` , | ` ,                    | Field programmable<br>Commercial temperature |

**Cypress Semiconductor Corporation** 198 Champion Court Document Number: 38-07189 Rev. \*K Revised May 31, 2017

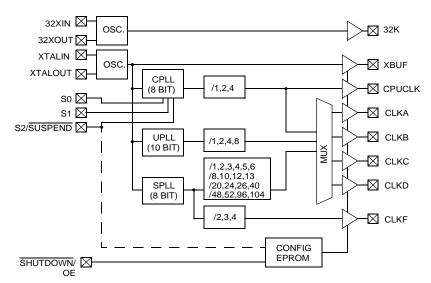

## **Logic Block Diagram**

## **Contents**

| Pinouts                                | 4 |

|----------------------------------------|---|

| Pin Definitions                        | 4 |

| Functional Overview                    | 5 |

| Output Configuration                   | 5 |

| Power Saving Features                  | 5 |

| CyClocks Software                      |   |

| Cypress FTG Programmer                 |   |

| Custom Configuration Request Procedure |   |

| Maximum Ratings                        | 6 |

| Operating Conditions                   | 6 |

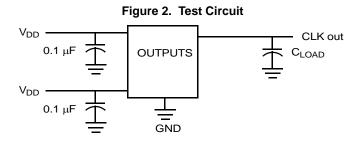

| Test Circuit                           |   |

| Electrical Characteristics             |   |

| Electrical Characteristics             | 7 |

| Switching Characteristics              | 8 |

| Switching Characteristics              |   |

| Switching Waveforms                    |   |

| Ordering information                    | 11         |

|-----------------------------------------|------------|

| Possible Configurations                 | <b>1</b> 1 |

| Ordering Code Definitions               | <b>1</b> 1 |

| Packaging Information                   | 12         |

| Package Characteristics                 | 12         |

| Package Diagram                         | 12         |

| Acronyms                                |            |

| Document Conventions                    | 13         |

| Units of Measure                        | 13         |

| Document History Page                   | 14         |

| Sales, Solutions, and Legal Information | 16         |

| Worldwide Sales and Design Support      |            |

| Products                                | 16         |

| PSoC® Solutions                         | 16         |

| Cypress Developer Community             |            |

| Technical Support                       |            |

## **Pinouts**

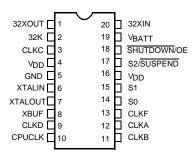

Figure 1. 20-pin SOIC pinout

## **Pin Definitions**

| Name                      | Pin Number | Description                                                                                                                                                                            |

|---------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32XOUT <sup>[1]</sup>     | 1          | 32.768-kHz crystal feedback.                                                                                                                                                           |

| 32K                       | 2          | 32.768-kHz output (always active if VBATT is present).                                                                                                                                 |

| CLKC                      | 3          | Configurable clock output C.                                                                                                                                                           |

| VDD                       | 4, 16      | Voltage supply.                                                                                                                                                                        |

| GND                       | 5          | Ground.                                                                                                                                                                                |

| XTALIN <sup>[2]</sup>     | 6          | Reference crystal input or external reference clock input.                                                                                                                             |

| XTALOUT <sup>[2, 3]</sup> | 7          | Reference crystal feedback.                                                                                                                                                            |

| XBUF                      | 8          | Buffered reference clock output.                                                                                                                                                       |

| CLKD                      | 9          | Configurable clock output D.                                                                                                                                                           |

| CPUCLK                    | 10         | CPU frequency clock output.                                                                                                                                                            |

| CLKB                      | 11         | Configurable clock output B.                                                                                                                                                           |

| CLKA                      | 12         | Configurable clock output A.                                                                                                                                                           |

| CLKF                      | 13         | Configurable clock output F.                                                                                                                                                           |

| S0                        | 14         | CPU clock select input, bit 0.                                                                                                                                                         |

| S1                        | 15         | CPU clock select input, bit 1.                                                                                                                                                         |

| S2/SUSPEND                | 17         | CPU clock select input, bit 2. Optionally enables suspend feature when LOW.                                                                                                            |

| SHUTDOWN/OE               | 18         | Places outputs in three-state $^{[4]}$ condition and shuts down chip when LOW. Optionally, only places outputs in three-state $^{[4]}$ condition and does not shut down chip when LOW. |

| VBATT <sup>[1]</sup>      | 19         | Battery supply for 32.768-kHz circuit.                                                                                                                                                 |

| 32XIN <sup>[1]</sup>      | 20         | 32.768 kHz crystal input.                                                                                                                                                              |

#### Notes

- 1. If power is applied to VBATT, then a watch crystal (32.768 KHz) must be connected to the 32XIN and 32XOUT pins.

2. For best accuracy, use a parallel-resonant crystal, C<sub>LOAD</sub> ≈ 17 pF or 18 pF.

3. Float XTALOUT pin if XTALIN is driven by reference clock (as opposed to crystal).

- 4. The CY2291 has weak pull downs on all outputs (except 32K). Hence, when a three-state condition is forced on the outputs, the output pins are pulled LOW.

#### **Functional Overview**

## **Output Configuration**

The CY2291 has five independent frequency sources on-chip. These are the 32-kHz oscillator, the reference oscillator, and three Phase-locked loops (PLLs). Each PLL has a specific function. The System PLL (SPLL) drives the CLKF output and provides fixed output frequencies on the configurable outputs. The SPLL offers the most output frequency divider options. The CPU PLL (CPLL) is controlled by the select inputs (S0–S2) to provide eight user-selectable frequencies with smooth slewing between frequencies. The Utility PLL (UPLL) provides the most accurate clock. It is often used for miscellaneous frequencies not provided by the other frequency sources.

All configurations are EPROM programmable, providing short sample and production lead times.

### **Power Saving Features**

The SHUTDOWN/OE input three-states the outputs when pulled LOW (the 32-kHz clock output is not affected). If system shutdown is enabled, a LOW on this pin also shuts off the PLLs, counters, the reference oscillator, and all other active components. The resulting current on the  $V_{DD}$  pins are less than 50  $\mu A$  plus 15  $\mu A$  max. for the 32-kHz subsystem and is typically 10  $\mu A$ . After leaving shutdown mode, the PLLs have to re-lock. All outputs except 32K have a weak pull down so that the outputs do not float when three-stated.  $^{[4]}$

The S2/SUSPEND input can be configured to shut down a customizable set of outputs and/or PLLs, when LOW. All PLLs and any of the outputs except 32K can be shut off in nearly any combination. The only limitation is that if a PLL is shut off, all outputs derived from it must also be shut off. Suspending a PLL shuts off all associated logic, while suspending an output simply forces a three-state condition<sup>[3]</sup>.

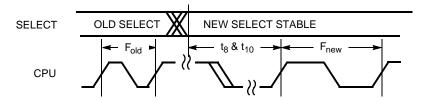

The CPUCLK can slew (transition) smoothly between 8 MHz and the maximum output frequency (100 MHz at 5V/80 MHz at 3.3 V for commercial temp. parts). This feature is extremely useful in "Green" PC and laptop applications, where reducing the frequency of operation can result in considerable power savings. This feature meets all 486 and Pentium® processor slewing requirements.

#### CyClocks Software

CyClocks™ is an easy-to-use application that allows you to configure any one of the EPROM programmable clocks offered by Cypress. You may specify the input frequency, PLL and output frequencies, and different functional options. Please note the output frequency ranges in this data sheet when specifying them in CyClocks to ensure that you stay within the limits. CyClocks also has a power calculation feature that allows you to see the power consumption of your specific configuration. CyClocks is a sub-application within the CyberClocks™ software. You can download a copy of CyberClocks for free on Cypress's web site at www.cypress.com.

## **Cypress FTG Programmer**

The Cypress frequency timing generator (FTG) Programmers is a portable programmer designed to custom program our family of EPROM field programmable clock devices. The FTG programmers connect to a PC serial port and allow users of CyClocks software to quickly and easily program any of the CY2291F, CY2292F, CY2071AF, and CY2907F devices. The ordering code for the Cypress FTG Programmer is CY3670.

### **Custom Configuration Request Procedure**

The CY229x are EPROM-programmable devices that may be configured in the factory or in the field by a Cypress Field Application Engineer (FAE). The output frequencies requested are matched as closely as the internal PLL divider and multiplier options allow. All custom requests must be submitted to your local Cypress FAE or sales representative. The method to use to request custom configurations is:

Use CyClocks™ software. This software automatically calculates the output frequencies that can be generated by the CY229x devices and provides a print-out of final pinout which can be submitted (in electronic or print format) to your local FAE or sales representative. The CyClocks software is available free of charge from the Cypress web site (http://www.cypress.com) or from your local sales representative.

Once the custom request has been processed you receive a part number with a 3-digit extension (for example, CY2292SC-128) specific to the frequencies and pinout of your device. This is the part number used for samples requests and production orders.

Document Number: 38-07189 Rev. \*K Page 5 of 16

## **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. These user guidelines are not tested.

Supply voltage .....-0.5 V to + 7.0 V DC input voltage .....-0.5 V to + 7.0 V

| Storage temperature                                     | −65 °C to +150 °C |

|---------------------------------------------------------|-------------------|

| Maximum soldering temperature (10 sec)                  | 260 °C            |

| Junction temperature                                    | 150 °C            |

| Package power dissipation                               | 750 mW            |

| Static discharge voltage (per MIL-STD-883, Method 3015) | ≥ 2000 V          |

## **Operating Conditions**

| Parameter <sup>[5]</sup>         | Description                                                                                   | Part Numbers   | Min  | Max  | Unit |

|----------------------------------|-----------------------------------------------------------------------------------------------|----------------|------|------|------|

| $V_{DD}$                         | Supply voltage, 5.0 V operation                                                               | All            | 4.5  | 5.5  | V    |

| $V_{DD}$                         | Supply voltage, 3.3 V operation                                                               | All            | 3.0  | 3.6  | V    |

| V <sub>BATT</sub> <sup>[1]</sup> | Battery backup voltage                                                                        | All            | 2.0  | 5.5  | V    |

| T <sub>A</sub>                   | Commercial operating temperature, ambient                                                     | CY2291/CY2291F | 0    | +70  | °C   |

| C <sub>LOAD</sub>                | Max. load capacitance 5.0 V operation                                                         | All            | _    | 25   | pF   |

| C <sub>LOAD</sub>                | Max. load capacitance 3.3 V operation                                                         | All            | _    | 15   | pF   |

| £                                | External reference crystal                                                                    | All            | 10.0 | 25.0 | MHz  |

| † <sub>REF</sub>                 | External reference clock [6, 7, 8]                                                            | All            | 1    | 30   | MHz  |

| t <sub>PU</sub>                  | Power-up time for all VDDs to reach minimum specified voltage (power ramps must be monotonic) |                |      | 50   | ms   |

## **Test Circuit**

- 5. Electrical parameters are guaranteed by design with these operating conditions, unless otherwise noted.

6. External input reference clock must have a duty cycle between 40% and 60%, measured at V<sub>DD</sub>/2.

- Refer to the White Paper "Crystal Parameters Recommendation for Cypress Frequency Synthesizers" for information on AC-coupling the external input reference clock.

The oscillator circuit is optimized for a crystal reference and for external reference clocks up to 20 MHz. For external reference clocks above 20 MHz, it is recommended that a 150Ω pull up resistor to V<sub>DD</sub> be connected to the XTALOUT pin.

## **Electrical Characteristics**

Commercial, 5.0 V

| Parameter          | Description                                                           | Conditions                                                    | Min                     | Тур | Max | Unit |

|--------------------|-----------------------------------------------------------------------|---------------------------------------------------------------|-------------------------|-----|-----|------|

| V <sub>OH</sub>    | HIGH-level output voltage                                             | I <sub>OH</sub> = 4.0 mA                                      | 2.4                     | -   | _   | V    |

| V <sub>OL</sub>    | LOW-level output voltage                                              | I <sub>OL</sub> = 4.0 mA                                      | _                       | _   | 0.4 | V    |

| V <sub>OH-32</sub> | 32.768-kHz HIGH-level output voltage                                  | I <sub>OH</sub> = 0.5 mA                                      | V <sub>BATT</sub> × 0.5 | -   | -   | V    |

| V <sub>OL-32</sub> | 32.768-kHz LOW-level output voltage                                   | I <sub>OL</sub> = 0.5 mA                                      | -                       | -   | 0.4 | V    |

| V <sub>IH</sub>    | HIGH-level input voltage <sup>[9]</sup>                               | Except crystal pins                                           | 2.0                     | _   | -   | V    |

| V <sub>IL</sub>    | LOW-level input voltage <sup>[9]</sup>                                | Except crystal pins                                           | _                       | _   | 0.8 | V    |

| I <sub>IH</sub>    | Input HIGH current                                                    | $V_{IN} = V_{DD} - 0.5 \text{ V}$                             | _                       | <1  | 10  | μΑ   |

| I <sub>IL</sub>    | Input LOW current                                                     | V <sub>IN</sub> = +0.5 V                                      | -                       | <1  | 10  | μΑ   |

| I <sub>OZ</sub>    | Output leakage current                                                | Three-state outputs                                           | _                       | _   | 250 | μА   |

| I <sub>DD</sub>    | V <sub>DD</sub> supply current commercial <sup>[10]</sup>             | V <sub>DD</sub> = V <sub>DD</sub> Max., 5 V operation         | -                       | 75  | 100 | mA   |

| I <sub>DDS</sub>   | V <sub>DD</sub> power supply current in shutdown mode <sup>[10]</sup> | Shutdown active, excluding V <sub>BATT</sub> CY2291 / CY2291F | _                       | 10  | 50  | μА   |

| I <sub>BATT</sub>  | V <sub>BATT</sub> power supply current                                | V <sub>BATT</sub> = 3.0 V                                     | _                       | 5   | 15  | μΑ   |

## **Electrical Characteristics**

Commercial, 3.3 V

| Parameter          | Description                                                           | Conditions                                                    | Min                      | Тур | Max | Unit |

|--------------------|-----------------------------------------------------------------------|---------------------------------------------------------------|--------------------------|-----|-----|------|

| V <sub>OH</sub>    | HIGH-level output voltage                                             | I <sub>OH</sub> = 4.0 mA                                      | 2.4                      | _   | _   | V    |

| V <sub>OL</sub>    | LOW-level output voltage                                              | I <sub>OL</sub> = 4.0 mA                                      | _                        | _   | 0.4 | V    |

| V <sub>OH-32</sub> | 32.768-kHz HIGH-level output voltage                                  | I <sub>OH</sub> = 0.5 mA                                      | V <sub>BATT</sub><br>0.5 | _   | _   | V    |

| V <sub>OL-32</sub> | 32.768-kHz LOW-level output voltage                                   | I <sub>OL</sub> = 0.5 mA                                      | -                        | _   | 0.4 | V    |

| V <sub>IH</sub>    | HIGH-level input voltage <sup>[9]</sup>                               | Except crystal pins                                           | 2.0                      | _   | -   | V    |

| V <sub>IL</sub>    | LOW-level input voltage <sup>[9]</sup>                                | Except crystal pins                                           | _                        | _   | 0.8 | V    |

| I <sub>IH</sub>    | Input HIGH current                                                    | $V_{IN} = V_{DD} - 0.5 \text{ V}$                             | _                        | <1  | 10  | μΑ   |

| I <sub>IL</sub>    | Input LOW current                                                     | V <sub>IN</sub> = +0.5 V                                      | _                        | <1  | 10  | μА   |

| l <sub>oz</sub>    | Output leakage current                                                | Three-state outputs                                           | _                        | _   | 250 | μА   |

| I <sub>DD</sub>    | V <sub>DD</sub> supply current <sup>[10]</sup> commercial             | $V_{DD} = V_{DD}$ Max., 3.3 V operation                       | _                        | 50  | 65  | mA   |

| I <sub>DDS</sub>   | V <sub>DD</sub> power supply current in shutdown mode <sup>[10]</sup> | Shutdown active, excluding V <sub>BATT</sub> CY2291 / CY2291F | _                        | 10  | 50  | μА   |

| I <sub>BATT</sub>  | V <sub>BATT</sub> power supply current                                | V <sub>BATT</sub> = 3.0 V                                     | _                        | 5   | 15  | μΑ   |

Document Number: 38-07189 Rev. \*K Page 7 of 16

Notes

9. Xtal inputs have CMOS thresholds.

10. Load = Max., V<sub>IN</sub> = 0 V or V<sub>DD</sub>, Typical (-104) configuration, CPUCLK = 66 MHz. Other configurations vary. Power can be approximated by the following formula (multiply by 0.65 for 3 V operation): I<sub>DD</sub> = 10 + (0.06 × (F<sub>CPLL</sub> + F<sub>UPLL</sub> + (2 × F<sub>SPLL</sub>))) + (0.27 × (F<sub>CLKA</sub> + F<sub>CLKB</sub> + F<sub>CLKC</sub> + F<sub>CLKD</sub> + F<sub>CPUCLK</sub> + F<sub>CLKF</sub> + F<sub>XBUF</sub>)).

## **Switching Characteristics**

Commercial, 5.0 V

| Parameter        | Name                              | Description                                                                             | on                                                                                                                          | Min              | Тур    | Max                   | Unit   |

|------------------|-----------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------|--------|-----------------------|--------|

| t <sub>1</sub>   | Output period                     | Clock output range,                                                                     | CY2291                                                                                                                      | 10<br>(100 MHz)  | _      | 13000<br>(76.923 kHz) | ns     |

| 1                | Cutput period                     | 5 V operation                                                                           | CY2291F                                                                                                                     | 11.1<br>(90 MHz) | _      | 13000<br>(76.923 kHz) | ns     |

|                  | Output duty cycle <sup>[11]</sup> | Duty cycle for output defined as $t_2 \div t_1^{[12]}$ $f_{OUT} \ge 66 \text{ MHz}$     | S,                                                                                                                          | 40%              | 50%    | 60%                   | _      |

|                  | Sulput duty syste                 | Duty cycle for output<br>defined as $t_2 \div t_1^{[12]}$<br>$f_{OUT} < 66 \text{ MHz}$ | S,                                                                                                                          | 45%              | 50%    | 55%                   | _      |

| t <sub>3</sub>   | Rise time                         | Output clock rise tim                                                                   | e <sup>[13]</sup>                                                                                                           | _                | 3      | 5                     | ns     |

| t <sub>4</sub>   | Fall time                         | Output clock fall time                                                                  | <u>,</u> [13]                                                                                                               | _                | 2.5    | 4                     | ns     |

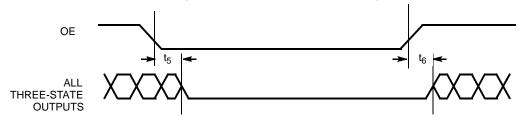

| t <sub>5</sub>   | Output disable time               | three-state mode after                                                                  | Time for output to enter three-state mode after SHUTDOWN/OE goes LOW                                                        |                  | 10     | 15                    | ns     |

| t <sub>6</sub>   | Output enable time                | Time for output to leave three-state mode after SHUTDOWN/OE goes HIGH                   |                                                                                                                             | _                | 10     | 15                    | ns     |

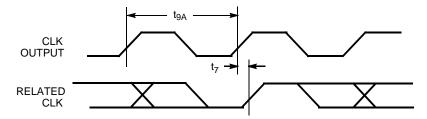

| t <sub>7</sub>   | Skew                              | Skew delay between identical or related o                                               | any<br>utputs <sup>[12, 14]</sup>                                                                                           | _                | < 0.25 | 0.5                   | ns     |

| t <sub>8</sub>   | CPUCLK Slew                       | Frequency transition                                                                    | rate                                                                                                                        | 1.0              | _      | 20.0                  | MHz/ms |

| t <sub>9A</sub>  | Clock jitter <sup>[15]</sup>      |                                                                                         | Peak-to-peak period jitter (t <sub>9A</sub><br>Max. – t <sub>9A</sub> min.),% of clock period<br>(f <sub>OUT</sub> < 4 MHz) |                  | < 0.5  | 1                     | %      |

| t <sub>9B</sub>  | Clock jitter <sup>[15]</sup>      | Max. – t <sub>9B</sub> min.)                                                            | Peak-to-peak period jitter (t <sub>9B</sub>                                                                                 |                  | < 0.7  | 1                     | ns     |

| t <sub>9C</sub>  | Clock jitter <sup>[15]</sup>      | Peak-to-peak period jitter<br>(16 MHz < f <sub>OUT</sub> ≤ 50 MHz)                      |                                                                                                                             | -                | < 400  | 500                   | ps     |

| t <sub>9D</sub>  | Clock jitter <sup>[15]</sup>      | Peak-to-peak period jitter (f <sub>OUT</sub> > 50 MHz)                                  |                                                                                                                             | _                | < 250  | 350                   | ps     |

| t <sub>10A</sub> | Lock time for CPLL                | Lock Time from Power-up                                                                 |                                                                                                                             | 1                | < 25   | 50                    | ms     |

| t <sub>10B</sub> | Locktime for UPLL and SPLL        | Lock Time from Pow                                                                      | er-up                                                                                                                       | 1                | < 0.25 | 1                     | ms     |

|                  | Slew limits                       | CPU PLL Slew limits                                                                     | CY2291                                                                                                                      | 8                | _      | 100                   | MHz    |

|                  | Olow millio                       | Of O I LE GIEW IIIIIIGS                                                                 | CY2291F                                                                                                                     | 8                | -      | 90                    | MHz    |

Notes

11. XBUF duty cycle depends on XTALIN duty cycle.

12. Measured at 1.4 V.

13. Measured between 0.4V and 2.4 V.

14. CLKF is not guaranteed to be in phase with CLKA-D, even if it is referenced off the same PLL.

15. Jitter varies with configuration. All standard configurations sample tested at the factory conform to this limit. For more information on jitter, refer to the White Paper: "Datasheet Jitter Specifications for Cypress Timing Products".

## **Switching Characteristics**

Commercial, 3.3 V

| Parameter        | Name                              | Description                                                                                         |                                                                      | Min              | Тур    | Max                   | Unit   |

|------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------|--------|-----------------------|--------|

|                  | Output period                     | Clock output range,                                                                                 | CY2291                                                               | 12.5<br>(80 MHz) | -      | 13000<br>(76.923 kHz) | ns     |

|                  | Output period                     | 3.3 V operation                                                                                     | CY2291F                                                              | 15<br>(66.6 MHz) | _      | 13000<br>(76.923 kHz) | ns     |

| t <sub>1</sub>   | Output duty cycle <sup>[16]</sup> | Duty cycle for output defined as $t_2 \div t_1^{[17]}$ $f_{OUT} \ge 66 \text{ MHZ}$                 | ts,                                                                  | 40%              | 50%    | 60%                   | _      |

|                  | Output duty cycle                 | Duty cycle for output<br>defined as $t_2 \div t_1^{[17]}$<br>$f_{OUT} < 66 \text{ MHZ}$             | ts,                                                                  | 45%              | 50%    | 55%                   | _      |

| t <sub>3</sub>   | Rise time                         | Output clock rise tim                                                                               | e <sup>[18]</sup>                                                    | _                | 3      | 5                     | ns     |

| t <sub>4</sub>   | Fall time                         | Output clock fall time                                                                              | [18]                                                                 | -                | 2.5    | 4                     | ns     |

| t <sub>5</sub>   | Output disable time               | three-state mode aft                                                                                | Time for output to enter three-state mode after SHUTDOWN/OE goes LOW |                  | 10     | 15                    | ns     |

| t <sub>6</sub>   | Output enable time                | Time for output to leave three-state mode after SHUTDOWN/OE goes HIGH                               |                                                                      | -                | 10     | 15                    | ns     |

| t <sub>7</sub>   | Skew                              | Skew delay betweer identical or related o                                                           | any<br>utputs <sup>[17, 19]</sup>                                    | _                | < 0.25 | 0.5                   | ns     |

| t <sub>8</sub>   | CPUCLK Slew                       | Frequency transition                                                                                | rate                                                                 | 1.0              | _      | 20.0                  | MHz/ms |

| t <sub>9A</sub>  | Clock jitter <sup>[20]</sup>      | Peak-to-peak period (t <sub>9A</sub> Max. – t <sub>9A</sub> min.) % of clock period (f <sub>C</sub> | ,                                                                    | -                | < 0.5  | 1                     | %      |

| t <sub>9B</sub>  | Clock jitter <sup>[20]</sup>      | Peak-to-peak period ( $t_{9B}$ Max. – $t_{9B}$ min.) (4 MHz $\leq$ $t_{OUT} \leq$ 16 I              | •                                                                    | -                | < 0.7  | 1                     | ns     |

| t <sub>9C</sub>  | Clock jitter <sup>[20]</sup>      | Peak-to-peak period jitter<br>(16 MHz < f <sub>OUT</sub> ≤ 50 MHz)                                  |                                                                      | -                | < 400  | 500                   | ps     |

| t <sub>9D</sub>  | Clock jitter <sup>[20]</sup>      | Peak-to-peak period jitter<br>(f <sub>OUT</sub> > 50 MHz)                                           |                                                                      | -                | < 250  | 350                   | ps     |

| t <sub>10A</sub> | Lock time for CPLL                | Lock time from power-up                                                                             |                                                                      | -                | < 25   | 50                    | ms     |

| t <sub>10B</sub> | Lock time for UPLL and SPLL       | Lock time from power                                                                                | er-up                                                                | -                | < 0.25 | 1                     | ms     |

|                  | Slew limits                       | CPU PLL slew limits                                                                                 | CY2291                                                               | 8<br>8           | -      | 80                    | MHz    |

|                  | Olew mines                        | OI OI LE SIEW IIIIIIG                                                                               | CY2291F                                                              |                  | _      | 66.6                  | MHz    |

<sup>16.</sup> XBUF duty cycle depends on XTALIN duty cycle. 17. Measured at 1.4 V.

<sup>17.</sup> Measured at 1.4 v.

18. Measured between 0.4 V and 2.4 V.

19. CLKF is not guaranteed to be in phase with CLKA-D, even if it is referenced off the same PLL.

20. Jitter varies with configuration. All standard configurations sample tested at the factory conform to this limit. For more information on jitter, refer to the White Paper: "Datasheet Jitter Specifications for Cypress Timing Products".

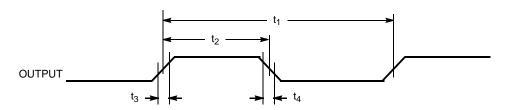

## **Switching Waveforms**

Figure 3. All Outputs, Duty Cycle and Rise/Fall Time

Figure 4. Output Three-State Timing [21]

Figure 5. CLK Outputs Jitter and Skew

Figure 6. CPU Frequency Change

Note

<sup>21.</sup> The CY2291 has weak pull downs on all outputs (except 32K). Hence, when a three-state condition is forced on the outputs, the output pins are pulled LOW.

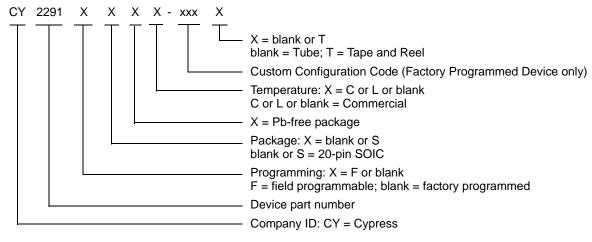

## **Ordering Information**

| Ordering Code | Package Type                | Operating Range | Operating Voltage |

|---------------|-----------------------------|-----------------|-------------------|

| Pb-free       |                             |                 |                   |

| CY2291FX      | 20-pin SOIC                 | Commercial      | 3.3 V or 5.0 V    |

| CY2291FXT     | 20-pin SOIC – Tape and reel | Commercial      | 3.3 V or 5.0 V    |

Some product offerings are factory programmed customer specific devices with customized part numbers. The Possible Configurations table shows the available device types, but not complete part numbers. Contact your local Cypress FAE of Sales Representative for more information.

## **Possible Configurations**

| Ordering Code  | Package Type                | Operating Range | Operating Voltage |

|----------------|-----------------------------|-----------------|-------------------|

| Pb-free        |                             |                 |                   |

| CY2291SXC-xxx  | 20-pin SOIC                 | Commercial      | 5.0 V             |

| CY2291SXC-xxxT | 20-pin SOIC – Tape and Reel | Commercial      | 5.0 V             |

| CY2291SXL-xxx  | 20-pin SOIC                 | Commercial      | 3.3 V             |

| CY2291SXL-xxxT | 20-pin SOIC – Tape and Reel | Commercial      | 3.3 V             |

## **Ordering Code Definitions**

Document Number: 38-07189 Rev. \*K Page 11 of 16

## **Packaging Information**

## **Package Characteristics**

| Ī | Parameter <sup>[22]</sup> | Description                              | Test Conditions                                                 | 20-pin SOIC | Unit |

|---|---------------------------|------------------------------------------|-----------------------------------------------------------------|-------------|------|

|   | $\theta_{JA}$             | Thermal resistance (junction to ambient) | Test conditions follow standard test methods and procedures for | 73          | °C/W |

|   | $\theta$ JC               | Thermal resistance (junction to case)    | measuring thermal impedance, in accordance with EIA/JESD51.     | 38          | °C/W |

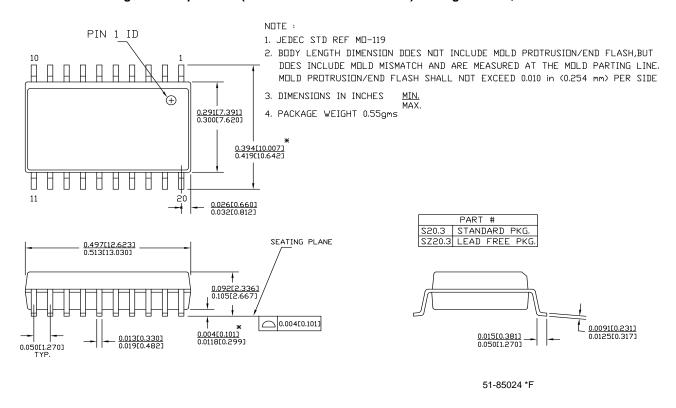

## **Package Diagram**

Figure 7. 20-pin SOIC (0.513 × 0.300 × 0.0932 Inches) Package Outline, 51-85024

## Note

22. These parameters are guaranteed by design and are not tested.

Document Number: 38-07189 Rev. \*K Page 12 of 16

## **Acronyms**

Table 1. Acronyms Used in this Document

| Acronym | Description                             |

|---------|-----------------------------------------|

| CLKIN   | Clock Input                             |

| CMOS    | complementary Metal Oxide Semiconductor |

| OE      | Output Enable                           |

| PLL     | Phase Locked Loop                       |

| SPLL    | System Phase Locked Loop                |

| PPM     | Parts Per Million                       |

| FTG     | Frequency Time Generator                |

| FAE     | Field Application Engineer              |

## **Document Conventions**

## **Units of Measure**

Table 2. Units of Measure

| Symbol | Unit of Measure   |

|--------|-------------------|

| °C     | degrees Celsius   |

| fF     | femtofarad        |

| KB     | 1024 bytes        |

| Kbit   | 1024 bits         |

| kHz    | kilohertz         |

| MHz    | megahertz         |

| ΜΩ     | megaohm           |

| μΑ     | microampere       |

| μF     | microfarad        |

| μH     | microhenry        |

| μs     | microsecond       |

| μV     | microvolt         |

| mA     | milliampere       |

| ms     | millisecond       |

| nA     | nanoampere        |

| ns     | nanosecond        |

| nV     | nanovolt          |

| рА     | picoampere        |

| pF     | picofarad         |

| рр     | peak-to-peak      |

| ppm    | parts per million |

| ps     | picosecond        |

# **Document History Page**

| Document Title: CY2291, Three-PLL General Purpose EPROM Programmable Clock Generator Document Number: 38-07189 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision                                                                                                       | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| **                                                                                                             | 110321  | SZV                | 10/28/01           | Change from Spec number: 38-00410 to 38-07189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *A                                                                                                             | 121836  | RBI                | 12/14/02           | Updated Operating Conditions:<br>Added t <sub>PU</sub> parameter and its details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| *B                                                                                                             | 276756  | RGL                | 10/18/04           | Updated Ordering Information:<br>Updated part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *C                                                                                                             | 2565316 | AESA / KVM         | 09/16/08           | Updated Functional Overview: Updated CyClocks Software: Updated description. Updated Ordering Information: Updated part numbers. Replaced "Lead-Free" with "Pb-Free". Added Note "Not recommended for new designs." and referred the same note in "CY2291FI". Updated Packaging Information: Updated Package Diagram: spec 51-85024 – Changed revision from *B to *C. Updated to new template.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *D                                                                                                             | 2898985 | KVM                | 03/25/2010         | Updated Ordering Information: Updated part numbers. Removed Note "Not recommended for new designs." and its reference. Added Possible Configurations (for "xxx" parts). Added Note "Some product offerings are factory programmed customer specific devices with customized part numbers. The Possible Configurations table shows the available device types, but not complete part numbers. Contact your local Cypress FAE or Sales Representative for more information." and referred the same note in "Ordering Code" column in Possible Configurations. Updated Package Diagram: spec 51-85024 – Changed revision from *C to *D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *E                                                                                                             | 3080949 | BASH               | 11/10/2010         | Removed Benefits. Added Functional Description. Updated Functional Overview: Removed Operation. Added Acronyms and Units of Measure. Updated to new template.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *F                                                                                                             | 3450141 | PURU               | 01/12/2011         | Updated Pin Definitions: Added Note 1 and referred the same note in 32XOUT pin. Removed Note "Please refer to application note "Understanding the CY2291, CY2292 and CY2295" for more information." and its reference. Updated Switching Characteristics: Removed Note "Please refer to application note "Understanding the CY2291, CY2292 and CY2295" for more information." and its reference. Updated Switching Characteristics: Removed Note "Please refer to application note "Understanding the CY2291, CY2292 and CY2295" for more information." and its reference. Updated Switching Characteristics: Removed Note "Please refer to application note "Understanding the CY2291, CY2292 and CY2295" for more information." and its reference. Updated Switching Characteristics: Removed Note "Please refer to application note "Understanding the CY2291, CY2292 and CY2295" for more information." and its reference. Updated Switching Characteristics: Removed Note "Please refer to application note "Understanding the CY2291, CY2292 and CY2295" for more information." and its reference. Updated Packaging Information: Updated Package Characteristics: Changed value of $\theta_{\rm JC}$ parameter from 125 °C/W to 70 °C/W. Changed value of $\theta_{\rm JC}$ parameter from 25 °C/W to 46 °C/W. |

| *G                                                                                                             | 3849272 | PURU               | 12/21/2012         | Removed "Understanding the CY2291 and CY2292" application note related information in all instances across the document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Document Number: 38-07189 Rev. \*K

## **Document History Page** (continued)

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                      |

|----------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *H       | 4201345 | CINM               | 11/25/2013         | Updated Packaging Information: Updated Package Diagram: spec 51-85024 – Changed revision from *D to *E. Updated to new template. Completing Sunset Review.                                                                 |

| *        | 4576237 | XHT                | 11/21/2014         | Updated Functional Description: Added "For a complete list of related documentation, click here." at the end. Updated Packaging Information: Updated Package Diagram: spec 51-85024 – Changed revision from *E to *F.      |

| *J       | 5528179 | XHT                | 11/21/2016         | Updated to new template. Completing Sunset Review.                                                                                                                                                                         |

| *K       | 5754889 | PSR                | 05/31/2017         | Updated Cypress logo, Copyright information, and Sales page. Updated Packaging Information. Delete all Industrial range references in the datasheet. Updated Selection Guide, Packaging Information, Operating Conditions. |

Document Number: 38-07189 Rev. \*K Page 15 of 16

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers

Automotive

Clocks & Buffers

Interface

Internet of Things

cypress.com/arm

cypress.com/automotive

cypress.com/clocks

cypress.com/interface

cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

## PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

## **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2001-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.