## **Dual Narrow/Wideband RF Transceiver**

**Preliminary Technical Data**

# ADRV9002

#### **FEATURES**

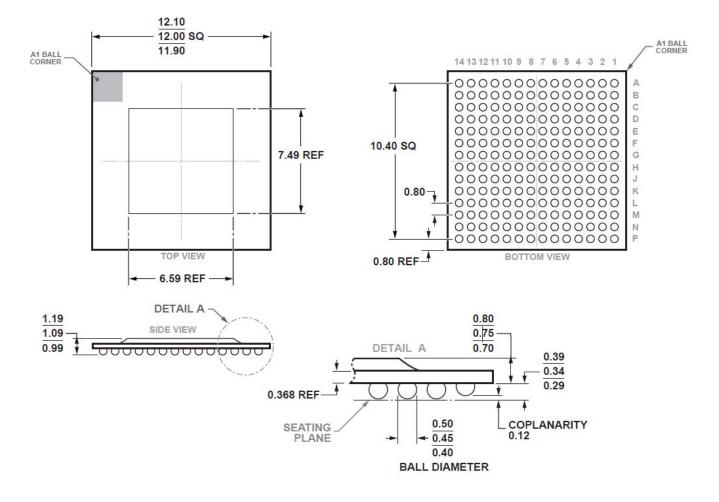

2 × 2 highly integrated transceiver Frequency range of 30 MHz to 6000 MHz Transmitter and receiver bandwidth up to 40 MHz Fully integrated, fractional-N, RF synthesizers LVDS and CSSI Low power monitor and sleep modes Multichip synchronization capabilities FFH Dynamic profile switching for dynamic data rates and sample rates Fully integrated DPD for narrowband and wideband waveforms Fully programmable via a 4-wire SPI 12 mm × 12 mm, 196-ball CSP\_BGA

#### APPLICATIONS

Mission critical communications Very high frequency (VHF), ultrahigh frequency (UHF), and cellular to 6 GHz Time division duplexing (TDD) and frequency division

Time division duplexing (TDD) and frequency division duplexing (FDD) applications

#### **GENERAL DESCRIPTION**

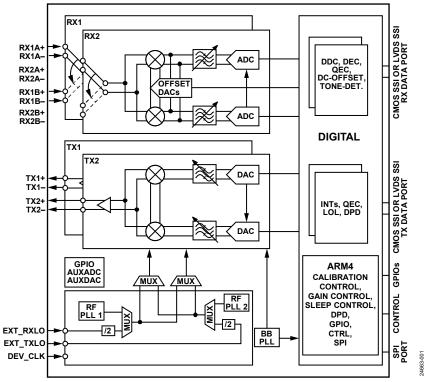

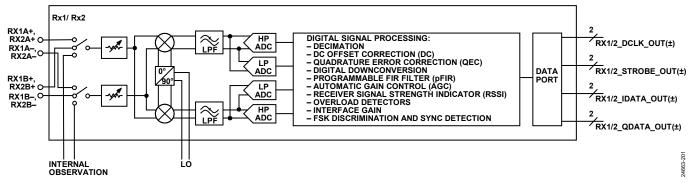

The ADRV9002 is a highly integrated, RF transceiver that has dual-channel transmitters, dual-channel receivers, integrated synthesizers, and digital signal processing functions.

The IC delivers a versatile combination of high performance and low power consumption required by battery powered radio equipment and can operate in both FDD and TDD modes. The ADRV9002 operates from 30 MHz to 6000 MHz and covers the UHF, VHF, licensed and unlicensed cellular bands, and industrial, scientific, and medical (ISM) bands. The IC can support both narrowband and wideband standards up to 40 MHz bandwidth on both receive and transmit. The transceiver consists of direct conversion signal paths with state of the art noise figure and linearity. Each complete receiver and transmitter subsystem includes dc offset correction, quadrature error correction, and programmable digital filters, which eliminate the need for these functions in the digital baseband. In addition, several auxiliary functions such as auxiliary analog-to-digital converters (ADCs), auxiliary digital-to-analog converters (DACs), and general-purpose input/outputs (GPIOs) are integrated to provide additional monitoring and control capability.

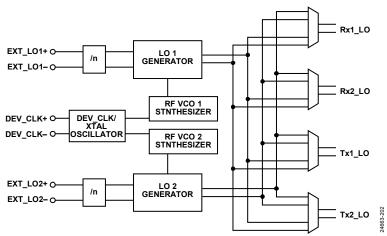

The fully integrated phase-locked loops (PLLs) provide high performance, low power, fractional-N frequency synthesis for the transmitter, receiver, and clock sections. Careful design and layout techniques provide the isolation required in high performance personal radio applications.

All voltage controlled oscillator (VCO) and loop filter components are integrated to minimize the external component count. The local oscillators (LOs) have flexible configuration options and include fast lock modes.

The transceiver includes low power sleep and monitor modes to save power and extend the battery life of portable devices while monitoring communication.

The fully integrated, low power digital predistortion (DPD) is optimized for both narrowband and wideband signals and enables linearization of high efficiency power amplifiers.

The ADRV9002 core can be powered directly from 1.0 V, 1.3 V, and 1.8 V regulators and is controlled via a standard 4-wire serial port. Other voltage supplies are used to provide proper digital interface levels and to optimize receiver, transmitter, and auxiliary converter performance.

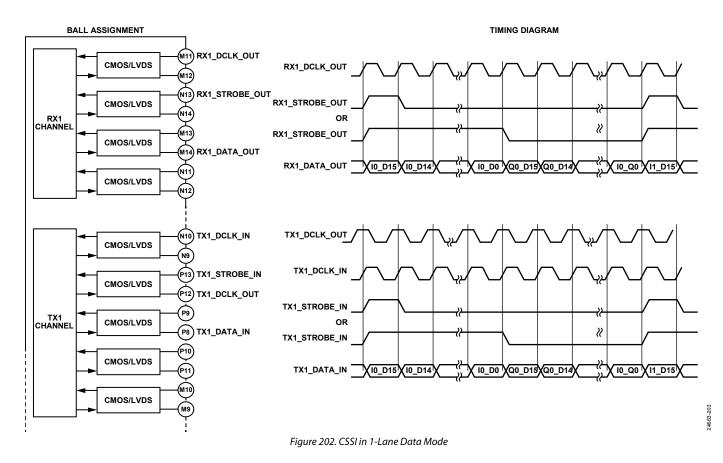

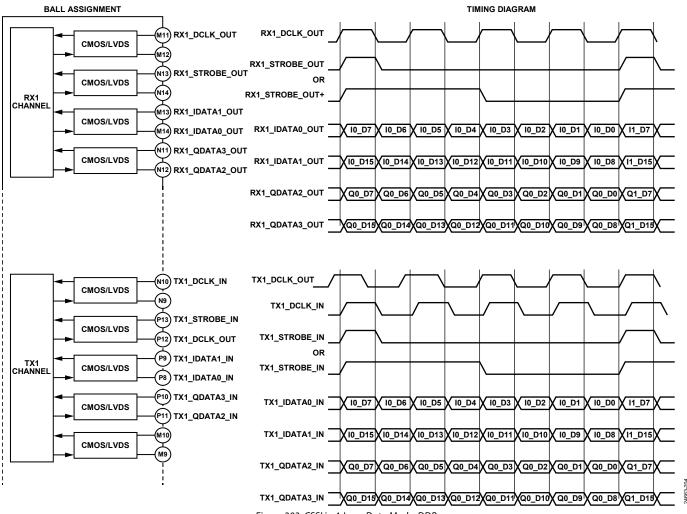

High data rate and low data rate interfaces are supported using configurable complementary metal-oxide semiconductors (CMOS) or low voltage differential signaling (LVDS) serial synchronous interface (SSI) choice. The ADRV9002 is packaged in a 12 mm  $\times$  12 mm, 196-ball chip scale package ball grid array (CSP\_BGA).

Rev. PrA

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### TABLE OF CONTENTS

| Features1                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------|

| Applications 1                                                                                                     |

| General Description                                                                                                |

| Functional Block Diagram                                                                                           |

| Specifications                                                                                                     |

| Transmitter Specifications 4                                                                                       |

| Receiver Specifications 6                                                                                          |

| Internal LO, External LO, and Device Clock                                                                         |

| Digital Interfaces and Auxiliary Converters14                                                                      |

| Power Supply Specifications                                                                                        |

| Current Consumption Estimates (Typical Values)16                                                                   |

|                                                                                                                    |

| Timing Specifications                                                                                              |

| Timing Specifications    18      Absolute Maximum Ratings    20                                                    |

|                                                                                                                    |

| Absolute Maximum Ratings                                                                                           |

| Absolute Maximum Ratings                                                                                           |

| Absolute Maximum Ratings20Reflow Profile20Thermal Resistance20                                                     |

| Absolute Maximum Ratings20Reflow Profile20Thermal Resistance20Electrostatic Discharge (ESD) Ratings20              |

| Absolute Maximum Ratings20Reflow Profile20Thermal Resistance20Electrostatic Discharge (ESD) Ratings20ESD Caution20 |

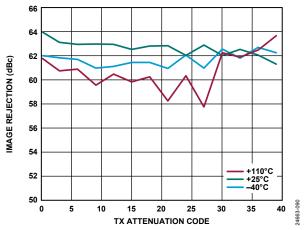

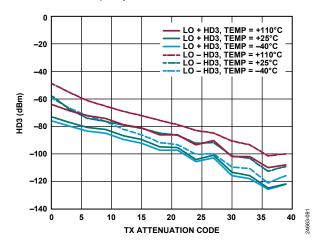

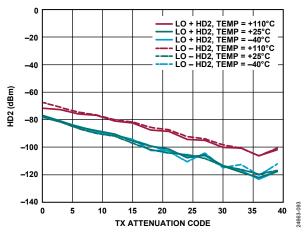

| 470 MHz Ba     | nd         | <br>   |

|----------------|------------|--------|

| 900 MHz Ba     | nd         | <br>39 |

| 2400 MHz B     | and        | <br>44 |

| 3500 MHz B     | and        | <br>49 |

| 5800 MHz B     | and        | <br>55 |

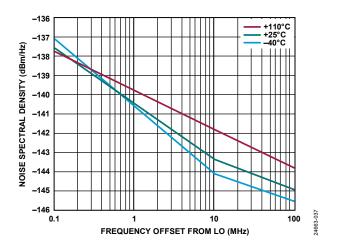

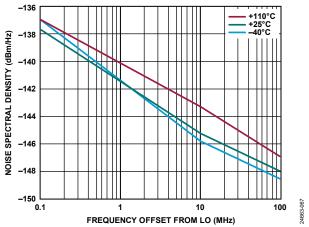

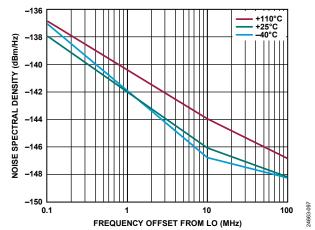

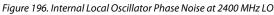

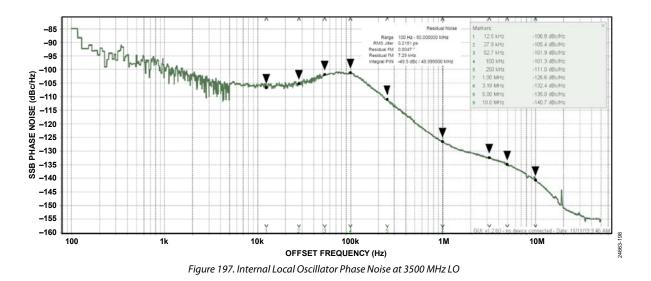

| Phase Noise    |            | <br>60 |

| Theory of Ope  | ration     | <br>62 |

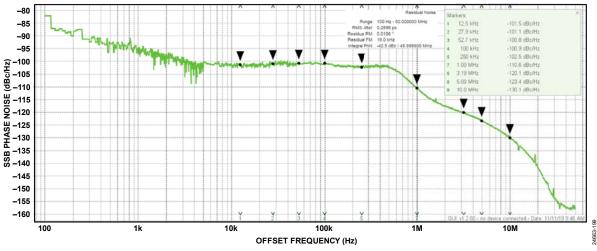

| Transmitter    |            | <br>62 |

| Receiver       |            | <br>63 |

| DPD            |            | <br>64 |

| Clock Input    |            | <br>64 |

| Synthesizers   |            | <br>64 |

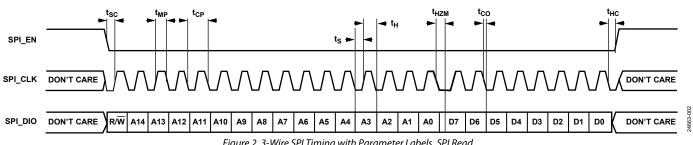

| SPI Interface  | 2          | <br>65 |

| GPIO Pins      |            | <br>65 |

| Auxillary Co   | onverters  | <br>65 |

| JTAG Bound     | lary Scan  | <br>66 |

| Applications I | nformation | <br>67 |

| Power Suppl    | y Sequence | <br>67 |

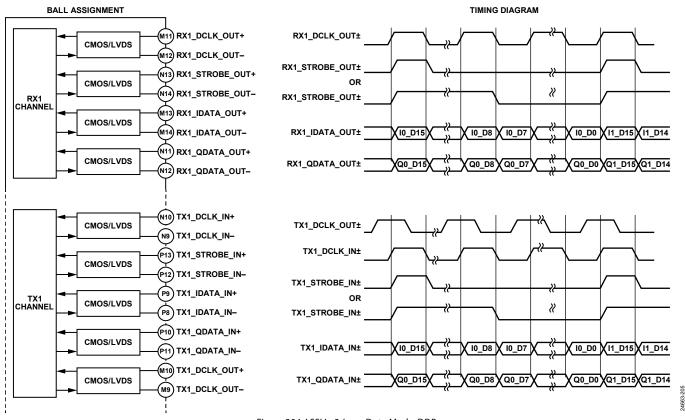

| Digital Data   | Interface  | <br>67 |

| Outline Dimen  | isions     | <br>71 |

|                |            |        |

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

Downloaded from Arrow.com.

### **SPECIFICATIONS**

Electrical characteristics are at the operating ambient temperature range,  $VDDA_1P0 = 1.0 V$ ,  $VDDA_1P3 = 1.3 V$ ,  $VDDA_1P8 = 1.8 V$ ,  $VDD_1P0 = 1.0 V$ ,  $VDD_1P8 = 1.8 V$ . The following values are not de-embedded. Refer to the Typical Performance Characteristics section for input/output circuit path loss.

#### TRANSMITTER SPECIFICATIONS

Table 1. Transmitters (Tx1 and Tx2)

| Parameter                                                  | Symbol | Min   | Тур  | Мах  | Units    | Test Conditions/Comments                                                                                                                                                                           |

|------------------------------------------------------------|--------|-------|------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CENTER FREQUENCY                                           |        | 30    |      | 6000 | MHz      |                                                                                                                                                                                                    |

| TRANSMITTER SYNTHESIS<br>BANDWIDTH                         |        | 0.012 |      | 40   | MHz      | Zero-IF mode, see the DPD section for more information.                                                                                                                                            |

| BANDWIDTH FLATNESS                                         |        |       | 0.1  |      | dB       | 10 MHz bandwidth span, including digital compensation.                                                                                                                                             |

| DEVIATION FROM LINEAR PHASE                                |        |       | 1    |      | Degree   | 40 MHz bandwidth.                                                                                                                                                                                  |

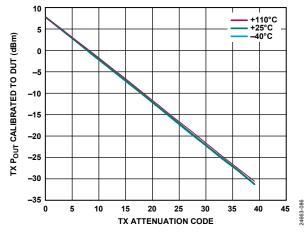

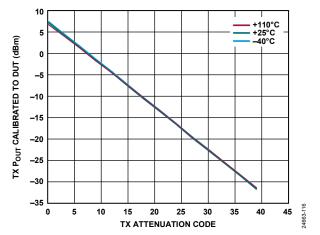

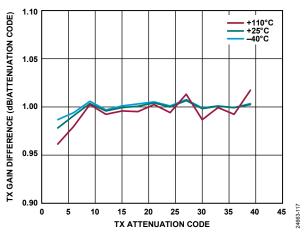

| POWER CONTROL RANGE                                        |        |       |      |      |          |                                                                                                                                                                                                    |

| IQ Mode                                                    |        |       | 42   |      | dB       | Increased calibration time, reduced QEC <sup>1</sup> , and LOL <sup>2</sup> performance beyond 20 dB.                                                                                              |

| Direct Modulation Mode                                     |        |       | 12   |      | dB       |                                                                                                                                                                                                    |

| POWER CONTROL RESOLUTION                                   |        |       |      |      |          |                                                                                                                                                                                                    |

| IQ Mode                                                    |        |       | 0.05 |      | dB       |                                                                                                                                                                                                    |

| Direct Modulation Mode                                     |        |       | 0.5  |      | dB       |                                                                                                                                                                                                    |

| IN BAND NOISE FLOOR                                        |        |       | -154 |      | dBFS³/Hz | 0 dB attenuation, in band noise falls 1 dB for each dB of attenuation for attenuation settings between 0 dB and 20 dB.                                                                             |

| OUT OF BAND NOISE FLOOR                                    |        |       | -156 |      | dBFS/Hz  | 0 dB attenuation with $3 \times$ bandwidth/2 offset.                                                                                                                                               |

| Tx1 TO Tx2 ISOLATION                                       |        |       |      |      |          |                                                                                                                                                                                                    |

| 30 MHz                                                     |        |       | 107  |      | dB       |                                                                                                                                                                                                    |

| 470 MHz                                                    |        |       | 107  |      | dB       |                                                                                                                                                                                                    |

| 900 MHz                                                    |        |       | 73   |      | dB       |                                                                                                                                                                                                    |

| 2400 MHz                                                   |        |       | 73   |      | dB       |                                                                                                                                                                                                    |

| 3500 MHz                                                   |        |       | 73   |      | dB       |                                                                                                                                                                                                    |

| 5800 MHz                                                   |        |       | 73   |      | dB       |                                                                                                                                                                                                    |

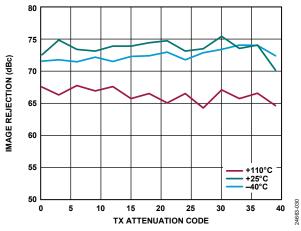

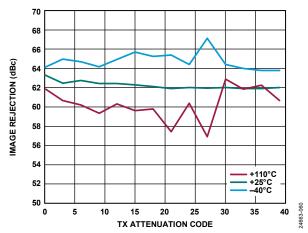

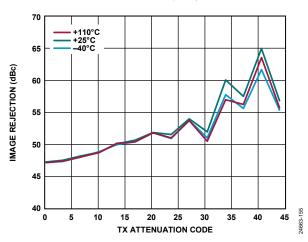

| IMAGE REJECTION WITH<br>INITIALIZATION CALIBRATION<br>ONLY |        |       |      |      |          |                                                                                                                                                                                                    |

| Wideband                                                   |        |       |      |      |          | Up to 20 dB transmitter attenuation, 10 MHz bandwidth, 0 dB observation receiver attenuation, and QEC tracking calibration is disabled.                                                            |

| 30 MHz                                                     |        |       | 67   |      | dBc      |                                                                                                                                                                                                    |

| 470 MHz                                                    |        |       | 69   |      | dBc      |                                                                                                                                                                                                    |

| 900 MHz                                                    |        |       | 67   |      | dBc      |                                                                                                                                                                                                    |

| 2400 MHz                                                   |        |       | 70   |      | dBc      |                                                                                                                                                                                                    |

| 3500 MHz                                                   |        |       | TBD  |      | dBc      |                                                                                                                                                                                                    |

| 5800 MHz                                                   |        |       | TBD  |      | dBc      |                                                                                                                                                                                                    |

| Narrow-Band                                                |        |       |      |      |          | Up to 20 dB transmitter attenuation, 100 kHz bandwidth,<br>0 dB observation receiver attenuation, and QEC tracking<br>calibration is disabled. The signal is symmetrical and<br>transmitted on LO. |

| 30 MHz                                                     |        |       | 83   |      | dBc      |                                                                                                                                                                                                    |

| 470 MHz                                                    |        |       | 85   |      | dBc      |                                                                                                                                                                                                    |

| 900 MHz                                                    |        |       | 71   |      | dBc      |                                                                                                                                                                                                    |

| 2400 MHz                                                   |        |       | 62   |      | dBc      |                                                                                                                                                                                                    |

| 3500 MHz                                                   |        |       | TBD  |      | dBc      |                                                                                                                                                                                                    |

| 5800 MHz                                                   |        |       | TBD  |      | dBc      |                                                                                                                                                                                                    |

| Parameter                                                    | Symbol | Min Ty | o Max | Units | Test Conditions/Comments                                                                                                                                                                |

|--------------------------------------------------------------|--------|--------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IMAGE REJECTION WITH                                         |        |        |       |       |                                                                                                                                                                                         |

| INITIALIZATION CALIBRATION                                   |        |        |       |       |                                                                                                                                                                                         |

| AND TRACKING CALIBRATION                                     |        |        |       |       | 0 dB transmitter attenuation 40 MHz handwidth 0.2                                                                                                                                       |

| Wideband                                                     |        |        |       |       | 0 dB transmitter attenuation, 40 MHz bandwidth, -0.2<br>dBFS, 18 MHz continuous wave <sup>4</sup> signal input, 50 Ω load, 0<br>dB observation receiver attenuation, and QEC is active. |

| 30 MHz                                                       |        | 73     |       | dBc   |                                                                                                                                                                                         |

| 470 MHz                                                      |        | 63     |       | dBc   |                                                                                                                                                                                         |

| 900 MHz                                                      |        | 64     |       | dBc   |                                                                                                                                                                                         |

| 2400 MHz                                                     |        | 65     |       | dBc   |                                                                                                                                                                                         |

| 3500 MHz                                                     |        | 48     |       | dBc   |                                                                                                                                                                                         |

| 5800 MHz                                                     |        | 48     |       | dBc   |                                                                                                                                                                                         |

| Narrow-band                                                  |        |        |       |       | Up to 20 dB transmitter attenuation, 100 kHz bandwidth,<br>0 dB observation receiver attenuation, QEC is active, and<br>the signal is symmetrical and transmitted on LO.                |

| 30 MHz                                                       |        | тво    | )     | dBc   | 5,                                                                                                                                                                                      |

| 470 MHz                                                      |        | TBL    |       | dBc   |                                                                                                                                                                                         |

| 900 MHz                                                      |        | TBL    |       | dBc   |                                                                                                                                                                                         |

| 2400 MHz                                                     |        | TBL    |       | dBc   |                                                                                                                                                                                         |

| 3500 MHz                                                     |        | ТВС    |       | dBc   |                                                                                                                                                                                         |

| 5800 MHz                                                     |        | TBI    |       | dBc   |                                                                                                                                                                                         |

| CONTINUOUS WAVE FULL-                                        |        |        |       |       | –0.2 dBFS, 18 MHz continuous wave signal input, 50 $\Omega$                                                                                                                             |

| SCALE OUTPUT POWER                                           |        |        |       |       | load, and 0 dB transmitter attenuation.                                                                                                                                                 |

| 30 MHz                                                       |        | 7.7    |       | dBm   |                                                                                                                                                                                         |

| 470 MHz                                                      |        | 7.6    |       | dBm   |                                                                                                                                                                                         |

| 900 MHz                                                      |        | 7.7    |       | dBm   |                                                                                                                                                                                         |

| 2400 MHz                                                     |        | 7.3    |       | dBm   |                                                                                                                                                                                         |

| 3500 MHz                                                     |        | 7.4    |       | dBm   |                                                                                                                                                                                         |

| 5800 MHz                                                     |        | 6.8    |       | dBm   |                                                                                                                                                                                         |

| OUTPUT IMPEDANCE                                             | Zout   | 50     |       | Ω     | Differential, see the ADRV9001 System Development User Guide for more information.                                                                                                      |

| MAXIMUM OUTPUT LOAD<br>VOLTAGE STANDING WAVE<br>RATIO (VSWR) |        |        | 3     | Ω     | Use the maximum value to ensure adequate calibration.                                                                                                                                   |

| OUTPUT RETURN LOSS                                           |        |        |       |       | Unmatched differential port return loss.                                                                                                                                                |

| 30 MHz                                                       |        | 28     |       | dB    |                                                                                                                                                                                         |

| 470 MHz                                                      |        | 24     |       | dB    |                                                                                                                                                                                         |

| 900 MHz                                                      |        | 22     |       | dB    |                                                                                                                                                                                         |

| 2400 MHz                                                     |        | 17     |       | dB    |                                                                                                                                                                                         |

| 3500 MHz                                                     |        | 10     |       | dB    |                                                                                                                                                                                         |

| 5800 MHz                                                     |        | 7      |       | dB    |                                                                                                                                                                                         |

| OUTPUT THIRD-ORDER<br>INTERCEPT POINT                        | OIP3   |        |       |       | 0 dB transmitter attenuation. continuous wave tones at 17 MHz and 18 MHz, –11 dBFS/tone, calibrated to the device.                                                                      |

| 30 MHz                                                       |        | 32     |       | dBm   |                                                                                                                                                                                         |

| 470 MHz                                                      |        | 31     |       | dBm   |                                                                                                                                                                                         |

| 900 MHz                                                      |        | 30     |       | dBm   |                                                                                                                                                                                         |

| 2400 MHz                                                     |        | 28     |       | dBm   |                                                                                                                                                                                         |

| 3500 MHz                                                     |        | 31     |       | dBm   |                                                                                                                                                                                         |

| 5800 MHz                                                     |        | 26     |       | dBm   |                                                                                                                                                                                         |

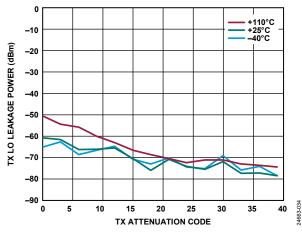

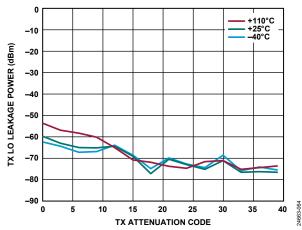

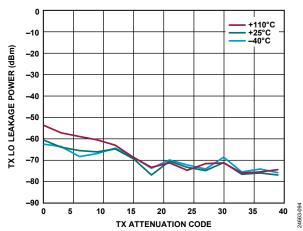

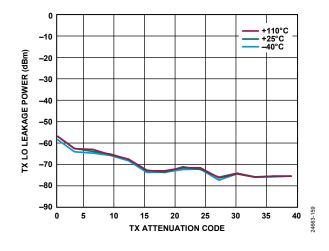

| CARRIER LEAKAGE WITH<br>INITIALIZATION CALIBRATION<br>ONLY   |        |        |       |       | LO leakage tracking calibration disabled, 0 dB transmitter attenuation, and scales dB for dB with attenuation.                                                                          |

| Wideband                                                     |        |        |       |       |                                                                                                                                                                                         |

| 30 MHz LO                                                    |        | -76    | 5     | dBFS  |                                                                                                                                                                                         |

| 470 MHz LO                                                   |        | -76    | 5     | dBFS  |                                                                                                                                                                                         |

| Parameter                                                                      | Symbol | Min Typ | Max | Units | Test Conditions/Comments                                            |

|--------------------------------------------------------------------------------|--------|---------|-----|-------|---------------------------------------------------------------------|

| 900 MHz LO                                                                     |        | -76     |     | dBFS  |                                                                     |

| 2400 MHz LO                                                                    |        | -75     |     | dBFS  |                                                                     |

| 3500 MHz LO                                                                    |        | TBD     |     | dBFS  |                                                                     |

| 5800 MHz LO                                                                    |        | TBD     |     | dBFS  |                                                                     |

| Narrow-Band                                                                    |        |         |     |       |                                                                     |

| 30 MHz LO                                                                      |        | -73     |     | dBFS  |                                                                     |

| 470 MHz LO                                                                     |        | -76     |     | dBFS  |                                                                     |

| 900 MHz LO                                                                     |        | -76     |     | dBFS  |                                                                     |

| 2400 MHz LO                                                                    |        | -70     |     | dBFS  |                                                                     |

| 3500 MHz LO                                                                    |        | TBD     |     | dBFS  |                                                                     |

| 5800 MHz LO                                                                    |        | TBD     |     | dBFS  |                                                                     |

| CARRIER LEAKAGE WITH<br>INITIALIZATION CALIBRATION<br>AND TRACKING CALIBRATION |        |         |     |       | LO leakage calibration is active with 0 dB transmitter attenuation. |

| Wideband                                                                       |        |         |     |       |                                                                     |

| 30 MHz LO                                                                      |        | -61     |     | dBm   |                                                                     |

| 470 MHz LO                                                                     |        | -60     |     | dBm   |                                                                     |

| 900 MHz LO                                                                     |        | -60     |     | dBm   |                                                                     |

| 2400 MHz LO                                                                    |        | -58     |     | dBm   |                                                                     |

| 3500 MHz LO                                                                    |        | -56     |     | dBm   |                                                                     |

| 5800 MHz LO                                                                    |        | -54     |     | dBm   |                                                                     |

| Narrow-band                                                                    |        |         |     |       |                                                                     |

| 30 MHz LO                                                                      |        | TBD     |     | dBm   |                                                                     |

| 470 MHz LO                                                                     |        | TBD     |     | dBm   |                                                                     |

| 900 MHz LO                                                                     |        | TBD     |     | dBm   |                                                                     |

| 2400 MHz LO                                                                    |        | TBD     |     | dBm   |                                                                     |

| 3500 MHz LO                                                                    |        | TBD     |     | dBm   |                                                                     |

| 5800 MHz LO                                                                    |        | TBD     |     | dBm   |                                                                     |

<sup>1</sup> Quadrature error correction (QEC) is the system for minimizing quadrature images of a desired signal. <sup>2</sup> Local oscillator leakage (LOL) is a measure of the amount of the LO signal that is passed from a mixer with the desired signal.

<sup>3</sup> dBFS represents the ratio of the actual output signal to the maximum possible output level for a continuous wave output signal at the given RF attenuation setting. <sup>4</sup> A continuous wave is a single frequency signal.

#### **RECEIVER SPECIFICATIONS**

Table 2. Receivers (Rx1A, Rx1B, Rx2A, and Rx2B)

| Parameter                              | Symbol | Min | Тур | Max  | Units | Test Conditions/Comments                                                          |

|----------------------------------------|--------|-----|-----|------|-------|-----------------------------------------------------------------------------------|

| CENTER FREQUENCY                       |        | 30  |     | 6000 | MHz   |                                                                                   |

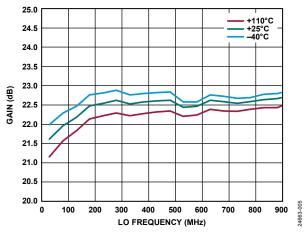

| MAXIMUM GAIN                           |        |     |     |      |       | High performance receiver ADCs, 0 dB attenuation, and 5.6 MHz baseband frequency. |

| 30 MHz                                 |        |     | 22  |      | dB    |                                                                                   |

| 470 MHz                                |        |     | 23  |      | dB    |                                                                                   |

| 900 MHz                                |        |     | 23  |      | dB    |                                                                                   |

| 2400 MHz                               |        |     | 23  |      | dB    |                                                                                   |

| 3500 MHz                               |        |     | 19  |      | dB    |                                                                                   |

| 5800 MHz                               |        |     | 18  |      | dB    |                                                                                   |

| ATTENUATION RANGE FROM<br>MAXIMUM GAIN |        |     | 36  |      | dB    |                                                                                   |

| Attenuation Accuracy                   |        |     |     |      |       |                                                                                   |

| Gain Step                              |        |     | 0.5 |      | dB    | Attenuator steps from 0 dB to 30 dB.                                              |

|                                        |        |     | TBD |      | dB    | Attenuator steps from 30 dB to 36 dB.                                             |

| Gain Step Error                        |        |     | 0.1 |      | dB    |                                                                                   |

| FREQUENCY RESPONSE                     |        |     |     |      |       |                                                                                   |

| Peak-to-Peak Gain Deviation            |        |     | 1   |      | dB    | 40 MHz bandwidth including digital compensation.                                  |

| Peak-to-Peak Gain Deviation            |        |     | 0.2 |      | dB    | Any 10 MHz span including digital compensation.                                   |

| ADRV9002 | ) |

|----------|---|

|----------|---|

| Parameter                                                | Symbol             | Min | Тур   | Max   | Units | Test Conditions/Comments                                                                                                                                                                                                     |

|----------------------------------------------------------|--------------------|-----|-------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RECEIVER BANDWIDTH                                       |                    | 12  |       | 40000 | kHz   | Zero-IF mode, the analog low-pass filter (LPF) bandwidth<br>is 5 MHz minimum, and the programmable finite impulse<br>response (FIR) filter bandwidth is configurable over the<br>entire range.                               |

| RECEIVER ALIAS BAND<br>REJECTION                         |                    | 80  |       |       | dB    | This performance is achieved because of the digital filters.                                                                                                                                                                 |

| CONTINUOUS WAVE FULL-<br>SCALE INPUT POWER <sup>1</sup>  | FSIP               |     | -11.4 |       | dBm   | This continuous wave signal level corresponds to the input<br>power at maximum gain that produces 0 dBFS at the ADC<br>output, this level increases dB for dB with attenuation.<br>Back off by at least –2 dBFS is required. |

| INPUT IMPEDANCE                                          |                    |     | 100   |       | Ω     | Differential, see the ADRV9001 System Development User Guide for more information.                                                                                                                                           |

| INPUT PORT RETURN LOSS                                   |                    |     |       |       |       | Unmatched differential port return loss, simulated.                                                                                                                                                                          |

| 30 MHz                                                   |                    |     | TBD   |       | dB    | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                        |

| 470 MHz                                                  |                    |     | 30    |       | dB    |                                                                                                                                                                                                                              |

| 900 MHz                                                  |                    |     | 25    |       | dB    |                                                                                                                                                                                                                              |

| 2400 MHz                                                 |                    |     | 18    |       | dB    |                                                                                                                                                                                                                              |

| 3500 MHz                                                 |                    |     | 15    |       | dB    |                                                                                                                                                                                                                              |

| 5800 MHz                                                 |                    |     | 14    |       | dB    |                                                                                                                                                                                                                              |

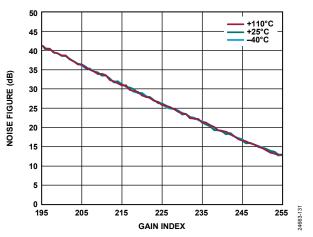

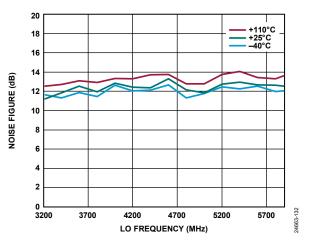

| NOISE FIGURE                                             | NF                 |     |       |       |       |                                                                                                                                                                                                                              |

| 30 MHz                                                   |                    |     | 14    |       | dB    |                                                                                                                                                                                                                              |

| 470 MHz                                                  |                    |     | 11    |       | dB    |                                                                                                                                                                                                                              |

| 900 MHz                                                  |                    |     | 11    |       | dB    | High performance receiver ADCs, 0 dB attenuation at                                                                                                                                                                          |

| 2400 MHz                                                 |                    |     | 12    |       | dB    | device under test (DUT) receive port, integrated<br>bandwidth from 8 MHz to 9 MHz.                                                                                                                                           |

| 3500 MHz                                                 |                    |     | 13    |       | dB    |                                                                                                                                                                                                                              |

| 5800 MHz                                                 |                    |     | 15    |       | dB    |                                                                                                                                                                                                                              |

| Noise Figure Ripple                                      |                    |     | 1     |       | dB    | High performance receiver ADCs at the band edge.                                                                                                                                                                             |

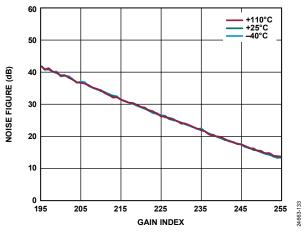

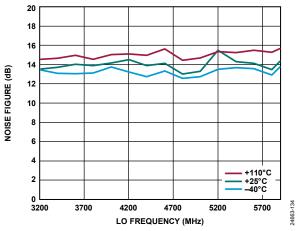

| 30 MHz                                                   |                    |     | 14    |       | dB    |                                                                                                                                                                                                                              |

| 470 MHz                                                  |                    |     | 12    |       | dB    |                                                                                                                                                                                                                              |

| 900 MHz                                                  |                    |     | 15    |       | dB    | Low power receiver ADCs, 0 dB attenuation at the DUT                                                                                                                                                                         |

| 2400 MHz                                                 |                    |     | 12    |       | dB    | receive port, integrated bandwidth from 8 MHz to 9 MHz.                                                                                                                                                                      |

| 3500 MHz                                                 |                    |     | 12    |       | dB    |                                                                                                                                                                                                                              |

| 5800 MHz                                                 |                    |     | 13    |       | dB    |                                                                                                                                                                                                                              |

| Noise Figure Ripple                                      |                    |     | 1     |       | dB    | Low power receiver ADCs at the band edge.                                                                                                                                                                                    |

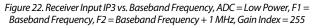

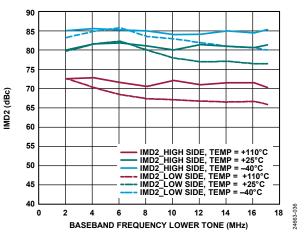

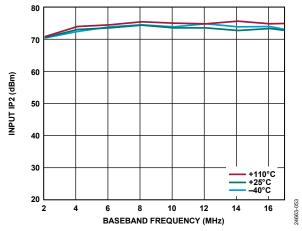

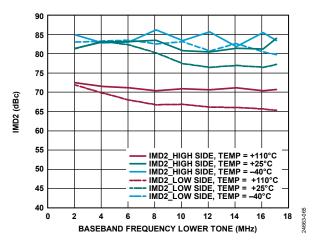

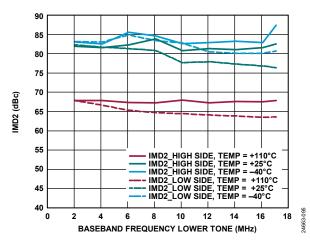

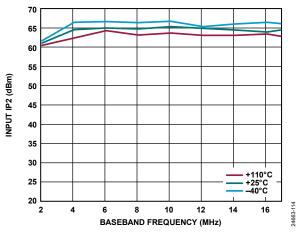

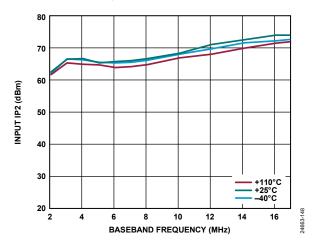

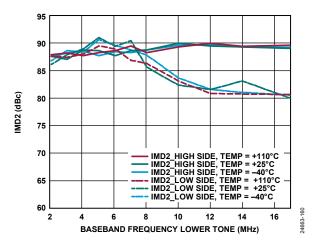

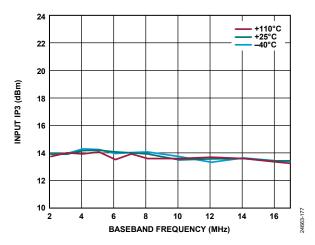

| SECOND-ORDER INPUT<br>INTERMODULATION<br>INTERCEPT POINT |                    |     |       |       |       |                                                                                                                                                                                                                              |

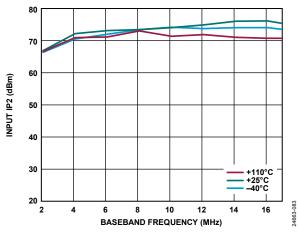

| Wideband                                                 | IIP2 <sub>WB</sub> |     |       |       |       | High performance receiver ADCs, 0 dB receiver attenuation, 1 dB cutoff frequency (f1dB) of Transimpedance Amplifier (TIA) = 20 MHz, two continuous wave tones at 17 MHz and 18 MHz, FSIP – 12 dB/tone.                       |

| 30 MHz                                                   |                    |     | 70    |       | dBm   |                                                                                                                                                                                                                              |

| 470 MHz                                                  |                    |     | 73    |       | dBm   |                                                                                                                                                                                                                              |

| 900 MHz                                                  |                    |     | 75    |       | dBm   |                                                                                                                                                                                                                              |

| 2400 MHz                                                 |                    |     | 66    |       | dBm   |                                                                                                                                                                                                                              |

| 3500 MHz                                                 |                    |     | 68    |       | dBm   |                                                                                                                                                                                                                              |

| 5800 MHz                                                 |                    |     | 66    |       | dBm   |                                                                                                                                                                                                                              |

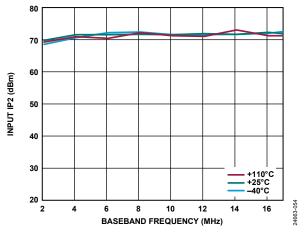

| Narrow-Band                                              | IIP2 <sub>LB</sub> |     |       |       |       | High performance receiver ADCs, 0 dB receiver<br>attenuation, f1dB of TIA = 2 MHz, two continuous wave<br>tones at 100 kHz and 150 kHz, FSIP – 12 dB/tone.                                                                   |

| 30 MHz                                                   |                    |     | 75    |       | dBm   |                                                                                                                                                                                                                              |

| 470 MHz                                                  |                    |     | 86    |       | dBm   |                                                                                                                                                                                                                              |

| 900 MHz                                                  |                    |     | 74    |       | dBm   |                                                                                                                                                                                                                              |

| 2400 MHz                                                 |                    |     | 68    |       | dBm   |                                                                                                                                                                                                                              |

Rev. PrA | Page 7 of 71

| Parameter                                                                               | Symbol                       | Min | Тур | Max | Units | Test Conditions/Comments                                                                                                                                   |

|-----------------------------------------------------------------------------------------|------------------------------|-----|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3500 MHz                                                                                |                              |     | 71  |     | dBm   |                                                                                                                                                            |

| 5800 MHz                                                                                |                              |     | 64  |     | dBm   |                                                                                                                                                            |

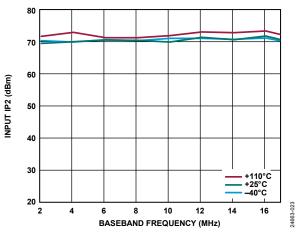

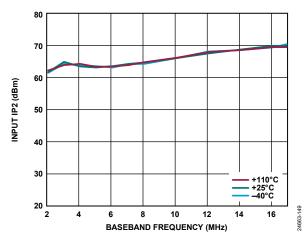

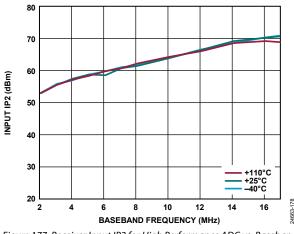

| SECOND-ORDER INPUT<br>INTERMODULATION<br>INTERCEPT POINT                                |                              |     |     |     |       |                                                                                                                                                            |

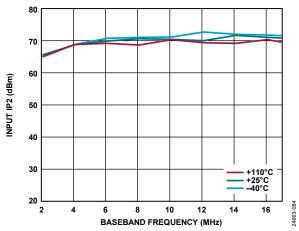

| Wideband                                                                                | IIP2 <sub>WB</sub>           |     |     |     |       | Low power receiver ADCs, 0 dB receiver attenuation, f1dB of TIA = 20 MHz, two continuous wave tones at 17 MHz and 18 MHz, FSIP – 12 dB/tone.               |

| 30 MHz                                                                                  |                              |     | 70  |     | dBm   |                                                                                                                                                            |

| 470 MHz                                                                                 |                              |     | 72  |     | dBm   |                                                                                                                                                            |

| 900 MHz                                                                                 |                              |     | 71  |     | dBm   |                                                                                                                                                            |

| 2400 MHz                                                                                |                              |     | 65  |     | dBm   |                                                                                                                                                            |

| 3500 MHz                                                                                |                              |     | 74  |     | dBm   |                                                                                                                                                            |

| 5800 MHz                                                                                |                              |     | 71  |     | dBm   |                                                                                                                                                            |

| Narrow-Band                                                                             | IIP2 <sub>LB</sub>           |     |     |     |       | Low power receiver ADCs, 0 dB receiver attenuation, f1dB of TIA = 2 MHz, two continuous wave tones at 100 kHz and 150 kHz, FSIP – 12 dB/tone.              |

| 30 MHz                                                                                  |                              |     | TBD |     | dBm   |                                                                                                                                                            |

| 470 MHz                                                                                 |                              |     | TBD |     | dBm   |                                                                                                                                                            |

| 900 MHz                                                                                 |                              |     | TBD |     | dBm   |                                                                                                                                                            |

| 2400 MHz                                                                                |                              |     | TBD |     | dBm   |                                                                                                                                                            |

| 3500 MHz                                                                                |                              |     | TBD |     | dBm   |                                                                                                                                                            |

| 5800 MHz                                                                                |                              |     | TBD |     | dBm   |                                                                                                                                                            |

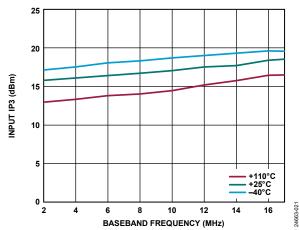

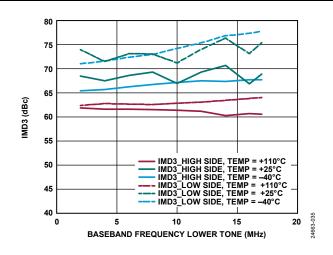

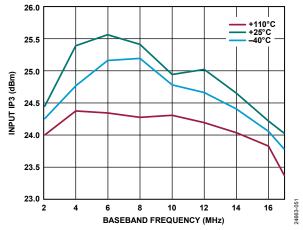

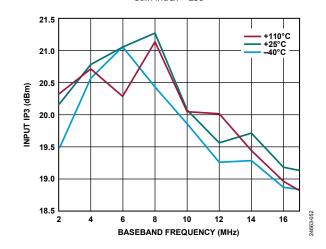

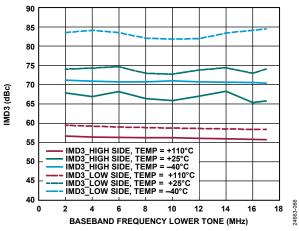

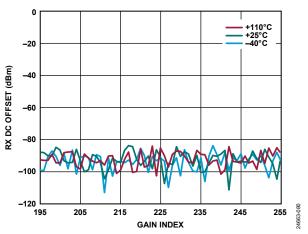

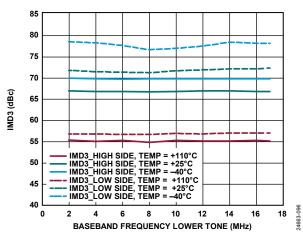

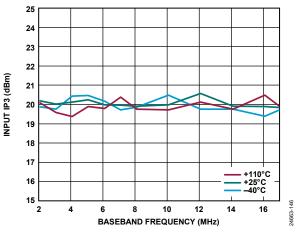

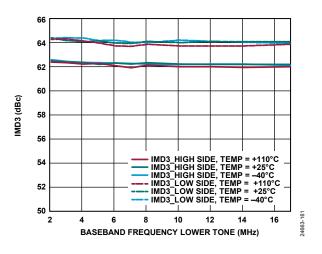

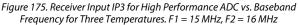

| THIRD-ORDER INPUT<br>INTERMODULATION INTERCEPT<br>POINT, DIFFERENCE PRODUCT<br>Wideband | WB –                         |     |     |     |       | High performance receiver ADCs, 0 dB receiver                                                                                                              |

| Wiccound                                                                                | IIP3 <sub>DIFF</sub>         |     |     |     |       | attenuation, f1dB of TIA = 20 MHz, two continuous wave tones at 17 MHz and 18 MHz, FSIP – 12 dB/tone.                                                      |

| 30 MHz                                                                                  |                              |     | 19  |     | dBm   |                                                                                                                                                            |

| 470 MHz                                                                                 |                              |     | 24  |     | dBm   |                                                                                                                                                            |

| 900 MHz                                                                                 |                              |     | 23  |     | dBm   |                                                                                                                                                            |

| 2400 MHz                                                                                |                              |     | 22  |     | dBm   |                                                                                                                                                            |

| 3500 MHz                                                                                |                              |     | 20  |     | dBm   |                                                                                                                                                            |

| 5800 MHz                                                                                |                              |     | 14  |     | dBm   |                                                                                                                                                            |

| Narrow-Band                                                                             | LB –<br>IIP3 <sub>DIFF</sub> |     |     |     |       | High performance receiver ADCs, 0 dB receiver<br>attenuation, f1dB of TIA = 2 MHz, two continuous wave<br>tones at 100 kHz and 150 kHz, FSIP – 12 dB/tone. |

| 30 MHz                                                                                  |                              |     | 27  |     | dBm   |                                                                                                                                                            |

| 470 MHz                                                                                 |                              |     | 24  |     | dBm   |                                                                                                                                                            |

| 900 MHz                                                                                 |                              |     | 26  |     | dBm   |                                                                                                                                                            |

| 2400 MHz                                                                                |                              |     | 25  |     | dBm   |                                                                                                                                                            |

| 3500 MHz                                                                                |                              |     | 24  |     | dBm   |                                                                                                                                                            |

| 5800 MHz                                                                                |                              |     | 21  |     | dBm   |                                                                                                                                                            |

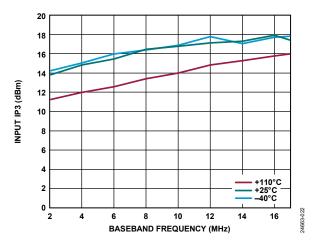

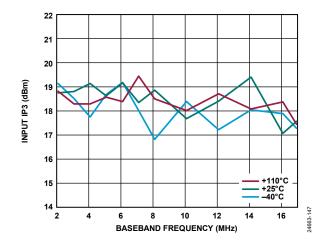

| Wideband                                                                                | WB –<br>IIP3 <sub>DIFF</sub> |     |     |     |       | Low power receiver ADCs, 0 dB receiver attenuation, f1dB of TIA = 20 MHz, two continuous wave tones at 17 MHz and 18 MHz, FSIP – 12 dB/tone.               |

| 30 MHz                                                                                  |                              |     | 17  |     | dBm   |                                                                                                                                                            |

| 470 MHz                                                                                 |                              |     | 19  |     | dBm   |                                                                                                                                                            |

| 900 MHz                                                                                 |                              |     | 19  |     | dBm   |                                                                                                                                                            |

| 2400 MHz                                                                                |                              |     | 19  |     | dBm   |                                                                                                                                                            |

| 3500 MHz                                                                                |                              |     | 15  |     | dBm   |                                                                                                                                                            |

| 5800 MHz                                                                                | 1                            |     | 15  |     | dBm   |                                                                                                                                                            |

| Parameter                           | Symbol                       | Min Ty | /p | Max | Units | Test Conditions/Comments                                                                                                                      |

|-------------------------------------|------------------------------|--------|----|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Narrow-Band                         | LB –<br>IIP3 <sub>DIFF</sub> |        |    |     |       | Low power receiver ADCs, 0 dB receiver attenuation, f1dB of TIA = 2 MHz, two continuous wave tones at 100 kHz and 150 kHz, FSIP – 12 dB/tone. |

| 30 MHz                              |                              | 20     | )  |     | dBm   |                                                                                                                                               |

| 470 MHz                             |                              | 19     | )  |     | dBm   |                                                                                                                                               |

| 900 MHz                             |                              | 18     | 3  |     | dBm   |                                                                                                                                               |

| 2400 MHz                            |                              | 15     | 5  |     | dBm   |                                                                                                                                               |

| 3500 MHz                            |                              | 14     | ŀ  |     | dBm   |                                                                                                                                               |

| 5800 MHz                            |                              | 13     |    |     | dBm   |                                                                                                                                               |

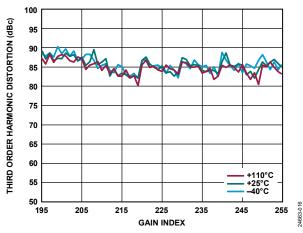

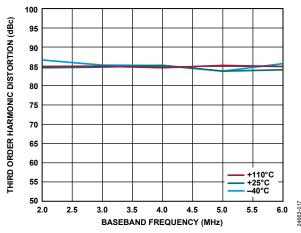

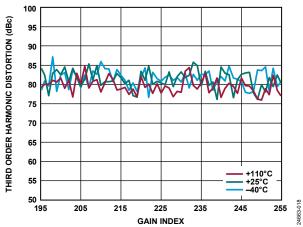

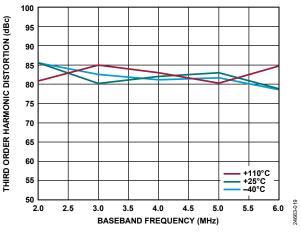

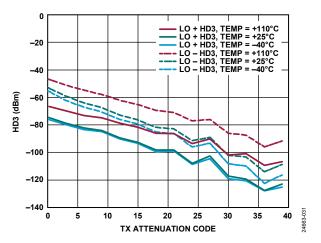

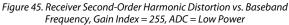

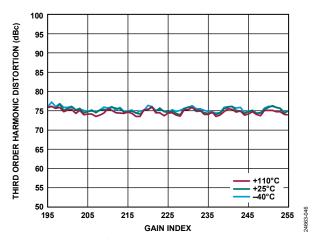

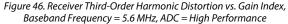

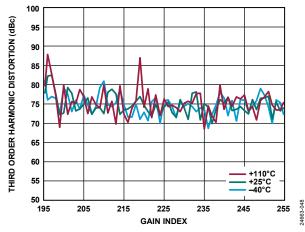

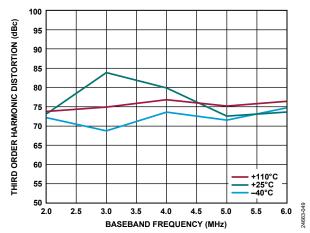

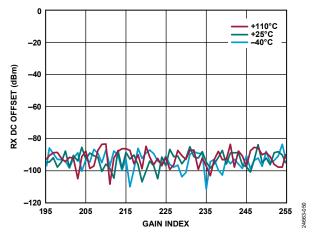

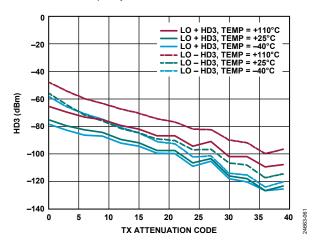

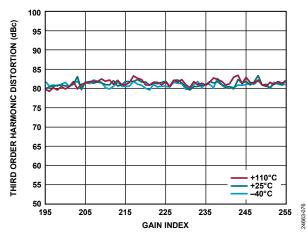

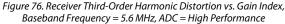

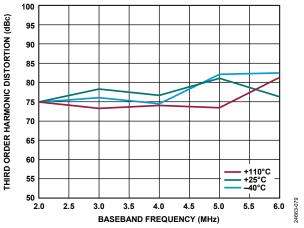

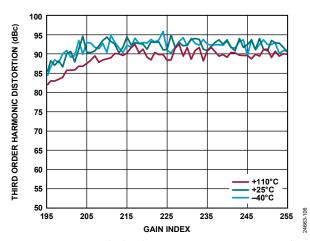

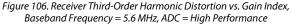

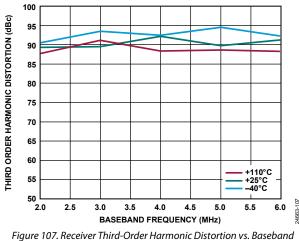

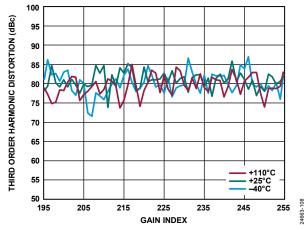

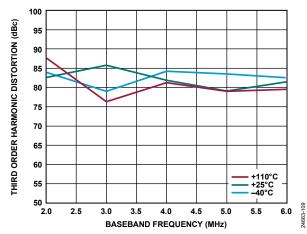

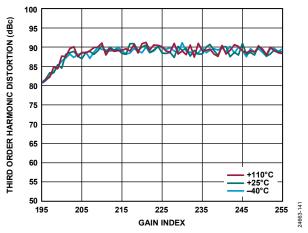

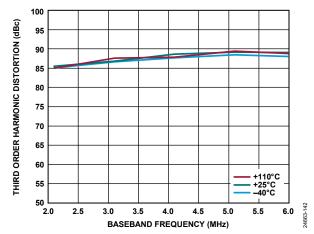

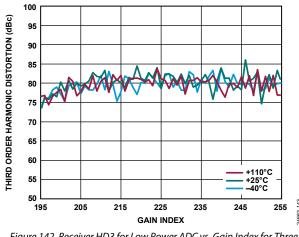

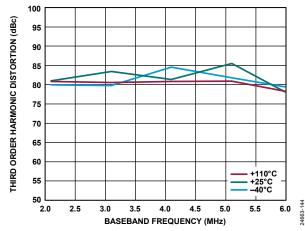

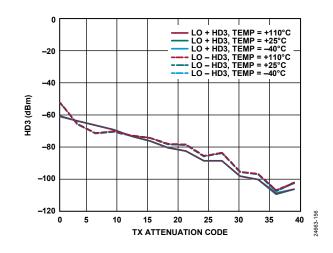

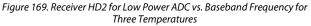

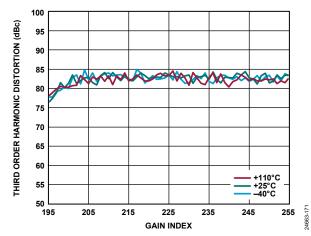

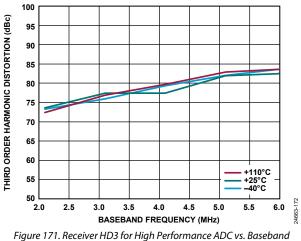

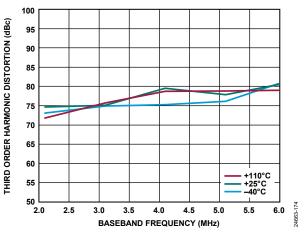

| THIRD-ORDER HARMONIC                |                              |        |    |     |       |                                                                                                                                               |

| DISTORTION                          |                              |        |    |     |       |                                                                                                                                               |

| Wideband                            | HD3 <sub>wb</sub>            |        |    |     |       | High performance receiver ADCs, FSIP – 7 dB continuous wave tone at 5.6 MHz, f1dB of TIA = 20 MHz, HD3 product at 16.8 MHz.                   |

| 30 MHz                              |                              | -8     | 35 |     | dBc   | The RF source is low-pass filtered before DUT.                                                                                                |

| 470 MHz                             |                              | -7     | 75 |     | dBc   |                                                                                                                                               |

| 900 MHz                             |                              | -8     | 32 |     | dBc   |                                                                                                                                               |

| 2400 MHz                            |                              | _9     | 90 |     | dBc   |                                                                                                                                               |

| 3500 MHz                            |                              | _9     | 90 |     | dBc   |                                                                                                                                               |

| 5800 MHz                            |                              | -8     | 39 |     | dBc   |                                                                                                                                               |

| Narrow-Band                         | HD3 <sub>LB</sub>            |        |    |     |       | High performance receiver ADCs, FSIP – 7 dB continuous wave tone at 34 kHz, f1dB of TIA = 2 MHz, HD3 product at 102 kHz.                      |

| 30 MHz                              |                              | _1     | 00 |     | dBc   |                                                                                                                                               |

| 470 MHz                             |                              | _9     | 99 |     | dBc   |                                                                                                                                               |

| 900 MHz                             |                              | _9     | 93 |     | dBc   |                                                                                                                                               |

| 2400 MHz                            |                              | _9     |    |     | dBc   |                                                                                                                                               |

| 3500 MHz                            |                              | _9     |    |     | dBc   |                                                                                                                                               |

| 5800 MHz                            |                              |        |    |     | dBc   |                                                                                                                                               |

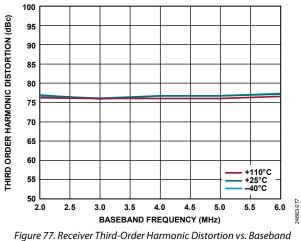

| Wideband                            | HD3 <sub>WB</sub>            |        |    |     |       | Low power receiver ADCs, FSIP – 7 dB continuous wave tone at 5.6 MHz, f1dB of TIA = 20 MHz, HD3 product at 16.8 MHz.                          |

| 30 MHz                              |                              | -8     | 30 |     | dBc   | RF source low-pass filtered before DUT.                                                                                                       |

| 470 MHz                             |                              | -7     | 74 |     | dBc   |                                                                                                                                               |

| 900 MHz                             |                              | -7     | 76 |     | dBc   |                                                                                                                                               |

| 2400 MHz                            |                              | -8     | 32 |     | dBc   |                                                                                                                                               |

| 3500 MHz                            |                              | -7     | 78 |     | dBc   |                                                                                                                                               |

| 5800 MHz                            |                              | -8     | 30 |     | dBc   |                                                                                                                                               |

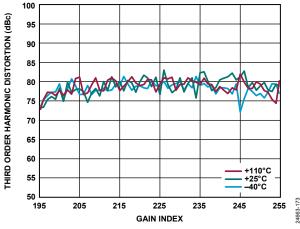

| Narrow-Band                         | HD3 <sub>LB</sub>            |        |    |     |       | Low power receiver ADCs, FSIP – 7 dB continuous wave<br>tone at 34 kHz, f1dB of TIA = 2 MHz, HD3 product at 102<br>kHz.                       |

| 30 MHz                              |                              | TE     | BD |     | dBc   |                                                                                                                                               |

| 470 MHz                             |                              | -8     |    |     | dBc   |                                                                                                                                               |

| 900 MHz                             |                              | -7     |    |     | dBc   |                                                                                                                                               |

| 2400 MHz                            |                              | -7     |    |     | dBc   |                                                                                                                                               |

| 3500 MHz                            |                              | -7     |    |     | dBc   |                                                                                                                                               |

| 5800 MHz                            |                              | -7     | 74 |     | dBc   |                                                                                                                                               |

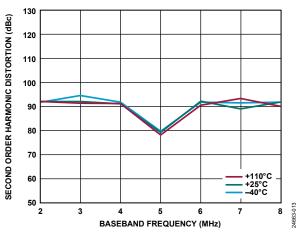

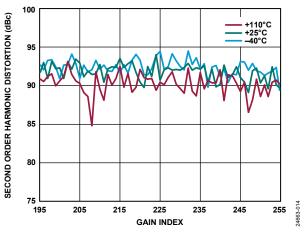

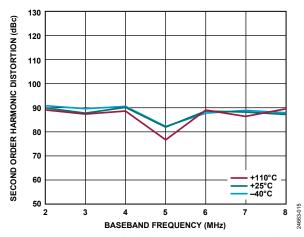

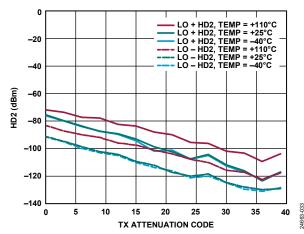

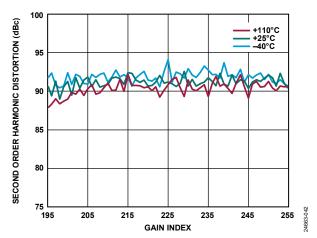

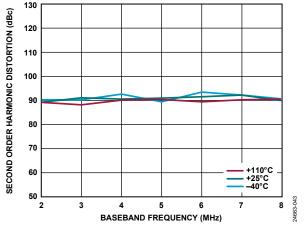

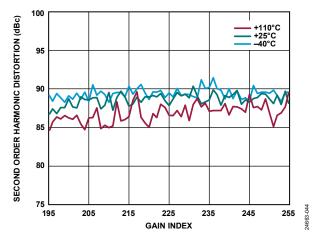

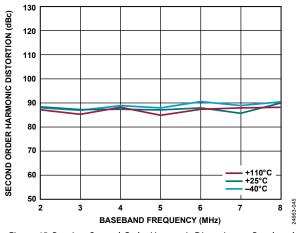

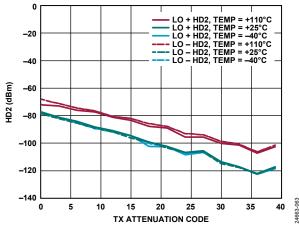

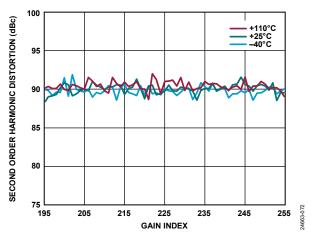

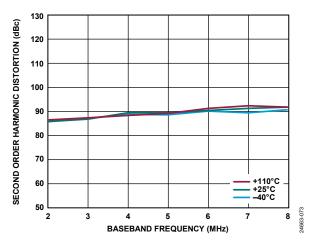

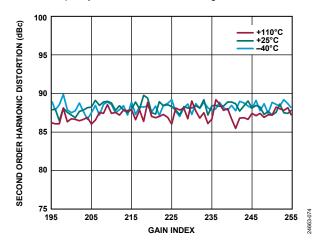

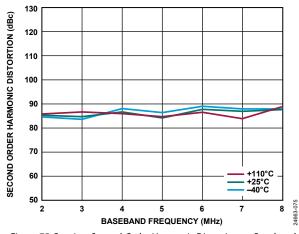

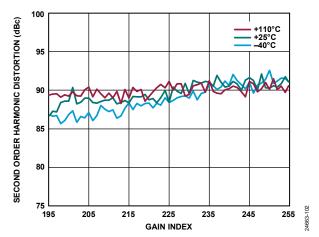

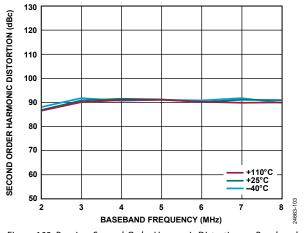

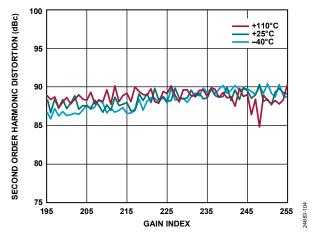

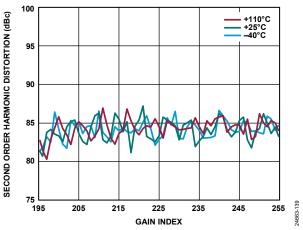

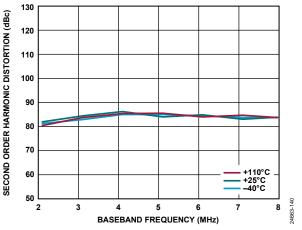

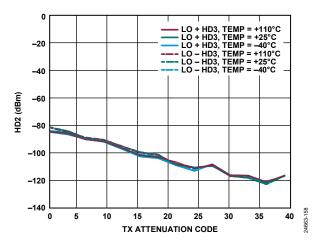

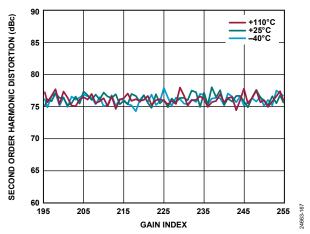

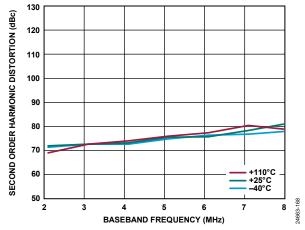

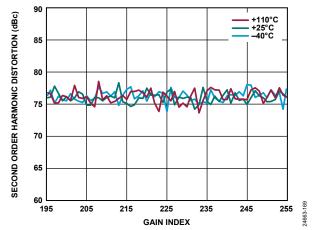

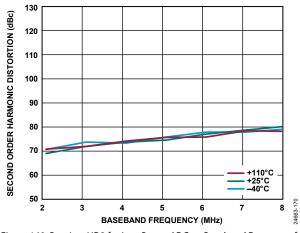

| SECOND-ORDER HARMONIC<br>DISTORTION |                              |        |    |     |       |                                                                                                                                               |

| Wideband                            | HD2 <sub>wB</sub>            |        |    |     |       | High performance receiver ADCs, FSIP – 7 dB continuous<br>wave tone at 5.6 MHz, f1dB of TIA = 20 MHz, HD2 product<br>at 11.2 MHz.             |

| 30 MHz                              |                              | _9     | 90 |     | dBc   |                                                                                                                                               |

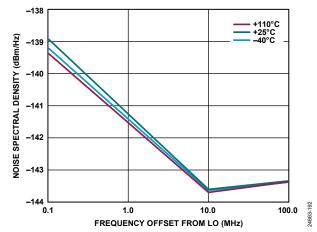

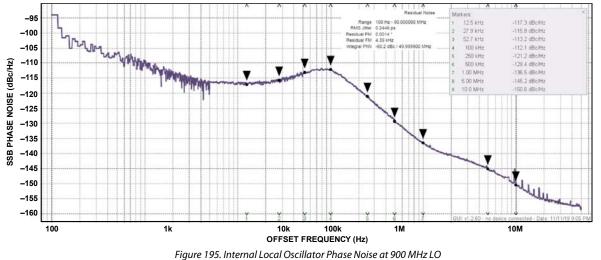

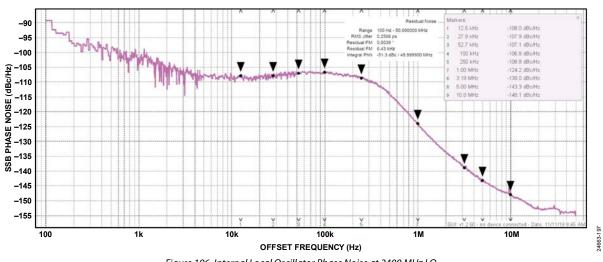

| 470 MHz                             |                              | _9     |    |     | dBc   |                                                                                                                                               |