# Quad, 16-Bit, 12 GSPS RF DAC with Wideband Channelizers

#### **FEATURES**

- ▶ Flexible, reconfigurable common platform design

- ▶ 4 DAC cores connected to various DSP and bypass datapaths

- ▶ Supports single, dual, and quad band

- ▶ Datapaths and DSP blocks are fully bypassable

- ▶ On-chip PLL with multichip synchronization

- ▶ External RFCLK input option for off-chip PLL

- ▶ Maximum DAC sample rate up to 12 GSPS

- ▶ Maximum data rate up to 12 GSPS using JESD204C

- ▶ Useable analog bandwidth to 8 GHz

- ▶ DAC ac performance at 12 GSPS

- ▶ Full-scale output current range: 6.43 mA to 37.75 mA

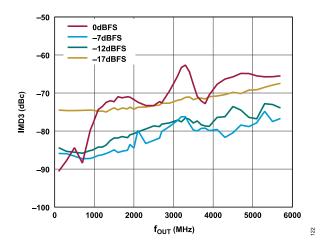

- ▶ Two-tone IMD3 (-7 dBFS per tone): -78.9 dBc

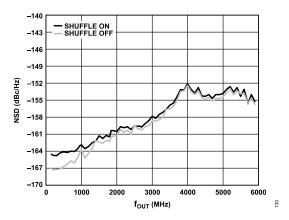

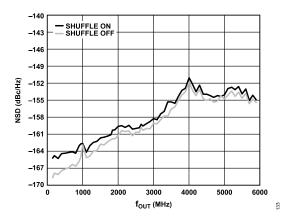

- ▶ NSD, single-tone at 3.7 GHz: -155.1 dBc/Hz

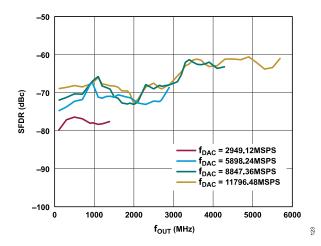

- ▶ SFDR, single-tone at 3.7 GHz: -70 dBc

- ▶ Versatile digital features

- Selectable interpolation filters

- ▶ Configurable or bypassable DUCs

- ▶ 8 fine complex DUCs and 4 coarse complex DUCs

- ▶ 48-bit NCO per DUC

- Option to bypass fine and coarse DUC

- Programmable delay per datapath

- ▶ Transmit DPD support

- ▶ Fine DUC channel gain control and delay adjust

- Auxiliary features

- ▶ Direct digital synthesis and fast frequency hopping

- Low latency loopback mode (receive datapath NCO outputs can be routed to the transmit datapaths)

- Power amplifier downstream protection circuitry

- On-chip temperature monitoring unit

- ▶ Flexible GPIO pins

- ▶ TDD power savings option

- ▶ SERDES JESD204B/JESD204C interface

- ▶ 8-lane JESD204B/C receiver (JRx)

- ▶ JESD204B compliance with the maximum 15.5 Gbps

- ▶ JESD204C compliance with the maximum 24.75 Gbps

- Supports real or complex digital data (8-, 12-, 16-, or 24-bit)

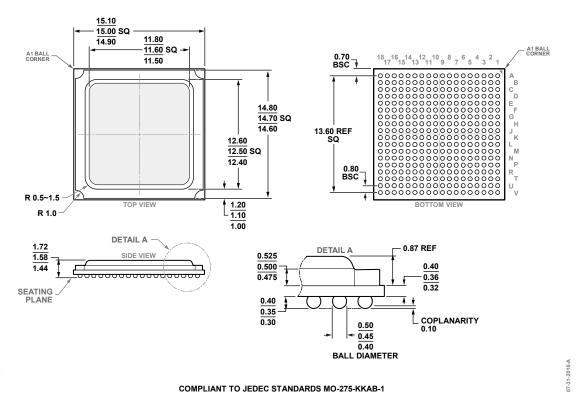

- ▶ 15 mm × 15 mm, 324-ball BGA with 0.8 mm pitch

#### **APPLICATIONS**

- ▶ Wireless communications infrastructure

- Microwave point to point, E-band and 5G mmWave

#### Rev. A

# DOCUMENT FEEDBACK TECHNICAL SUPPORT

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

- ▶ Broadband communications systems

- ▶ DOCSIS 3.1 and 4.0 CMTS

- Phased array radar and electronic warfare

- ▶ Electronic test and measurement systems

#### **GENERAL DESCRIPTION**

The AD9177 is a highly integrated device with four 16-bit, 12 GSPS maximum sample rate, RF digital-to-analog converter (DAC) cores supporting up to eight baseband channels. The device is well suited for applications requiring wideband DACs to process signals of wide instantaneous bandwidth. The device features an 8-lane, 24.75 Gbps JESD204C or 15.5 Gbps JESD204B data receiver (JRx) port, an on-chip clock multiplier, and digital signal processing (DSP) datapaths capable of processing complex signals for wideband or multiband direct to RF applications, phase array radar systems, and electronic warfare applications. The DSP datapaths can be bypassed to allow a direct connection between the data receiver port and the DAC cores.

For direct digital synthesis (DDS) applications, the AD9177 can be operated without a data receiver port to generate multiple sine wave tones of varying frequencies. The main numerically controlled oscillator (NCO) block inside each of the four course digital upconverters (DUCs) contains one 48-bit NCO and a bank of thirty one 32-bit NCOs, each with an independent phase accumulator. Similarly, the main NCO block inside each of the course and fine digital downconverters (DDCs) in the receive datapath contains a bank of sixteen 48-bit NCOs that can be looped into the transmit datapath for processing ahead of the course DUCs and DAC outputs. Combined with general-purpose input/output (GPIO) controls for frequency hopping, preconfigurable profile selection, and the ability to synchronize the NCOs to a common trigger using the SYSREF input port, this bank allows phase coherent fast frequency hopping (FFH) for applications where multiple devices are synchronized or where NCO frequencies are continuously adjusted during operation.

## **TABLE OF CONTENTS**

| Features                                                                        | CMOS Pin Specifications.  DAC AC Specifications.  Timing Specifications.  Absolute Maximum Ratings.  Thermal Resistance.  ESD Caution.  Pin Configuration and Function Descriptions.  Typical Performance Characteristics.  DAC.  Theory of Operation.  Applications Information.  Outline Dimensions.  Ordering Guide.  Evaluation Boards. | 12<br>14<br>14<br>15<br>18<br>18<br>22<br>24<br>25 |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Electrical and Speed Specifications8                                            |                                                                                                                                                                                                                                                                                                                                             |                                                    |

| REVISION HISTORY                                                                |                                                                                                                                                                                                                                                                                                                                             |                                                    |

| <b>7/2021—Rev. 0 to Rev. A</b> Changes to Data Sheet Title and Features Section |                                                                                                                                                                                                                                                                                                                                             | ′                                                  |

6/2021—Revision 0: Initial Version

analog.com Rev. A | 2 of 25

Data Sheet

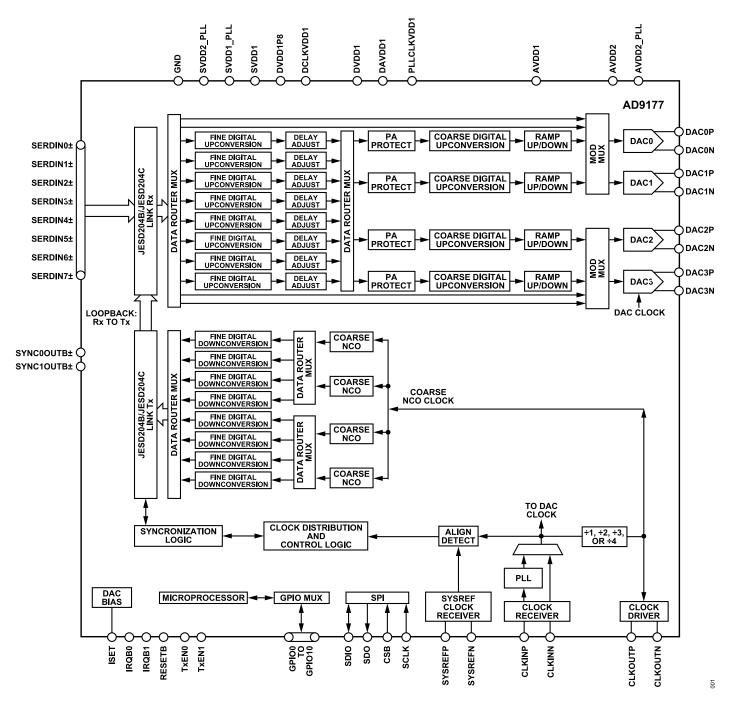

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

analog.com Rev. A | 3 of 25

#### **SPECIFICATIONS**

#### RECOMMENDED OPERATING CONDITIONS

Successful DAC calibration is required during the device initialization phase that occurs shortly after power-up to ensure long-term reliability of the DAC core circuitry. Refer to the UG-1578 user guide for more information on device initialization.

Table 1.

| Parameter                                             | Min  | Тур | Max  | Unit |

|-------------------------------------------------------|------|-----|------|------|

| OPERATING JUNCTION TEMPERATURE (T <sub>J</sub> )      | -40  |     | +120 | °C   |

| ANALOG SUPPLY VOLTAGE RANGE                           |      |     |      |      |

| AVDD2, AVDD2_PLL                                      | 1.9  | 2.0 | 2.1  | V    |

| AVDD1, PLLCLKVDD1                                     | 0.95 | 1.0 | 1.05 | V    |

| DIGITAL SUPPLY VOLTAGE RANGE                          |      |     |      |      |

| DVDD1, DCLKVDD1, DAVDD1                               | 0.95 | 1.0 | 1.05 | V    |

| DVDD1P8                                               | 1.7  | 1.8 | 2.1  | V    |

| SERIALIZER/DESERIALIZER (SERDES) SUPPLY VOLTAGE RANGE |      |     |      |      |

| SVDD2_PLL                                             | 1.9  | 2.0 | 2.1  | V    |

| SVDD1, SVDD1_PLL                                      | 0.95 | 1.0 | 1.05 | V    |

#### POWER CONSUMPTION

Typical at nominal supplies and maximum at 5% supplies. For the minimum and maximum values,  $T_J$  varies between -40°C and +120°C. For the typical values,  $T_A$  = 25°C, which corresponds to  $T_J$  = 80°C, unless otherwise noted.

DAC datapath with a complex I/Q data rate frequency ( $f_{IQ\_DATA}$ ) = 2 GSPS, interpolation of 6×, and DAC frequency ( $f_{DAC}$ ) of 12 GSPS. JESD204C mode of 24C (L = 8, M = 8, F = 3, S = 2, K = 256, E = 3, N = 12, NP = 12).

See the UG-1578 user guide for further information on the JESD204B and JESD204C mode configurations and a detailed description of the settings referenced throughout this data sheet. A table showing other operational modes and the corresponding typical and maximum power consumption numbers is included.

**Table 2. Power Consumption**

| Parameter                                                                | Test Conditions/Comments                        | Min | Тур  | Max  | Unit |

|--------------------------------------------------------------------------|-------------------------------------------------|-----|------|------|------|

| CURRENTS                                                                 |                                                 |     |      |      |      |

| AVDD2 (I <sub>AVDD2</sub> )                                              | 2.0 V supply                                    |     | 273  | 301  | mA   |

| AVDD2_PLL (I <sub>AVDD2 PLL</sub> ) +SVDD2_PLL (I <sub>SVDD2 PLL</sub> ) | 2.0 V supply                                    |     | 45   | 56   | mA   |

| Power Dissipation for 2 V Supplies                                       | 2.0 V supply total power dissipation            |     | 0.63 | 0.7  | W    |

| PLLCLKVDD1 (I <sub>PLLCLKVDD1</sub> )                                    | 1.0 V supply                                    |     | 15   | 25   | mA   |

| AVDD1 (I <sub>AVDD1</sub> )                                              | 1.0 V supply                                    |     | 1770 | 2338 | mA   |

| DAVDD1 (I <sub>DAVDD1</sub> )                                            | 1.0 V supply                                    |     | 1140 | 1484 | mA   |

| DVDD1 (I <sub>DVDD1</sub> )                                              | 1.0 V supply                                    |     | 1823 | 2973 | mA   |

| SVDD1 (I <sub>SVDD1</sub> ) + SVDD1_PLL (I <sub>SVDD1_PLL</sub> )        | 1.0 V supply                                    |     | 1046 | 1600 | mA   |

| Power Dissipation for 1 V Supplies                                       | 1.0 V supply total power dissipation            |     | 5.7  | 8.4  | W    |

| DVDD1P8 (I <sub>DVDD1P8</sub> )                                          | 1.8 V supply                                    |     | 7    | 10   | mA   |

| Total Power Dissipation                                                  | Total power dissipation of 2 V and 1 V supplies |     | 6.4  | 9.1  | W    |

analog.com Rev. A | 4 of 25

#### **SPECIFICATIONS**

#### DAC DC SPECIFICATIONS

Nominal supplies with DAC full-scale output current ( $I_{OUTFS}$ ) = 26 mA, unless otherwise noted. ADC setup in 4 GSPS, full bandwidth mode (all digital downconverters bypassed). For the minimum and maximum values,  $T_J = -40^{\circ}$ C to +120°C, and for the typical values,  $T_A = 25^{\circ}$ C, which corresponds to  $T_J = 80^{\circ}$ C, unless otherwise noted.

Table 3. DAC DC Specifications

| Parameter                                                       | Test Conditions/Comments                                                                                                                                                                                                                | Min  | Тур  | Max             | Unit  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------|-------|

| DAC RESOLUTION                                                  |                                                                                                                                                                                                                                         | 16   |      |                 | Bit   |

| DAC ACCURACY                                                    |                                                                                                                                                                                                                                         |      |      |                 |       |

| Gain Error                                                      |                                                                                                                                                                                                                                         |      | 1.5  |                 | % FSR |

| Gain Matching                                                   |                                                                                                                                                                                                                                         |      | 0.7  |                 | % FSR |

| Integral Nonlinearity (INL)                                     | Shuffling disabled                                                                                                                                                                                                                      |      | 8.0  |                 | LSB   |

| Differential Nonlinearity (DNL)                                 | Shuffling disabled                                                                                                                                                                                                                      |      | 3.5  |                 | LSB   |

| DAC ANALOG OUTPUTS                                              | DACxP and DACxN                                                                                                                                                                                                                         |      |      |                 |       |

| Full-Scale Output Current Range                                 | AC coupling, setting resistance ( $R_{SET}$ ) = 5 k $\Omega$                                                                                                                                                                            |      |      |                 |       |

| AC Coupling                                                     | Output common-mode voltage (V <sub>CM</sub> ) = 0 V                                                                                                                                                                                     | 6.43 | 26.5 | 37.75           | mA    |

| DC Coupling                                                     | 50 $\Omega$ shunt to a negative supply, forcing V <sub>CM</sub> = 0 V                                                                                                                                                                   | 6.43 |      | 37.75           | mA    |

|                                                                 | 50 $\Omega$ shunt to GND, forcing V <sub>CM</sub> = 0.3 V                                                                                                                                                                               | 6.43 |      | 20 <sup>1</sup> | mA    |

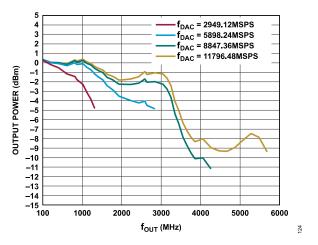

| Full-Scale Sine Wave Output Power with AC Coupling <sup>2</sup> | Ideal 2:1 balun interface to 50 $\Omega$                                                                                                                                                                                                |      |      |                 |       |

| I <sub>OUTFS</sub> = 26.5 mA                                    |                                                                                                                                                                                                                                         |      | 3.3  |                 | dBm   |

| I <sub>OUTFS</sub> = 37.75 mA                                   |                                                                                                                                                                                                                                         |      | 7    |                 | dBm   |

| Common-Mode Output Voltage (VCM <sub>OUT</sub> )                |                                                                                                                                                                                                                                         |      | 0    |                 | V     |

| AC Coupling                                                     | Bias each output to GND across a shunt inductor                                                                                                                                                                                         |      | 0    |                 | V     |

| DC Coupling                                                     | Bias each output to a negative voltage rail across a 25 $\Omega$ to 200 $\Omega$ resistor, selected such that VCM <sub>OUT</sub> = 0 V, VCM <sub>OUT</sub> = 0.3 V is with a 25 $\Omega$ resistor to GND and I <sub>OUTFS</sub> = 20 mA |      | 0    | 0.3             | V     |

| Differential Resistance                                         |                                                                                                                                                                                                                                         |      | 100  |                 | Ω     |

$<sup>^{\</sup>rm 1}$  For dc-coupled applications, the maximum full-scale output current is limited by the maximum VCM  $_{\rm OUT}$  specification.

analog.com Rev. A | 5 of 25

<sup>&</sup>lt;sup>2</sup> The actual measured full-scale power is frequency dependent due to DAC sinc response, impedance mismatch loss, and balun insertion loss.

#### **SPECIFICATIONS**

#### **CLOCK INPUTS AND OUTPUTS**

For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and  $\pm 5\%$  of nominal supply, unless otherwise noted.

Table 4. Clock Inputs and Outputs

| Parameter                                          | Test Conditions/Comments | Min | Тур | Max | Unit   |

|----------------------------------------------------|--------------------------|-----|-----|-----|--------|

| CLOCK INPUTS                                       | CLKINP and CLKINN        |     |     |     |        |

| Differential Input Power                           | Direct RF clock          |     |     |     |        |

| Minimum                                            |                          |     |     | 0   | dBm    |

| Maximum                                            |                          |     |     | 6   | dBm    |

| Common-Mode Voltage                                | AC-coupled               |     |     | 0.5 | V      |

| Differential Input Resistance                      |                          |     |     | 100 | Ω      |

| Differential Input Capacitance                     |                          |     |     | 0.3 | pF     |

| CLOCK OUTPUTS (ADC CLOCK DRIVER)                   | ADCDRVP and ADCDRVN      |     |     |     |        |

| Differential Output Voltage Magnitude <sup>1</sup> | 1.5 GHz                  |     |     | 740 | mV p-p |

|                                                    | 2.0 GHz                  |     |     | 690 | mV p-p |

|                                                    | 3.0 GHz                  |     |     | 640 | mV p-p |

|                                                    | 6.0 GHz                  |     |     | 490 | mV p-p |

| Differential Output Resistance                     |                          |     |     | 100 | Ω      |

| Common-Mode Voltage                                | AC-coupled               |     |     | 0.5 | V      |

$<sup>^{1}</sup>$  Measured with differential 100  $\Omega$  load and less than 2 mm of printed circuit board (PCB) trace from package ball.

# **CLOCK INPUT AND PHASE-LOCKED LOOP (PLL) FREQUENCY SPECIFICATIONS**

For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and  $\pm 5\%$  of nominal supply, unless otherwise noted.

Table 5. Clock Input and PLL Frequency Specifications

| Parameter                                                | <b>Test Conditions/Comments</b> | Min               | Тур | Max   | Unit |

|----------------------------------------------------------|---------------------------------|-------------------|-----|-------|------|

| CLOCK INPUTS (CLKINP, CLKINN) FREQUENCY RANGES           |                                 | 25                |     | 12000 | MHz  |

| PHASE FREQUENCY DETECTOR (PFD) INPUT FREQUENCY RANGES    |                                 | 25                |     | 750   | MHz  |

| FREQUENCY RANGES ACCORDING TO CLOCK PATH CONFIGURATION   |                                 |                   |     |       |      |

| Direct Clock (PLL Off)                                   |                                 | 2900 <sup>1</sup> |     | 12000 | MHz  |

| PLL Reference Clock (PLL On)                             | M divider set to divide by 1    | 25                |     | 750   | MHz  |

|                                                          | M divider set to divide by 2    | 50                |     | 1500  | MHz  |

|                                                          | M divider set to divide by 3    | 75                |     | 2250  | MHz  |

|                                                          | M divider set to divide by 4    | 100               |     | 3000  | MHz  |

| PLL VOLTAGE CONTROLLED OSCILLATOR (VCO) FREQUENCY RANGES |                                 |                   |     |       |      |

| VCO Output                                               |                                 |                   |     |       |      |

| Divide by 1                                              | D divider set to divide by 1    | 5.8               |     | 12    | GHz  |

| Divide by 2                                              | D divider set to divide by 2    | 2.9               |     | 6     | GHz  |

| Divide by 3                                              | D divider set to divide by 3    | 1.93333           |     | 4     | GHz  |

| Divide by 4                                              | D divider set to divide by 4    | 1.45              |     | 3     | GHz  |

<sup>1</sup> The minimum direct clock frequency is limited by the minimum DAC (core) sample rate, as specified in Table 6. The clock receiver can accommodate the full range between the minimum PLL reference clock frequency and the maximum direct clock frequency.

analog.com Rev. A | 6 of 25

#### **SPECIFICATIONS**

#### DAC SAMPLE RATE SPECIFICATIONS

Nominal supplies. For the minimum and maximum values,  $T_J = -40^{\circ}\text{C}$  to +120°C and ±5% of nominal supply. For the typical values,  $T_A = 25^{\circ}\text{C}$ , which corresponds to  $T_J = 80^{\circ}\text{C}$ , unless otherwise noted.

Table 6. DAC Sample Rate Specifications

| Parameter                    | Min | Тур | Max | Unit |

|------------------------------|-----|-----|-----|------|

| DAC SAMPLE RATE <sup>1</sup> |     |     |     |      |

| Minimum                      |     |     | 2.9 | GSPS |

| Maximum                      | 12  |     |     | GSPS |

<sup>&</sup>lt;sup>1</sup> Pertains to the update rate of the DAC core, independent of the datapath and JESD204 mode configuration.

#### INPUT DATA RATE SPECIFICATIONS

For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and  $\pm 5\%$  of nominal supply, unless otherwise noted.

Table 7. Input Data Rate Specifications

| Parameter <sup>1, 2</sup>                                                   | Test Conditions/Comments                                                                                                                                                                                | Min | Тур | Max   | Unit |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------|

| MAXIMUM DATA RATE PER NUMBER OF ACTIVE DAC OUTPUTS                          |                                                                                                                                                                                                         |     |     |       |      |

|                                                                             | Single DAC, fine digital upconverter (FDUC) and coarse digital upconverter (CDUC) bypassed (1× interpolation), 16-bit resolution, limited by the maximum DAC clock rate                                 |     |     | 12000 | MSPS |

|                                                                             | Quad DAC, FDUC and CDUC bypassed (1× interpolation), 12-bit resolution, limited by the maximum JESD204C link throughput (M = 4, L = 8)                                                                  |     |     | 4000  | MSPS |

| MAXIMUM COMPLEX (I/Q) DATA RATE PER<br>NUMBER OF ACTIVE INPUT DATA CHANNELS |                                                                                                                                                                                                         |     |     |       |      |

|                                                                             | 1 channel: FDUC bypassed, 1 CDUC enabled, 12-bit or 16-bit resolution, limited by the maximum CDUC NCO clock rate                                                                                       |     |     | 6000  | MSPS |

|                                                                             | 2 channels: FDUC bypassed, 2 CDUCs enabled, 12-bit resolution, limited by the maximum JESD204C link throughput (M = 4, L = 8)                                                                           |     |     | 4000  | MSPS |

|                                                                             | 4 channels: FDUC bypassed, 4 CDUCs enabled, 12-bit resolution, limited by the maximum JESD204C link throughput (M = 8, L = 8)                                                                           |     |     | 2000  | MSPS |

|                                                                             | 8 channels: 8 FDUCs enabled, one or more CDUC enabled, 12-bit or 16-bit resolution, limited by the maximum FDUC NCO clock rate divided by the minimum 2× interpolation rate required to enable the FDUC |     |     | 750   | MSPS |

<sup>1</sup> The values listed for these parameters are the maximum possible when considering all JESD204 modes of operation. Some modes are more limiting, based on other parameters.

analog.com Rev. A | 7 of 25

The interpolation filters in the Tx datapath have a total complex filter bandwidth of 80% of the data rate, combining the 40% bandwidth in the I path and 40% bandwidth in the Q path. Similarly, the decimation stages inside the Rx datapath use filters with a total complex filter bandwidth of 81.4%. Therefore, the maximum allowed instantaneous complex signal bandwidth (iBW) per channel is calculated as iBW = (complex I/Q data rate per channel) × (total complex filter bandwidth).

## **SPECIFICATIONS**

#### NCO FREQUENCY SPECIFICATIONS

For the minimum and maximum values,  $T_J = -40^{\circ}$ C to +120°C and ±5% of nominal supply, unless otherwise noted.

**Table 8. NCO Frequency Specifications**

| Parameter                                              | Test Conditions/Comments                                        | Min  | Тур Мах | Unit |

|--------------------------------------------------------|-----------------------------------------------------------------|------|---------|------|

| MAXIMUM NCO CLOCK RATE                                 |                                                                 |      |         |      |

| FDUC NCO                                               |                                                                 |      | 1.5     | GHz  |

| CDUC NCO                                               |                                                                 |      | 12      | GHz  |

| MAXIMUM NCO SHIFT FREQUENCY RANGE                      |                                                                 |      |         |      |

| FDUC NCO                                               | Channel interpolation rate must be > 1×                         | -750 | +750    | MHz  |

| CDUC NCO                                               | f <sub>DAC</sub> = 12 GHz, main interpolation rate must be > 1× | -6   | +6      | GHz  |

| MAXIMUM FREQUENCY SPACING BETWEEN CHANNELIZER CHANNELS |                                                                 |      |         |      |

| Tx FDUC Channels                                       | Maximum FDUC NCO clock rate × 0.8 <sup>1</sup>                  |      | 1200    | MHz  |

<sup>&</sup>lt;sup>1</sup> The 0.8 factor is because the total complex pass-band of the first interpolation filter is 80% of the filter input data rate.

## JESD204B AND JESD204C INTERFACE ELECTRICAL AND SPEED SPECIFICATIONS

Nominal supplies. For the minimum and maximum values,  $T_J = -40^{\circ}\text{C}$  to +120°C and ±5% of nominal supply, and for the typical values,  $T_A = 25^{\circ}\text{C}$ , which corresponds to  $T_J = 80^{\circ}\text{C}$ , unless otherwise noted.

Table 9. Serial Interface Rate Specifications

| Parameter                      | Test Conditions/Comments | Min Typ | Max    | Unit |

|--------------------------------|--------------------------|---------|--------|------|

| JESD204B SERIAL INTERFACE RATE | Serial lane rate         | 1.0     | 15.5   | Gbps |

| Unit Interval                  |                          | 64.5    | 1000.0 | ps   |

| JESD204C SERIAL INTERFACE RATE | Serial lane rate         | 6.0     | 24.75  | Gbps |

| Unit Interval                  |                          | 40.4    | 166.67 | ps   |

Table 10. JESD204 Receiver (JRx) Electrical Specifications

| Parameter                                    | Test Conditions/Comments               | Min | Тур                     | Max                   | Unit   |

|----------------------------------------------|----------------------------------------|-----|-------------------------|-----------------------|--------|

| JESD204 DATA INPUTS                          | SERDINx±, where x = 0 to 7             |     |                         |                       |        |

| Standards Compliance                         |                                        |     | JESD204B and            | IESD204C              |        |

| Differential Voltage, R <sub>VDIFF</sub>     |                                        |     | 800                     |                       | mV p-p |

| Differential Impedance, Z <sub>RDIFF</sub>   | At dc                                  |     | 98                      |                       | Ω      |

| Termination Voltage, V <sub>TT</sub>         | AC-coupled                             |     | 0.97                    |                       | V      |

| SYNCxOUTB± OUTPUTS1                          | Where x = 0 or 1                       |     |                         |                       |        |

| Output Differential Voltage, V <sub>OD</sub> | Driving 100 $\Omega$ differential load |     | 400                     |                       | mV     |

| Output Offset Voltage, V <sub>OS</sub>       |                                        |     | DVDD1P8/2 + 0.2         |                       | V      |

| SYNCxOUTB+ AND SYNCxOUTB-                    | CMOS output option                     | Re  | efer to the CMOS Pin Sp | pecifications section |        |

<sup>&</sup>lt;sup>1</sup> IEEE 1596.3 standard LVDS compatible.

Table 11. SYSREF Electrical Specifications

| Parameter                                        | Test Conditions/Comments | Min | Тур    | Max                | Unit  |

|--------------------------------------------------|--------------------------|-----|--------|--------------------|-------|

| SYSREFP AND SYSREFN INPUTS                       |                          |     |        |                    |       |

| Logic Compliance                                 |                          |     | LVDS/L | VPECL <sup>1</sup> |       |

| Differential Input Voltage                       |                          |     | 0.7    | 1.9                | V p-p |

| Input Common-Mode Voltage Range                  | DC-coupled               |     | 0.675  | 2                  | V     |

| Input Resistance, R <sub>IN</sub> (Differential) |                          |     | 100    |                    | Ω     |

| Input Capacitance (Differential)                 |                          |     | 1      |                    | pF    |

<sup>1</sup> LVDS means low voltage differential signaling and LVPECL means low voltage positive/pseudo emitter-coupled logic.

analog.com Rev. A | 8 of 25

## **SPECIFICATIONS**

## **CMOS PIN SPECIFICATIONS**

For the minimum and maximum values,  $T_J = -40^{\circ}\text{C}$  to  $+120^{\circ}\text{C}$ , 1.7 V  $\leq$  DVDD1P8  $\leq$  2.1 V, other supplies nominal, unless otherwise noted.

Table 12. CMOS Pin Specifications

| Parameter         | Symbol          | Test Conditions/Comments                       | Min            | Тур | Max           | Unit |

|-------------------|-----------------|------------------------------------------------|----------------|-----|---------------|------|

| INPUTS            |                 | SDIO, SCLK, CSB, RESETB, RXEN0, RXEN1,         |                |     |               |      |

|                   |                 | TXEN0, TXEN1, SYNC0INB±, SYNC1INB±, and        |                |     |               |      |

|                   |                 | GPIOx                                          |                |     |               |      |

| Logic 1 Voltage   | V <sub>IH</sub> |                                                | 0.70 × DVDD1P8 |     |               | V    |

| Logic 0 Voltage   | V <sub>IL</sub> |                                                |                |     | 0.3 × DVDD1P8 | V    |

| Input Resistance  |                 |                                                | 40             |     |               | kΩ   |

| OUTPUTS           |                 | SDIO, SDO, GPIOx, SYNC0OUTB±, and              |                |     |               |      |

|                   |                 | SYNC1OUTB±, 4 mA load                          |                |     |               |      |

| Logic 1 Voltage   | V <sub>OH</sub> |                                                | DVDD1P8 - 0.45 |     |               | V    |

| Logic 0 Voltage   | V <sub>OL</sub> |                                                |                |     | 0.45          | V    |

| INTERRUPT OUTPUTS |                 | IRQB_0 and IRQB_1, pull-up resistor of 5 kΩ to |                |     |               |      |

|                   |                 | DVDD1P8                                        |                |     |               |      |

| Logic 1 Voltage   | V <sub>OH</sub> |                                                | 1.35           |     |               | V    |

| Logic 0 Voltage   | V <sub>OL</sub> |                                                |                |     | 0.48          | V    |

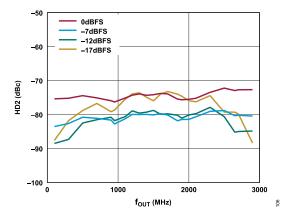

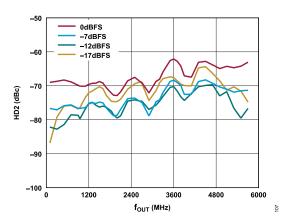

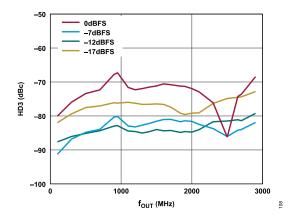

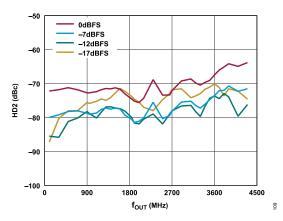

## **DAC AC SPECIFICATIONS**

Nominal supplies with  $T_A$  = 25°C. Specifications represent the average of all four DAC channels with the DAC  $I_{OUTFS}$  = 26 mA, unless otherwise noted.

Table 13. DAC AC Specifications

| Parameter                                      | Test Conditions/Comments                           | Min | Тур | Max | Unit |

|------------------------------------------------|----------------------------------------------------|-----|-----|-----|------|

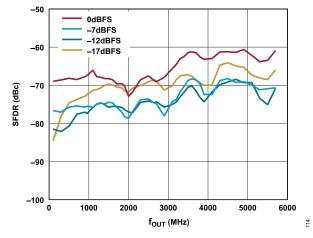

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)             |                                                    |     |     |     |      |

| Single-Tone, f <sub>DAC</sub> = 12 GSPS        | -7 dBFS digital backoff, shuffle enabled, 15C mode |     |     |     |      |

| Output Frequency (f <sub>OUT</sub> ) = 70 MHz  |                                                    | 63  | 80  |     | dBc  |

| f <sub>OUT</sub> = 100 MHz                     |                                                    |     | 77  |     | dBc  |

| f <sub>OUT</sub> = 500 MHz                     |                                                    |     | 76  |     | dBc  |

| f <sub>OUT</sub> = 900 MHz                     |                                                    |     | 77  |     | dBc  |

| f <sub>OUT</sub> = 1900 MHz                    |                                                    | 61  | 79  |     | dBc  |

| f <sub>OUT</sub> = 2600 MHz                    |                                                    |     | 75  |     | dBc  |

| f <sub>OUT</sub> = 3700 MHz                    |                                                    |     | 69  |     | dBc  |

| f <sub>OUT</sub> = 4500 MHz                    |                                                    |     | 68  |     | dBc  |

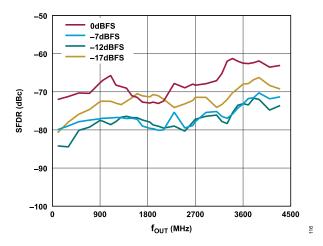

| Single-Tone, f <sub>DAC</sub> = 9 GSPS         | -7 dBFS digital backoff, shuffle enabled, 15C mode |     |     |     |      |

| f <sub>OUT</sub> = 100 MHz                     |                                                    |     | 78  |     | dBc  |

| f <sub>OUT</sub> = 500 MHz                     |                                                    |     | 78  |     | dBc  |

| f <sub>OUT</sub> = 900 MHz                     |                                                    |     | 77  |     | dBc  |

| f <sub>OUT</sub> = 1900 MHz                    |                                                    |     | 80  |     | dBc  |

| f <sub>OUT</sub> = 2600 MHz                    |                                                    |     | 80  |     | dBc  |

| f <sub>OUT</sub> = 3700 MHz                    |                                                    |     | 72  |     | dBc  |

| Single-Tone, f <sub>DAC</sub> = 6 GSPS         | -7 dBFS digital backoff, shuffle enabled, 15C mode |     |     |     |      |

| f <sub>OUT</sub> = 100 MHz                     |                                                    |     | 84  |     | dBc  |

| f <sub>OUT</sub> = 500 MHz                     |                                                    |     | 81  |     | dBc  |

| f <sub>OUT</sub> = 900 MHz                     |                                                    |     | 82  |     | dBc  |

| f <sub>OUT</sub> = 1900 MHz                    |                                                    |     | 81  |     | dBc  |

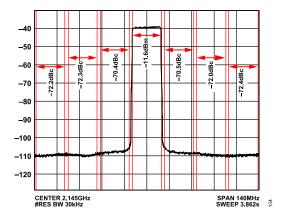

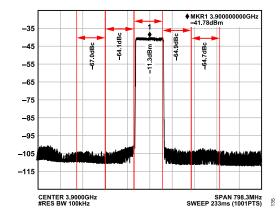

| ADJACENT CHANNEL LEAKAGE RATIO                 |                                                    |     |     |     |      |

| Single Carrier 20 MHz LTE Downlink Test Vector | -1 dBFS digital backoff, 256 QAM                   |     |     |     |      |

analog.com Rev. A | 9 of 25

# **SPECIFICATIONS**

Table 13. DAC AC Specifications

| Parameter                                                                           | Test Conditions/Comments                                               | Min | Тур  | Max | Unit        |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|------|-----|-------------|

| f <sub>DAC</sub> = 12 GSPS                                                          | f <sub>OUT</sub> = 1840 MHz                                            |     | 77   |     | dBc         |

|                                                                                     | f <sub>OUT</sub> = 2650 MHz                                            |     | 76   |     | dBc         |

|                                                                                     | f <sub>OUT</sub> = 3500 MHz                                            |     | 73   |     | dBc         |

| f <sub>DAC</sub> = 9 GSPS                                                           | f <sub>OUT</sub> = 1900 MHz                                            |     | 77   |     | dBc         |

|                                                                                     | f <sub>OUT</sub> = 2650 MHz                                            |     | 77   |     | dBc         |

| f <sub>DAC</sub> = 6 GSPS                                                           | f <sub>OUT</sub> = 750 MHz                                             |     | 79   |     | dBc         |

| 5.10                                                                                | f <sub>OUT</sub> = 1840 MHz                                            |     | 77   |     | dBc         |

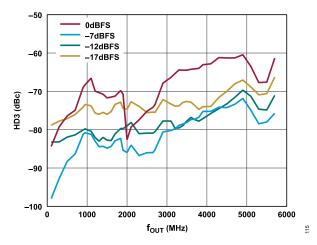

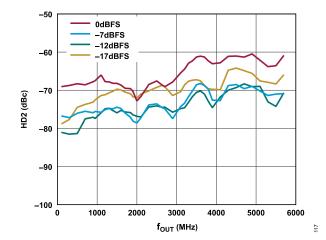

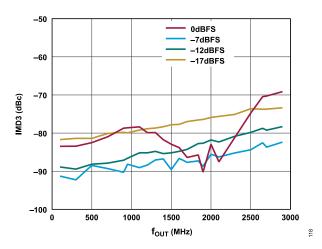

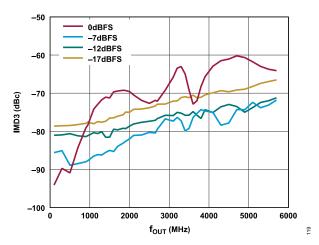

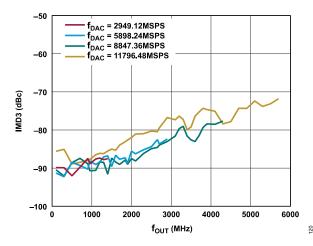

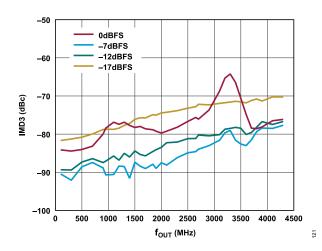

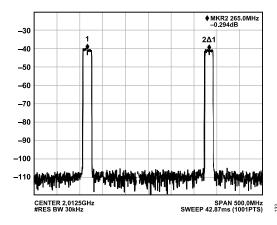

| THIRD-ORDER INTERMODULATION DISTORTION (IMD3)                                       | Two tone test, 1 MHz spacing, 0 dBFS digital backoff, -6 dBFS per tone |     |      |     |             |

| f <sub>DAC</sub> = 12 GSPS                                                          | f <sub>OUT</sub> = 1900 MHz                                            |     | -69  | -62 | dBc         |

|                                                                                     | f <sub>OUT</sub> = 2600 MHz                                            |     | -72  |     | dBc         |

|                                                                                     | f <sub>OUT</sub> = 3700 MHz                                            |     | -72  |     | dBc         |

| f <sub>DAC</sub> = 9 GSPS                                                           | f <sub>OUT</sub> = 1900 MHz                                            |     | -79  |     | dBc         |

| UNU                                                                                 | f <sub>OUT</sub> = 2600 MHz                                            |     | -76  |     | dBc         |

| f <sub>DAC</sub> = 6 GSPS                                                           | f <sub>OUT</sub> = 900 MHz                                             |     | -79  |     | dBc         |

| DAC 0 001. 0                                                                        | f <sub>OUT</sub> = 1900 MHz                                            |     | -90  |     | dBc         |

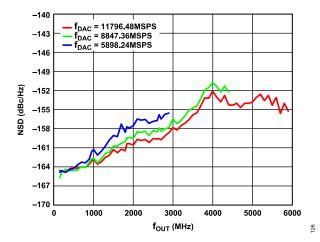

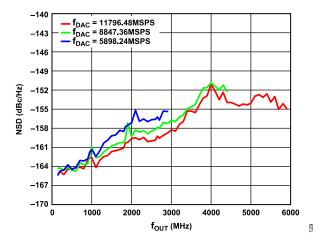

| NOISE SPECTRAL DENSITY (NSD)                                                        | 0 dBFS, NSD measurement taken at 10% away from                         |     |      |     | ubo         |

| tolog of Eofficial (Hob)                                                            | f <sub>OUT</sub> , shuffle off                                         |     |      |     |             |

| Single-Tone, f <sub>DAC</sub> = 12 GSPS                                             |                                                                        |     |      |     |             |

| f <sub>OUT</sub> = 150 MHz                                                          |                                                                        |     | -168 |     | dBc/Hz      |

| f <sub>OUT</sub> = 500 MHz                                                          |                                                                        |     | -167 |     | dBc/Hz      |

| f <sub>OUT</sub> = 950 MHz                                                          |                                                                        |     | -165 |     | dBc/Hz      |

| f <sub>OUT</sub> = 1840 MHz                                                         |                                                                        |     | -162 |     | dBc/Hz      |

| f <sub>OUT</sub> = 2650 MHz                                                         |                                                                        |     | -160 |     | dBc/Hz      |

| f <sub>OUT</sub> = 3700 MHz                                                         |                                                                        |     | -155 |     | dBc/Hz      |

| f <sub>OUT</sub> = 4500 MHz                                                         |                                                                        |     | -154 |     | dBc/Hz      |

| Single-Tone, f <sub>DAC</sub> = 9 GSPS                                              |                                                                        |     | 101  |     | GD0/112     |

| f <sub>OUT</sub> = 150 MHz                                                          |                                                                        |     | -168 |     | dBc/Hz      |

| f <sub>OUT</sub> = 500 MHz                                                          |                                                                        |     | -166 |     | dBc/Hz      |

| f <sub>OUT</sub> = 950 MHz                                                          |                                                                        |     | -164 |     | dBc/Hz      |

| f <sub>OUT</sub> = 1840 MHz                                                         |                                                                        |     | -160 |     | dBc/Hz      |

| f <sub>OUT</sub> = 1640 MHz                                                         |                                                                        |     | -158 |     | dBc/Hz      |

|                                                                                     |                                                                        |     |      |     |             |

| f <sub>OUT</sub> = 3700 MHz                                                         |                                                                        |     | -154 |     | dBc/Hz      |

| Single-Tone, f <sub>DAC</sub> = 6 GSPS                                              |                                                                        |     | 400  |     | -ID - /I I- |

| f <sub>OUT</sub> = 150 MHz                                                          |                                                                        |     | -168 |     | dBc/Hz      |

| f <sub>OUT</sub> = 500 MHz                                                          |                                                                        |     | -165 |     | dBc/Hz      |

| f <sub>OUT</sub> = 950 MHz                                                          |                                                                        |     | -163 |     | dBc/Hz      |

| f <sub>OUT</sub> = 1840 MHz                                                         |                                                                        |     | -159 |     | dBc/Hz      |

| f <sub>OUT</sub> = 2650 MHz                                                         |                                                                        |     | -157 |     | dBc/Hz      |

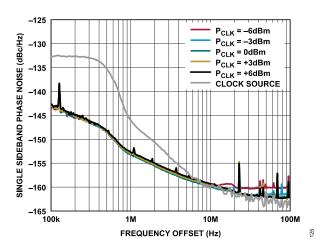

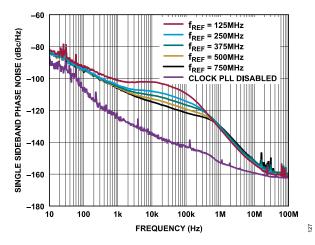

| SINGLE SIDEBAND PHASE NOISE OFFSET (PLL DISABLED)                                   | Direct device clock input at 6 dBm                                     |     |      |     |             |

| $f_{OUT}$ = 3.6 GHz, $f_{DAC}$ = 12 GSPS, CLKINx Frequency ( $f_{CLKIN}$ ) = 12 GHz | Rohde & Schwarz SMA100B B711 option                                    |     |      |     |             |

| 1 kHz                                                                               |                                                                        |     | -118 |     | dBc/Hz      |

| 10 kHz                                                                              |                                                                        |     | -129 |     | dBc/Hz      |

| 100 kHz                                                                             |                                                                        |     | -137 |     | dBc/Hz      |

| 600 kHz                                                                             |                                                                        |     | -144 |     | dBc/Hz      |

| 1.2 MHz                                                                             |                                                                        |     | -148 |     | dBc/Hz      |

| 1.8 MHz                                                                             |                                                                        |     | -149 |     | dBc/Hz      |

| 6 MHz                                                                               |                                                                        |     | -153 |     | dBc/Hz      |

analog.com Rev. A | 10 of 25

## **SPECIFICATIONS**

Table 13. DAC AC Specifications

| Parameter                                                       | Test Conditions/Comments                                                                                                           | Min | Тур  | Max | Unit   |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

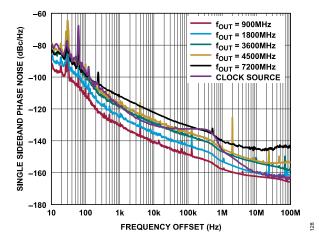

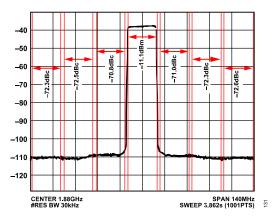

| SINGLE SIDEBAND PHASE NOISE OFFSET (PLL ENABLED)                | Loop filter component values include C1 = 22 nF,<br>R1 = 226 $\Omega$ , C2 = 2.2 nF, C3 = 33 nF,<br>and PFD = 500 MHz <sup>1</sup> |     | ·    |     |        |

| $f_{OUT}$ = 1.8 GHz, $f_{DAC}$ = 12 GSPS, $f_{CLKIN}$ = 0.5 GHz |                                                                                                                                    |     |      |     |        |

| 1 kHz                                                           |                                                                                                                                    |     | -106 |     | dBc/Hz |

| 10 kHz                                                          |                                                                                                                                    |     | -113 |     | dBc/Hz |

| 100 kHz                                                         |                                                                                                                                    |     | -120 |     | dBc/Hz |

| 600 kHz                                                         |                                                                                                                                    |     | -127 |     | dBc/Hz |

| 1.2 MHz                                                         |                                                                                                                                    |     | -134 |     | dBc/Hz |

| 1.8 MHz                                                         |                                                                                                                                    |     | -138 |     | dBc/Hz |

| 6 MHz                                                           |                                                                                                                                    |     | -150 |     | dBc/Hz |

$<sup>^{1}\,\,</sup>$  See UG-1578 for details on the loop filter components.

analog.com Rev. A | 11 of 25

Data Sheet

## **SPECIFICATIONS**

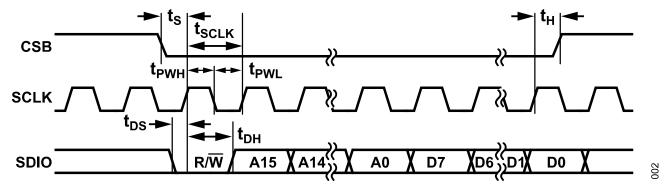

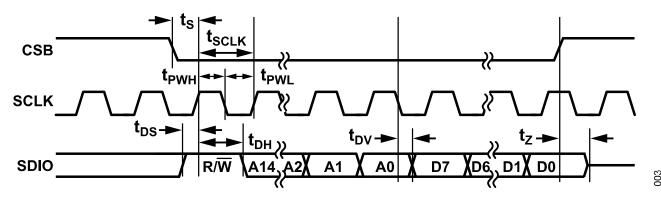

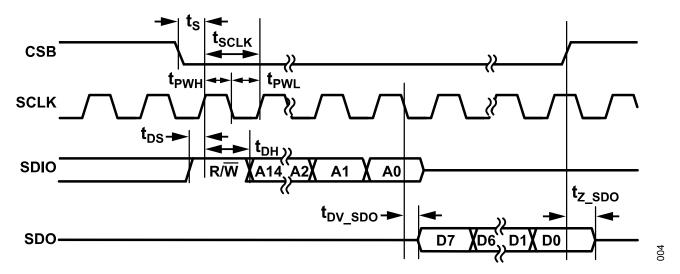

## **TIMING SPECIFICATIONS**

For the minimum and maximum values,  $T_J$  = -40°C to +120°C and ±5% of nominal supply, unless otherwise noted.

## **Table 14. Timing Specifications**

| Parameter                                   | Symbol                                  | Test Conditions/Comments                    | Min Typ | Max | Unit |

|---------------------------------------------|-----------------------------------------|---------------------------------------------|---------|-----|------|

| SERIAL PORT INTERFACE (SPI) WRITE OPERATION |                                         |                                             |         |     |      |

| Maximum SCLK Clock Rate                     | f <sub>SCLK</sub> , 1/t <sub>SCLK</sub> |                                             | 33      |     | MHz  |

| SCLK Clock High                             | t <sub>PWH</sub>                        | SCLK = 33 MHz                               | 8       |     | ns   |

| SCLK Clock Low                              | t <sub>PWL</sub>                        | SCLK = 33 MHz                               | 8       |     | ns   |

| SDIO to SCLK Setup Time                     | t <sub>DS</sub>                         |                                             | 4       |     | ns   |

| SCLK to SDIO Hold Time                      | t <sub>DH</sub>                         |                                             | 4       |     | ns   |

| CSB to SCLK Setup Time                      | t <sub>S</sub>                          |                                             | 4       |     | ns   |

| CLK to CSB Hold Time                        | t <sub>H</sub>                          |                                             | 4       |     | ns   |

| SPI READ OPERATION                          |                                         |                                             |         |     |      |

| LSB First Data Format                       |                                         |                                             |         |     |      |

| Maximum SCLK Clock Rate                     | f <sub>SCLK</sub> , 1/t <sub>SCLK</sub> |                                             | 33      |     | MHz  |

| SCLK Clock High                             | t <sub>PWH</sub>                        |                                             | 8       |     | ns   |

| SCLK Clock Low                              | t <sub>PWL</sub>                        |                                             | 8       |     | ns   |

| MSB First Data Format                       |                                         |                                             |         |     |      |

| Maximum SCLK Clock Rate                     | f <sub>SCLK</sub> , 1/t <sub>SCLK</sub> |                                             | 15      |     | MHz  |

| SCLK Clock High                             | t <sub>PWH</sub>                        |                                             | 30      |     | ns   |

| SCLK Clock Low                              | t <sub>PWL</sub>                        |                                             | 30      |     | ns   |

| SDIO to SCLK Setup Time                     | t <sub>DS</sub>                         |                                             | 4       |     | ns   |

| SCLK to SDIO Hold Time                      | t <sub>DH</sub>                         |                                             | 4       |     | ns   |

| CSB to SCLK Setup Time                      | t <sub>S</sub>                          |                                             | 4       |     | ns   |

| SCLK to SDIO Data Valid Time                | t <sub>DV</sub>                         |                                             | 20      |     | ns   |

| SCLK to SDO Data Valid Time                 | t <sub>DV_SDO</sub>                     |                                             | 20      |     | ns   |

| CSB to SDIO Output Valid to High-Z          | t <sub>Z</sub>                          |                                             | 20      |     | ns   |

| CSB to SDO Output Valid to High-Z           | t <sub>Z_SDO</sub>                      |                                             | 20      |     | ns   |

| RESETB                                      |                                         | Minimum hold time to trigger a device reset | 40      |     | ns   |

**AD9177**

## **Timing Diagrams**

Figure 2. Timing Diagram for 3-Wire Write Operation

analog.com Rev. A | 12 of 25

## **SPECIFICATIONS**

Figure 3. Timing Diagram for 3-Wire Read Operation

Figure 4. Timing Diagram for 4-Wire Read Operation

analog.com Rev. A | 13 of 25

#### **ABSOLUTE MAXIMUM RATINGS**

Table 15.

| Parameter                                                                                 | Rating                       |

|-------------------------------------------------------------------------------------------|------------------------------|

| ISET, DACxP, DACxN                                                                        | -0.3 V to AVDD2 + 0.3 V      |

| VCO_COARSE, VCO_FINE, VCO_VCM, VCO_VREG                                                   | -0.3 V to AVDD2_PLL + 0.3 V  |

| CLKINP, CLKINN                                                                            | -0.2 V to PLLCLKVDD1 + 0.2 V |

| ADCDRVN, ADCDRVP                                                                          | -0.2 V to CLKVDD1 + 0.2 V    |

| SERDINx±                                                                                  | -0.2 V to SVDD1 + 0.2 V      |

| SYSREFP, SYSREFN                                                                          | -0.2 V to +2.5 V             |

| SYNCXOUTB±, RESETB, TXENX, RXENX, IRQB_X, CSB, SCLK, SDIO, SDO, TMU_REFN, TMU_REFP, GPIOX | -0.3 V to DVDD1P8 + 0.3 V    |

| AVDD2, AVDD2_PLL, SVDD2_PLL,<br>DVDD1P8                                                   | -0.3 V to +2.2 V             |

| PLLCLKVDD1, AVDD1, DAVDD1,<br>DCLKVDD1, DVDD1, SVDD1,<br>SVDD1_PLL                        | -0.2 V to +1.2 V             |

| Temperature                                                                               |                              |

| Maximum Junction (T <sub>J</sub> ) <sup>1</sup>                                           | 120°C                        |

| Storage Range                                                                             | -65°C to +150°               |

Do not exceed this temperature for any duration of time when the device is powered.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. The use of appropriate thermal management techniques is recommended to ensure that the maximum  $T_J$  does not exceed the limits shown in Table 15.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{\text{JC TOP}}$  is the junction to case, thermal resistance.

$\theta_{\text{JB}}$  is the junction to board, thermal resistance.

Table 16. Simulated Thermal Resistance<sup>1</sup>

| PCB Type         | Airflow Velocity (m/sec) | $\theta_{JA}$ | θ <sub>JC_TOP</sub> | $\theta_{JB}$ | Unit |

|------------------|--------------------------|---------------|---------------------|---------------|------|

| JEDEC 2s2p Board | 0.0                      | 14.9          | 0.70                | 1.8           | °C/W |

Thermal resistance values specified are simulated based on JEDEC specifications in compliance with JESD51-12 with the device power equal to 9 W.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. A | 14 of 25

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

Table 17. Pin Function Descriptions

| Pin No.                                                                   | Mnemonic   | Type  | Description                                                             |

|---------------------------------------------------------------------------|------------|-------|-------------------------------------------------------------------------|

| POWER SUPPLIES                                                            |            |       |                                                                         |

| A2, E2, H2, L2, P2, V2, D7, E7, P7, R7, B11, U11                          | AVDD2      | Input | Analog 2.0 V Supply Inputs for DAC.                                     |

| L3                                                                        | AVDD2_PLL  | Input | Analog 2.0 V Supply Input for Clock PLL Linear Dropout Regulator (LDO). |

| J5                                                                        | PLLCLKVDD1 | Input | Analog 1.0 V Supply Input for Clock PLL.                                |

| D2, D3, D4, E3, F3, N3, P3, R2, R3, R4, G7, G8, M7, M8, G6, M6, D6, R6    | AVDD1      | Input | Analog 1.0 V Supply Inputs for DAC Clock.                               |

| E5, F5, N5, P5, J7, K7, D10, R10                                          | DAVDD1     | Input | Digital Analog 1.0 V Supply Inputs.                                     |

| F10, H9, H11, J9, J11, K9, K11, L9, L11, M9                               | DVDD1      | Input | Digital 1.0 V Supply Inputs.                                            |

| K5                                                                        | DCLKVDD1   | Input | Digital 1.0 V Clock Generation Supply.                                  |

| A16, B16, C16, D16, E16, F16, G16, H16, M16, N16, P16, R16, T16, U16, V16 | SVDD1      | Input | Digital 1.0 V Supply Inputs for SERDES Deserializer and Serializer.     |

analog.com Rev. A | 15 of 25

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 17. Pin Function Descriptions

| Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Mnemonic         | Туре         | Description                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SVDD2_PLL        | Input        | Digital 2.0 V Supply Input for SERDES LDO.                                                                                                                                                                                                                                              |

| J16, K16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SVDD1_PLL        | Input        | Digital 1.0 V Supply Inputs for SERDES Clock Generation and PLL.                                                                                                                                                                                                                        |

| C13, F9, T13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDD1P8          | Input        | Digital Interface and Temperature Monitoring Unit (TMU) Supply Inputs (Nominal 1.8 V).                                                                                                                                                                                                  |

| A1, A3, A4, A7, A8, A11, A17, A18, B2 to B6, B9, B10, B14, B15, C2, C5 to C8, C11, C17, C18, D1, D5, D9, D14, D15, E1, E4, E6, E17, E18, F2, F4, F6 to F8, F14, F15, G2 to G5, G17, G18, H1, H5 to H8, H10, H12, H14, H15, J2, J8, J10, J12, J14, J15, J17, J18, K2, K8, K10, K12, K14, K17, K18, L1, L5 to L8, L10, L12, L14, M2 to M5, M10, M17, M18, N2, N4, N6 to N10, N14, N15, P1, P4, P6, P17, P18, R1, R5, R9, R14, R15, T2, T5 to T8, T11, T17, T18, U2 to U6, U9, U10, U14, U15, V1, V3, V4, V7, V8, V11, V17, V18 | GND              | Input/output | Ground References.                                                                                                                                                                                                                                                                      |

| ANALOG OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |              |                                                                                                                                                                                                                                                                                         |

| B1, C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DACOP, DACON     | Output       | DACO Output Currents, Ground Referenced. Tie these pins to GND if unused.                                                                                                                                                                                                               |

| G1, F1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DAC1P, DAC1N     | Output       | DAC1 Output Currents, Ground Referenced. Tie these pins to GND if unused.                                                                                                                                                                                                               |

| M1, N1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DAC2P, DAC2N     | Output       | DAC2 Output Currents, Ground Referenced. Tie these pins to GND if unused.                                                                                                                                                                                                               |

| U1, T1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DAC3P, DAC3N     | Output       | DAC3 Output Currents, Ground Referenced. Tie these pins to GND if unused.                                                                                                                                                                                                               |

| H3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ISET             | Output       | DAC Bias Current Setting Pin. Connect this pin with a 5 k $\Omega$ resistor to GND.                                                                                                                                                                                                     |

| C4, C3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADCDRVP, ADCDRVN | Output       | Optional Clock Output (for example, ADC Clock Driver for an external ADC). These pins are disabled by default. Leave the pins floating if unused.                                                                                                                                       |

| K3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VCO_VREG         | Output       | PLL LDO Regulator Output. Decouple this pin to GND with a 2.2 µF capacitor.                                                                                                                                                                                                             |

| G9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TMU_REFN         | Output       | TMU ADC Negative Reference. Connect this pin to GND.                                                                                                                                                                                                                                    |

| G10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TMU_REFP         | Output       | TMU ADC Positive Reference. Connect this pin to DVDD1P8.                                                                                                                                                                                                                                |